Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

|                            |                                                                                   |

| Product Status             | Obsolete                                                                          |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 97                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                  |

| Supplier Device Package    | 124-VTLA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm124t-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note 1: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MZ EF family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- MCLR pin (see 2.3 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see 2.4 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 μF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close to

the pins as possible. It is recommended that the

capacitors be placed on the same side of the board

as the device. If space is constricted, the capacitor

can be placed on another layer on the PCB using a

via; however, ensure that the trace length from the

pin to the capacitor is within one-quarter inch

(6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

© 2015-2016 Microchip Technology Inc.

**TABLE 4-6:** SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS

|                  |                                                                        |          |                                             | SBTxREG                      | Gy Register                                |                  |                   |                   | SBTxRD  | y Register                                                      | SBTxWR  | y Register                                        |

|------------------|------------------------------------------------------------------------|----------|---------------------------------------------|------------------------------|--------------------------------------------|------------------|-------------------|-------------------|---------|-----------------------------------------------------------------|---------|---------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                      | Name     | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size   | Priority<br>(PRI) | Priority<br>Level | Name    | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name    | Write Permission (GROUP3, GROUP2, GROUP1, GROUP0) |

| 0                | System Bus                                                             | SBT0REG0 | R                                           | 0x1F8F0000                   | R                                          | 64 KB            | _                 | 0                 | SBT0RD0 | R/W <sup>(1)</sup>                                              | SBT0WR0 | R/W <sup>(1)</sup>                                |

| 0                |                                                                        | SBT0REG1 | R                                           | 0x1F8F8000                   | R                                          | 32 KB            | _                 | 3                 | SBT0RD1 | R/W <sup>(1)</sup>                                              | SBT0WR1 | R/W <sup>(1)</sup>                                |

|                  | Flash Memory <sup>(6)</sup> :                                          | SBT1REG0 | R                                           | 0x1D000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT1RD0 | R/W <sup>(1)</sup>                                              | SBT1WR0 | 0, 0, 0, 0                                        |

|                  | Program Flash<br>Boot Flash                                            | SBT1REG2 | R                                           | 0x1F8E0000                   | R                                          | 4 KB             | 1                 | 2                 | SBT1RD2 | R/W <sup>(1)</sup>                                              | SBT1WR2 | R/W <sup>(1)</sup>                                |

|                  | Prefetch Module                                                        | SBT1REG3 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD3 | R/W <sup>(1)</sup>                                              | SBT1WR3 | 0, 0, 0, 0                                        |

|                  |                                                                        | SBT1REG4 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD4 | R/W <sup>(1)</sup>                                              | SBT1WR4 | 0, 0, 0, 0                                        |

| 1                |                                                                        | SBT1REG5 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD5 | R/W <sup>(1)</sup>                                              | SBT1WR5 | 0, 0, 0, 0                                        |

|                  |                                                                        | SBT1REG6 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD6 | R/W <sup>(1)</sup>                                              | SBT1WR6 | 0, 0, 0, 0                                        |

|                  |                                                                        | SBT1REG7 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD7 | R/W <sup>(1)</sup>                                              | SBT1WR7 | 0, 0, 0, 0                                        |

|                  |                                                                        | SBT1REG8 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD8 | R/W <sup>(1)</sup>                                              | SBT1WR8 | 0, 0, 0, 0                                        |

|                  | RAM Bank 1 Memory                                                      | SBT2REG0 | R                                           | 0x00000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT2RD0 | R/W <sup>(1)</sup>                                              | SBT2WR0 | R/W <sup>(1)</sup>                                |

| 2                |                                                                        | SBT2REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | _                 | 3                 | SBT2RD1 | R/W <sup>(1)</sup>                                              | SBT2WR1 | R/W <sup>(1)</sup>                                |

|                  |                                                                        | SBT2REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT2RD2 | R/W <sup>(1)</sup>                                              | SBT2WR2 | R/W <sup>(1)</sup>                                |

|                  | RAM Bank 2 Memory                                                      | SBT3REG0 | R <sup>(4)</sup>                            | R <sup>(4)</sup>             | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT3RD0 | R/W <sup>(1)</sup>                                              | SBT3WR0 | R/W <sup>(1)</sup>                                |

| 3                |                                                                        | SBT3REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | _                 | 3                 | SBT3RD1 | R/W <sup>(1)</sup>                                              | SBT3WR1 | R/W <sup>(1)</sup>                                |

|                  |                                                                        | SBT3REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT3RD2 | R/W <sup>(1)</sup>                                              | SBT3WR2 | R/W <sup>(1)</sup>                                |

| 4                | External Memory via EBI and EBI                                        | SBT4REG0 | R                                           | 0x20000000                   | R                                          | 64 MB            | _                 | 0                 | SBT4RD0 | R/W <sup>(1)</sup>                                              | SBT4WR0 | R/W <sup>(1)</sup>                                |

| 4                | Module <sup>(6)</sup>                                                  | SBT4REG2 | R                                           | 0x1F8E1000                   | R                                          | 4 KB             | 0                 | 1                 | SBT4RD2 | R/W <sup>(1)</sup>                                              | SBT4WR2 | R/W <sup>(1)</sup>                                |

|                  | Peripheral Set 1:                                                      | SBT5REG0 | R                                           | 0x1F800000                   | R                                          | 128 KB           | _                 | 0                 | SBT5RD0 | R/W <sup>(1)</sup>                                              | SBT5WR0 | R/W <sup>(1)</sup>                                |

|                  | System Control<br>Flash Control                                        | SBT5REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | _                 | 3                 | SBT5RD1 | R/W <sup>(1)</sup>                                              | SBT5WR1 | R/W <sup>(1)</sup>                                |

| 5                | DMT/WDT<br>RTCC<br>CVR<br>PPS Input<br>PPS Output<br>Interrupts<br>DMA | SBT5REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT5RD2 | R/W <sup>(1)</sup>                                              | SBT5WR2 | R/W <sup>(1)</sup>                                |

Legend:

R = Read;

R/W = Read/Write;

'x' in a register name = 0-13;

'y' in a register name = 0-8.

Reset values for these bits are '0', '1', '1', '1', respectively. Note 1:

- The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset.

- The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset.

- 4: Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses.

- See Table 4-1for information on specific target memory size and start addresses.

- The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

REGISTER 4-4: SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 |                   | -                 |                   | _                 | _                 | _                | 1                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   |                   | _                 | -                 |                   | _                 | -                |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | GROU             | P<1:0>           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-3 Unimplemented: Read as '0'

bit 1-0 GROUP<1:0>: Requested Permissions Group bits

11 = Group 3

10 = Group 2

01 = Group 1

00 = Group 0

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

REGISTER 4-5: SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | _                 | _                 | -                 | _                 | _                 | _                 | _                | ERRP             |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 |                   |                   | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

bit 23-0 Unimplemented: Read as '0'

**Note:** Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | _                 | _                 | -                 | 1                 | NRSTX            | NRST             |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |

| 23.10        |                   |                   |                   | LSEO              | F<7:0>            |                   |                  |                  |

| 15:8         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |

| 13.6         |                   |                   |                   | FSEO              | F<7:0>            |                   |                  |                  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | HSEO              | F<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25 NRSTX: Reset of XCLK Domain bit

1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY

0 = Normal operation

bit 24 NRST: Reset of CLK Domain bit

1 = Reset the CLK domain, which is clock recovered from the peripheral bus

0 = Normal operation

bit 23-16 LSEOF<7:0>: Low-Speed EOF bits

These bits set the Low-Speed transaction in units of  $1.067 \mu s$  (default setting is  $121.6 \mu s$ ) prior to the EOF to stop new transactions from beginning.

bit 15-8 FSEOF<7:0>: Full-Speed EOF bits

These bits set the Full-Speed transaction in units of 533.3  $\mu$ s (default setting is 63.46  $\mu$ s) prior to the EOF to stop new transactions from beginning.

bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits

These bits set the Hi-Speed transaction in units of 133.3 µs (default setting is 17.07µs) prior to the EOF to stop new transactions from beginning.

### REGISTER 21-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule is not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 **DISSLW:** Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send NACK during Acknowledge

- 0 = Send ACK during Acknowledge

- bit 4 ACKEN: Acknowledge Sequence Enable bit

(when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for  $1^2$ C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

| ഗ         |

|-----------|

| ©         |

| 2         |

| $\approx$ |

| $\preceq$ |

| ώ         |

| $\simeq$  |

| జ         |

| Y         |

| g         |

| Š         |

| ĕ         |

| 363       |

|           |

TABLE 22-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       | •         |        |         |                                  |       |        |       |       | Bi          | ts          |         |       |          |          |      |        |       | "          |

|-----------------------------|-----------------------|-----------|--------|---------|----------------------------------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name      | Bit Range | 31/15  | 30/14   | 29/13                            | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 2600                        | U4MODE <sup>(1)</sup> | 31:16     | _      | _       | _                                | _     | _      | -     | _     | _           | -           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      | ON     | _       | SIDL                             | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2610                        | U4STA <sup>(1)</sup>  | 31:16     |        | _       | _                                | _     | _      |       | _     | ADM_EN      |             |         | 1     | ADDR     |          | 1    | 1      |       | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>  | UTXINV                           | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2620                        | U4TXREG               | 31:16     |        | _       | _                                |       | _      |       |       | _           |             | _       | _     |          | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        | _       | _                                |       | _      |       | _     | TX8         |             | I       |       | Transmit | Register | 1    | I      |       | 0000       |

| 2630                        | U4RXREG               | 31:16     |        | _       | _                                |       | _      |       | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        | _       | _                                |       | _      |       | _     | RX8         |             | I       |       | Receive  | Register | 1    | I      |       | 0000       |

| 2640                        | U4BRG <sup>(1)</sup>  | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        |         |                                  |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 2800                        | U5MODE <sup>(1)</sup> | 31:16     |        | _       | _                                | _     | _      |       | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      | ON     | _       | SIDL                             | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2810                        | U5STA <sup>(1)</sup>  | 31:16     | _      | _       | _                                | -     | _      | _     | _     | ADM_EN      |             |         |       | ADDR     |          |      |        | 1     | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>  | UTXINV                           | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2820                        | U5TXREG               | 31:16     | _      | _       | _                                | -     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 2020                        |                       | 15:0      | _      | _       | _                                | -     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |      |        | 1     | 0000       |

| 2830                        | U5RXREG               | 31:16     | _      | _       | _                                | -     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             | 00.020                | 15:0      | _      | _       | _                                | _     | _      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2840                        | U5BRG <sup>(1)</sup>  | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 2010                        | CODICO                | 15:0      |        |         |                                  |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 2400                        | U6MODE <sup>(1)</sup> | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 27100                       |                       | 15:0      | ON     | _       | SIDL                             | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2A10                        | U6STA <sup>(1)</sup>  | 31:16     | _      | _       | _                                | -     | _      | _     | _     | ADM_EN      |             |         |       | ADDR     |          |      |        | 1     | 0000       |

|                             |                       | 15:0      | UTXISE | EL<1:0> | UTXINV                           | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2A20                        | U6TXREG               | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| _,0                         |                       | 15:0      | _      | _       | _                                | _     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 2A30                        | U6RXREG               | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      |       | 0000       |

| 2,100                       | SSICKILLO             | 15:0      | _      | _       | _                                | _     | _      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2A40                        | U6BRG <sup>(1)</sup>  | 31:16     | _      | _       | _                                | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| _,                          | CODICO                | 15:0      |        |         | Baud Rate Generator Prescaler 00 |       |        |       |       | 0000        |             |         |       |          |          |      |        |       |            |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more informa-Note 1:

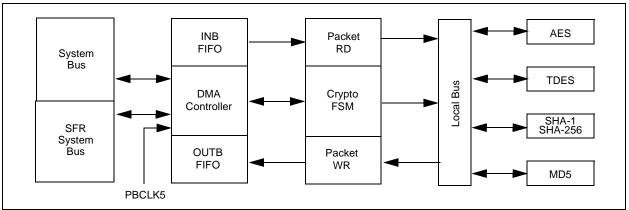

#### 26.0 CRYPTO ENGINE

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Crypto Engine is intended to accelerate applications that need cryptographic functions. By executing these functions in the hardware module, software overhead is reduced and actions, such as encryption, decryption, and authentication can execute much more quickly.

The Crypto Engine uses an internal descriptor-based DMA for efficient programming of the security association data and packet pointers (allowing scatter/gather data fetching). An intelligent state machine schedules the Crypto Engines based on the protocol selection and packet boundaries. The hardware engines can perform the encryption and authentication in sequence or in parallel.

The following are key features of the Crypto Engine:

- · Bulk ciphers and hash engines

- Integrated DMA to off-load processing:

- Buffer descriptor-based

- Secure association per buffer descriptor

- Some functions can execute in parallel

Bulk ciphers that are handled by the Crypto Engine include:

- AES:

- 128-bit, 192-bit, and 256-bit key sizes

- CBC, ECB, CTR, CFB, and OFB modes

- · DES/TDES:

- CBC, ECB, CFB, and OFB modes

Authentication engines that are available through the Crypto Engine include:

- SHA-1

- SHA-256

- MD-5

- AES-GCM

- HMAC operation (for all authentication engines)

The rate of data that can be processed by the Crypto Engine depends on these factors:

- · Which engine is in use

- Whether the engines are used in parallel or in series

- The demands on source and destination memories by other parts of the system (i.e., CPU, DMA, etc.)

- The speed of PBCLK5, which drives the Crypto Engine

Table 26-1 shows typical performance for various engines.

TABLE 26-1: CRYPTO ENGINE PERFORMANCE

| Engine/<br>Algorithm | Performance<br>Factor<br>(Mbps/MHz) | Maximum Mbps<br>(PBCLK5 = 100 MHz) |

|----------------------|-------------------------------------|------------------------------------|

| DES                  | 14.4                                | 1440                               |

| TDES                 | 6.6                                 | 660                                |

| AES-128              | 9.0                                 | 900                                |

| AES-192              | 7.9                                 | 790                                |

| AES-256              | 7.2                                 | 720                                |

| MD5                  | 15.6                                | 1560                               |

| SHA-1                | 13.2                                | 1320                               |

| SHA-256              | 9.3                                 | 930                                |

REGISTER 26-3: CEBDADDR: CRYPTO ENGINE BUFFER DESCRIPTOR REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   |                   |                   | BDPADDR           | <31:24>           |                   |                  |                  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | BDPADDR           | <23:16>           |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | BDPADDF           | R<15:8>           |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BDPADD            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 BDPADDR<31:0>: Current Buffer Descriptor Process Address Status bits

These bits contain the current descriptor address that is being processed by the Buffer Descriptor Processor (BDP).

# REGISTER 26-4: CEBDPADDR: CRYPTO ENGINE BUFFER DESCRIPTOR PROCESSOR REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | BASEADDI          | R<31:24>          |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | BASEADDI          | R<23:16>          |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | BASEADD           | R<15:8>           |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BASEADE           | DR<7:0>           |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 BASEADDR<31:0>: Buffer Descriptor Base Address bits

These bits contain the physical address of the first Buffer Descriptor in the Buffer Descriptor chain. When enabled, the Crypto DMA begins fetching Buffer Descriptors from this address.

**CEINTEN: CRYPTO ENGINE INTERRUPT ENABLE REGISTER REGISTER 26-7:**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                   | -                 | _                 | -                 | _                 | _                 | _                | _                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                     |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | _                 | _                 | _                 | _                 | AREIE             | PKTIE             | BDPIE            | PENDIE <sup>(1)</sup> |

-n = Value at POR

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 Unimplemented: Read as '0'

Legend:

bit 3 AREIE: Access Response Error Interrupt Enable bit

1 = Access response error interrupts are enabled

0 = Access response error interrupts are not enabled

bit 2 PKTIE: DMA Packet Completion Interrupt Enable bit

1 = DMA packet completion interrupts are enabled

0 = DMA packet completion interrupts are not enabled

**BDPIE:** DMA Buffer Descriptor Processor Interrupt Enable bit bit 1

1 = BDP interrupts are enabled

0 = BDP interrupts are not enabled

PENDIE: Master Interrupt Enable bit(1) bit 0

1 = Crypto Engine interrupts are enabled

0 = Crypto Engine interrupts are not enabled

Note 1: The PENDIE bit is a global enable bit and must be enabled together with the other interrupts desired.

### 26.2 Crypto Engine Buffer Descriptors

Host software creates a linked list of buffer descriptors and the hardware updates them. Table 26-3 provides a list of the Crypto Engine buffer descriptors, followed by format descriptions of each buffer descriptor (see Figure 26-2 through Figure 26-9).

TABLE 26-3: CRYPTO ENGINE BUFFER DESCRIPTORS

| Name (see Note 1) |       | Bit<br>31/2315/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|-------------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| BD_CTRL           | 31:24 | DESC_EN           | _                 | (                 | CRY_MODE<2:0      | >                 | _                 | _                | _                |  |  |  |  |  |

|                   | 23:16 | _                 | SA_FETCH_EN       | _                 | _                 | LAST_BD           | LIFM              | PKT_INT_EN       | CBD_INT_EN       |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | BD_BUFLEN         | <15:8>            |                   | •                |                  |  |  |  |  |  |

|                   | 7:0   |                   |                   |                   | BD_BUFLEN         | N<7:0>            |                   |                  |                  |  |  |  |  |  |

| BD_SA_ADDR        | 31:24 |                   |                   |                   | BD_SAADDR         | <31:24>           |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   |                   |                   | BD_SAADDR         | <23:16>           |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   | BD_SAADDR<15:8>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   | BD_SAADR<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| BD_SCRADDR        | 31:24 |                   |                   |                   | BD_SRCADDR        | R<31:24>          |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   | BD_SRCADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | BD_SRCADDI        | R<15:8>           |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   |                   | BD_SRCADDR<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| BD_DSTADDR        | 31:24 |                   | BD_DSTADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 | BD_DSTADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  | BD_DSTADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   | BD_DSTADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| BD_NXTPTR         | 31:24 |                   | BD_NXTADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   |                   |                   | BD_NXTADDR        | ?<23:16>          |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | BD_NXTADDF        | R<15:8>           |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   |                   |                   |                   | BD_NXTADD         | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| BD_UPDPTR         | 31:24 |                   |                   |                   | BD_UPDADDR        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   |                   |                   | BD_UPDADDR        | R<23:16>          |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | BD_UPDADDI        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   |                   | BD_UPDADDR<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| BD_MSG_LEN        | 31:24 |                   |                   |                   | MSG_LENGTH        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   |                   |                   | MSG_LENGTH        | 1<23:16>          |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | MSG_LENGTI        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   | MSG_LENGTH<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| BD_ENC_OFF        | 31:24 |                   |                   |                   | ENCR_OFFSE        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 23:16 |                   |                   |                   | ENCR_OFFSE        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 15:8  |                   |                   |                   | ENCR_OFFSE        |                   |                   |                  |                  |  |  |  |  |  |

|                   | 7:0   |                   |                   |                   | ENCR_OFFSI        | ET<7:0>           |                   |                  |                  |  |  |  |  |  |

Note 1: The buffer descriptor must be allocated in memory on a 64-bit boundary.

**FIGURE 28-1: ADC BLOCK DIAGRAM** SYSCLK REFOLKS AN0 AVDD AVss VRFF+ VREE-AN45 🖾 01 ADCSEL<1:0>  $\boxtimes$ N/C  $\boxtimes$ 10 N/C ☆ Tclk SH0ALT<1:0> CONCLKDIV<5:0> (ADCTRGMODE<17:16>) VREFSEL<2:0> AN5 VREFH VREFL TAD0-TAD4 ADCDIV<6:0> VREFL Τq (ADCxTIME<22:16>) DIFF0<1> (ADCIMCON1<1>) ADC0 T<sub>AD7</sub> ADCDIV<6:0> (ADCCON2<6:0>) AN4 ⊠ AN49 ⊠ N/C 10 N/C ⊠ SH4ALT<1:0> (ADCTRGMODE<25:24>) AN9 ADC4 VREFL DIFF4<1> (ADCIMCON1<1>) -⊠ AN5 -⊠ AN41 IVREF (AN43) - X AN42 IVTEMP (AN44) ADC7 CVD Capacitor AN10 ⊠-VREFL DIFFx<1> x = 5 to 44(ADCIMCONy<z>) v = 1 to 3.z = 1 to 31 (Odd numbers)ADCDATA0 FIFO ADCDATA44 Data Digital Filter SYSTEM BUS Interrupt/Event Digital Comparator Triggers, Turbo Channel, Scan Control Logic Capacitive Voltage Interrupt/Event Divider (CVD) Trigger Interrupt Status and Control Registers

TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                          | a             |       |                |       |       |       |       |      | Bit    | s      |      |      |      |      |      |      |      | s          |

|-----------------------------|--------------------------|---------------|-------|----------------|-------|-------|-------|-------|------|--------|--------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name         | Bit Range     | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

|                             | ADCDATA13                | 31:16         |       | DATA<31:16> 00 |       |       |       |       |      |        |        |      |      |      | 0000 |      |      |      |            |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B238                        | ADCDATA14                | 31:16         |       |                |       |       |       |       |      | DATA<  | 31:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B23C                        | ADCDATA15                | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B240                        | ADCDATA16                | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B244                        | ADCDATA17                | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B248                        | ADCDATA18                | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| D0 40                       | 1 DOD 1 T1 10(1)         | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B24C                        | ADCDATA19 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| DOFO                        | A DOD A TA CO(1)         | 15:0          |       |                |       |       |       |       |      | DATA ( |        |      |      |      |      |      |      |      | 0000       |

| B250                        | ADCDATA20 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| DOE 4                       | ADCDATA21 <sup>(1)</sup> | 15:0<br>31:16 |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| D254                        | ADCDATAZI ,              | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B258                        | ADCDATA22 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| DEGG                        | , LOOD, LINEZ            | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B25C                        | ADCDATA23 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| 5200                        | , 15 05, 11, 120         | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B260                        | ADCDATA24 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B264                        | ADCDATA25 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B268                        | ADCDATA26 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  | 31:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B26C                        | ADCDATA27 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  | 31:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B270                        | ADCDATA28 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  | 31:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B274                        | ADCDATA29 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  | 31:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

| B278                        | ADCDATA30 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

| B27C                        | ADCDATA31 <sup>(1)</sup> | 31:16         |       |                |       |       |       |       |      | DATA<  |        |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                |       |       |       |       |      | DATA<  | 15:0>  |      |      |      |      |      |      |      | 0000       |

1: 2: 3: Note

This bit or register is not available on 64-pin devices.

This bit or register is not available on 64-pin and 100-pin devices.

Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory-programmed DEVADCx Flash registers into the corresponding ADCxCFG registers.

#### REGISTER 28-25: ADCDATAX: ADC OUTPUT DATA REGISTER ('x' = 0 THROUGH 44)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|           | DATA<31:24>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16     | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8      | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|           |                   |                   |                   | DATA              | <7:0>             |                   |                  |                  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 DATA<31:0>: ADC Converted Data Output bits.

Note 1: The registers, ADCDATA19 through ADCDATA34, are not available on 64-pin devices.

- 2: The registers, ADCDATA35 through ADCDATA42, are not available on 64-pin and 100-pin devices.

- **3:** When an alternate input is used as the input source for a dedicated ADC module, the data output is still read from the Primary input Data Output Register.

- **4:** Reading the ADCDATAx register value after changing the FRACT bit converts the data into the format specified by FRACT bit.

#### REGISTER 29-18: CIRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 ('n' = 0-31)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

|              | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |

| 23.10        | SID<2:0>          |                   |                   | _                 | EXID              | — EID<17:16>      |                  |                  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15.6         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

|              |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-21 SID<10:0>: Standard Identifier bits

1 = Message address bit SIDx must be '1' to match filter

0 = Message address bit SIDx must be '0' to match filter

bit 20 Unimplemented: Read as '0'

bit 19 **EXID:** Extended Identifier Enable bits

1 = Match only messages with extended identifier addresses

0 = Match only messages with standard identifier addresses

bit 18 Unimplemented: Read as '0'

bit 17-0 **EID<17:0>:** Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

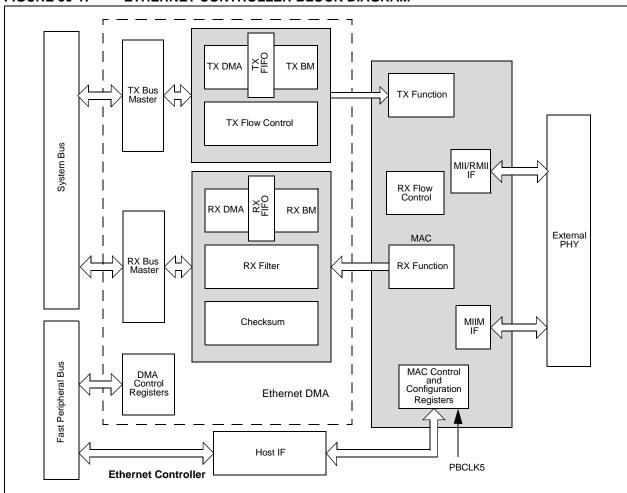

#### 30.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is

available from the Microchip web site

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

(www.microchip.com/PIC32).

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- · Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- · Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- Supports various hardware statistics counters

Figure 30-1 illustrates a block diagram of the Ethernet controller.

#### FIGURE 30-1: ETHERNET CONTROLLER BLOCK DIAGRAM

#### REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2,6)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- bit 5 **RXBUSY:** Receive Busy bit (3,6)

- 1 = RX logic is receiving data

- 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- **Note 1:** This bit is only used for RX operations.

- 2: This bit is only affected by TX operations.

- 3: This bit is only affected by RX operations.

- 4: This bit is affected by TX and RX operations.

- 5: This bit will be set when the ON bit (ETHCON1<15>) = 1.

- **6:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

# REGISTER 30-19: ETHMCOLFRM: ETHERNET CONTROLLER MULTIPLE COLLISION FRAMES STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | -                 | _                 | _                 | -                | _                |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 13.6         | MCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   | MCOLFRMCNT<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 MCOLFRMCNT<15:0>: Multiple Collision Frame Count bits

Increment count for frames that were successfully transmitted after there was more than one collision.

**Note 1:** This register is only used for TX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 30-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|------------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0                          | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |

| 31.24        |                              | _                 |                   | _                 | _                    | _                 | _                | _                |  |  |

| 23:16        | U-0                          | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |