Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | MIPS32® M-Class                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| Speed                     | 180MHz                                                                           |

| Connectivity              | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| lumber of I/O             | 120                                                                              |

| rogram Memory Size        | 2MB (2M x 8)                                                                     |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 512K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| ata Converters            | A/D 48x12b                                                                       |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 144-LQFP                                                                         |

| upplier Device Package    | 144-LQFP (20x20)                                                                 |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm144-e-pl |

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the following documents, browse the documentation section of the Microchip web site (www.microchip.com).

- Section 1. "Introduction" (DS60001127)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 22. "12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" (DS60001344)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

- Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183)

- Section 42. "Oscillators with Enhanced PLL" (DS60001250)

- Section 46. "Serial Quad Interface (SQI)" (DS60001244)

- Section 47. "External Bus Interface (EBI)" (DS60001245)

- Section 48. "Memory Organization and Permissions" (DS60001214)

- Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246)

- Section 50. "CPU for Devices with MIPS32® microAptiv™ and M-Class Cores" (DS60001192)

- Section 51. "Hi-Speed USB with On-The-Go (OTG)" (DS60001326)

- Section 52. "Flash Program Memory with Support for Live Update" (DS60001193)

### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This data sheet contains device-specific information for PIC32MZ EF devices.

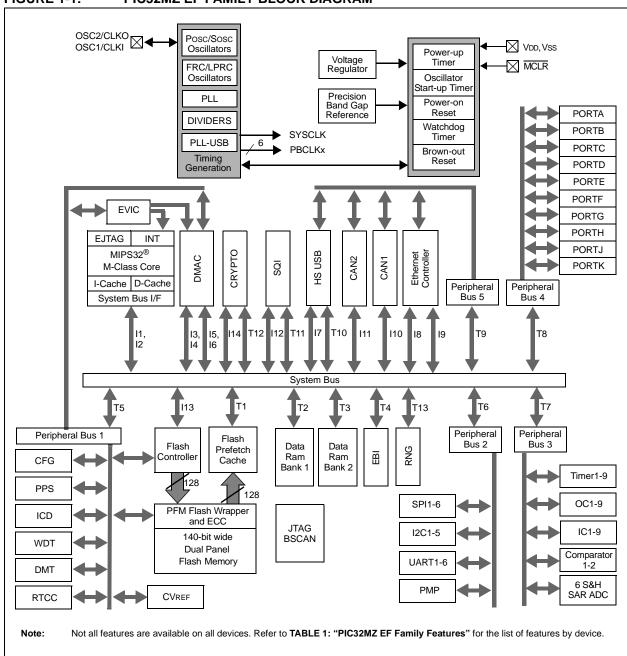

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

FIGURE 1-1: PIC32MZ EF FAMILY BLOCK DIAGRAM

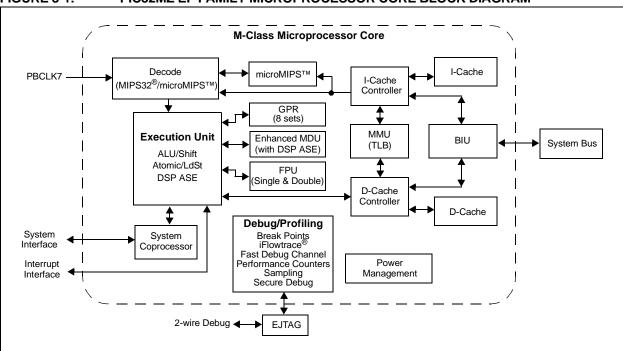

A block diagram of the PIC32MZ EF family processor core is shown in Figure 3-1.

FIGURE 3-1: PIC32MZ EF FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

## 8.2 Oscillator Control Registers

## TABLE 8-2: OSCILLATOR CONFIGURATION REGISTER MAP

| SS                          |                                 |           |                                                 |       |           |       |            |       |              | Bits    |           |      |         |       |           |        |            |       |                           |

|-----------------------------|---------------------------------|-----------|-------------------------------------------------|-------|-----------|-------|------------|-------|--------------|---------|-----------|------|---------|-------|-----------|--------|------------|-------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                           | 30/14 | 29/13     | 28/12 | 27/11      | 26/10 | 25/9         | 24/8    | 23/7      | 22/6 | 21/5    | 20/4  | 19/3      | 18/2   | 17/1       | 16/0  | All Resets <sup>(2)</sup> |

| 1200                        | OSCCON                          | 31:16     | _                                               | _     | _         | _     | _          |       | FRCDIV<2:0:  | >       | DRMEN     | _    | SLP2SPD | _     | _         |        | _          | _     | 0000                      |

| 1200                        | OSCCON                          | 15:0      | _                                               |       | COSC<2:0> |       | _          |       | NOSC<2:0>    |         | CLKLOCK   | _    | _       | SLPEN | CF        | ı      | SOSCEN     | OSWEN | xx0x                      |

| 1210                        | OSCTUN                          | 31:16     | _                                               | -     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1210                        | 0301014                         | 15:0      | _                                               | -     | _         | _     | _          | _     | _            | _       | _         | _    |         |       | TUN       | l<5:0> |            |       | 00xx                      |

| 1220                        | SPLLCON                         | 31:16     | PLLODIV<2:0> - PLLMULT<6:0>                     |       |           |       |            |       |              |         |           | 01xx |         |       |           |        |            |       |                           |

| 1220                        | 31 LLCON                        | 15:0      | _                                               | ı     | _         | 1     | _          |       | PLLIDIV<2:0: | >       | PLLICLK   | _    | _       | _     | _         | PL     | .LRANGE<2: | 0>    | 0x0x                      |

| 1280                        | REFO1CON                        | 31:16     | _                                               |       |           |       |            |       |              | ROI     | DIV<14:0> |      |         |       |           |        |            |       | 0000                      |

| 1200                        | KLIOTOON                        | 15:0      | ON                                              | ı     | SIDL      | OE    | RSLP       | _     | DIVSWEN      | ACTIVE  | 1         | _    | _       | _     |           | ROSE   | EL<3:0>    |       | 0000                      |

| 1290                        | REFO1TRIM                       | 31:16     |                                                 |       |           | R     | >0:8>MIRTC |       |              |         |           | _    | _       | _     | _         | 1      | _          | _     | 0000                      |

| 1230                        | INET OTTINIIVI                  | 15:0      | _                                               | ı     | _         | 1     | _          | _     | _            | _       | 1         | _    | _       | _     | _         | 1      | _          | _     | 0000                      |

| 1240                        | REFO2CON                        | 31:16     | _                                               |       |           |       |            |       |              | ROI     | DIV<14:0> |      |         |       |           |        |            |       | 0000                      |

| 12/10                       | KEI OZOON                       | 15:0      | 0 ON - SIDL OE RSLP - DIVSWEN ACTIVE ROSEL<3:0: |       |           |       |            |       |              | EL<3:0> |           | 0000 |         |       |           |        |            |       |                           |

| 12B0                        | REFO2TRIM                       | 31:16     |                                                 |       |           | R     | >0:8>MIRTC |       |              |         |           | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1200                        | IXEI OZITKIWI                   | 15:0      | _                                               | _     | _         | _     | _          |       | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1200                        | REFO3CON                        | 31:16     | _                                               |       |           |       |            |       |              | ROI     | DIV<14:0> |      |         |       |           |        |            |       | 0000                      |

| 1200                        | KEI OSOON                       | 15:0      | ON                                              | _     | SIDL      | OE    | RSLP       |       | DIVSWEN      | ACTIVE  | _         | _    | _       | _     |           | ROSE   | EL<3:0>    |       | 0000                      |

| 1200                        | REFO3TRIM                       | 31:16     |                                                 |       |           | R     | >0:8>MIRTC |       |              |         |           | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1200                        | TRET COTTAIN                    | 15:0      | _                                               | _     | _         | _     | _          |       | _            |         | _         |      | _       |       | _         | _      | _          | _     | 0000                      |

| 12E0                        | REFO4CON                        | 31:16     | _                                               |       |           |       |            |       |              |         | OIV<14:0> |      |         |       |           |        |            |       | 0000                      |

| 1220                        | KEI O IOON                      | 15:0      | ON                                              | _     | SIDL      | OE    | RSLP       |       | DIVSWEN      | ACTIVE  | _         |      | _       |       |           | ROSE   | EL<3:0>    |       | 0000                      |

| 12F0                        | REFO4TRIM                       | 31:16     |                                                 |       |           | R     | OTRIM<8:0> |       |              |         |           | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 0                           |                                 | 15:0      | _                                               | _     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1300                        | PB1DIV                          | 31:16     | _                                               | _     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| .000                        |                                 | 15:0      | _                                               | _     | _         | _     | PBDIVRDY   | _     | _            | _       | _         |      |         | P     | BDIV<6:0> |        |            |       | 8801                      |

| 1310                        | PB2DIV                          | 31:16     | _                                               | _     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| .0.0                        | . 525.1                         | 15:0      | ON                                              | _     | _         | _     | PBDIVRDY   | _     | _            | _       | _         |      |         | P     | BDIV<6:0> |        |            |       | 8801                      |

| 1320                        | PB3DIV                          | 31:16     | _                                               | _     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| .020                        | . 505.1                         | 15:0      | ON                                              | _     | _         | _     | PBDIVRDY   | _     | _            | _       | _         |      |         | P     | BDIV<6:0> |        |            |       | 8801                      |

| 1330                        | PB4DIV                          | 31:16     | _                                               | _     | _         | _     | _          | _     | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| 1000                        | , 5-51                          | 15:0      | ON                                              | -     | _         | _     | PBDIVRDY   | _     | _            | _       | _         |      |         | P     | BDIV<6:0> |        |            |       | 8801                      |

| 1340                        | PB5DIV                          | 31:16     | _                                               | _     | _         | _     | _          |       | _            | _       | _         | _    | _       | _     | _         | _      | _          | _     | 0000                      |

| .515                        | . 20011                         | 15:0      | ON                                              | _     | _         | —     | PBDIVRDY   | _     | _            | _       | _         |      |         | P     | BDIV<6:0> | •      |            |       | 8801                      |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

te 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

<sup>2:</sup> Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

### REGISTER 9-2: PRESTAT: PREFETCH MODULE STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | R/W-0, HS         | R/W-0, HS         | U-0              | U-0              |  |  |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | PFMDED            | PFMSEC            | _                | -                |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | _                 | -                 | -                 | -                 | _                 | -                 | 1                | 1                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 13.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |  |

| 7:0          | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |  |  |  |  |  |

| 7.0          |                   | PFMSECCNT<7:0>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

**Legend:** HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 Unimplemented: Read as '0'

bit 27 **PFMDED:** Flash Double-bit Error Detected (DED) Status bit

This bit is set in hardware and can only be cleared (i.e., set to '0') in software.

1 = A DED error has occurred

0 = A DED error has not occurred

bit 26 PFMSEC: Flash Single-bit Error Corrected (SEC) Status bit

1 = A SEC error occurred when PFMSECCNT<7:0> was equal to zero

0 = A SEC error has not occurred

bit 25-8 Unimplemented: Read as '0'

bit 7-0 **PFMSECCNT<7:0>:** Flash SEC Count bits

11111111 - 00000000 = SEC count

REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 | _                 | _                 |                   | _                 |                  | _                |

| 22,46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 |                   | _                 |                  | _                |

| 15.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | _                 | _                 | _                 | _                 |                   | -                 | -                | -                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 | _                 | _                 | _                | WINOPN           |

**Legend:** HC = Hardware Cleared HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BAD1: Bad STEP1<7:0> Value Detect bit

1 = Incorrect STEP1<7:0> value was detected 0 = Incorrect STEP1<7:0> value was not detected

bit 6 BAD2: Bad STEP2<7:0> Value Detect bit

1 = Incorrect STEP2<7:0> value was detected

0 = Incorrect STEP2<7:0> value was not detected

bit 5 DMTEVENT: Deadman Timer Event bit

1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment)

0 = Deadman timer even was not detected

bit 4-1 **Unimplemented:** Read as '0'

bit 0 WINOPN: Deadman Timer Clear Window bit

1 = Deadman timer clear window is open

0 = Deadman timer clear window is not open

REGISTER 19-2: SPIXCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 21.24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31:24        | _                    |                   | _                 |                   |                          |                   |                  | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    |                   | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15.6         | SPISGNEXT            | 1                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

|              | AUDEN <sup>(1)</sup> |                   | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extended

bit 14-13 Unimplemented: Read as '0'

bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun Generates Error Events

0 = Transmit Underrun Does Not Generates Error Events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error which stop SPI operation

bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error which stop SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

1 = Audio protocol is enabled

0 = Audio protocol is disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 Unimplemented: Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right Justified mode

01 = Left Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

### REGISTER 20-5: SQI1CLKCON: SQI CLOCK CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2           | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                         | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | -                 | -                 | _                 | -                           | _                | _                |  |  |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                       | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | CLKDIV<10:8> <sup>(1)</sup> |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                       | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CLKDIV<7:0>(1)    |                   |                   |                   |                   |                             |                  |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                         | R-0              | R/W-0            |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                           | STABLE           | EN               |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-19 Unimplemented: Read as '0'

bit 18-8 CLKDIV<10:0>: SQI Clock Tsqi Frequency Select bit(1)

10000000000 = Base clock TBC is divided by 2048

01000000000 = Base clock TBC is divided by 1024

00100000000 = Base clock TBC is divided by 512

00010000000 = Base clock TBC is divided by 256

00001000000 = Base clock TBC is divided by 128

Dase clock TBC is divided by 120

00000100000 = Base clock TBC is divided by 64 00000010000 = Base clock TBC is divided by 32

00000001000 = Base clock TBC is divided by 16

0000000100 = Base clock TBC is divided by 8

00000000010 = Base clock TBC is divided by 4

0000000001 = Base clock TBC is divided by 2

00000000000 = Base clock TBC

Setting these bits to '00000000000' specifies the highest frequency of the SQI clock.

bit 7-2 **Unimplemented:** Read as '0'

bit 1 STABLE: Tsqi Clock Stable Select bit

This bit is set to '1' when the SQI clock, TsQI, is stable after writing a '1' to the EN bit.

1 = Tsqi clock is stable

0 = Tsql clock is not stable

bit 0 EN: Tsqi Clock Enable Select bit

When clock oscillation is stable, the SQI module will set the STABLE bit to '1'.

- 1 = Enable the SQI clock (TsQI) (when clock oscillation is stable, the SQI module sets the STABLE bit to '1')

- 0 = Disable the SQI clock (TSQI) (the SQI module should stop its clock to enter a low power state); SFRs can still be accessed, as they use PBCLK5

**Note 1:** Refer to Table 37-34 in **37.0** "Electrical Characteristics" for the maximum clock frequency specifications.

### REGISTER 25-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 |                   |                   | _                 | -                 | _                | _                |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH01<3:0>      |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |  |  |

| 7:0          | U-0 U-0           |                   | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

|              | _                 | _                 | _                 | _                 | WDAY01<3:0>       |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

## 27.1 RNG Control Registers

## TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  |               |       |                               |       |       |          |       |        | Bits   | ;     |      |      |      |          |      |      |      |            |

|-----------------------------|------------------|---------------|-------|-------------------------------|-------|-------|----------|-------|--------|--------|-------|------|------|------|----------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                         | 29/13 | 28/12 | 27/11    | 26/10 | 25/9   | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16         |       |                               |       |       |          |       |        | ID<15: | .0>   |      |      |      |          |      |      |      | xxxx       |

| 0000                        | KNOVEK           | 15:0          |       | VERSION<7:0> REVISION<7:0> xx |       |       |          |       |        |        |       |      | xxxx |      |          |      |      |      |            |

| 6004                        | RNGCON           | 31:16         | _     | _                             | _     | _     | _        | _     | _      | _      | _     | _    | _    | _    | _        | _    | _    | _    | 0000       |

|                             |                  | 15:0          | _     | _                             | _     | LOAD  | TRNGMODE | CONT  | PRNGEN | TRNGEN |       |      |      | PLEN | N<7:0>   |      |      |      | 0064       |

| 6008                        | RNGPOLY1         | 31:16         |       |                               |       |       |          |       |        | POLY<3 | 1:0>  |      |      |      |          |      |      |      | FFFF       |

|                             |                  | 15:0          |       | 0000                          |       |       |          |       |        |        |       |      |      |      |          |      |      |      |            |

| 600C                        | RNGPOLY2         | 31:16         |       |                               |       |       |          |       |        | POLY<3 | 1:0>  |      |      |      |          |      |      |      | FFFF       |

|                             |                  | 15:0          |       |                               |       |       |          |       |        |        |       |      |      |      |          |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16         |       |                               |       |       |          |       |        | RNG<3  | 1:0>  |      |      |      |          |      |      |      | FFFF       |

|                             |                  | 15:0          |       |                               |       |       |          |       |        |        |       |      |      |      |          |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 31:16         |       |                               |       |       |          |       |        | RNG<3  | 1:0>  |      |      |      |          |      |      |      | FFFF       |

|                             |                  | 15:0          |       |                               |       |       |          |       |        |        |       |      |      |      |          |      |      |      | FFFF       |

| 6018                        | RNGSEED1         | 31:16         |       |                               |       |       |          |       |        | SEED<3 | 31:0> |      |      |      |          |      |      |      | 0000       |

|                             |                  | 15:0          |       |                               |       |       |          |       |        |        |       |      |      |      |          |      |      |      | 0000       |

| 601C                        | RNGSEED2         | 31:16         |       | SEED<31:0>                    |       |       |          |       |        |        |       |      |      |      |          |      |      |      |            |

| <u> </u>                    |                  | 15:0<br>31:16 |       |                               |       |       |          |       |        |        | _     |      |      |      | _        |      |      |      | 0000       |

| 6020                        | RNGCNT           |               |       | _                             | _     | _     | _        |       | _      | _      |       | _    | _    | _    |          | _    | _    | _    | 0000       |

| <u> </u>                    |                  | 15:0          | _     | _                             | _     |       |          |       | L -    | _      |       |      |      |      | RCNT<6:0 | >    |      |      | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 27-1: RNGVER: RANDOM NUMBER GENERATOR VERSION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        |                   |                   |                   | ID<15             | 5:8>              |                   |                  |                  |  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | ID<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | VERSION<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

|              |                   |                   |                   | REVISIO           | N<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 **ID<15:0>:** Block Identification bits bit 15-8 **VERSION<7:0>:** Block Version bits bit 7-0 **REVISION<7:0>:** Block Revision bits

REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2

| Bit Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 04-04     | R/W-0                 |

| 31:24     | DIFF31 <sup>(1)</sup> | SIGN31 <sup>(1)</sup> | DIFF30 <sup>(1)</sup> | SIGN30 <sup>(1)</sup> | DIFF29 <sup>(1)</sup> | SIGN29 <sup>(1)</sup> | DIFF28 <sup>(1)</sup> | SIGN28 <sup>(1)</sup> |

| 00.40     | R/W-0                 |

| 23:16     | DIFF27 <sup>(1)</sup> | SIGN27 <sup>(1)</sup> | DIFF26 <sup>(1)</sup> | SIGN26 <sup>(1)</sup> | DIFF25 <sup>(1)</sup> | SIGN25 <sup>(1)</sup> | DIFF24 <sup>(1)</sup> | SIGN24 <sup>(1)</sup> |

| 45.0      | R/W-0                 |

| 15:8      | DIFF23 <sup>(1)</sup> | SIGN23 <sup>(1)</sup> | DIFF22 <sup>(1)</sup> | SIGN22 <sup>(1)</sup> | DIFF21 <sup>(1)</sup> | SIGN21 <sup>(1)</sup> | DIFF20 <sup>(1)</sup> | SIGN20 <sup>(1)</sup> |

| 7.0       | R/W-0                 |

| 7:0       | DIFF19 <sup>(1)</sup> | SIGN19 <sup>(1)</sup> | DIFF18                | SIGN18                | DIFF17                | SIGN17                | DIFF16                | SIGN16                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 DIFF31: AN31 Mode bit<sup>(1)</sup>

1 = AN31 is using Differential mode

0 = AN31 is using Single-ended mode

bit 30 SIGN31: AN31 Signed Data Mode bit<sup>(1)</sup>

1 = AN31 is using Signed Data mode

0 = AN31 is using Unsigned Data mode

bit 29 **DIFF30:** AN30 Mode bit<sup>(1)</sup>

1 = AN30 is using Differential mode

0 = AN30 is using Single-ended mode

bit 28 SIGN30: AN30 Signed Data Mode bit<sup>(1)</sup>

1 = AN30 is using Signed Data mode

0 = AN30 is using Unsigned Data mode

bit 27 **DIFF29:** AN29 Mode bit<sup>(1)</sup>

1 = AN29 is using Differential mode

0 = AN29 is using Single-ended mode

bit 26 SIGN29: AN29 Signed Data Mode bit<sup>(1)</sup>

1 = AN29 is using Signed Data mode

0 = AN29 is using Unsigned Data mode

bit 25 DIFF28: AN28 Mode bit<sup>(1)</sup>

1 = AN28 is using Differential mode

0 = AN28 is using Single-ended mode

bit 24 SIGN28: AN28 Signed Data Mode bit<sup>(1)</sup>

1 = AN28 is using Signed Data mode

0 = AN28 is using Unsigned Data mode

bit 23 **DIFF27:** AN27 Mode bit<sup>(1)</sup>

1 = AN27 is using Differential mode

0 = AN27 is using Single-ended mode

bit 22 SIGN27: AN27 Signed Data Mode bit<sup>(1)</sup>

1 = AN27 is using Signed Data mode

0 = AN27 is using Unsigned Data mode

**Note 1:** This bit is not available on 64-pin devices.

### **REGISTER 28-34: ADCSYSCFG1: ADC SYSTEM CONFIGURATION REGISTER 1**

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04     | R-y               | R-y               | R-y               | R-y               | R-y               | R-y               | R-y              | R-y              |  |  |

| 31:24     |                   |                   |                   | AN<31:23>         |                   |                   |                  |                  |  |  |

| 22:40     | R-y               | R-y               | R-y               | R-y               | R-y               | R-1               | R-1              | R-1              |  |  |

| 23:16     | AN<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R-1               | R-1               | R-1               | R-1               | R-1               | R-1               | R-1              | R-1              |  |  |

| 15:8      | AN<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R-1               | R-1               | R-1               | R-1               | R-1               | R-1               | R-1              | R-1              |  |  |

| 7:0       |                   |                   |                   | AN<               | 7:0>              |                   |                  |                  |  |  |

Legend:y = POR value is determined by the specific deviceR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<math>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-0 AN<31:0>: ADC Analog Input bits

These bits reflect the system configuration and are updated during boot-up time. By reading these readonly bits, the user application can determine whether or not an analog input in the device is available. AN<31:0>: Reflects the presence or absence of the respective analog input (AN31-AN0).

#### **REGISTER 28-35: ADCSYSCFG2: ADC SYSTEM CONFIGURATION REGISTER 2**

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24     | _                 | _                 | _                 | _                 | _                 |                   | _                |                  |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16     | _                 | _                 | _                 | _                 | _                 | 1                 | _                | _                |  |

| 45.0      | U-0               | U-0               | U-0               | R-1               | R-1               | R-y               | R-y              | R-y              |  |

| 15:8      | _                 | _                 | _                 | AN<44:40>         |                   |                   |                  |                  |  |

| 7.0       | R-y               | R-y               | R-y               | R-y               | R-y               | R-y               | R-y              | R-y              |  |

| 7:0       |                   |                   |                   | AN<3              | 9:32>             |                   |                  |                  |  |

Legend:y = POR value is determined by the specific deviceR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is cleared<math>x = Bit is unknown

bit 31-13 **Unimplemented:** Read as '0' bit 12-0 **AN<44:32>:** ADC Analog Input bits

These bits reflect the system configuration and are updated during boot-up time. By reading these readonly bits, the user application can determine whether or not an analog input in the device is available. AN<63:32>: Reflects the presence or absence of the respective analog input (AN63-AN32).

## REGISTER 30-3: ETHTXST: ETHERNET CONTROLLER TX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        | TXSTADDR<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        |                   | TXSTADDR<23:16>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15.6         |                   | TXSTADDR<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |  |  |

| 7.0          |                   |                   | TXSTADE           | DR<7:2>           |                   |                   |                  | _                |  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-2 TXSTADDR<31:2>: Starting Address of First Transmit Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress.

This address must be 4-byte aligned (bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for TX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

## REGISTER 30-4: ETHRXST: ETHERNET CONTROLLER RX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | RXSTADDR<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        |                   | RXSTADDR<23:16>   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 13.6         | RXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |  |

| 7.0          |                   | RXSTADDR<7:2>     |                   |                   |                   |                   |                  |                  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-2 RXSTADDR<31:2>: Starting Address of First Receive Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress.

This address must be 4-byte aligned (bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

**Note 1:** This register is only used for RX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

## 32.1 Comparator Voltage Reference Control Registers

## TABLE 32-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       |                                 | a l       |       | Bits  |       |       |       |       |      |      |      |       | s    |       |      |      |      |      |           |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| ٥٥٥٥                      | CVRCON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _     | _    | _     | _    | _    | _    | _    | 0000      |

| UEUU                      | CVRCON                          | 15:0      | ON    | _     | -     | _     | _     | _     | _    | 1    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

REGISTER 34-7: CFGCON: CONFIGURATION CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0       |

|--------------|--------------------|-------------------|-----------------------|------------------------|-----------------------|-------------------|-----------------------|------------------------|

| 04:04        | U-0                | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 31:24        | _                  | _                 | _                     | _                      | _                     | _                 | DMAPRI <sup>(1)</sup> | CPUPRI <sup>(1)</sup>  |

| 22.40        | U-0                | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 23:16        | _                  | _                 | _                     | _                      | _                     | _                 | ICACLK <sup>(1)</sup> | OCACLK <sup>(1)</sup>  |

| 45.0         | U-0                | U-0               | R/W-0                 | R/W-0                  | R/W-0                 | U-0               | U-0                   | R/W-0                  |

| 15:8         | _                  | _                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | PGLOCK <sup>(1)</sup> | 1                 | _                     | USBSSEN <sup>(1)</sup> |

| 7.0          | R/W-0              | U-0               | R/W-1                 | R/W-1                  | R/W-1                 | R/W-0             | U-0                   | R/W-1                  |

| 7:0          | /:0 IOANCPEN — ECC |                   | ECCC                  | ON<1:0>                | JTAGEN                | TROEN             | _                     | TDOEN                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25 DMAPRI: DMA Read and DMA Write Arbitration Priority to SRAM bit<sup>(1)</sup>

1 = DMA gets High Priority access to SRAM

0 = DMA uses Least Recently Serviced Arbitration (same as other initiators)

bit 24 **CPUPRI:** CPU Arbitration Priority to SRAM When Servicing an Interrupt bit<sup>(1)</sup>

1 = CPU gets High Priority access to SRAM

0 = CPU uses Least Recently Serviced Arbitration (same as other initiators)

bit 23-18 Unimplemented: Read as '0'

bit 17 ICACLK: Input Capture Alternate Clock Selection bit (1)

1 = Input Capture modules use an alternative Timer pair as their timebase clock

0 = All Input Capture modules use Timer2/3 as their timebase clock

bit 16 OCACLK: Output Compare Alternate Clock Selection bit (1)

1 = Output Compare modules use an alternative Timer pair as their timebase clock

0 = All Output Compare modules use Timer2/3 as their timebase clock

bit 15-14 Unimplemented: Read as '0'

bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

1 = Peripheral Pin Select is locked. Writes to PPS registers are not allowed

0 = Peripheral Pin Select is not locked. Writes to PPS registers are allowed

bit 12 **PMDLOCK:** Peripheral Module Disable bit<sup>(1)</sup>

1 = Peripheral module is locked. Writes to PMD registers are not allowed

0 = Peripheral module is not locked. Writes to PMD registers are allowed

bit 11 **PGLOCK:** Permission Group Lock bit<sup>(1)</sup>

1 = Permission Group registers are locked. Writes to PG registers are not allowed

0 = Permission Group registers are not locked. Writes to PG registers are allowed

bit 10-9 Unimplemented: Read as '0'

bit 8 USBSSEN: USB Suspend Sleep Enable bit (1)

Enables features for USB PHY clock shutdown in Sleep mode.

1 = USB PHY clock is shut down when Sleep mode is active

0 = USB PHY clock continues to run when Sleep is active

Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

# 37.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MZ EF device AC characteristics and timing parameters.

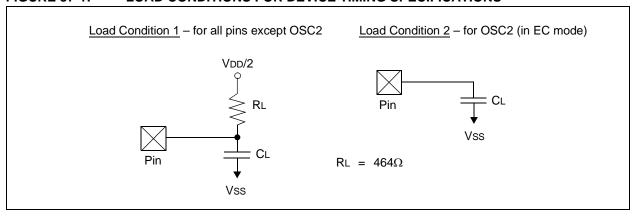

FIGURE 37-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

**TABLE 37-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS**

| AC CHARACTERISTICS |        |                                          |      | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                          |  |  |

|--------------------|--------|------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                          | Min. | Typical <sup>(1)</sup>                                                                                                                                                                                                                           | Max. | Units | Conditions               |  |  |

| DO56               | CL     | All I/O pins (except pins used as CxOUT) | _    | _                                                                                                                                                                                                                                                | 50   | pF    | EC mode for OSC2         |  |  |

| DO58               | Св     | SCLx, SDAx                               | _    | _                                                                                                                                                                                                                                                | 400  | pF    | In I <sup>2</sup> C mode |  |  |

| DO59               | Csqı   | All SQI pins                             | _    | _                                                                                                                                                                                                                                                | 10   | pF    | _                        |  |  |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE 38-3: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| ABLE 30-3. DO CHARACTERIOTICO: IDEE CORRERT (IDEE) |                                                                |                        |                                                                                                                                                     |                  |  |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| DC CHARACTERISTICS                                 |                                                                |                        | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                  |  |  |  |  |  |

| Parameter No.                                      | Typical <sup>(2)</sup>                                         | Maximum <sup>(4)</sup> | Units Conditions                                                                                                                                    |                  |  |  |  |  |  |

| Idle Current                                       | Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |                                                                                                                                                     |                  |  |  |  |  |  |

| EDC30a                                             | 7                                                              | 52                     | mA                                                                                                                                                  | 4 MHz (Note 3)   |  |  |  |  |  |

| EDC31a                                             | 8                                                              | 56                     | mA                                                                                                                                                  | 10 MHz           |  |  |  |  |  |

| EDC32a                                             | 13                                                             | 66                     | mA                                                                                                                                                  | 60 MHz (Note 3)  |  |  |  |  |  |

| EDC33a                                             | 21                                                             | 86                     | mA                                                                                                                                                  | 130 MHz (Note 3) |  |  |  |  |  |

| EDC34                                              | 26                                                             | 96                     | mA                                                                                                                                                  | 180 MHz (Note 3) |  |  |  |  |  |

- **Note 1:** The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC+PLL with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:128 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** Data in the "Maximum" column is at 3.3V, +125°C at specified operating frequency. Parameters are for design guidance only and are not tested.

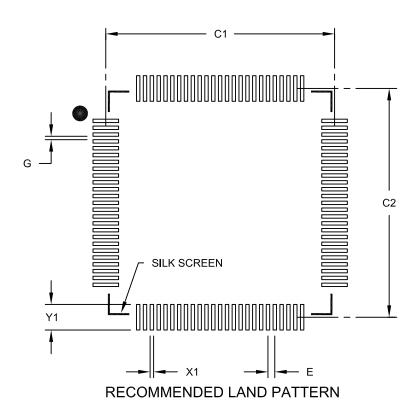

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |          |       |      |  |  |

|---------------------------|-------------|----------|-------|------|--|--|

| Dimension                 | MIN         | NOM      | MAX   |      |  |  |

| Contact Pitch             | E           | 0.40 BSC |       |      |  |  |

| Contact Pad Spacing       | C1          |          | 13.40 |      |  |  |

| Contact Pad Spacing       | C2          |          | 13.40 |      |  |  |

| Contact Pad Width (X100)  | X1          |          |       | 0.20 |  |  |

| Contact Pad Length (X100) | Y1          |          |       | 1.50 |  |  |

| Distance Between Pads     | G           | 0.20     |       |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

TABLE A-3: ADC DIFFERENCES (CONTINUED)

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                            | PIC32MZ EF Feature                                                                                                                                                                                               |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                       | ger Source                                                                                                                                                                                                       |  |  |  |  |  |  |

| On PIC32MX devices, there are four sources that can trigger a                                                                                                         | On PIC32MZ EF devices, the list of sources for triggering a scan                                                                                                                                                 |  |  |  |  |  |  |

| scan conversion in the ADC module: Auto, Timer3, INT0, and clearing the SAMP bit.                                                                                     | conversion has been expanded to include the comparators, Output Compare, and two additional Timers. In addition, trigger sources can be simulated by setting the RQCNVRT (ADCCON3<8>) bit.                       |  |  |  |  |  |  |

| SSRC<2:0> (AD1CON1<7:5>)<br>111 = Auto convert                                                                                                                        | STRGSRC<4:0> (ADCCON1<20:16>) 11111 = Reserved                                                                                                                                                                   |  |  |  |  |  |  |

| 110 = Reserved                                                                                                                                                        | •                                                                                                                                                                                                                |  |  |  |  |  |  |

| 101 = Reserved                                                                                                                                                        | •                                                                                                                                                                                                                |  |  |  |  |  |  |

| 100 = Reserved<br>011 = Reserved                                                                                                                                      | 01101 = Reserved                                                                                                                                                                                                 |  |  |  |  |  |  |

| 010 = Timer3 period match                                                                                                                                             | 01100 = Comparator 2 COUT                                                                                                                                                                                        |  |  |  |  |  |  |

| 001 = Active transition on INT0 pin                                                                                                                                   | 01011 = Comparator 1 COUT                                                                                                                                                                                        |  |  |  |  |  |  |

| 000 = Clearing SAMP bit                                                                                                                                               | 01010 = OCMP5<br>01001 = OCMP3                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                                                                                                                                       | 01000 = OCMP1                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                       | 00111 = TMR5 match                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                                                                                                                       | 00110 = TMR3 match                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                                                                                                                       | 00101 = TMR1 match                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                                                                                                                       | 00100 = INTO                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                       | 00011 = Reserved<br>00010 = Global level software trigger (GLSWTRG)                                                                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                       | 00001 = Global software trigger (GSWTRG)                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                                                                                                                       | 00000 = No trigger                                                                                                                                                                                               |  |  |  |  |  |  |

| Output Format                                                                                                                                                         |                                                                                                                                                                                                                  |  |  |  |  |  |  |

| On PIC32MX devices, the output format was decided for all ADC                                                                                                         | On PIC32MZ EF devices, the FRACT bit determines whether                                                                                                                                                          |  |  |  |  |  |  |

| channels based on the setting of the FORM<2:0> bits.                                                                                                                  | fractional or integer format is used. Then, each input can have its own setting for input (differential or single-ended) and sign (signed or unsigned) using the DIFFx and SIGNx bits in the ADCIMODx registers. |  |  |  |  |  |  |