Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |  |

|----------------------------|---------------------------------------------------------------------|--|

| Product Status             | Obsolete                                                            |  |

| Core Processor             | Coldfire V2                                                         |  |

| Core Size                  | 32-Bit Single-Core                                                  |  |

| Speed                      | 66MHz                                                               |  |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB           |  |

| Peripherals                | DMA, WDT                                                            |  |

| Number of I/O              | 32                                                                  |  |

| Program Memory Size        | 16KB (4K x 32)                                                      |  |

| Program Memory Type        | ROM                                                                 |  |

| EEPROM Size                | -                                                                   |  |

| RAM Size                   | 1K x 32                                                             |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |  |

| Data Converters            | -                                                                   |  |

| Oscillator Type            | External                                                            |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                     |  |

| Mounting Type              | Surface Mount                                                       |  |

| Package / Case             | 196-LBGA                                                            |  |

| Supplier Device Package    | 196-LBGA (15x15)                                                    |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf5272vf66 |  |

# **Table of Contents (Continued)**

| Parag<br>Num | graph<br>ber Title                            | Page<br>Number |

|--------------|-----------------------------------------------|----------------|

|              | 16.5.5 Bus Operation                          | 16-29          |

|              | 16.5.5.1 Read Cycles                          | 16-29          |

|              | 16.5.5.2 Write Cycles                         | 16-29          |

|              | 16.5.5.3 Interrupt Acknowledge Cycles         | 16-29          |

|              | 16.5.6 Programming                            | 16-30          |

|              | 16.5.6.1 UART Module Initialization Sequence  | 16-30          |

|              | Chapter 17                                    |                |

|              | General Purpose I/O Module                    |                |

| 17.1         | Overview                                      |                |

|              | Port Control Registers                        |                |

|              | 17.2.1 Port A Control Register (PACNT)        |                |

|              | 17.2.2 Port B Control Register (PBCNT)        |                |

|              | 17.2.3 Port C Control Register                |                |

|              | 17.2.4 Port D Control Register (PDCNT)        |                |

|              | Data Direction Registers                      |                |

|              | 17.3.1 Fort A Data Direction Register (PADDR) |                |

|              | 17.3.3 Port C Data Direction Register (PCDDR) |                |

|              | Port Data Registers                           |                |

|              | 17.4.1 Port Data Register (PxDAT)             |                |

|              | Chapter 18                                    |                |

|              | Pulse-Width Modulation (PWM) Module           |                |

| 18.1         | Overview                                      |                |

| 18.2         | PWM Operation                                 |                |

| 18.3         | PWM Programming Model                         |                |

|              | 18.3.1 PWM Control Register (PWCRn)           |                |

|              | 18.3.2 PWM Width Register (PWWDn)             | 18-4           |

|              | Chapter 19                                    |                |

|              | Signal Descriptions                           |                |

| 19.1         | MCF5272 Block Diagram with Signal Interfaces  |                |

| 19.2         | Signal List                                   |                |

| 19.3         | Address Bus (A[22:0]/SDA[13:0])               |                |

| 19.4         | Data Bus (D[31:0])                            |                |

|              | 19.4.1 Dynamic Data Bus Sizing                |                |

| 19.5         | Chip Selects (CS7/SDCS, CS[6:0])              |                |

| 19.6         | Bus Control Signals                           |                |

|              | 19.6.1 Output Enable/Read (OE/RD)             | 19-20          |

|              |                                               |                |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

Freescale Semiconductor

# **List of Tables (Continued)**

| Table<br>Numbe | r Title                                                    | Page<br>Number |

|----------------|------------------------------------------------------------|----------------|

|                |                                                            | Number         |

| 19-9           | MCF5272 CS0 Memory                                         |                |

|                | th Selection19-38                                          |                |

| 19-10          | MCF5272 High Impedance                                     |                |

|                | election19-38                                              |                |

| 20-1           | ColdFire Bus Signal Summary                                | 20-1           |

| 20-2           | Chip Select Memory                                         |                |

|                | Decoding Priority20-4                                      |                |

| 20-3           | Byte Strobe Operation for 32-Bit Data Bus                  | 20-6           |

| 20-4           | Byte Strobe Operation                                      |                |

|                | t Data Bus—SRAM Cycles20-6                                 |                |

| 20-5           | Byte Strobe Operation                                      |                |

|                | t Data Bus—SDRAM Cycles20-6                                |                |

| 20-6           | Data Bus Requirement for Read/Write Cycles                 |                |

| 20-7           | External Bus Interface Codes for CSBRs                     |                |

| 21-1           | JTAG Signals                                               |                |

| 21-2           | Instructions                                               |                |

| 23-1           | Maximum Supply, Input Voltage and Storage Temperature      |                |

| 23-2           | Operating Temperature                                      |                |

| 23-3           | Thermal Resistance                                         |                |

| 23-4           | DC Electrical Specifications                               |                |

| 23-5           | I/O Driver Capability                                      |                |

| 23-6           | Clock Input and Output Timing Specifications               |                |

| 23-7           | Processor Bus Input Timing Specifications                  |                |

| 23-8           | Processor Bus Output Timing Specifications                 |                |

| 23-9           | Debug AC Timing Specification                              |                |

| 23-10          | SDRAM Interface Timing Specifications                      |                |

| 23-11          | MII Receive Signal Timing                                  |                |

| 23-12          | MII Transmit Signal Timing                                 |                |

| 23-13          | MII Async Inputs Signal Timing                             |                |

| 23-14          | MII Serial Management Channel Timing                       |                |

| 23-15          | Timer Module AC Timing Specifications                      |                |

| 23-16          | UART Modules AC Timing Specifications                      |                |

| 23-17          | IDL Master Mode Timing, PLIC Ports 1, 2, and 3             |                |

| 23-18          | IDL Slave Mode Timing, PLIC Ports 0–3                      |                |

| 23-19          | GCI Slave Mode Timing, PLIC Ports 0–3                      |                |

| 23-20          | GCI Master Mode Timing, PLIC PORTs 1, 2, 3                 |                |

| 23-21          | General-Purpose I/O Port AC Timing Specifications          |                |

| 23-22          | USB Interface AC Timing Specifications                     |                |

| 23-23          | IEEE 1149.1 (JTAG) AC Timing Specifications                | 23-30          |

| 23-24          | QSPI Modules AC Timing Specifications                      |                |

| 23-25          | PWM Modules AC Timing Specifications                       |                |

| A-1            | On-Chip Module Base Address Offsets from MBAR              |                |

| A-2            | CPU Space Registers Memory Map                             |                |

| A-3            | On-Chip Peripherals and Configuration Registers Memory Map | A-2            |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

#### **ColdFire Core**

## Table 2-21. MCF5272 Exceptions (continued)

| Exception              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt<br>Exception | Interrupt exception processing, with interrupt recognition and vector fetching, includes uninitialized and spurious interrupts as well as those where the requesting device supplies the 8-bit interrupt vector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Reset<br>Exception     | Asserting the reset input signal (RSTI) causes a reset exception. Reset has the highest exception priority; it provides for system initialization and recovery from catastrophic failure. When assertion of RSTI is recognized, current processing is aborted and cannot be recovered. The reset exception places the processor in supervisor mode by setting SR[S] and disables tracing by clearing SR[T]. This exception also clears SR[M] and sets the processor's interrupt priority mask in the SR to the highest level (level 7). Next, the VBR is initialized to 0x0000_0000. Configuration registers controlling the operation of all processor-local memories (cache and RAM modules on the MCF5272) are invalidated, disabling the memories.  Note: Other implementation-specific supervisor registers are also affected. Refer to each of the modules in this manual for details on these registers. |

|                        | If the processor is not halted and it has ownership of the bus, it initiates the reset exception by performing two longword read bus cycles. The longword at address 0 is loaded into the stack pointer and the longword at address 4 is loaded into the PC. After the initial instruction is fetched from memory, program execution begins at the address in the PC. If an access error or address error occurs before the first instruction executes, the processor enters the fault-on-fault halted state.                                                                                                                                                                                                                                                                                                                                                                                                   |

If a ColdFire processor encounters any type of fault during the exception processing of another fault, the processor immediately halts execution with the catastrophic fault-on-fault condition. A reset is required to force the processor to exit this halted state.

2-30 Freescale Semiconductor

# 3.1.3 MAC Instruction Set Summary

The MAC unit supports the integer multiply operations defined by the baseline ColdFire architecture and the new multiply-accumulate instructions. Table 3-1 summarizes the MAC unit instruction set.

| Instruction                   | Mnemonic                          | Description                                                                                                                          |

|-------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Multiply Signed               | MULS <ea>y,Dx</ea>                | Multiplies two signed operands yielding a signed result                                                                              |

| Multiply Unsigned             | MULU <ea>y,Dx</ea>                | Multiplies two unsigned operands yielding an unsigned result                                                                         |

| Multiply Accumulate           | MAC Ry,RxSF<br>MSAC Ry,RxSF       | Multiplies two operands, then adds or subtracts the product to/from the accumulator                                                  |

| Multiply Accumulate with Load | MAC Ry,RxSF,Rw<br>MSAC Ry,RxSF,Rw | Multiplies two operands, then adds or subtracts the product to/from the accumulator while loading a register with the memory operand |

| Load Accumulator              | MOV.L {Ry,#imm},ACC               | Loads the accumulator with a 32-bit operand                                                                                          |

| Store Accumulator             | MOV.L ACC,Rx                      | Writes the contents of the accumulator to a register                                                                                 |

| Load MACSR                    | MOV.L {Ry,#imm},MACSR             | Writes a value to the MACSR                                                                                                          |

| Store MACSR                   | MOV.L MACSR,Rx                    | Writes the contents of MACSR to a register                                                                                           |

| Store MACSR to CCR            | MOV.L MACSR,CCR                   | Writes the contents of MACSR to the processor's CCR register                                                                         |

| Load MASK                     | MOV.L {Ry,#imm},MASK              | Writes a value to MASK                                                                                                               |

| Store MASK                    | MOV.L MASK,Rx                     | Writes the contents of MASK to a register                                                                                            |

**Table 3-1. MAC Instruction Summary**

# 3.1.4 Data Representation

The MAC unit supports three basic operand types:

- Two's complement signed integer: In this format, an N-bit operand represents a number within the range  $-2^{(N-1)} \le \text{operand} \le 2^{(N-1)} 1$ . The binary point is to the right of the least significant bit.

- Two's complement unsigned integer: In this format, an N-bit operand represents a number within the range  $0 \le \text{operand} \le 2^N$  1. The binary point is to the right of the least significant bit.

- Two's complement, signed fractional: In an N-bit number, the first bit is the sign bit. The remaining bits signify the first N-1 bits after the binary point. Given an N-bit number,  $a_{N-1}a_{N-2}a_{N-3}...$   $a_2a_1a_0$ , its value is given by the following formula:

$$+\sum_{i=0}^{N-2} 2^{(i+1-N)} \cdot ai$$

This format can represent numbers in the range  $-1 \le operand \le 1 - 2^{(N-1)}$ .

For words and longwords, the greatest negative number that can be represented is -1, whose internal representation is 0x8000 and  $0x0x8000\_0000$ , respectively. The most positive word is 0x7FFF or  $(1 - 2^{-15})$ ; the most positive longword is  $0x7FFF\_FFFF$  or  $(1 - 2^{-31})$ .

# 3.2 MAC Instruction Execution Timings

For information on MAC instruction execution timings, refer to Section 2.7, "Instruction Timing."

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

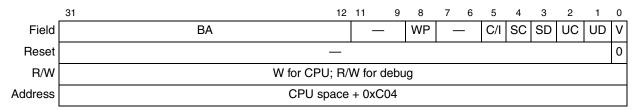

## 4.3.2.1 SRAM Base Address Register (RAMBAR)

RAMBAR determines the base address location of the internal SRAM module, as well as the definition of the types of accesses allowed for it.

- RAMBAR is a 32-bit write-only supervisor control register. It is accessed in the CPU address space via the MOVEC instruction with an Rc encoding of 0xC04. RAMBAR can be read or written in background debug mode (BDM). At system reset, the V bit is cleared and the remaining bits are uninitialized. To access the SRAM module, RAMBAR must be written with the appropriate base address after system reset.

- The SRAM base address register (RAMBAR) can be accessed only in supervisor mode using the MOVEC instruction with an Rc value of 0xC04.

Figure 4-1. SRAM Base Address Register (RAMBAR)

RAMBAR fields are described in Table 4-2.

**Table 4-2. RAMBAR Field Description**

| Bits  | Name                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–12 | ВА                           | Base address. SRAM module base address. The SRAM module occupies a 4-Kbyte space defined by BA. SRAM can reside on any 4-Kbyte boundary in the 4-Gbyte address space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11–9  | _                            | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8     | WP                           | Write protect. Controls read/write properties of the SRAM.  O Allows read and write accesses to the SRAM module.  Allows only read accesses to the SRAM module. Any attempted write reference generates an access error exception to the ColdFire processor core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7–6   | _                            | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5–1   | C/I,<br>SC,<br>SD,<br>UC, UD | Address space masks (ASn). These fields allow certain types of accesses to be masked, or inhibited from accessing the SRAM module. These bits are useful for power management as described in Section 4.3.2.3, "Programming RAMBAR for Power Management." In particular, C/I is typically set. The address space mask bits are follows:  C/I = CPU space/interrupt acknowledge cycle mask. Note that C/I must be set if BA = 0.  SC = Supervisor code address space mask SD = Supervisor data address space mask UC = User code address space mask UD = User data address space mask For each ASn bit:  O An access to the SRAM module can occur for this address space  1 Disable this address space from the SRAM module. References to this address space cannot access the SRAM module and are processed like other non-SRAM references. |

| 0     | V                            | Valid. Enables/disables the SRAM module. V is cleared at reset.  0 RAMBAR contents are not valid.  1 RAMBAR contents are valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

Freescale Semiconductor 4-3

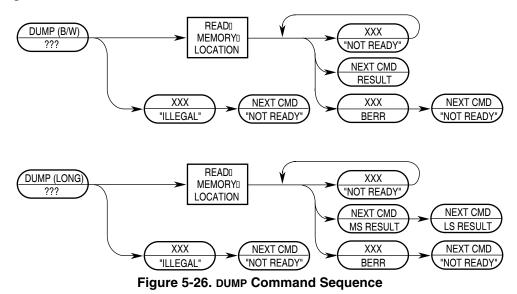

## 5.5.3.3.5 Dump Memory Block (DUMP)

DUMP is used with the READ command to access large blocks of memory. An initial READ is executed to set up the starting address of the block and to retrieve the first result. If an initial READ is not executed before the first DUMP, an illegal command response is returned. The DUMP command retrieves subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent DUMP commands use this address, perform the memory read, increment it by the current operand size, and store the updated address in the temporary register.

#### NOTE

DUMP does not check for a valid address; it is a valid command only when preceded by NOP, READ, or another DUMP command. Otherwise, an illegal command response is returned. NOP can be used for intercommand padding without corrupting the address pointer.

The size field is examined each time a DUMP command is processed, allowing the operand size to be dynamically altered.

## Command/Result Formats:

|          |         | 15      |          |  | 12  | 11  |         |     | 8        | 7    | 4   | 1   | 3 |  | 0 |

|----------|---------|---------|----------|--|-----|-----|---------|-----|----------|------|-----|-----|---|--|---|

| Byte     | Command | 0x1     |          |  |     | 0xD |         |     | 0x0      |      |     | 0x0 |   |  |   |

|          | Result  | x x x x |          |  | Χ   | Χ   | Х       | Χ   | D[7:0]   |      |     |     |   |  |   |

| Word     | Command | 0x1     |          |  | 0xD |     |         | 0x4 |          |      | 0x0 |     |   |  |   |

|          | Result  |         |          |  |     |     | D[15:0] |     |          |      |     |     |   |  |   |

| Longword | Command | 0x1     |          |  |     | 0xD |         |     | 0x8      |      |     | 0x0 |   |  |   |

|          | Result  |         | <u>.</u> |  |     |     |         |     | D[31:16] |      |     |     |   |  |   |

|          |         |         | D[       |  |     |     |         |     | D[1      | 5:0] |     |     |   |  |   |

Figure 5-25. DUMP Command/Result Formats

## Command Sequence:

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

Freescale Semiconductor 5-27

## 11.7 Differences between MCF5272 FEC and MPC860T FEC

The MCF5272 features the same FEC as the MPC860T with a few differences. The following list pertains to the MCF5272.

- Limited throughput full-duplex 100 Mbps operation. External bus use is the limiting factor.

- Only big-endian mode is supported for buffer descriptors and buffers.

- Separate interrupt vectors for Rx, Tx and non-time critical interrupts

- Interrupt priority is set in the interrupt controller

- The formula for calculating E MDC clock frequency differs between MCF5272 and MPC860T:

- MCF5272: E\_MDC\_FREQUENCY= system frequency / (4 \* MII\_SPEED)

- MPC860T: E\_MDC\_FREQUENCY= system frequency / (2 \* MII\_SPEED)

#### NOTE

MCF5272 ethernet controller signal names are generally identical to those used in the MPC860T, except for a prefix of 'E\_'. For example, MDC in the MPC860T corresponds to E\_MDC in the MCF5272.

Freescale Semiconductor 11-39

#### **Universal Serial Bus (USB)**

packet size and the EPDP*n* registers are updated in real-time, not just at the end of a packet as with other endpoint types. If the packet size is larger than the FIFO size, the FIFO level interrupt must be used.

Isochronous packets are guaranteed to occur once per USB frame. The SOF and ASOF interrupts are provided in order for the user to synchronize the data flow with the USB. The SOF interrupt occurs every 1 ms provided the USB is active. The ASOF interrupt is generated if the USB module fails to detect a SOF packet within the set timeout period.

It is strongly recommended that interrupts be used rather than polling for isochronous endpoints as isochronous endpoints do not have any error detection or flow-control mechanisms. If the packet size is larger than the FIFO size, using interrupts is required.

## 12.4.4.2.1 IN Endpoints

The user should write one packet of data to the IN FIFO per frame. If an ASOF interrupt occurs, the user may wish to insert additional data in the data stream if the data for the frame is lost. The following example demonstrates how to handle an isochronous IN packet each frame with a packet size larger than the FIFO size:

- 1. Wait for the SOF interrupt for synchronization.

- 2. Write data to the FIFO until filled.

- 3. Wait for FIFO\_LVL interrupt.

- 4. Read EPnDP to determine the number of bytes that can be written to the FIFO.

- 5. Write data to the FIFO to fill it or until all of the data for the packet has been written.

- 6. Repeat steps 3–5 until the entire packet has been written to the FIFO.

## **12.4.4.2.2 OUT Endpoints**

The user should read one packet of data from the OUT FIFO per frame. If an ASOF interrupt occurs, the user may wish to discard the data for the frame. The following example demonstrates how to handle an isochronous OUT packet each frame with a packet size larger than the FIFO size:

- 1. Wait for SOF interrupt for synchronization. The user may want to track that a packet is received for every frame.

- 2. Wait for the FIFO\_LVL interrupt.

- 3. Read EPDPn to determine number of bytes in the FIFO.

- 4. Read data the indicated number of bytes from the FIFO.

- 5. Repeat steps 2–4 until entire packet is received.

- 6. Wait for EOP or SOF interrupt and read any remaining data in the FIFO.

- 7. An EOT interrupt indicates a short or zero-length packet.

# 12.4.5 Class- and Vendor-Specific Request Operation

The class- and vendor-specific requests are specific to a particular device class or vendor, and are not processed by the USB request processor. When the USB module receives a class or vendor request, the parameters for the request are written to the DRR1 and DRR2 registers and the user is notified of the

12-34 Freescale Semiconductor

#### Physical Layer Interface Controller (PLIC)

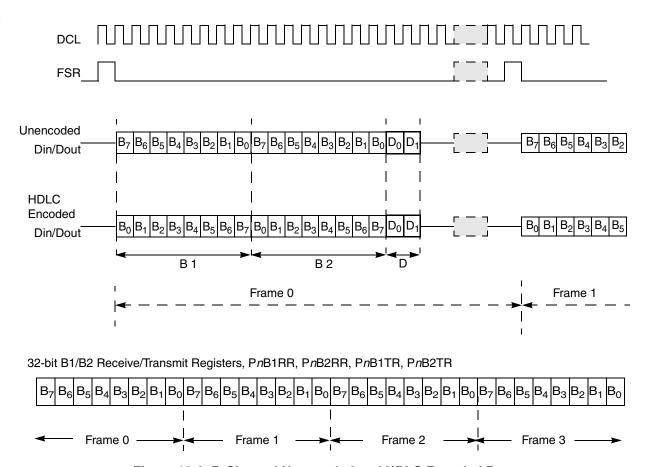

Figure 13-6. B-Channel Unencoded and HDLC Encoded Data

### 13.2.3.2 B-Channel HDLC Encoded Data

When the incoming B channels contain HDLC encoded data they are presented on the physical line least significant bit (lsb) first. The Soft HDLC expects the first bit received to be aligned in the lsb position of a byte, with the last bit received aligned in the msb position.

Because the presentation of HDLC encoded data on the physical interface is lsb (least significant bit) first for B1 and B2 the lsb is right-aligned in the transmit and receive shift register, that is, the first bit of the B-channel received is aligned in the lsb position through to the last received bit of a byte that is aligned in the msb position.

The ordering of the bytes over four frames within the longword register is as for unencoded data; that is, the first frame is aligned in the MSB through to the fourth frame, which is aligned in the LSB position. See Figure 13-6.

### 13.2.3.3 D-Channel HDLC Encoded Data

When the incoming D channels contain HDLC-encoded data, they are presented on the physical line lsb first. The Soft HDLC expects the first bit received to be aligned in the lsb position of a byte, with the last bit received aligned in the msb position.

13-6 Freescale Semiconductor

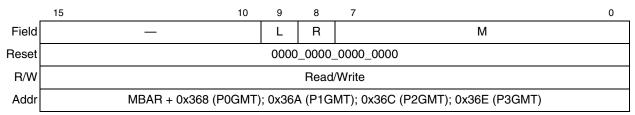

# 13.5.13 GCI Monitor Channel Transmit Registers (P0GMT-P3GMT)

All bits in these registers are read/write and are cleared on hardware or software reset.

The PnGMT registers are 16 bit register containing the control and monitor channel bits to be transmitted for each of the four ports on the MCF5272.

A byte of monitor channel data to be transmitted on a certain port is put into an associated register using the format shown in Figure 13-25. A maskable interrupt is generated when this byte of data has been successfully transmitted.

Figure 13-25. GCI Monitor Channel Transmit Registers (P0GMT–P3GMT)

## Table 13-8. POGMT-P3GMT Field Descriptions

| Bits  | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–10 | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9     | Ļ    | Last.  Default reset value  Set by the CPU. Indicates to the monitor channel controller to transmit the end of message signal on the E bit. Both PnGMT[L] and PnGMT[R] must be set for the monitor channel controller to send the end of message signal. PnGMT[M7:0] are ignored and 0xFF is sent with the end of message condition necessitating sending the monitor channel information using PnGMT[R] to control the monitor channel transmitter, followed at the end of the frame by setting PnGMT[L] and PnGMT[R]. The L bit is automatically cleared by the GCI controller. |

| 8     | R    | Ready.  0 Default reset value.  1 Set by the CPU. Indicate to the monitor channel controller that a byte of data is ready for transmission.  Automatically cleared by the GCI controller when it generates a transmit acknowledge (ACK bit in PGMTS register) or when the L bit is reset.                                                                                                                                                                                                                                                                                         |

| 7–0   | М    | Monitor channel data byte. Written by the CPU when a byte is ready for transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3 Freescale Semiconductor 13-25

**Physical Layer Interface Controller (PLIC)**

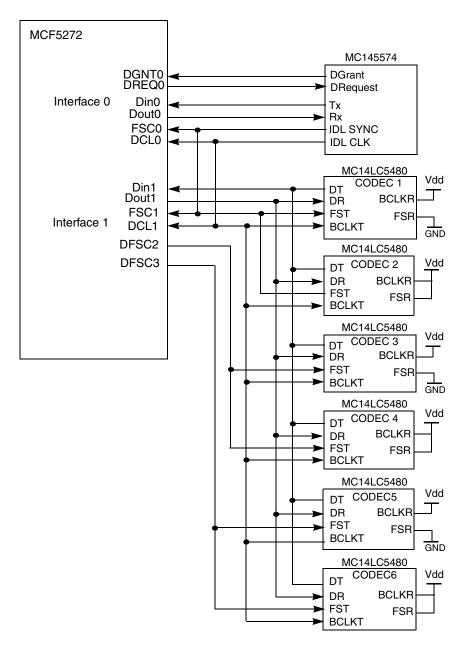

# 13.6.3 Example 1: ISDN SOHO PBX with Ports 0, 1, 2, and 3

In this example, all four ports are used to connect an external transceiver and six CODECs. Port 0 and port 1 are programmed in slave mode. An external transceiver, MC145574, is connected to port 0. Port 1, 2, and 3 are used to connect up to six external PCM CODECs.

Figure 13-37. ISDN SOHO PABX Example

In the previous example, Freescale's MC14LC5480 CODECs and MC145574 S/T transceiver are shown. The S/T transceiver in this example is connected to port 0 and the FSC0 frame sync signal is used exclusively for synchronizing the data on the transceiver's IDL interface. CODECs 1 and 2 are connected to frame sync 1, FSC1. CODECs 3 and 4 are connected to DFSC2 which is the output of programmable

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

13-38 Freescale Semiconductor

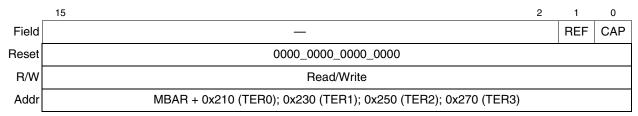

# 15.3.5 Timer Event Registers (TER0-TER3)

TERs are used to report events recognized by the timer. On recognition of an event, the timer sets the appropriate TER*n* bit, regardless of the corresponding interrupt enable bits (ORI and CE) in the TMR*n*. Writing a 1 to a bit clears it; writing 0 has no effect. Both bits must be cleared before the timer can negate the request to the interrupt controller. Both bits may be cleared simultaneously.

Figure 15-6. Timer Event Registers (TER0-TER3)

Table 15-2 describes TER*n* fields.

Table 15-2. TERn Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–2 | _    | Reserved, should be cleared.                                                                                                                                                                                                                               |

| 1    | REF  | Output reference event.  0 The counter has not reached the TRR value  1 The counter reached the TRR value. TMR[ORI] is used to enable the interrupt request caused by this event. Write a 1 to this bit to clear the event condition.                      |

| 0    | CAP  | Capture event.  0 The counter value has not been latched into the TCAP.  1 The counter value is latched in the TCAP. TMR[CE] is used to enable capture and the interrupt request caused by this event. Write a 1 to this bit to clear the event condition. |

Freescale Semiconductor 15-5

General Purpose I/O Module

# 17.2.3 Port C Control Register

There is no port C control register. Port C is enabled only when the external data bus is 16 bits wide. This is done by holding QSPI\_DOUT/WSEL high during reset. When QSPI\_DOUT/WSEL is low during reset, the external data bus is 32 bits wide and port C is unavailable.

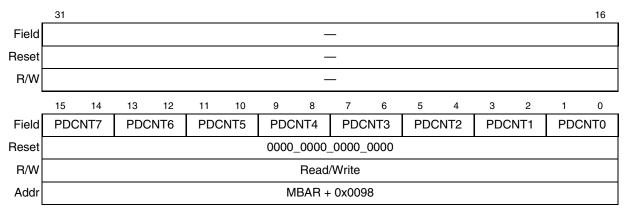

# 17.2.4 Port D Control Register (PDCNT)

PDCNT, shown in Table 17-8, is used to configure pins that have multiple functions but no associated GPIO capability. Port D has no data register nor data direction register.

Figure 17-3. Port D Control Register (PDCNT)

Table 17-7 describes PDCNT fields. Table 17-8 provides the same information organized by function.

| Bits  | Name   | Description                                                          |

|-------|--------|----------------------------------------------------------------------|

| 31–16 | _      | Reserved                                                             |

| 15–14 | PDCNT7 | Configure pin K6. 00 High impedance 01 PWM_OUT2 10 TIN1 11 Reserved  |

| 13–12 | PDCNT6 | Configure pin P5. 00 High impedance 01 PWM_OUT1 10 TOUT1 11 Reserved |

| 11–10 | PDCNT5 | Configure pin P2. 00 High impedance 01 Reserved 10 DIN3 11 INT4      |

| 9–8   | PDCNT4 | Configure pin K1.                                                    |

Table 17-7. PDCNT Field Descriptions

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

00 High impedance01 DOUT010 URT1\_TxD11 Reserved

17-8 Freescale Semiconductor

## **Signal Descriptions**

Table 19-1. Signal Descriptions Sorted by Function (Sheet 4 of 8)

| Configured                      |                     | Pin Function | าร           | Description  | Map<br>BGA                                                    | I/O                                            | Drive | Cpf  |     |

|---------------------------------|---------------------|--------------|--------------|--------------|---------------------------------------------------------------|------------------------------------------------|-------|------|-----|

| by (see notes) <sup>1</sup>     | 0 (Reset)           | 1            | 2            | 3            | Description                                                   | Pin                                            | 1/0   | (mA) | Срі |

|                                 | E_MDIO              | _            | _            | _            | Management channel<br>serial data (100 base-T<br>only)        | N10                                            | I/O   | 2    |     |

|                                 | E_RxCLK             | _            | _            | _            | Ethernet Rx clock                                             | N7                                             | I     |      |     |

|                                 | E_RxD0              | _            | _            | _            | Ethernet Rx data                                              | P7                                             | I     |      |     |

|                                 | E_RxDV              | _            | _            | _            | Ethernet Rx data valid                                        | M7                                             | I     |      |     |

|                                 | E_Tx CLK            | _            | _            | _            | Ethernet Tx clock                                             | L7                                             | I     |      |     |

|                                 | E_TxD0              | _            | _            | _            | Ethernet Tx data                                              | N6                                             | 0     | 4    | 30  |

|                                 | E_TxEN              | _            | _            | _            | Ethernet Tx enable                                            | P8                                             | 0     | 2    | 30  |

|                                 | E_TxER              | _            | _            | _            | Transmit error (100 base-T Ethernet only)                     | M10                                            | 0     | 2    | 30  |

|                                 | FSC1/FSR1/<br>DFSC1 | _            | _            | _            | PLIC port 1 IDL FSR/GCI<br>FSC1/Generated frame<br>sync 1 Out | L4                                             | I/O   | 2    | 30  |

|                                 | GND                 | Ground       | _            | _            |                                                               | E[7,8]<br>F[7,8]<br>G[6–9]<br>H[6–9]<br>J[7,8] |       |      |     |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | DCL0         | URT1_CLK     | _            | Port 0 data clock/UART1 baud clock                            | J4                                             | I     |      |     |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | DIN0         | URT1_RxD     | _            | IDL/GCI data in/UART1<br>Rx data                              | K1                                             | I     |      |     |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | _            | URT1_<br>CTS | QSPI_<br>CS2 | UART1 CTS/QSPI_CS2                                            | K2                                             | I/O   | 2    | 30  |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | _            | URT1_RTS     | INT5         | UART1 RTS/INT5                                                | K3                                             | I/O   | 2    | 30  |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | DOUT0        | URT1_TxD     | _            | IDL-GCI data Out/UART1<br>Tx data                             | K4                                             | 0     | 2    | 30  |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | _            | DIN3         | INT4         | Interrupt 4 input/PLIC port 3 data input                      | P2                                             | I     |      |     |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | PWM_<br>OUT1 | TOUT1        | _            | PWM output compare 1<br>/Timer 1 output compare               | P5                                             | 0     | 4    | 30  |

| Port D Cntl<br>Reg <sup>3</sup> | High Z              | PWM_<br>OUT2 | TIN1         | _            | PWM output compare 2<br>/Timer 1 input                        | K6                                             | I/O   | 4    | 30  |

|                                 | INT1/<br>USB_WOR    | _            | _            | _            | Interrupt input 1/USB wake-on-ring                            | M4                                             | I     |      |     |

|                                 | INT2                | _            | _            | _            | Interrupt input 1                                             | P3                                             | I     |      |     |

|                                 | INT3                | _            | _            | _            | Interrupt input 3                                             | N3                                             | I     |      |     |

19-6 Freescale Semiconductor

Table 19-1. Signal Descriptions Sorted by Function (Sheet 7 of 8)

| Configured                     |                    | Pin Function | ıs | - Description | Map<br>BGA                                           | I/O | Drive | Cpf  |     |

|--------------------------------|--------------------|--------------|----|---------------|------------------------------------------------------|-----|-------|------|-----|

| by<br>(see notes) <sup>1</sup> | 0 (Reset)          | 1            | 2  | 3             | Description                                          | Pin | 1/0   | (mA) | Срі |

|                                | PST3               | _            | _  | _             | Internal processor status 3                          | D3  | 0     | 4    | 30  |

|                                | PWM_OUT0           | _            | _  | _             | PWM output compare 0                                 | N5  | 0     | 4    | 30  |

|                                | QSPI_CLK/<br>BUSW1 | _            | _  | _             | QSPI serial clock/CS0 bus width bit 1                | L5  | 0     | 4    | 30  |

|                                | QSPI_CS0/<br>BUSW0 | _            | _  | _             | QSPI peripheral chip select 0/CS0 bus width bit 0    | M5  | 0     | 2    | 30  |

|                                | QSPI_Din           | _            | _  | _             | QSPI data input                                      | P4  | I     |      |     |

|                                | QSPI_Dout/<br>WSEL | _            | _  | _             | QSPI data output/Bus width selection                 | N4  | I/O   | 4    | 30  |

|                                | R/W                | _            | _  | _             | Read/Write                                           | P14 | 0     | 10   | 30  |

|                                | RAS0               | _            | _  | _             | SDRAM row select strobe                              | A10 | 0     | 10   | 30  |

|                                | RSTI               | _            | _  | _             | Device reset                                         | M12 | ı     |      |     |

|                                | RSTO               | _            | _  | _             | Reset output strobe                                  | F4  | 0     | 4    | 30  |

|                                | SDBA0              | _            | _  | _             | SDRAM bank 0 select                                  | J14 | 0     | 10   | 30  |

|                                | SDBA1              | _            | _  | _             | SDRAM bank 1 select                                  | H12 | 0     | 10   | 30  |

|                                | SDCLK              | _            | _  | _             | SDRAM (bus) clock,<br>Same frequency as CPU<br>clock | E14 | 0     | 10   | 30  |

|                                | SDCLKE             | _            | _  | _             | SDRAM clock enable                                   | D13 | 0     | 10   | 30  |

|                                | SDCS/<br>CS7       | _            | _  | _             | SDRAM chip select/CS7                                | B10 | 0     | 10   | 30  |

|                                | SDWE               | _            | _  | _             | SDRAM write enable                                   | В9  | 0     | 10   | 30  |

|                                | BYPASS             | _            | _  | _             | Bypass internal test mode                            | M13 | 0     | 4    | 30  |

| MTMOD <sup>4</sup>             | TCK                | PSTCLK       | _  | _             | JTAG test clock in/<br>BDM PSTCLK output             | C4  | I/O   | 4    | 30  |

| MTMOD <sup>4</sup>             | TDI                | DSI          | _  | _             | JTAG test data in/BDM data in                        | A4  | I     |      |     |

| MTMOD <sup>4</sup>             | TDO                | DSO          | _  | _             | JTAG test data out<br>/BDM data out                  | D5  | 0     | 4    | 30  |

|                                | TEA                | _            | _  | _             | BDM debug transfer error acknowledge                 | А3  | I     |      |     |

|                                | TEST               | _            | _  | _             | Device test mode enable                              | E6  | I     |      |     |

|                                | TIN0               | _            | _  | _             | Timer 0 input                                        | L6  | I     |      |     |

| MTMOD <sup>4</sup>             | TMS                | BKPT         | _  | _             | JTAG test mode/BDM select breakpoint input           | B4  | I     |      |     |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

Freescale Semiconductor 19-9

**IEEE 1149.1 Test Access Port (JTAG)**

#### **Boundary Scan Register** 21.4

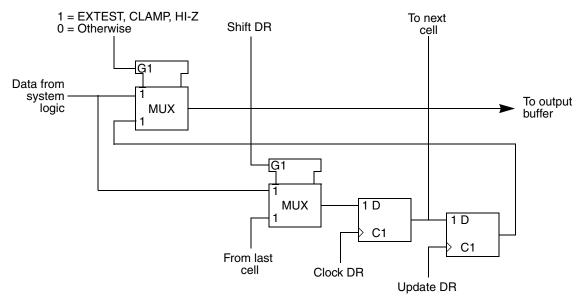

The boundary scan register contains bits for all device signal and clock pins and associated control signals. Bidirectional pins include a single scan bit for data (IO.Cell) as shown in Figure 21-6. These bits are controlled by an enable cell, shown in Figure 21-5. The control bit value determines whether the bidirectional pin is an input or an output. One or more bidirectional data bits can be serially connected to a control bit as shown in Figure 21-7. Note that when bidirectional data bits are sampled, bit data can be interpreted only after examining the I/O control bit to determine pin direction.

Open-drain bidirectional bits require separate input and output cells as no direction control is available from which to determine signal direction. Programmable open-drain signals also have an enable cell (XXX.de) to select whether the pin is open drain or push-pull. Signals with pull-up or pull-down resistors have an associated enable cell (XXX.pu); one enable cell can control multiple resistors.

Figure 21-3 to Figure 21-8 show the four MCF5272 cell types.

Figure 21-3. Output Cell (O.Cell) (BC-1)

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3 21-4 Freescale Semiconductor

**Electrical Characteristics**

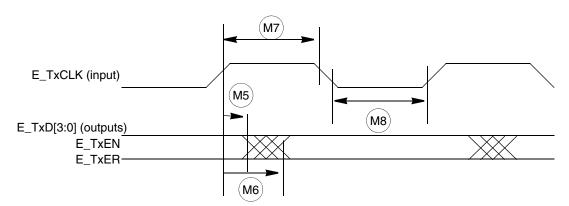

# 23.6.2 MII Transmit Signal Timing (E\_TxD[3:0], E\_TxEN, E\_TxER, E\_TxCLK)

Table 23-12 lists MII transmit channel timings.

The transmitter functions correctly up to a E\_TxCLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed twice the E\_TxCLK frequency.

The transmit outputs (E\_TxD[3:0], E\_TxEN, E\_TxER) can be programmed to transition from either the rising or falling edge of E\_TxCLK, and the timing is the same in either case. This options allows the use of non-compliant MII PHYs.

Refer to the Ethernet chapter for details of this option and how to enable it.

| Table 23-12. MII Transmit Signal | Timing |  |

|----------------------------------|--------|--|

| 4                                |        |  |

| Num | Characteristic <sup>1</sup>                   | Min | Max | Unit           |

|-----|-----------------------------------------------|-----|-----|----------------|

| M5  | E_TxCLK to E_TxD[3:0], E_TxEN, E_TxER invalid | 5   | _   | nS             |

| M6  | E_TxCLK to E_TxD[3:0], E_TxEN, E_TxER valid   | _   | 25  | nS             |

| M7  | E_TxCLK pulse-width high                      | 35% | 65% | E_TxCLK period |

| M8  | E_TxCLK pulse-width low                       | 35% | 65% | E_TxCLK period |

<sup>&</sup>lt;sup>1</sup> E\_TxCLK, ETxD0, and E\_TxEN have the same timing in 10 Mbit 7-wire interface mode.

Figure 23-12 shows MII transmit signal timings listed in Table 23-12.

Figure 23-12. MII Transmit Signal Timing Diagram

23-18 Freescale Semiconductor

# Table A-10. UART0 Module Memory Map

| MBAR<br>Offset | [31:24]                                                            | [23:16]  | [15:8]   | [7:0] |

|----------------|--------------------------------------------------------------------|----------|----------|-------|

| 0x0100         | UART0 Mode Register 1/2<br>(U0MR1/U0MR2)                           | Reserved |          |       |

| 0x0104         | UART0 Status (U0SR)                                                | Reserved |          |       |

| 0x0104         | UART0 Clock Select<br>Register (U0CSR)                             |          | Reserved |       |

| 0x0108         | UART0 Command Register<br>(U0CR)                                   | Reserved |          |       |

| 0x010C         | UART0 Receive Buffer<br>(U0RxB)                                    | Reserved |          |       |

| 0x010C         | UART0 Transmit Buffer<br>(U0TxB)                                   |          | Reserved |       |

| 0x0110         | UART0 CTS Change<br>Register (U0CCR)                               |          | Reserved |       |

| 0x0110         | UART0 Auxiliary Control<br>Register (U0ACR)                        | Reserved |          |       |

| 0x0114         | UART0 Interrupt Status<br>Register (U0ISR)                         | Reserved |          |       |

| 0x0114         | UART0 Interrupt Mask<br>Register (U0IMR)                           | Reserved |          |       |

| 0x0118         | UART0 Baud Prescaler<br>MSB (U0BG1)                                | Reserved |          |       |

| 0x011C         | UART0 Baud Prescaler<br>LSB (U0BG2)                                | Reserved |          |       |

| 0x0120         | UART0 AutoBaud MSB<br>Register (U0ABR1)                            | Reserved |          |       |

| 0x0124         | UART0 AutoBaud LSB<br>Register (U0ABR2)                            | Reserved |          |       |

| 0x0128         | UART0 TxFIFO<br>Control/Status Register<br>(U0TxFCSR)              | Reserved |          |       |

| 0x012C         | UART0 RxFIFO<br>Control/Status Register<br>(U0RxFCSR)              |          | Reserved |       |

| 0x130          | UART0 Fractional Precision<br>Divider Control Registers<br>(UFPDn) | Reserved |          |       |

| 0x0134         | UART0 CTS Unlatched<br>Input (U0IP)                                | Reserved |          |       |

| 0x0138         | UART0 RTS O/P Bit Set<br>Command Register<br>(U0OP1)               | Reserved |          |       |

| 0x013C         | UART0 RTS O/P Bit Reset<br>Command Register<br>(U0OP0)             | Reserved |          |       |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

Freescale Semiconductor A-5

## **List of Memory Maps**

# Table A-14. PLIC Module Memory Map

| MBAR<br>Offset | [31:24]                                                     | [23:16]                           | [15:8]                                         | [7:0]                             |

|----------------|-------------------------------------------------------------|-----------------------------------|------------------------------------------------|-----------------------------------|

| 0x0300         | Port0 B1 Data Receive (P0B1RR)                              |                                   |                                                |                                   |

| 0x0304         | Port1 B1 Data Receive (P1B1RR)                              |                                   |                                                |                                   |

| 0x0308         |                                                             | Port2 B1 Data Re                  | eceive (P2B1RR)                                |                                   |

| 0x030C         |                                                             | Port3 B1 Data Ro                  | eceive (P3B1RR)                                |                                   |

| 0x0310         | Port0 B2 Data Receive (P0B2RR)                              |                                   |                                                |                                   |

| 0x0314         | Port1 B2 Data Receive (P1B2RR)                              |                                   |                                                |                                   |

| 0x0318         | Port2 B2 Data Receive (P2B2RR)                              |                                   |                                                |                                   |

| 0x031C         |                                                             | Port3 B2 Data Re                  | eceive (P3B2RR)                                |                                   |

| 0x0320         | Port 0 D Data Receive<br>(P0DRR)                            | Port 1 D Data Receive<br>(P1DRR)  | Port 2 D Data Receive<br>(P2DRR)               | Port 3 D Data Receive<br>(P3DRR)  |

| 0x0328         |                                                             | Port0 B1 Data Tr                  | ansmit (P0B1TR)                                |                                   |

| 0x032C         | Port1 B1 Data Transmit (P1B1TR)                             |                                   |                                                |                                   |

| 0x0330         | Port2 B1 Data Transmit (P2B1TR)                             |                                   |                                                |                                   |

| 0x0334         | Port3 B1 Data Transmit (P3B1TR)                             |                                   |                                                |                                   |

| 0x0338         | Port0 B2 Data Transmit (P0B2TR)                             |                                   |                                                |                                   |

| 0x033C         | Port1 B2 Data Transmit (P1B2TR)                             |                                   |                                                |                                   |

| 0x0340         |                                                             | Port2 B2 Data Tr                  | ansmit (P2B2TR)                                |                                   |

| 0x0344         |                                                             | Port3 B2 Data Tr                  | ansmit (P3B2TR)                                |                                   |

| 0x0348         | Port 0 D Data Transmit<br>(P0DTR)                           | Port 1 D Data Transmit<br>(P1DTR) | Port 2 D Data Transmit<br>(P2DTR)              | Port 3 D Data Transmit<br>(P3DTR) |

| 0x0350         | Port0 GCI/IDL Configu                                       | ration Register (P0CR)            | Port1 GCI/IDL Configuration Register (P1CR)    |                                   |

| 0x0354         | Port2 GCI/IDL Configuration Register (P2CR)                 |                                   | Port3 GCI/IDL Configuration Register (P3CR)    |                                   |

| 0x0358         | Port0 Interrupt Configuration Register (P0ICR)              |                                   | Port1 Interrupt Configuration Register (P1ICR) |                                   |

| 0x035C         | Port2 Interrupt Configuration Register (P2ICR)              |                                   | Port3 Interrupt Configuration Register (P3ICR) |                                   |

| 0x0360         | Port0 GCI Monitor RX (P0GMR)                                |                                   | Port1 GCI Monitor RX (P1GMR)                   |                                   |

| 0x0364         | Port2 GCI Monitor RX (P2GMR)                                |                                   | Port3 GCI Monitor RX (P3GMR)                   |                                   |

| 0x0368         | Port0 GCI Monitor TX (P0GMT)                                |                                   | Port1 GCI Monitor TX (P1GMT)                   |                                   |

| 0x036C         | Port2 GCI Monitor TX (P2GMT)                                |                                   | Port3 GCI Monitor TX (P3GMT)                   |                                   |

| 0x0370         | Reserved                                                    | GCI Monitor TX Status<br>(PGMTS)  | GCI Monitor TX abort<br>(PGMTA)                | Reserved                          |

| 0x0374         | Port0 GCI C/I RX (P0GCIR)                                   | Port1 GCI C/I RX (P1GCIR)         | Port2 GCI C/I RX (P2GCIR)                      | Port3 GCI C/I RX (P3GCIR)         |

| 0x0378         | Port0 GCI C/I TX (P0GCIT)                                   | Port1 GCI C/I TX (P1GCIT)         | Port2 GCI C/I TX (P2GCIT)                      | Port3 GCI C/I TX (P3GCIT)         |

| 0x037C         | Reserved GCI C/I TX Status (PGCITSR)                        |                                   |                                                |                                   |

| 0x0383         | Reserved GCI D-Channel Status (PDCSR)                       |                                   | GCI D-Channel Status<br>(PDCSR)                |                                   |

| 0x0384         | Port0 Periodic Status (P0PSR)                               |                                   | Port1 Periodic                                 | Status (P1PSR)                    |

| 0x0388         | Port2 Periodic Status (P2PSR) Port3 Periodic Status (P3PSR) |                                   |                                                |                                   |

MCF5272 ColdFire® Integrated Microprocessor User's Manual, Rev. 3

A-8 Freescale Semiconductor

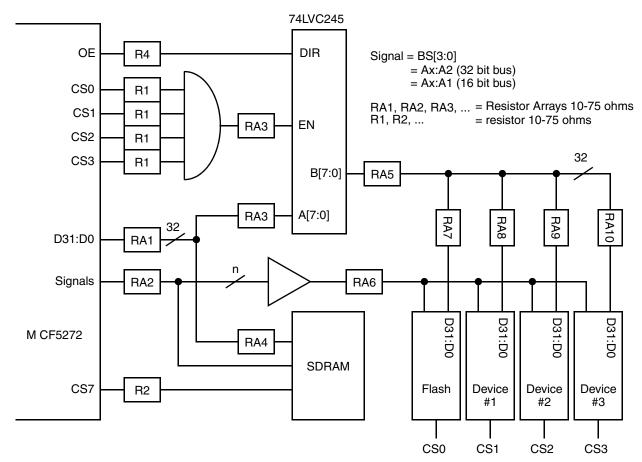

### **Buffering and Impedance Matching**

Figure B-1. Buffering and Termination

B-2 Freescale Semiconductor