Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Coldfire V2                                               |

| Core Size                  | 32-Bit Single-Core                                        |

| Speed                      | 66MHz                                                     |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB |

| Peripherals                | DMA, WDT                                                  |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 16KB (4K x 32)                                            |

| Program Memory Type        | ROM                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 32                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | External                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 196-LBGA                                                  |

| Supplier Device Package    | 196-LBGA (15x15)                                          |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf5272vm66  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents (Continued)

Paragraph Number

Title

### Page Number

Chapter 12

## Universal Serial Bus (USB)

| 12.1 | Introduction    |                                                                       | 12-1  |

|------|-----------------|-----------------------------------------------------------------------|-------|

| 12.2 | Module Operat   | tion                                                                  | 12-2  |

|      | 12.2.1 USB M    | odule Architecture                                                    | 12-2  |

|      | 12.2.1.1        | USB Transceiver Interface                                             | 12-3  |

|      | 12.2.1.2        | Clock Generator                                                       | 12-4  |

|      | 12.2.1.3        | USB Control Logic                                                     | 12-4  |

|      | 12.2.1.4        | Endpoint Controllers                                                  | 12-5  |

|      | 12.2.1.5        | USB Request Processor                                                 | 12-5  |

| 12.3 | Register Descr  | iption and Programming Model                                          | 12-7  |

|      | 12.3.1 USB M    | emory Map                                                             | 12-7  |

|      | 12.3.2 Register | r Descriptions                                                        | 12-9  |

|      | 12.3.2.1        | USB Frame Number Register (FNR)                                       | 12-9  |

|      | 12.3.2.2        | USB Frame Number Match Register (FNMR)                                | 12-9  |

|      | 12.3.2.3        | USB Real-Time Frame Monitor Register (RFMR)                           |       |

|      | 12.3.2.4        | USB Real-Time Frame Monitor Match Register (RFMMR)                    | 12-11 |

|      | 12.3.2.5        | USB Function Address Register (FAR)                                   | 12-11 |

|      | 12.3.2.6        | USB Alternate Settings Register (ASR)                                 | 12-12 |

|      | 12.3.2.7        | USB Device Request Data 1 and 2 Registers (DRR1/2)                    | 12-13 |

|      | 12.3.2.8        | USB Specification Number Register (SPECR)                             |       |

|      | 12.3.2.9        | USB Endpoint 0 Status Register (EP0SR)                                | 12-14 |

|      | 12.3.2.10       | USB Endpoint 0 IN Configuration Register (IEP0CFG)                    | 12-15 |

|      | 12.3.2.11       | USB Endpoint 0 OUT Configuration Register (OEP0CFG)                   | 12-16 |

|      | 12.3.2.12       | USB Endpoint 1–7 Configuration Register (EPnCFG)                      | 12-16 |

|      | 12.3.2.13       | USB Endpoint 0 Control Register (EP0CTL)                              | 12-17 |

|      | 12.3.2.14       |                                                                       |       |

|      | 12.3.2.15       | USB Endpoint 0 Interrupt Mask (EP0IMR) and General/Endpoint 0 Interru | ıpt   |

|      | Registers       | (EPOISR)                                                              | 12-22 |

|      | 12.3.2.16       | USB Endpoints 1-7 Status / Interrupt Registers (EPnISR)               | 12-25 |

|      | 12.3.2.17       | USB Endpoint 1–7 Interrupt Mask Registers (EPnIMR)                    | 12-26 |

|      | 12.3.2.18       | USB Endpoint 0-7 Data Registers (EPnDR)                               | 12-27 |

|      | 12.3.2.19       | USB Endpoint 0-7 Data Present Registers (EPnDPR)                      | 12-28 |

|      |                 | aration RAM                                                           |       |

|      | 12.3.3.1        | Configuration RAM Content                                             | 12-28 |

|      | 12.3.3.2        | USB Device Configuration Example                                      | 12-29 |

|      | 12.3.4 USB M    | odule Access Times                                                    | 12-30 |

|      | 12.3.4.1        | Registers                                                             | 12-30 |

|      | 12.3.4.2        | Endpoint FIFOs                                                        |       |

|      | 12.3.4.3        | Configuration RAM                                                     | 12-30 |

|      |                 |                                                                       |       |

### Table vii. QSPI Module Memory Map (continued)

| MBAR<br>Offset | Register Name           | Old Mnemonic | New Mnemonic |

|----------------|-------------------------|--------------|--------------|

| 0x00AC         | QSPI Interrupt Register | SPINT        | QIR          |

| 0x00B0         | QSPI Address Register   | SPADDR       | QAR          |

| 0x00B4         | QSPI Data Register      | SPDATA       | QDR          |

### Table viii. PWM Module Memory Map

| MBAR<br>Offset | Register Name              | Old Mnemonic | New Mnemonic |

|----------------|----------------------------|--------------|--------------|

| 0x00C0         | PWM Control Register 0     | PWMCR1       | PWCR0        |

| 0x00C4         | PWM Control Register 1     | PWMCR2       | PWCR1        |

| 0x00C8         | PWM Control Register 2     | PWMCR3       | PWCR2        |

| 0x00D0         | PWM Pulse-Width Register 0 | PWMWD1       | PWWD0        |

| 0x00D4         | PWM Pulse-Width Register 1 | PWMWD2       | PWWD1        |

| 0x00D8         | PWM Pulse-Width Register 2 | PWMWD3       | PWWD2        |

### Table ix. DMA Module Memory Map

| MBAR<br>Offset | Register Name                    | Old Mnemonic | New Mnemonic |

|----------------|----------------------------------|--------------|--------------|

| 0x00E0         | DMA Mode Register                | DCMR         | No change    |

| 0x00E6         | DMA Interrupt Register           | DCIR         | No change    |

| 0x00E8         | DMA Byte Count Register          | DBCR         | No change    |

| 0x00EC         | DMA Source Address Register      | DSAR         | No change    |

| 0x00F0         | DMA Destination Address Register | DDAR         | No change    |

### Table x. UART0 Module Memory Map

| MBAR<br>Offset | Register Name               | Old Mnemonic | New Mnemonic |

|----------------|-----------------------------|--------------|--------------|

| 0x0100         | UART0 Mode Register 1/2     | U1MR1/U1MR2  | U0MR1/U0MR2  |

| 0x0104         | UART0 Status                | U1SR         | U0SR         |

| 0x0104         | UART0 Clock Select Register | U1CSR        | U0CSR        |

| 0x0108         | UART0 Command Register      | U1CR         | U0CR         |

| 0x010C         | UART0 Receive Buffer        | U1RxB        | U0RxB        |

| 0x010C         | UART0 Transmit Buffer       | U1TxB        | U0TxB        |

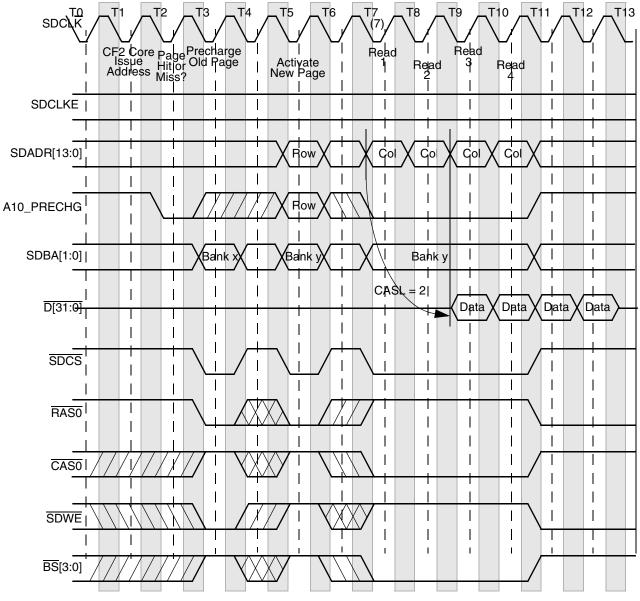

SDRAM Controller

Figure 9-9. SDRAM Burst Read, 32-Bit Port, Page Miss, Access = 9-1-1-1

| Step | Description             |

|------|-------------------------|

| 7    | Set HTUR and HTLR       |

| 8    | Set EMRBR               |

| 9    | Set ERDSR               |

| 10   | Set ETDSR               |

| 11   | Set RCR                 |

| 12   | Set TCR                 |

| 13   | Set MSCR (optional)     |

| 14   | Initialize (Empty) TxBD |

| 15   | Initialize (Empty) RxBD |

Table 11-32. User Initialization Process (before ETHER\_EN) (continued)

## 11.5.24 FEC Initialization

In the FEC, the descriptor control machine initializes a few registers whenever the ETHER\_EN control is asserted. The transmit and receive FIFO pointers are reset, the transmit backoff random number is initialized, and the transmit and receive blocks are activated. After the FEC initialization sequence is complete, the hardware is ready for operation, waiting for RDAR and TDAR to be asserted by the user.

### 11.5.24.1 User Initialization (after setting ETHER\_EN)

The user initializes portions of the FEC after setting ETHER\_EN. The exact values depend on the particular application. The sequence probably resembles the steps shown in Table 11-33, though these could also be done before asserting ETHER\_EN.

| Step | Description                                     |  |

|------|-------------------------------------------------|--|

| 1    | Fill Receive Descriptor Ring with Empty Buffers |  |

| 2    | Set RDAR                                        |  |

Table 11-33. User Initialization (after ETHER\_EN)

## 11.6 Buffer Descriptors

Data associated with the FEC controller is stored in buffers, which are referenced by buffer descriptors (BDs) organized as tables in the dual-port RAM. These tables have the same basic configuration as those used by the USB.

The BD table allows users to define separate buffers for transmission and reception. Each table forms a circular queue, or ring. The FEC uses status and control fields in the BDs to inform the core that the buffers have been serviced, to confirm reception and transmission events, or to indicate error conditions.

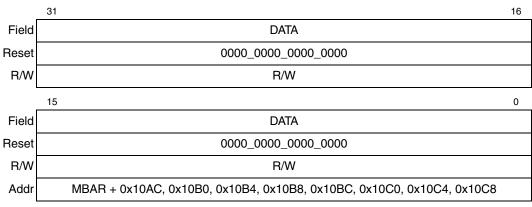

### 12.3.2.18 USB Endpoint 0–7 Data Registers (EPnDR)

Figure 12-21 shows the USB endpoint 0-7 data registers.

#### Figure 12-21. USB Endpoint 0-7 Data Registers (EPnDR)

Table 12-17 lists field descriptions for the USB endpoint 0–7 data registers.

#### Table 12-17. EPnDR Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31–0 | DATA | The EP <i>n</i> DR registers allow data to be written to/from each endpoint's FIFO. For IN endpoints, the registers are write-only and writing to a full FIFO is ignored. For OUT endpoints, the registers are read-only, and reading from an empty FIFO returns undefined data. These registers can be accessed using 8-, 16-, or 32-bit accesses in order to read/write 1, 2, or 4 bytes from/to the FIFO at one time. |  |

#### Physical Layer Interface Controller (PLIC)

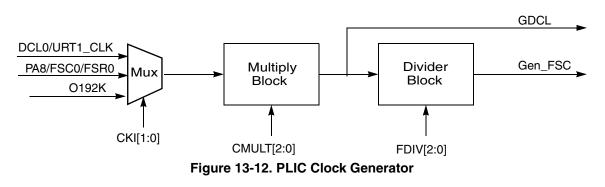

The above settings can be made by a single write of the 16-bit value 0x802B to PCSR.

The following restrictions should be observed when using the clock generator module:

- The smallest multiplication factor is 2.

- CLKIN should be significantly greater than (> 20 times) the synthesized clock.

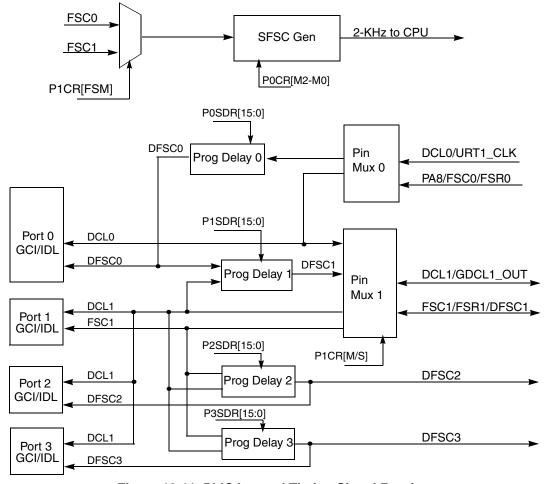

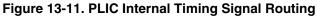

Figure 13-11 and Figure 13-12 show the connectivity and relationship of the timing signals within the PLIC block.

## 13.3.2 Super Frame Sync Generation

Figure 13-11 shows the generation of the 2-KHz super frame sync. The choice of either FSC0 or FSC1 is possible using P1CR[FSM]. This allows either the port 0 or port 1 timing to be used to generate the 2-KHz super frame sync interrupt. The SFSC block then divides this accordingly. When P1CR[FSM] is set, FSC1 is the source of the super frame sync. In case P1CR[MS] is 0 (that is, port 1 is in slave mode), the interrupt is ultimately driven by an external source. In case the M/S bit is 1 (that is, port 1 is in master mode), FSC1 ultimately comes from port 0.

## 13.3.3 Frame Sync Synthesis

Figure 13-11 illustrates the relationships between the various frame sync clocks. DFSC1 is generated through programmable delay 1 referenced to DFSC0. DFSC2 and DFSC3 are generated through programmable delays 2 and 3 referenced to DFSC1. Note well the following:

- POSDR settings affect DFSC[0–3]

- P1SDR settings affect DFSC[1–3]

- P2SDR settings affect only DFSC2

- P3SDR settings affect only DFSC3

## 13.4 PLIC Register Memory Map

Table 13-1 lists the PLIC registers with their offset address from MBAR and their default value on reset.

| MBAR<br>Offset | [31:24]                                                                                                            | [23:16]          | [15:8]          | [7:0] |

|----------------|--------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------|

| 0x0300         |                                                                                                                    | Port0 B1 Data Re | eceive (P0B1RR) |       |

| 0x0304         |                                                                                                                    | Port1 B1 Data Re | eceive (P1B1RR) |       |

| 0x0308         |                                                                                                                    | Port2 B1 Data Re | eceive (P2B1RR) |       |

| 0x030C         |                                                                                                                    | Port3 B1 Data Re | eceive (P3B1RR) |       |

| 0x0310         |                                                                                                                    | Port0 B2 Data Re | eceive (P0B2RR) |       |

| 0x0314         |                                                                                                                    | Port1 B2 Data Re | eceive (P1B2RR) |       |

| 0x0318         |                                                                                                                    | Port2 B2 Data Re | eceive (P2B2RR) |       |

| 0x031C         |                                                                                                                    | Port3 B2 Data Re | eceive (P3B2RR) |       |

| 0x0320         | Port0 D Data Receive<br>(P0DRR)Port1 D Data Receive<br>(P1DRR)Port2 D Data Receive<br>(P2DRR)Port3 D Data<br>(P3DF |                  |                 |       |

| 0x0328         |                                                                                                                    | Port0 B1 Data Tr | ansmit (P0B1TR) |       |

| 0x032C         |                                                                                                                    | Port1 B1 Data Tr | ansmit (P1B1TR) |       |

| 0x0330         | Port2 B1 Data Transmit (P2B1TR)                                                                                    |                  |                 |       |

| 0x0334         | Port3 B1 Data Transmit (P3B1TR)                                                                                    |                  |                 |       |

| 0x0338         | Port0 B2 Data Transmit (P0B2TR)                                                                                    |                  |                 |       |

| 0x033C         |                                                                                                                    | Port1 B2 Data Tr | ansmit (P1B2TR) |       |

Table 13-1. PLIC Module Memory Map

Physical Layer Interface Controller (PLIC)

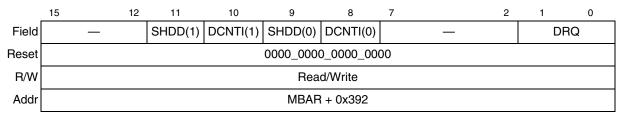

## 13.5.20 D-Channel Request Register (PDRQR)

All bits in this read/write register are cleared on hardware or software reset.

The PDRQR register contains D-channel control bits for all four ports on the MCF5272.

#### Figure 13-32. D-Channel Request Registers (PDRQR)

| Bits  | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15–12 |       | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 11, 9 | SHDD  | <ul> <li>D-channel shift direction.</li> <li>D-channel data is msb first. The first bit received is assumed to be the most significant bit and is loaded into the msb position of the D-channel receive register for the respective port. SHDD(1) configures the shift direction for ports 1, 2 and 3, SHDD(0) configures the shift direction for port 0.</li> <li>D-channel data is lsb first for the D channel. The first bit received is assumed to be the least significant bit and is loaded into the lsb position of the D-channel receive register for the respective port.</li> </ul> |  |

| 10, 8 | DCNTI | <ul> <li>D-channel control ignore. Allows the D-Channel contention function to be ignored.</li> <li>00 contention active on both ports</li> <li>01 ignore contention on port 0</li> <li>10 ignore contention on port 1</li> <li>11 ignore contention on both ports</li> </ul>                                                                                                                                                                                                                                                                                                                 |  |

| 7–2   | —     | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1–0   | DRQ   | The value written to these bits is driven onto the DREQ pins associated with port 0 and port 1. When set, a logic high, 1, is driven on to the corresponding pin.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

### Table 13-15. PDRQR Field Descriptions

#### Physical Layer Interface Controller (PLIC)

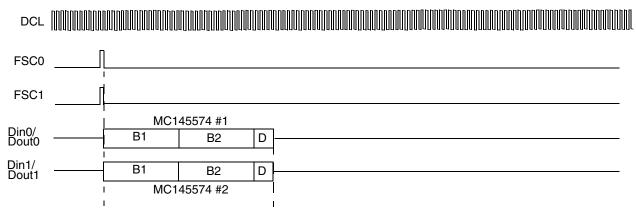

Two of Freescale's MC145574 S/T transceivers are shown connected to ports 0 and 1. The frame sync control signal FSC0 is connected to S/T transceiver one, while FSC1 is connected to transceiver two.

Figure 13-42 shows an example of the IDL bus timing relationship of the S/T transceivers when in standard IDL2 8-bit mode with a common frame sync.

Figure 13-42. Standard IDL2 8-Bit Mode

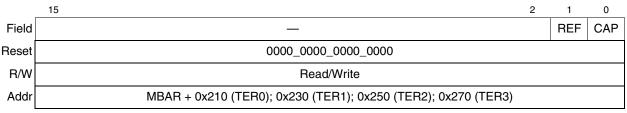

## 15.3.5 Timer Event Registers (TER0–TER3)

TERs are used to report events recognized by the timer. On recognition of an event, the timer sets the appropriate TERn bit, regardless of the corresponding interrupt enable bits (ORI and CE) in the TMRn. Writing a 1 to a bit clears it; writing 0 has no effect. Both bits must be cleared before the timer can negate the request to the interrupt controller. Both bits may be cleared simultaneously.

Figure 15-6. Timer Event Registers (TER0–TER3)

Table 15-2 describes TER*n* fields.

| Table 15 | 5-2. TER <i>n</i> | <b>Field Des</b> | criptions |

|----------|-------------------|------------------|-----------|

|----------|-------------------|------------------|-----------|

| Bits | Name                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–2 | _                                                                                                                                                                                                                                                                                  | Reserved, should be cleared.                                                                                                                                                                                                                                              |

| 1    | REF                                                                                                                                                                                                                                                                                | <ul> <li>Output reference event.</li> <li>0 The counter has not reached the TRR value</li> <li>1 The counter reached the TRR value. TMR[ORI] is used to enable the interrupt request caused by this event. Write a 1 to this bit to clear the event condition.</li> </ul> |

| 0    | CAP       Capture event.         0       The counter value has not been latched into the TCAP.         1       The counter value is latched in the TCAP. TMR[CE] is used to enable capture and the inter caused by this event. Write a 1 to this bit to clear the event condition. |                                                                                                                                                                                                                                                                           |

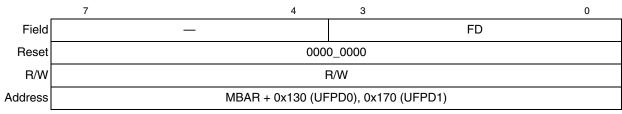

## 16.3.15 UART Fractional Precision Divider Control Registers (UFPDn)

The UFPD*n* registers allow greater accuracy when deriving a transmitter/receiver clock source from CLKIN. The use of the UFPD*n* registers is optional; if the contents are left in the reset state, code written for other ColdFire devices containing UART modules will not be affected by the addition of these registers. The contents of these registers allow the frequency to be divided by a factor of up to 16. When autobaud is used, these registers are updated automatically to reflect the clock rate being used. Host software can write to these registers to make fine adjustments to the clock rate. See Section 16.5.1.2, "Calculating Baud Rates," for an example of UFPD*n* programming.

Figure 16-18. UART Fractional Precision Divider Control Registers (UFPDn)

Table 16-12 describes UFPDn fields.

#### Table 16-12. UFPDn Field Descriptions

| Bits | Name | Description                                                                                                                                                       |  |  |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7–4  | _    | Reserved, should be cleared.                                                                                                                                      |  |  |

| 3–0  | FD   | Fractional divider. The value of these bits, from 0 to 15, determine the scale factor by which the clocking source for the transmitter and/or receiver is scaled. |  |  |

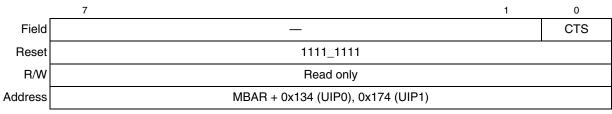

### 16.3.16 UART Input Port Registers (UIPn)

The UIP registers, Figure 16-19, show the current state of the  $\overline{\text{CTS}}$  input.

Figure 16-19. UART Input Port Registers (UIPn)

Table 16-13 describes UIPn fields.

#### Table 16-13. UIPn Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                                    |  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7–1  | —    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                   |  |  |

| 0    |      | <ul> <li>CTS state.The CTS value is latched and reflects the state of the input pin when UIP<i>n</i> is read. Note: This bit has the same function and value as UIPCR<i>n</i>[RTS].</li> <li>The current state of the CTS input is logic 0.</li> <li>The current state of the CTS input is logic 1.</li> </ul> |  |  |

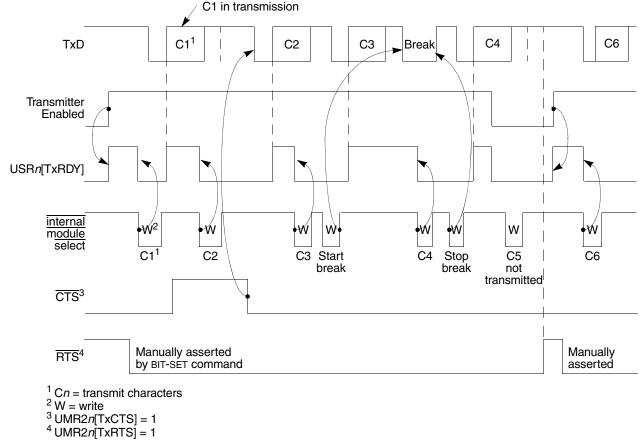

If the transmitter is reset through a software command, operation stops immediately (see Section 16.3.5, "UART Command Registers (UCRn)"). The transmitter is reenabled through the UCR*n* to resume operation after a disable or software reset.

If the clear-to-send operation is enabled,  $\overline{\text{CTS}}$  must be asserted for the character to be transmitted. If  $\overline{\text{CTS}}$  is negated in the middle of a transmission, the character in the shift register is sent and TxD remains in mark state until  $\overline{\text{CTS}}$  is reasserted. If the transmitter is forced to send a continuous low condition by issuing a START BREAK command, the transmitter ignores the state of  $\overline{\text{CTS}}$ .

If the transmitter is programmed to automatically negate  $\overline{\text{RTS}}$  when a message transmission completes,  $\overline{\text{RTS}}$  must be asserted manually before a message is sent. In applications in which the transmitter is disabled after transmission is complete and  $\overline{\text{RTS}}$  is appropriately programmed,  $\overline{\text{RTS}}$  is negated one bit time after the character in the shift register is completely transmitted. The transmitter must be manually reenabled by reasserting  $\overline{\text{RTS}}$  before the next message is to be sent.

The transmitter must be enabled prior to accepting a START BREAK command. If the transmitter is disabled while the BREAK is active, the BREAK is not terminated. The BREAK can only be terminated by using the STOP BREAK command.

Figure 16-25 shows the functional timing information for the transmitter.

Figure 16-31. UART Mode Programming Flowchart (Sheet 5 of 5)

General Purpose I/O Module

| Pin Number | PACNT[ <i>xx</i> ] = 00<br>(Function 0b00) | PACNT[ <i>xx</i> ] = 01<br>(Function 0b01) | PACNT[ <i>xx</i> ] = 10<br>(Function 0b10) | PACNT[ <i>xx</i> ] = 11<br>(Function 0b11) |  |

|------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--|

| D2         | PA0                                        | USB_TP                                     | —                                          | —                                          |  |

| D1         | PA1                                        | USB_RP                                     | —                                          | —                                          |  |

| E5         | PA2                                        | USB_RN                                     | —                                          | —                                          |  |

| E4         | PA3                                        | USB_TN                                     | —                                          | —                                          |  |

| E3         | PA4                                        | USB_Susp                                   | —                                          | —                                          |  |

| E2         | PA5                                        | USB_TxEN                                   | —                                          | —                                          |  |

| E1         | PA6                                        | USB_RxD                                    | —                                          | —                                          |  |

| P1         | PA7                                        | QSPI_CS3                                   | DOUT3                                      | —                                          |  |

| J2         | PA8                                        | FSC0/FSR0                                  | —                                          | —                                          |  |

| J3         | PA9                                        | DGNT0                                      | —                                          | —                                          |  |

| K5         | PA10                                       | DREQ0                                      | —                                          | —                                          |  |

| L1         | PA11                                       | Reserved                                   | QSPI_CS1                                   | -                                          |  |

| L2         | PA12                                       | DFSC2                                      | —                                          | —                                          |  |

| L3         | PA13                                       | DFSC3                                      | —                                          | —                                          |  |

| M2         | PA14                                       | DREQ1                                      |                                            |                                            |  |

| M3         | PA15                                       | DGNT1 <sup>1</sup>                         | —                                          | —                                          |  |

#### Table 17-4. Port A Control Register Function Bits

<sup>1</sup> If this pin is programmed to function as  $\overline{INT6}$ , it is not available as a GPIO.

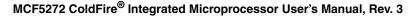

## 17.2.2 Port B Control Register (PBCNT)

PBCNT, shown in Figure 17-2, is used to configure the pins assigned to signals that are multiplexed with GPIO port B.

Table 17-5 describes PBCNT fields. Table 17-6 provides the same information organized by function.

Signal Descriptions

## 19.11.4 USB Transmit Data Negative (USB\_TN/PA3)

USB mode: USB\_TN is the inverted data transmit output.

Port A mode: This pin can also be configured as the PA3 I/O.

## 19.11.5 USB Suspend Driver (USB\_SUSP/PA4)

USB mode: USB\_SUSP is used to put the USB driver in suspend operation.

Port A mode: This pin can also be configured as the PA4 I/O.

## 19.11.6 USB Transmitter Output Enable (USB\_TxEN/PA5)

USB mode: USB\_TxEN enables the transceiver to transmit data on the bus. It requires a 4.7-K<sup>3</sup>/<sub>4</sub> pullup resistor to ensure that the external USB Tx driver is off between the MCF5272 coming out of reset and initializing the port A pin configuration register.

Port A mode: This pin can also be configured as the PA5 I/O.

## 19.11.7 USB Rx Data Output (USB\_RxD/PA6)

USB mode: USB\_RxD is the receive data output from the differential receiver inputs USB\_RN and USB\_RP.

Port A mode: This pin can also be configured as the PA6 I/O.

## 19.11.8 USB\_D+ and USB\_D-

USB\_D+ and USB\_D- are the on-chip USB interface transceiver signals. When these signals are enabled, the USB module uses them to communicate to an external USB bus. When not used, each signal should be pulled to VDD using a 4.7-K<sup>3</sup>/<sub>4</sub> resistor.

## 19.11.9 USB\_CLK

USB\_CLK is used to connect an external 48-MHz oscillator to the USB module. When this pin is tied to GND or VDD, the USB module automatically uses the internal CPU clock. In this case the CLKIN must be 48 MHz if the system is to use the USB function.

## 19.11.10 INT1/USB Wake-on-Ring (USB\_WOR)

The USB module allows for INT1 to generate the USB wake-on-ring signal to the USB host controller. This function is enabled by a control bit in the USB module. WOR is provided to allow the CPU and the USB interface to be woken up when in power down mode. This occurs when the USB controller detects a resume state at the USB inputs.

The interrupt output of an ISDN transceiver, such as the MC145574, can be connected to INT1/USB\_WOR. Before putting the device into sleep mode, the USB module's wake on ring function

| Signal         | Description                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI/DSI        | Test and debug data in. Input provided for loading serial data port shift registers (boundary-scan, bypass, and instruction registers). Shifting in of data depends on the state of the JTAG controller state machine and the instruction currently in the instruction register. Data is shifted in on the rising edge of TCK. |

| TRST/<br>DSCLK | JTAG test reset. TRST asynchronously resets the JTAG TAP logic when low.                                                                                                                                                                                                                                                       |

| MTMOD          | Freescale test mode select. Negating MTMOD enables JTAG mode; asserting it enables BDM mode.                                                                                                                                                                                                                                   |

#### Table 21-1. JTAG Signals (continued)

## 21.3 TAP Controller

The TAP controller is a synchronous state machine that controls JTAG logic and interprets the sequence of logical values on TMS. The value adjacent to each arrow in the state machine in Figure 21-2 reflects the value of TMS sampled on the rising edge of TCK. For a description of the TAP controller states, refer to the IEEE 1149.1 document.

Figure 21-2. TAP Controller State Machine

### 23.3 AC Electrical Specifications

### NOTE

AC timing specifications may be subject to change during ongoing qualification.

AC timing specifications assume maximum output load capacitance on all output pins including SDCLK. If this value is different, the input and output timing specifications would need to be adjusted to match the clock load.

AC timing specifications referenced to SDCLK assume SDRAM control register bit 3 is 0. After reset this bit is set.

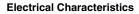

### 23.3.1 Clock Input and Output Timing Specifications

Table 23-6 lists clock input and output timings.

| Name             | Ob any stariatio                                      | 0–60 | 0–66 MHz |      |

|------------------|-------------------------------------------------------|------|----------|------|

|                  | Characteristic                                        | Min  | Max      | Unit |

|                  | Frequency of operation                                | 0    | 66.00    | MHz  |

| C1               | CLKIN period (T) <sup>1</sup>                         | 15   | _        | nS   |

| C2 <sup>2</sup>  | CLKIN fall time (from $V_h = 2.4$ V to $V_l = 0.5$ V) |      | 2        | nS   |

| C3 <sup>2</sup>  | CLKIN rise time (from $V_1 = 0.5$ V to $V_h = 2.4$ V) | —    | 2        | nS   |

| C4               | CLKIN duty cycle (measured at 1.5 V)                  | 45   | 55       | %    |

| C4a <sup>3</sup> | CLKIN pulse-width high (measured at 1.5 V)            | 6.75 | 8.25     | nS   |

| C4b <sup>3</sup> | CLKIN pulse-width low (measured at 1.5 V)             | 6.75 | 8.25     | nS   |

#### Table 23-6. Clock Input and Output Timing Specifications

<sup>1</sup> The clock period is referred to as T in the electrical specifications. The time for T is always in nS. Timing specifications can be given in terms of T. For example, 2T+5 nS

<sup>2</sup> Specification values are not tested.

<sup>3</sup> Specification values listed are for maximum frequency of operation.

Clock input and output timings listed in Table 23-6 are shown in Figure 23-1.

Figure 23-1. Clock Input Timing Diagram

List of Memory Maps

| CPU SPACE<br>ADDRESS | NAME   | Size | SYSTEM CONFIGURATION REGISTERS       | Program Access   | Debug Access |

|----------------------|--------|------|--------------------------------------|------------------|--------------|

| 0x0002               | (CACR) | 32   | Cache Control Register               | MOVEC            | RCREG, WCREG |

| 0x0004               | (ACR0) | 32   | Cache Access Control Register 0      | MOVEC            | RCREG, WCREG |

| 0x0005               | (ACR1) | 32   | Cache Access Control Register 1      | MOVEC            | RCREG, WCREG |

| 0x008x               | A7:A0  | 32   | Address registers A7:A0              | MOVE             | RAREG, WAREG |

| 0x008x               | D7:D0  | 32   | Data registers D7:D0                 | MOVE             | RDREG, WDREG |

| 0x0801               | (VBR)  | 32   | Vector Base Register                 | MOVEC            | RCREG, WCREG |

| 0x080E               | CCR    | 8    | Condition Code Register (Debug only) | MOVE to/from CCR | RCREG, WCREG |

| 0x080F               | PC     | 32   | Program Counter (Debug only)         |                  | RCREG, WCREG |

| 0x0C00               | ROMBAR | 32   | ROM Base Address Register            | MOVEC            | RCREG, WCREG |

| 0x0C04               | RAMBAR | 32   | SRAM Base Address Register           | MOVEC            | RCREG, WCREG |

| 0x0C0F               | MBAR   | 32   | Module Base Address Register         | MOVEC            |              |

#### Table A-2. CPU Space Registers Memory Map

### NOTE

MBAR must only be written using the MOVEC instruction. Writing to address MBAR+0x0000 causes unpredictable device operation.

#### Table A-3. On-Chip Peripherals and Configuration Registers Memory Map

| MBAR<br>Offset | [31:24]                              | [23:16]                                        | [15:8]                             | [7:0] |  |  |  |

|----------------|--------------------------------------|------------------------------------------------|------------------------------------|-------|--|--|--|

| 0x0000         |                                      | Module Base Address Register, Read Only (MBAR) |                                    |       |  |  |  |

| 0x0004         | System Configurat                    | ion Register (SCR)                             | Reserved                           |       |  |  |  |

| 0x0006         | Rese                                 | erved                                          | System Protection Register (SPR)   |       |  |  |  |

| 0x0008         |                                      | Power Management Register (PMR)                |                                    |       |  |  |  |

| 0x000E         | Rese                                 | erved                                          | Activate Low Power Register (ALPR) |       |  |  |  |

| 0x0010         | Device Identification Register (DIR) |                                                |                                    |       |  |  |  |

#### Table A-4. Interrupt Control Register Memory Map

| MBAR<br>Offset | [31:24]                                                   | [23:16] | [15:8] | [7:0] |  |  |

|----------------|-----------------------------------------------------------|---------|--------|-------|--|--|

| 0x0020         | Interrupt Control Register 1 (ICR1)                       |         |        |       |  |  |

| 0x0024         | Interrupt Control Register 2 (ICR2)                       |         |        |       |  |  |

| 0x0028         | Interrupt Control Register 3 (ICR3)                       |         |        |       |  |  |

| 0x002C         | Interrupt Control Register 4 (ICR4)                       |         |        |       |  |  |

| 0x0030         | Interrupt Source Register (ISR)                           |         |        |       |  |  |

| 0x0034         | Programmable Interrupt Transition Register (PITR)         |         |        |       |  |  |

| 0x0038         | Programmable Interrupt Wakeup Register (PIWR)             |         |        |       |  |  |

| 0x003F         | Reserved Programmable Interrupt<br>Vector Register (PIVR) |         |        |       |  |  |

```

Index

```

Pin descriptions, ??–19-38 address bus, 19-19 byte strobes, 19-20 clock, 19-25 data bus, 19-19 dynamic data bus sizing, 19-19 general-purpose I/O ports, 19-24 interrupt request inputs, 19-23 JTAG test access port and BDM debug port, 19-35-19-37 operating mode configuration, 19-37 PLI TDM ports, 19-30-19-35 power supply, 19-38 QSPI signals, 19-29-?? **RSTI**, 19-23 SDRAM bank selects, 19-23 clock enable, 19-22 column address strobe, 19-22 row address 10, 19-23 row address strobe, 19-22 write enable, 19-22 UART0 module signals, 19-24-19-25 USB module signals and PA, 19-25-19-27 Pipelines instruction fetch, 2-2 operand execution, 2-2 PLIC aperiodic status register, 13-23 application examples, 13-35-13-42 automatic echo mode, 13-9 B1 data receive registers, 13-15 transmit registers, 13-17 B2 data receive registers, 13-16 transmit registers, 13-17 **B-Channel** HDLC encoded data, 13-6 unencoded data, 13-5 clock select register, 13-34 clock synthesis, 13-11 D data receive registers, 13-16 transmit registers, 13-18 **D**-Channel HDLC encoded data, 13-6 unencoded data, 13-7 D-Channel request register, 13-32 D-Channel status register, 13-31 frame sync synthesis, 13-13 GCI C/I channel receive registers, 13-28 transmit registers, 13-29 transmit status register, 13-30 GCI interrupts aperiodic status, 13-10

GCI monitor channel receive registers, 13-24 transmit abort register, 13-26 transmit registers, 13-25 transmit status register, 13-27 GCI/IDL B- and D-Channel receive data registers, 13-3 transmit data registers, 13-4 B- and D-Channel bit alignment, 13-5 block. 13-3 D-Channel contention, 13-8 looping modes, 13-8 periodic frame interrupts, 13-9 initialization, 13-35 interrupt configuration example, 13-37 registers, 13-20 interrupt control, 13-11 introduction, 13-1 local loopback mode, 13-9 loopback control register, 13-20 periodic status registers, 13-22 port configuration example, 13-35 registers, 13-18 register memory map, 13-13 registers, general, 13-15 remote loopback mode, 13-9 super frame sync generation, 13-13 sync delay registers, 13-33 timing generator, 13-11 Ports parallel input/output, 1-6 Power management registers, 6-7 Program counter, 2-6 Programming model PWM, 18-2 **OSPI**, 14-9 Programming models Ethernet. 11-10 instruction cache, 4-12 MAC, 2-7 overview, 2-4 ROM, 4-5 SIM, 6-2 SRAM, 4-2 supervisor, 2-7, 2-7 user, 2-4 PST outputs, 5-3 PULSE instruction, 5-3 **PWM** control register, 18-3 operation, 18-2 overview, 18-1