Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 100MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 24kB                                                                    |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 3.30V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-LBGA                                                                |

| Supplier Device Package | 196-LBGA (15x15)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spakdsp303vl100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.4 Clock

Table 1-4. Clock Signals

| Signal<br>Name | Туре   | State<br>During<br>Reset | Signal Description                                                                                                                           |

|----------------|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL          | Input  | Input                    | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                   |

| XTAL           | Output | Chip-driven              | Crystal Output—Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

# 1.5 PLL

Table 1-5. Phase-Locked Loop Signals

| Signal<br>Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                               |

|----------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT         | Output | Chip-driven           | Clock Output—Provides an output clock synchronized to the internal core clock phase.                                                                                                             |

|                |        |                       | If the PLL is enabled and both the multiplication and division factors equal one, then CLKOUT is also synchronized to EXTAL.                                                                     |

|                |        |                       | If the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.                                                                                                                     |

| PCAP           | Input  | Input                 | <b>PLL Capacitor</b> —An input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to $V_{CCP}$ .                                  |

|                |        |                       | If the PLL is not used, PCAP can be tied to $V_{\text{CC}}$ , GND, or left floating.                                                                                                             |

| PINIT          | Input  | Input                 | PLL Initial—During assertion of RESET, the value of PINIT is written into the PLL enable (PEN) bit of the PLL control (PCTL) register, determining whether the PLL is enabled or disabled.       |

| NMI            | Input  |                       | Nonmaskable Interrupt—After RESET deassertion and during normal instruction processing, this Schmitt-trigger input is the negative-edge-triggered NMI request internally synchronized to CLKOUT. |

|                |        |                       | Note: PINIT/NMI can tolerate 5 V.                                                                                                                                                                |

## 1.8 Host Interface (HI08)

The HI08 provides a fast, 8-bit, parallel data port that connects directly to the host bus. The HI08 supports a variety of standard buses and connects directly to a number of industry-standard microcomputers, microprocessors, DSPs, and DMA hardware.

## 1.8.4 Host Port Usage Considerations

Asynchronous write to transmit

Asynchronous write to host

byte registers

Careful synchronization is required when the system reads multiple-bit registers that are written by another asynchronous system. This is a common problem when two asynchronous systems are connected (as they are in the Host port). The considerations for proper operation are discussed in **Table 1-10**.

| Action         | Description                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| byte registers | When reading the receive byte registers, Receive register High (RXH), Receive register Middle (RXM), or Receive register Low (RXL), the host interface programmer should use interrupts or poll the Receive register Data Full (RXDF) flag that indicates data is available. This assures that the data in the receive byte registers is valid. |

Table 1-10.

Host Port Usage Considerations

The host interface programmer should not write to the transmit byte registers,

The host interface programmer must change the Host Vector (HV) register only

when the Host Command bit (HC) is clear. This practice guarantees that the DSP

registers transfer valid data to the Host Receive (HRX) register.

Transmit register High (TXH), Transmit register Middle (TXM), or Transmit register Low (TXL), unless the Transmit register Data Empty (TXDE) bit is set indicating that the transmit byte registers are empty. This guarantees that the transmit byte

# 1.8.5 Host Port Configuration

vector

HI08 signal functions vary according to the programmed configuration of the interface as determined by the 16 bits in the HI08 Port Control Register.

interrupt control logic receives a stable vector.

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                        |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H[0-7]      | Input/Output    | Ignored Input                        | <b>Host Data</b> —When the HI08 is programmed to interface with a non-multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional Data bus.                    |

| HAD[0-7]    | Input/Output    |                                      | <b>Host Address</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional multiplexed Address/Data bus. |

| PB[0-7]     | Input or Output |                                      | Port B 0–7—When the HI08 is configured as GPIO through the HI08 Port Control Register, these signals are individually programmed as inputs or outputs through the HI08 Data Direction Register.           |

Table 1-11. Host Interface

Table 1-11. Host Interface (Continued)

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRW         | Input           | Ignored Input                        | Host Read/Write—When the HI08 is programmed to interface with a single-data-strobe host bus and the HI function is selected, this signal is the Host Read/Write (HRW) input.                                                                                                                                                                                                      |

| HRD/HRD     | Input           |                                      | Host Read Data—When the HI08 is programmed to interface with a double-data-strobe host bus and the HI function is selected, this signal is the HRD strobe Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HRD) after reset.                                                                                               |

| PB11        | Input or Output |                                      | Port B 11—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                                      |

| HDS/HDS     | Input           | Ignored Input                        | Host Data Strobe—When the HI08 is programmed to interface with a single-data-strobe host bus and the HI function is selected, this signal is the host data strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HDS) following reset.                                                                             |

| HWR/HWR     | Input           |                                      | Host Write Data—When the HI08 is programmed to interface with a double-data-strobe host bus and the HI function is selected, this signal is the host write data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HWR) following reset.                                                                        |

| PB12        | Input or Output |                                      | Port B 12—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                                      |

| HREQ/HREQ   | Output          | Ignored Input                        | Host Request—When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host request (HREQ) output. The polarity of the host request is programmable but is configured as active-low (HREQ) following reset. The host request may be programmed as a driven or open-drain output.                           |

| HTRQ/HTRQ   | Output          |                                      | <b>Transmit Host Request</b> —When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the transmit host request (HTRQ) output. The polarity of the host request is programmable but is configured as active-low (HTRQ) following reset. The host request may be programmed as a driven or open-drain output. |

| PB14        | Input or Output |                                      | Port B 14—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                                      |

Table 1-11. Host Interface (Continued)

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HACK/HACK   | Input           | Ignored Input                        | Host Acknowledge—When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host acknowledge (HACK) Schmitt-trigger input. The polarity of the host acknowledge is programmable but is configured as active-low (HACK) after reset.                                                           |

| HRRQ/HRRQ   | Output          |                                      | Receive Host Request—When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the receive host request (HRRQ) output. The polarity of the host request is programmable but is configured as active-low (HRRQ) after reset. The host request may be programmed as a driven or open-drain output. |

| PB15        | Input or Output |                                      | Port B 15—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                        |

Notes: 1.

- 1. In the Stop state, the signal maintains the last state as follows:

- If the last state is input, the signal is an ignored input.

- If the last state is output, the signal is tri-stated.

- 2. The Wait processing state does not affect the signal state.

- 3. All inputs are 5 V tolerant.

### Chapter 2

Specifications

### 2.1 Introduction

The DSP56303 is fabricated in high-density CMOS with Transistor-Transistor Logic (TTL) compatible inputs and outputs.

## 2.2 Maximum Ratings

#### **CAUTION**

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or V<sub>CC</sub>).

**Note:** In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the

same device that has a "minimum" value for another specification; adding a maximum to a

minimum represents a condition that can never exist.

## 2.5 DC Electrical Characteristics

Table 2-3. DC Electrical Characteristics<sup>6</sup>

| Characteristics                                                                                                                                    | Symbol                                                   | Min                                 | Тур               | Max                                        | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|-------------------|--------------------------------------------|----------------------|

| Supply voltage                                                                                                                                     | V <sub>CC</sub>                                          | 3.0                                 | 3.3               | 3.6                                        | V                    |

| Input high voltage  • D[0–23], BG, BB, TA  • MOD¹/IRQ¹, RESET, PINIT/NMI and all JTAG/ESSI/SCI/Timer/HI08 pins  • EXTAL <sup>8</sup>               | V <sub>IH</sub><br>V <sub>IHP</sub>                      | 2.0<br>2.0<br>0.8 × V <sub>CC</sub> | _<br>_<br>_       | V <sub>CC</sub><br>5.25<br>V <sub>CC</sub> | V<br>V               |

| Input low voltage  • D[0–23], BG, BB, TA, MOD¹/IRQ¹, RESET, PINIT  • All JTAG/ESSI/SCI/Timer/HI08 pins  • EXTAL <sup>8</sup>                       | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub>  | -0.3<br>-0.3<br>-0.3                | _<br>_<br>_       | 0.8<br>0.8<br>0.2 × V <sub>CC</sub>        | V<br>V<br>V          |

| Input leakage current                                                                                                                              | I <sub>IN</sub>                                          | -10                                 | _                 | 10                                         | μΑ                   |

| High impedance (off-state) input current (@ 2.4 V / 0.4 V)                                                                                         | I <sub>TSI</sub>                                         | -10                                 | _                 | 10                                         | μΑ                   |

| Output high voltage  • TTL $(I_{OH} = -0.4 \text{ mA})^{5,7}$ • CMOS $(I_{OH} = -10 \mu\text{A})^{5}$                                              | V <sub>OH</sub>                                          | 2.4<br>V <sub>CC</sub> – 0.01       | _                 | _<br>_                                     | V<br>V               |

| Output low voltage<br>• TTL ( $I_{OL}$ = 1.6 mA, open-drain pins $I_{OL}$ = 6.7 mA) <sup>5,7</sup><br>• CMOS ( $I_{OL}$ = 10 $\mu$ A) <sup>5</sup> | V <sub>OL</sub>                                          | _<br>_                              | _                 | 0.4<br>0.01                                | V<br>V               |

| Internal supply current <sup>2</sup> :  In Normal mode  In Wait mode <sup>3</sup> In Stop mode <sup>4</sup> PLL supply current                     | I <sub>CCI</sub><br>I <sub>CCW</sub><br>I <sub>CCS</sub> | _<br>_<br>_                         | 127<br>7.5<br>100 | <br><br><br>2.5                            | mA<br>mA<br>μA<br>mA |

| Input capacitance <sup>5</sup>                                                                                                                     | C <sub>IN</sub>                                          | _                                   |                   | 10                                         | pF                   |

Notes:

- 1. Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and MODD/IRQD pins.

- 2. Power Consumption Considerations on page Section 4-3 provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks (see Appendix A). The power consumption numbers in this specification are 90 percent of the measured results of this benchmark. This reflects typical DSP applications. Typical internal supply current is measured with V<sub>CC</sub> = 3.3 V at T<sub>J</sub> = 100°C.

- 3. In order to obtain these results, all inputs must be terminated (that is, not allowed to float).

- 4. In order to obtain these results, all inputs that are not disconnected at Stop mode must be terminated (that is, not allowed to float). PLL and XTAL signals are disabled during Stop state.

- 5. Periodically sampled and not 100 percent tested.

- **6.**  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ;  $T_J = -40 ^{\circ}\text{C}$  to +100  $^{\circ}\text{C}$ ,  $C_L = 50 \text{ pF}$

- 7. This characteristic does not apply to XTAL and PCAP.

- 8. Driving EXTAL to the low  $V_{IHX}$  or the high  $V_{ILX}$  value may cause additional power consumption (DC current). To minimize power consumption, the minimum  $V_{IHX}$  should be no lower than  $0.9 \times V_{CC}$  and the maximum  $V_{ILX}$  should be no higher than  $0.1 \times V_{CC}$ .

## 2.6 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a  $V_{IL}$  maximum of 0.3 V and a  $V_{IH}$  minimum of 2.4 V for all pins except EXTAL, which is tested using the input levels shown in Note 6 of the previous table. AC timing specifications, which are referenced to a device input signal, are measured in production with respect to the 50 percent point of the respective input signal transition. DSP56303 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.4 V and 2.4 V, respectively.

**Note:** Although the minimum value for the frequency of EXTAL is 0 MHz, the device AC test conditions are 15 MHz and rated speed.

### 2.6.1 Internal Clocks

Table 2-4. Internal Clocks, CLKOUT

| Characteristics                                                                                                          | Symbol           |                                                                                                                                                                                    | Expression <sup>1, 2</sup>                                           |                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cital acteristics                                                                                                        | Syllibol         | Min                                                                                                                                                                                | Тур                                                                  | Max                                                                                                                                                                                  |

| Internal operation frequency and CLKOUT with PLL enabled                                                                 | f                | _                                                                                                                                                                                  | $ \begin{array}{c} (Ef \times MF) / \\ (PDF \times DF) \end{array} $ | _                                                                                                                                                                                    |

| Internal operation frequency and CLKOUT with PLL disabled                                                                | f                | _                                                                                                                                                                                  | Ef/2                                                                 | _                                                                                                                                                                                    |

| Internal clock and CLKOUT high period  • With PLL disabled  • With PLL enabled and MF ≤ 4  • With PLL enabled and MF > 4 | T <sub>H</sub>   | $\begin{array}{c}\\ 0.49 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF}\\ 0.47 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF} \end{array}$ | ET <sub>C</sub><br>—<br>—                                            | $\begin{array}{c} -\\ 0.51 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF}\\ 0.53 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF} \end{array}$ |

| Internal clock and CLKOUT low period  • With PLL disabled  • With PLL enabled and MF ≤ 4  • With PLL enabled and MF > 4  | TL               | $\begin{array}{c}\\ 0.49\times \mathrm{ET_{C}}\times\\ \mathrm{PDF}\times \mathrm{DF/MF}\\ 0.47\times \mathrm{ET_{C}}\times\\ \mathrm{PDF}\times \mathrm{DF/MF} \end{array}$       | ET <sub>C</sub><br>—                                                 | $\begin{array}{c} -\\ 0.51 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF}\\ 0.53 \times \mathrm{ET_{C}} \times\\ \mathrm{PDF} \times \mathrm{DF/MF} \end{array}$ |

| Internal clock and CLKOUT cycle time with PLL enabled                                                                    | T <sub>C</sub>   | _                                                                                                                                                                                  | ET <sub>C</sub> × PDF ×<br>DF/MF                                     | _                                                                                                                                                                                    |

| Internal clock and CLKOUT cycle time with PLL disabled                                                                   | T <sub>C</sub>   | _                                                                                                                                                                                  | 2 × ET <sub>C</sub>                                                  | _                                                                                                                                                                                    |

| Instruction cycle time                                                                                                   | I <sub>CYC</sub> | _                                                                                                                                                                                  | T <sub>C</sub>                                                       | _                                                                                                                                                                                    |

Notes: 1. DF = Division Factor; Ef = External frequency; ET<sub>C</sub> = External clock cycle; MF = Multiplication Factor; PDF = Predivision Factor; T<sub>C</sub> = internal clock cycle

See the PLL and Clock Generation section in the DSP56300 Family Manual for a detailed discussion of the PLL.

**Table 2-7.** Reset, Stop, Mode Select, and Interrupt Timing<sup>6</sup> (Continued)

| Na  | Characteristics   | Evaracion  | 100 | MHz | l lnit |   |

|-----|-------------------|------------|-----|-----|--------|---|

| No. | Cital acteristics | Expression | Min | Max | Unit   | l |

Notes:

- 1. When fast interrupts are used and IRQA, IRQB, IRQC, and IRQD are defined as level-sensitive, timings 19 through 21 apply to prevent multiple interrupt service. To avoid these timing restrictions, the deasserted Edge-triggered mode is recommended when fast interrupts are used. Long interrupts are recommended for Level-sensitive mode.

- 2. This timing depends on several settings:

- For PLL disable, using internal oscillator (PLL Control Register (PCTL) Bit 16 = 0) and oscillator disabled during Stop (PCTL Bit 17 = 0), a stabilization delay is required to assure that the oscillator is stable before programs are executed. Resetting the Stop delay (Operating Mode Register Bit 6 = 0) provides the proper delay. While Operating Mode Register Bit 6 = 1 can be set, it is not recommended, and these specifications do not guarantee timings for that case.

- For PLL disable, using internal oscillator (PCTL Bit 16 = 0) and oscillator enabled during Stop (PCTL Bit 17=1), no stabilization delay is required and recovery is minimal (Operating Mode Register Bit 6 setting is ignored).

- For PLL disable, using external clock (PCTL Bit 16 = 1), no stabilization delay is required and recovery time is defined by the PCTL Bit 17 and Operating Mode Register Bit 6 settings.

- For PLL enable, if PCTL Bit 17 is 0, the PLL is shutdown during Stop. Recovering from Stop requires the PLL to get locked. The PLL lock procedure duration, PLL Lock Cycles (PLC), may be in the range of 0 to 1000 cycles. This procedure occurs in parallel with the stop delay counter, and stop recovery ends when the last of these two events occurs. The stop delay counter completes count or PLL lock procedure completion.

- PLC value for PLL disable is 0.

- The maximum value for ET<sub>C</sub> is 4096 (maximum MF) divided by the desired internal frequency (that is, for 66 MHz it is 4096/66 MHz = 62 μs). During the stabilization period, T<sub>C</sub>, T<sub>H</sub>, and T<sub>L</sub> is not constant, and their width may vary, so timing may vary as well.

- 3. Periodically sampled and not 100 percent tested.

- 4. Value depends on clock source:

- For an external clock generator, RESET duration is measured while RESET is asserted, V<sub>CC</sub> is valid, and the EXTAL input is active and valid.

- ullet For an internal oscillator,  $\overline{\text{RESET}}$  duration is measured while  $\overline{\text{RESET}}$  is asserted and  $V_{CC}$  is valid. The specified timing reflects the crystal oscillator stabilization time after power-up. This number is affected both by the specifications of the crystal and other components connected to the oscillator and reflects worst case conditions.

- When the V<sub>CC</sub> is valid, but the other "required RESET duration" conditions (as specified above) have not been yet met, the device circuitry is in an uninitialized state that can result in significant power consumption and heat-up. Designs should minimize this state to the shortest possible duration.

- 5. If PLL does not lose lock.

- **6.**  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ;  $T_J = -40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $C_L = 50 \text{ pF}$ .

- 7. WS = number of wait states (measured in clock cycles, number of  $T_C$ ).

- 8. Use the expression to compute a maximum value.

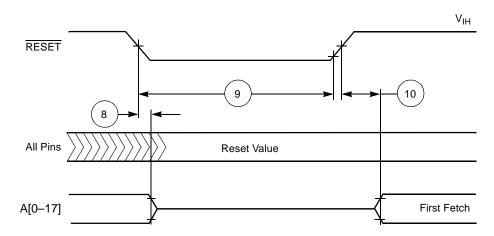

Figure 2-3. Reset Timing

Table 2-8. SRAM Read and Write Accesses (Continued)

| Na  | Characteristics                                   | Comple of | Everyonian1                                      | 100  | MHz  | l lm!t |

|-----|---------------------------------------------------|-----------|--------------------------------------------------|------|------|--------|

| No. | Characteristics                                   | Symbol    | Expression <sup>1</sup>                          | Min  | Max  | Unit   |

| 111 | WR deassertion to data high impedance             | _         | $0.25 \times T_{C} + 0.2$<br>[1 \le WS \le 3]    | _    | 2.7  | ns     |

|     |                                                   |           | 1.25 × TC + 0.2<br>[4 ≤ WS ≤ 7]                  | _    | 12.7 | ns     |

|     |                                                   |           | $2.25 \times T_{C} + 0.2$ [WS > 8]               | _    | 22.7 | ns     |

| 112 | Previous RD deassertion to data active (write)    | _         | $1.25 \times T_{C} - 4.0$ [1 $\leq$ WS $\leq$ 3] | 8.5  | _    | ns     |

|     |                                                   |           | $2.25 \times T_{C} - 4.0$ $[4 \le WS \le 7]$     | 18.5 | _    | ns     |

|     |                                                   |           | $3.25 \times T_{C} - 4.0$ [WS > 8]               | 28.5 | _    | ns     |

| 113 | RD deassertion time                               | _         | $0.75 \times T_{C} - 4.0$<br>[1 \le WS \le 3]    | 3.5  | _    | ns     |

|     |                                                   |           | $1.75 \times T_{C} - 4.0$ $[4 \le WS \le 7]$     | 13.5 | _    | ns     |

|     |                                                   |           | $2.75 \times T_{C} - 4.0$ [WS \ge 8]             | 23.5 | _    | ns     |

| 114 | WR deassertion time                               | _         | $0.5 \times T_{C} - 4.0$ [WS = 1]                | 1.0  | _    | ns     |

|     |                                                   |           | $T_{C} - 4.0$ [2 \le WS \le 3]                   | 6.0  | _    | ns     |

|     |                                                   |           | $2.5 \times T_{C} - 4.0$<br>[4 \le WS \le 7]     | 21.0 | _    | ns     |

|     |                                                   |           | $3.5 \times T_C - 4.0$<br>[WS \ge 8]             | 31.0 | _    | ns     |

| 115 | Address valid to RD assertion                     | _         | $0.5 \times T_C - 4.0$                           | 1.0  | _    | ns     |

| 116 | RD assertion pulse width                          | _         | $(WS + 0.25) \times T_C - 4.0$                   | 8.5  | _    | ns     |

| 117 | RD deassertion to address not valid               | _         | $0.25 \times T_{C} - 2.0$ [1 $\leq$ WS $\leq$ 3] | 0.5  | _    | ns     |

|     |                                                   |           | 1.25 × $T_C$ – 2.0<br>[4 ≤ WS ≤ 7]               | 10.5 | _    | ns     |

|     |                                                   |           | $2.25 \times T_{C} - 2.0$ [WS $\geq 8$ ]         | 20.5 |      | ns     |

| 118 | TA setup before RD or WR deassertion <sup>4</sup> | _         | $0.25 \times T_{C} + 2.0$                        | 4.5  | _    | ns     |

| 119 | TA hold after RD or WR deassertion                | -         | _                                                | 0    | -    | ns     |

- Notes: 1. WS is the number of wait states specified in the BCR. An expression is used to compute the number listed as the minimum or maximum value, as appropriate.

- Timings 100, 107 are guaranteed by design, not tested.

- All timings for 100 MHz are measured from 0.5  $\times$  Vcc to 0.5  $\times$  Vcc.

- Timing 118 is relative to the deassertion edge of  $\overline{RD}$  or  $\overline{WR}$  even if  $\overline{TA}$  remains asserted.  $V_{CC}=3.3~V\pm0.3~V;$   $T_{J}=-40^{\circ}C$  to  $+100^{\circ}C,$   $C_{L}=50~pF$

**Table 2-12.** DRAM Out-of-Page and Refresh Timings, Fifteen Wait States<sup>1,2</sup> (Continued)

| No     |    | Characteristics                                                                                                | Cumbal | Expression <sup>3</sup> | 100 MHz                                                                                                                            |     | Unit |  |  |  |  |

|--------|----|----------------------------------------------------------------------------------------------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|--|--|--|--|

| No.    |    | Characteristics                                                                                                | Symbol | Expression              | Min                                                                                                                                | Max | Unit |  |  |  |  |

| Notes: | 1. | The number of wait states for an out-of-page access is specified in the DRAM Control Register.                 |        |                         |                                                                                                                                    |     |      |  |  |  |  |

|        | 2. | The refresh period is specified in the DRAM Control Register.                                                  |        |                         |                                                                                                                                    |     |      |  |  |  |  |

|        | 3. | Use the expression to compute the maximum or minimum value listed (or both if the expression includes $\pm$ ). |        |                         |                                                                                                                                    |     |      |  |  |  |  |

|        | 4. | Either t <sub>RCH</sub> or t <sub>RRH</sub> must be satisfied for read cycles.                                 |        |                         |                                                                                                                                    |     |      |  |  |  |  |

|        | 5. |                                                                                                                |        | , the restricted timing | RD deassertion always occurs after CAS deassertion; therefore, the restricted timing is t <sub>OFF</sub> and not t <sub>GZ</sub> . |     |      |  |  |  |  |

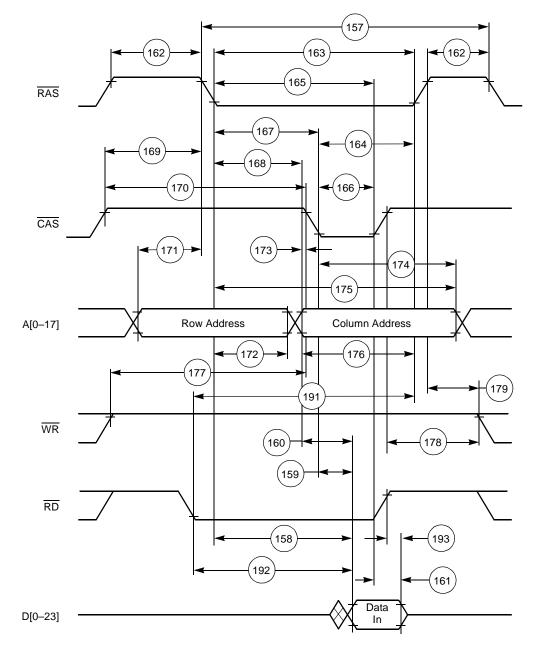

Figure 2-18. DRAM Out-of-Page Read Access

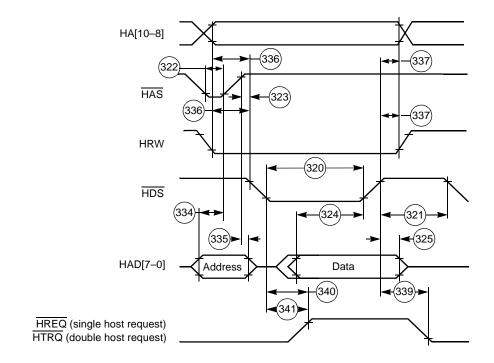

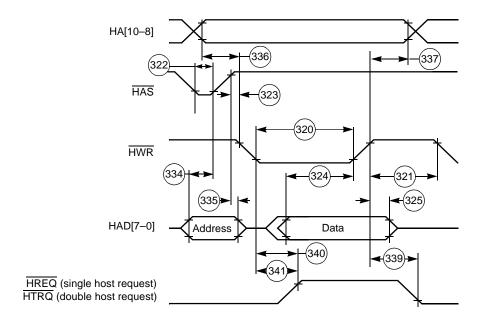

Figure 2-34. Write Timing Diagram, Multiplexed Bus, Single Data Strobe

Figure 2-35. Write Timing Diagram, Multiplexed Bus, Double Data Strobe

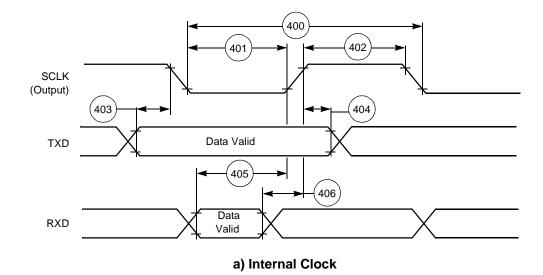

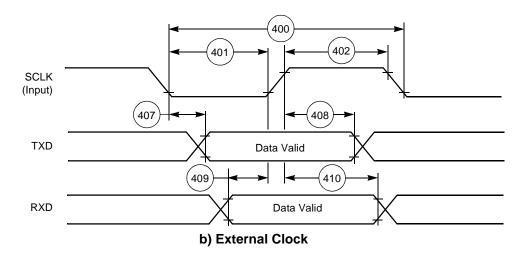

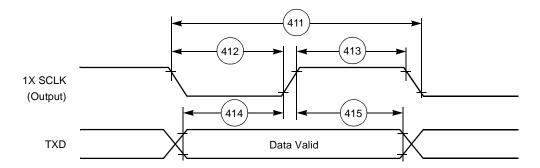

Figure 2-36. SCI Synchronous Mode Timing

Figure 2-37. SCI Asynchronous Mode Timing

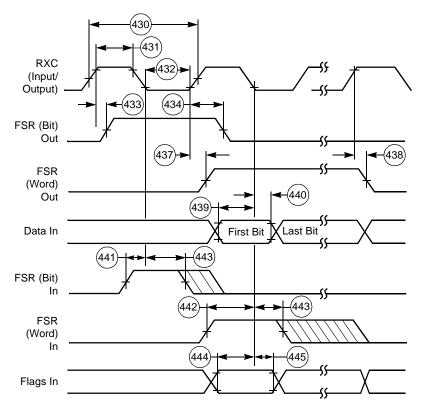

# 2.6.8 ESSI0/ESSI1 Timing

Table 2-18. ESSI Timings

| No. | Characteristics <sup>4, 5, 7</sup>                                   | Symbol             | Expression <sup>9</sup>                                   | 100 MHz      |              | Cond-              | Unit     |

|-----|----------------------------------------------------------------------|--------------------|-----------------------------------------------------------|--------------|--------------|--------------------|----------|

|     | Characteristics 7-7                                                  | Symbol             | Expression                                                | Min          | Max          | ition <sup>5</sup> | Unit     |

| 430 | Clock cycle <sup>1</sup>                                             | t <sub>SSICC</sub> | $\begin{array}{c} 3\times T_C \\ 4\times T_C \end{array}$ | 30.0<br>40.0 |              | x ck<br>i ck       | ns       |

| 431 | Clock high period     For internal clock     For external clock      |                    | 2 × T <sub>C</sub> - 10.0<br>1.5 × T <sub>C</sub>         | 10.0<br>15.0 |              |                    | ns<br>ns |

| 432 | Clock low period    For internal clock    For external clock         |                    | $2 \times T_{C} - 10.0$ $1.5 \times T_{C}$                | 10.0<br>15.0 | _<br>_       |                    | ns<br>ns |

| 433 | RXC rising edge to FSR out (bit-length) high                         |                    |                                                           | _<br>_       | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 434 | RXC rising edge to FSR out (bit-length) low                          |                    |                                                           | _            | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 435 | RXC rising edge to FSR out (word-length-relative) high <sup>2</sup>  |                    |                                                           | _<br>_       | 39.0<br>37.0 | x ck<br>i ck a     | ns       |

| 436 | RXC rising edge to FSR out (word-length-relative) low <sup>2</sup>   |                    |                                                           | _            | 39.0<br>37.0 | x ck<br>i ck a     | ns       |

| 437 | RXC rising edge to FSR out (word-length) high                        |                    |                                                           | _<br>_       | 36.0<br>21.0 | x ck<br>i ck a     | ns       |

| 438 | RXC rising edge to FSR out (word-length) low                         |                    |                                                           | _<br>_       | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 439 | Data in setup time before RXC (SCK in Synchronous mode) falling edge |                    |                                                           | 10.0<br>19.0 |              | x ck<br>i ck       | ns       |

| 440 | Data in hold time after RXC falling edge                             |                    |                                                           | 5.0<br>3.0   | _            | x ck<br>i ck       | ns       |

| 441 | FSR input (bl, wr) high before RXC falling edge <sup>2</sup>         |                    |                                                           | 1.0<br>23.0  | _            | x ck<br>i ck a     | ns       |

| 442 | FSR input (wl) high before RXC falling edge                          |                    |                                                           | 3.5<br>23.0  | _            | x ck<br>i ck a     | ns       |

| 443 | FSR input hold time after RXC falling edge                           |                    |                                                           | 3.0<br>0.0   | _            | x ck<br>i ck a     | ns       |

| 444 | Flags input setup before RXC falling edge                            |                    |                                                           | 5.5<br>19.0  | _            | x ck<br>i ck s     | ns       |

| 445 | Flags input hold time after RXC falling edge                         |                    |                                                           | 6.0<br>0.0   | _            | x ck<br>i ck s     | ns       |

| 446 | TXC rising edge to FST out (bit-length) high                         |                    |                                                           | _            | 29.0<br>15.0 | x ck<br>i ck       | ns       |

| 447 | TXC rising edge to FST out (bit-length) low                          |                    |                                                           | _            | 31.0<br>17.0 | x ck<br>i ck       | ns       |

| 448 | TXC rising edge to FST out (word-length-relative) high <sup>2</sup>  |                    |                                                           | _<br>_       | 31.0<br>17.0 | x ck<br>i ck       | ns       |

| 449 | TXC rising edge to FST out (word-length-relative) low <sup>2</sup>   |                    |                                                           | _            | 33.0<br>19.0 | x ck<br>i ck       | ns       |

Figure 2-39. ESSI Receiver Timing

## 3.2 TQFP Package Description

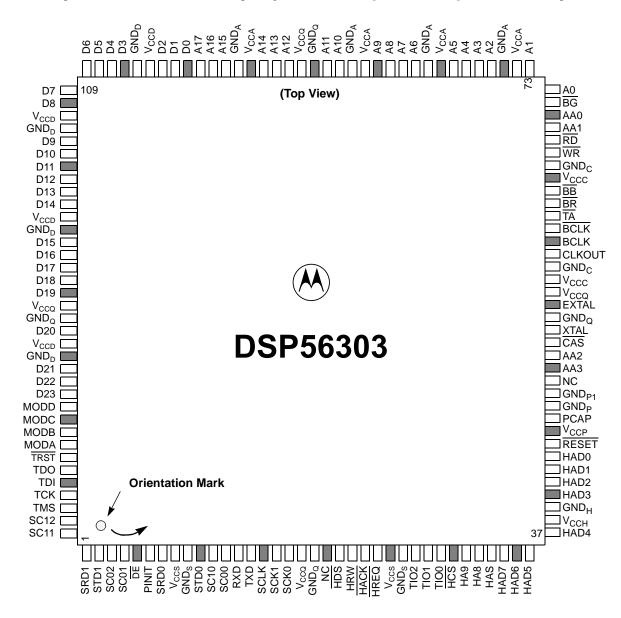

Top and bottom views of the TQFP package are shown in Figure 3-1 and Figure 3-2 with their pin-outs.

**Notes:** Because of size constraints in this figure, only one name is shown for multiplexed pins. Refer to **Table 3-1** and **Table 3-2** for detailed information about pin functions and signal names.

Figure 3-1. DSP56303 Thin Quad Flat Pack (TQFP), Top View

Table 3-2.

DSP56303 TQFP Signal Identification by Name

| Signal Name | Pin<br>No. | Signal Name | Pin<br>No. | Signal Name       | Pin<br>No. |

|-------------|------------|-------------|------------|-------------------|------------|

| A0          | 72         | BG          | 71         | D7                | 109        |

| A1          | 73         | BR          | 63         | D8                | 110        |

| A10         | 88         | CAS         | 52         | D9                | 113        |

| A11         | 89         | CLKOUT      | 59         | DE                | 5          |

| A12         | 92         | D0          | 100        | EXTAL             | 55         |

| A13         | 93         | D1          | 101        | GND <sub>A</sub>  | 75         |

| A14         | 94         | D10         | 114        | GND <sub>A</sub>  | 81         |

| A15         | 97         | D11         | 115        | GND <sub>A</sub>  | 87         |

| A16         | 98         | D12         | 116        | GND <sub>A</sub>  | 96         |

| A17         | 99         | D13         | 117        | GND <sub>C</sub>  | 58         |

| A2          | 76         | D14         | 118        | GND <sub>C</sub>  | 66         |

| A3          | 77         | D15         | 121        | GND <sub>D</sub>  | 104        |

| A4          | 78         | D16         | 122        | GND <sub>D</sub>  | 112        |

| A5          | 79         | D17         | 123        | GND <sub>D</sub>  | 120        |

| A6          | 82         | D18         | 124        | GND <sub>D</sub>  | 130        |

| A7          | 83         | D19         | 125        | GND <sub>H</sub>  | 39         |

| A8          | 84         | D2          | 102        | GND <sub>P</sub>  | 47         |

| A9          | 85         | D20         | 128        | GND <sub>P1</sub> | 48         |

| AA0         | 70         | D21         | 131        | GND <sub>Q</sub>  | 19         |

| AA1         | 69         | D22         | 132        | GND <sub>Q</sub>  | 54         |

| AA2         | 51         | D23         | 133        | GND <sub>Q</sub>  | 90         |

| AA3         | 50         | D3          | 105        | GND <sub>Q</sub>  | 127        |

| BB          | 64         | D4          | 106        | GND <sub>S</sub>  | 9          |

| BCLK        | 60         | D5          | 107        | GND <sub>S</sub>  | 26         |

| BCLK        | 61         | D6          | 108        | H0                | 43         |

### **TQFP Package Description**

Table 3-2.

DSP56303 TQFP Signal Identification by Name (Continued)

| Signal Name | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name      | Pin<br>No. |

|-------------|------------|------------------|------------|------------------|------------|

| RAS0        | 70         | SRD1             | 1          | V <sub>CCC</sub> | 57         |

| RAS1        | 69         | STD0             | 10         | V <sub>CCC</sub> | 65         |

| RAS2        | 51         | STD1             | 2          | V <sub>CCD</sub> | 103        |

| RAS3        | 50         | TA               | 62         | V <sub>CCD</sub> | 111        |

| RD          | 68         | TCK              | 141        | V <sub>CCD</sub> | 119        |

| RESET       | 44         | TDI              | 140        | V <sub>CCD</sub> | 129        |

| RXD         | 13         | TDO              | 139        | V <sub>CCH</sub> | 38         |

| SC00        | 12         | TIO0             | 29         | V <sub>CCP</sub> | 45         |

| SC01        | 4          | TIO1             | 28         | V <sub>CCQ</sub> | 18         |

| SC02        | 3          | TIO2             | 27         | V <sub>CCQ</sub> | 56         |

| SC10        | 11         | TMS              | 142        | V <sub>CCQ</sub> | 91         |

| SC11        | 144        | TRST             | 138        | V <sub>CCQ</sub> | 126        |

| SC12        | 143        | TXD              | 14         | V <sub>CCS</sub> | 8          |

| SCK0        | 17         | V <sub>CCA</sub> | 74         | V <sub>CCS</sub> | 25         |

| SCK1        | 16         | V <sub>CCA</sub> | 80         | WR               | 67         |

| SCLK        | 15         | V <sub>CCA</sub> | 86         | XTAL             | 53         |

| SRD0        | 7          | V <sub>CCA</sub> | 95         |                  |            |

## 4.4 PLL Performance Issues

The following explanations should be considered as general observations on expected PLL behavior. There is no test that replicates these exact numbers. These observations were measured on a limited number of parts and were not verified over the entire temperature and voltage ranges.

### 4.4.1 Phase Skew Performance

The phase skew of the PLL is defined as the time difference between the falling edges of EXTAL and CLKOUT for a given capacitive load on CLKOUT, over the entire process, temperature and voltage ranges. As defined in **Figure 2-2**, *External Clock Timing*, on page 2-5 for input frequencies greater than 15 MHz and the MF  $\leq$  4, this skew is greater than or equal to 0.0 ns and less than 1.8 ns; otherwise, this skew is not guaranteed. However, for MF < 10 and input frequencies greater than 10 MHz, this skew is between -1.4 ns and +3.2 ns.

### 4.4.2 Phase Jitter Performance

The phase jitter of the PLL is defined as the variations in the skew between the falling edges of EXTAL and CLKOUT for a given device in specific temperature, voltage, input frequency, MF, and capacitive load on CLKOUT. These variations are a result of the PLL locking mechanism. For input frequencies greater than 15 MHz and MF  $\leq$  4, this jitter is less than  $\pm$ 0.6 ns; otherwise, this jitter is not guaranteed. However, for MF < 10 and input frequencies greater than 10 MHz, this jitter is less than  $\pm$ 2 ns.

## 4.4.3 Frequency Jitter Performance

The frequency jitter of the PLL is defined as the variation of the frequency of CLKOUT. For small MF (MF < 10) this jitter is smaller than 0.5 percent. For mid-range MF (10 < MF < 500) this jitter is between 0.5 percent and approximately 2 percent. For large MF (MF > 500), the frequency jitter is 2–3 percent.

## 4.5 Input (EXTAL) Jitter Requirements

The allowed jitter on the frequency of EXTAL is 0.5 percent. If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the allowed jitter can be 2 percent. The phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed values.

```

interrupt signals 1-8

W

JTAG signals 1-18

mode control 1-8

Wait mode iv

OnCE signals 1-18

World Wide Web iv

PLL signals 1-4

X

Reset timing 2-7, 2-9

synchronous 2-10

X-data RAM iii

ROM, bootstrap iii

Y

S

Y-data RAM iii

Serial Communication Interface (SCI) iii, 1-1,

1-2, 1-16

Asynchronous mode timing 2-38

Synchronous mode timing 2-38

signal groupings 1-1

signals 1-1

functional grouping 1-2

Single Data Strobe 1-2

SRAM

read access 2-15

support iv

write access 2-15

Stop mode iv

Stop state

recovery from 2-12

Stop timing 2-7

supply voltage 2-2

Switch mode iii

synchronous bus timings

SRAM

2 wait states 2-26

SRAM 1 wait state (BCR controlled) 2-26

synchronous interrupt from Wait state timing 2-11

synchronous Reset timing 2-10

Т

target applications iv

Test Access Port (TAP) iii

timing diagram 2-46

Test Clock (TCLK) input timing diagram 2-45

thermal

design considerations 4-1

Timer

event input restrictions 2-43

Timers 1-1, 1-2, 1-17

interrupt generation 2-43

TQFP 3-1

mechanical drawing 3-9

pin list by name 3-6

pin list by number 3-4

pin-out drawing (bottom) 3-3

pin-out drawing (top) 3-2

```

### **Ordering Information**

Consult a Motorola Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Part     | Supply<br>Voltage | Package Type                                   | Pin<br>Count | Core<br>Frequency<br>(MHz) | Order Number  |

|----------|-------------------|------------------------------------------------|--------------|----------------------------|---------------|

| DSP56303 | 3.3 V I/O         | Thin Quad Flat Pack (TQFP)                     | 144          | 100                        | DSP56303PV100 |

|          |                   | Molded Array Process-Ball Grid Array (MAP-BGA) | 196          | 100                        | DSP56303VF100 |

#### **HOW TO REACH US:**

#### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu Minato-ku, Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

#### **TECHNICAL INFORMATION CENTER:**

1-800-521-6274

#### HOME PAGE:

http://www.motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. OnCE and digital dna are trademarks of Motorola, Inc. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1996, 2002