#### NXP USA Inc. - SPAKXC309VL100A Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 100MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 24kB                                                                    |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 3.30V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-LBGA                                                                |

| Supplier Device Package | 196-LBGA (15x15)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spakxc309vl100a |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|            | DSP56303 Features                                    | iii |

|------------|------------------------------------------------------|-----|

|            | Target Applications                                  | iv  |

|            | Product Documentation                                | iv  |

| Chapter 1  | Signal/ Connection Descriptions                      |     |

| •          | 1.1 Signal Groupings                                 |     |

|            | 1.2 Power                                            |     |

|            | 1.3 Ground                                           |     |

|            | 1.4 Clock                                            |     |

|            | 1.5 PLL                                              |     |

|            | 1.6 External Memory Expansion Port (Port A)          |     |

|            | 1.7 Interrupt and Mode Control                       |     |

|            | 1.8 Host Interface (HI08)                            |     |

|            | 1.9 Enhanced Synchronous Serial Interface 0 (ESSI0)  |     |

|            | 1.10 Enhanced Synchronous Serial Interface 1 (ESSI1) |     |

|            | 1.11 Serial Communication Interface (SCI)            |     |

|            | 1.12 Timers                                          |     |

|            | 1.13 JTAG and OnCE Interface                         |     |

| Chapter 2  | Specifications                                       |     |

|            | 2.1 Introduction                                     |     |

|            | 2.2 Maximum Ratings                                  |     |

|            | 2.4 Thermal Characteristics                          |     |

|            | 2.5 DC Electrical Characteristics                    |     |

|            | 2.6 AC Electrical Characteristics                    |     |

| Chapter 3  | Packaging                                            |     |

|            | 3.1 Pin-Out and Package Information                  |     |

|            | 3.2 TQFP Package Description                         |     |

|            | 3.3 TQFP Package Mechanical Drawing                  |     |

|            | 3.4 MAP-BGA Package Description                      |     |

|            | 3.5 MAP-BGA Package Mechanical Drawing               |     |

| Chapter 4  | Design Considerations                                |     |

|            | 4.1 Thermal Design Considerations                    |     |

|            | 4.2 Electrical Design Considerations                 |     |

|            | 4.3 Power Consumption Considerations                 |     |

|            | 4.4 PLL Performance Issues                           |     |

|            | 4.5 Input (EXTAL) Jitter Requirements                |     |

| Appendix A | Power Consumption Benchmark                          |     |

Index

**Data Sheet Conventions**

| OVERBAR      | Used to indicate a signal that | is active when pulled low (F     | or example, the $\overline{RESET}$ pin is a | ctive when low.)                 |

|--------------|--------------------------------|----------------------------------|---------------------------------------------|----------------------------------|

| "asserted"   | Means that a high true (active | e high) signal is high or that a | a low true (active low) signal is I         | ow                               |

| "deasserted" | Means that a high true (active | e high) signal is low or that a  | low true (active low) signal is h           | igh                              |

| Examples:    | Signal/Symbol                  | Logic State                      | Signal State                                | Voltage                          |

|              | PIN                            | True                             | Asserted                                    | V <sub>IL</sub> /V <sub>OL</sub> |

|              | PIN                            | False                            | Deasserted                                  | V <sub>IH</sub> /V <sub>OH</sub> |

|              | PIN                            | True                             | Asserted                                    | V <sub>IH</sub> /V <sub>OH</sub> |

|              | PIN                            | False                            | Deasserted                                  | V <sub>IL</sub> /V <sub>OL</sub> |

Note: Values for V\_{IL}, V\_{OL}, V\_{IH}, and V\_{OH} are defined by individual product specifications.

# 1.4 Clock

### Table 1-4. Clock Signals

| Signal<br>Name | Туре   | State<br>During<br>Reset | Signal Description                                                                                                                                   |

|----------------|--------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL          | Input  | Input                    | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                           |

| XTAL           | Output | Chip-driven              | <b>Crystal Output</b> —Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

# 1.5 PLL

| Signal<br>Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                                       |

|----------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT         | Output | Chip-driven           | <b>Clock Output</b> —Provides an output clock synchronized to the internal core clock phase.                                                                                                             |

|                |        |                       | If the PLL is enabled and both the multiplication and division factors equal one, then CLKOUT is also synchronized to EXTAL.                                                                             |

|                |        |                       | If the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.                                                                                                                             |

| PCAP           | Input  | Input                 | <b>PLL Capacitor</b> —An input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to $V_{CCP}$ .                                          |

|                |        |                       | If the PLL is not used, PCAP can be tied to $V_{CC},$ GND, or left floating.                                                                                                                             |

| PINIT          | Input  | Input                 | <b>PLL Initial</b> —During assertion of RESET, the value of PINIT is written into the PLL enable (PEN) bit of the PLL control (PCTL) register, determining whether the PLL is enabled or disabled.       |

| NMI            | Input  |                       | <b>Nonmaskable Interrupt</b> —After RESET deassertion and during normal instruction processing, this Schmitt-trigger input is the negative-edge-triggered NMI request internally synchronized to CLKOUT. |

|                |        |                       | Note: PINIT/NMI can tolerate 5 V.                                                                                                                                                                        |

#### Table 1-5. Phase-Locked Loop Signals

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRW         | Input           | Ignored Input                        | <b>Host Read/Write</b> —When the HI08 is programmed to interface with a single-data-strobe host bus and the HI function is selected, this signal is the Host Read/Write (HRW) input.                                                                                                                                                                                              |

| HRD/HRD     | Input           |                                      | <b>Host Read Data</b> —When the HI08 is programmed to interface with a double-data-strobe host bus and the HI function is selected, this signal is the HRD strobe Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HRD) after reset.                                                                                       |

| PB11        | Input or Output |                                      | <b>Port B 11</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

| HDS/HDS     | Input           | Ignored Input                        | <b>Host Data Strobe</b> —When the HI08 is programmed to interface with a single-data-strobe host bus and the HI function is selected, this signal is the host data strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HDS) following reset.                                                                     |

| HWR/HWR     | Input           |                                      | <b>Host Write Data</b> —When the HI08 is programmed to interface with a double-data-strobe host bus and the HI function is selected, this signal is the host write data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HWR) following reset.                                                                |

| PB12        | Input or Output |                                      | <b>Port B 12</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

| HREQ/HREQ   | Output          | Ignored Input                        | <b>Host Request</b> —When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host request (HREQ) output. The polarity of the host request is programmable but is configured as active-low (HREQ) following reset. The host request may be programmed as a driven or open-drain output.                   |

| HTRQ/HTRQ   | Output          |                                      | <b>Transmit Host Request</b> —When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the transmit host request (HTRQ) output. The polarity of the host request is programmable but is configured as active-low (HTRQ) following reset. The host request may be programmed as a driven or open-drain output. |

| PB14        | Input or Output |                                      | <b>Port B 14</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

Table 1-11. Host Interface (Continued)

| Signal Name | Туре                                         | State During<br>Reset <sup>1,2</sup>                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC12        | Input/Output                                 | Ignored Input                                                  | Serial Control Signal 2—The frame sync for both the transmitter<br>and receiver in synchronous mode and for the transmitter only in<br>asynchronous mode. When configured as an output, this signal is<br>the internally generated frame sync signal. When configured as an<br>input, this signal receives an external frame sync signal for the<br>transmitter (and the receiver in synchronous operation). |

| PD2         | Input or Output                              |                                                                | <b>Port D 2</b> —The default configuration following reset is GPIO input PD2. When configured as PD2, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SC12 through the Port D Control Register.                                                                                                                                         |

| SCK1        | Input/Output                                 | Ignored Input                                                  | <b>Serial Clock</b> —Provides the serial bit rate clock for the ESSI. The SCK1 is a clock input or output used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                                                                                        |

|             |                                              |                                                                | Although an external serial clock can be independent of and<br>asynchronous to the DSP system clock, it must exceed the<br>minimum clock cycle time of 6T (that is, the system clock<br>frequency must be at least three times the external ESSI clock<br>frequency). The ESSI needs at least three DSP phases inside<br>each half of the serial clock.                                                      |

| PD3         | Input or Output                              |                                                                | <b>Port D 3</b> —The default configuration following reset is GPIO input PD3. When configured as PD3, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SCK1 through the Port D Control Register.                                                                                                                                         |

| SRD1        | Input                                        | Ignored Input                                                  | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD1 is an input when data is being received.                                                                                                                                                                                                                                                            |

| PD4         | Input or Output                              |                                                                | <b>Port D 4</b> —The default configuration following reset is GPIO input PD4. When configured as PD4, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SRD1 through the Port D Control Register.                                                                                                                                         |

| STD1        | Output                                       | Ignored Input                                                  | Serial Transmit Data—Transmits data from the Serial Transmit<br>Shift Register. STD1 is an output when data is being transmitted.                                                                                                                                                                                                                                                                            |

| PD5         | Input or Output                              |                                                                | <b>Port D 5</b> —The default configuration following reset is GPIO input PD5. When configured as PD5, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal STD1 through the Port D Control Register.                                                                                                                                         |

| 2. T        | If the last state is<br>If the last state is | s input, the signal<br>s output, the sign<br>ing state does no | ins the last state as follows:<br>l is an ignored input.<br>al is tri-stated.<br>t affect the signal state.                                                                                                                                                                                                                                                                                                  |

| Table 1-13. | Enhanced Serial Synchronous Interface 1 (Continued) |

|-------------|-----------------------------------------------------|

|             |                                                     |

# 2.5 DC Electrical Characteristics

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                                                   | Min                                 | Тур               | Мах                                        | Unit           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|-------------------|--------------------------------------------|----------------|

| Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>CC</sub>                                          | 3.0                                 | 3.3               | 3.6                                        | V              |

| Input high voltage<br>• D[0-23], BG, BB, TA<br>• MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>8</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub>  | 2.0<br>2.0<br>0.8 × V <sub>CC</sub> |                   | V <sub>CC</sub><br>5.25<br>V <sub>CC</sub> | V<br>V<br>V    |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>8</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub>  | -0.3<br>-0.3<br>-0.3                | <br>              | 0.8<br>0.8<br>0.2 × V <sub>CC</sub>        | V<br>V<br>V    |

| Input leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I <sub>IN</sub>                                          | -10                                 | —                 | 10                                         | μΑ             |

| High impedance (off-state) input current (@ 2.4 V / 0.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <sub>TSI</sub>                                         | -10                                 | _                 | 10                                         | μΑ             |

| Output high voltage<br>• TTL $(I_{OH} = -0.4 \text{ mA})^{5,7}$<br>• CMOS $(I_{OH} = -10 \mu \text{A})^5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>OH</sub>                                          | 2.4<br>V <sub>CC</sub> – 0.01       | _                 |                                            | V<br>V         |

| Output low voltage<br>• TTL ( $I_{OL}$ = 1.6 mA, open-drain pins $I_{OL}$ = 6.7 mA) <sup>5,7</sup><br>• CMOS ( $I_{OL}$ = 10 $\mu$ A) <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>OL</sub>                                          |                                     | _                 | 0.4<br>0.01                                | V<br>V         |

| Internal supply current <sup>2</sup> :<br>• In Normal mode<br>• In Wait mode <sup>3</sup><br>• In Stop mode <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sub>CCI</sub><br>I <sub>CCW</sub><br>I <sub>CCS</sub> |                                     | 127<br>7.5<br>100 |                                            | mA<br>mA<br>μA |

| PLL supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | —                                   | 1                 | 2.5                                        | mA             |

| Input capacitance <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C <sub>IN</sub>                                          | —                                   | _                 | 10                                         | pF             |

| <ul> <li>Input capacitance<sup>3</sup></li> <li>C<sub>IN</sub> – – 10 p</li> <li>Notes: 1. Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and MODD/IRQD pins.</li> <li>2. Power Consumption Considerations on page Section 4-3 provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks (see Appendix A). The power consumption numbers in this specification are 90 perce of the measured results of this benchmark. This reflects typical DSP applications. Typical internal supply current is measured with V<sub>CC</sub> = 3.3 V at T<sub>J</sub> = 100°C.</li> <li>3. In order to obtain these results, all inputs must be terminated (that is, not allowed to float).</li> <li>4. In order to obtain these results, all inputs that are not disconnected at Stop mode must be terminate (that is, not allowed to float). PLL and XTAL signals are disabled during Stop state.</li> </ul> |                                                          |                                     |                   |                                            |                |

Table 2-3.

DC Electrical Characteristics<sup>6</sup>

- V<sub>CC</sub> = 3.3 V ± 0.3 V; T<sub>J</sub> = -40°C to +100 °C, C<sub>L</sub> = 50 pF

This characteristic does not apply to XTAL and PCAP.

Driving EXTAL to the low V<sub>IHX</sub> or the high V<sub>ILX</sub> value may cause additional power consumption (DC current). To minimize power consumption, the minimum V<sub>IHX</sub> should be no lower than  $0.9 \times V_{CC}$  and the maximum  $V_{ILX}$  should be no higher than  $0.1 \times V_{CC}.$

# 2.6.2 External Clock Operation

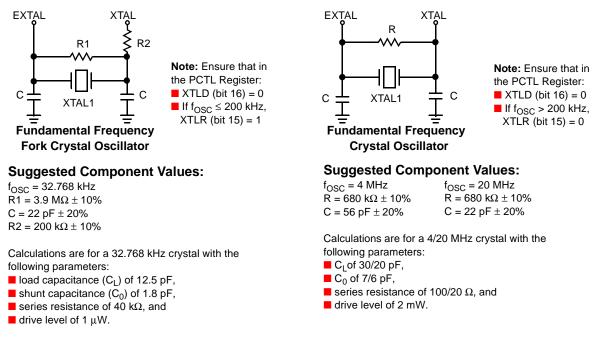

The DSP56303 system clock is derived from the on-chip oscillator or is externally supplied. To use the on-chip oscillator, connect a crystal and associated resistor/capacitor components to EXTAL and XTAL; examples are shown in **Figure 2-1**.

Figure 2-1. Crystal Oscillator Circuits

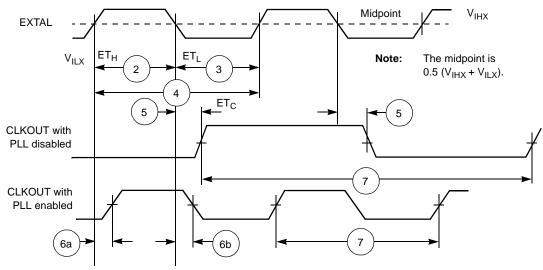

If an externally-supplied square wave voltage source is used, disable the internal oscillator circuit during bootup by setting XTLD (PCTL Register bit 16 = 1—see the *DSP56303 User's Manual*). The external square wave source connects to EXTAL; XTAL is not physically connected to the board or socket. **Figure 2-2** shows the relationship between the EXTAL input and the internal clock and CLKOUT.

Figure 2-2. External Clock Timing

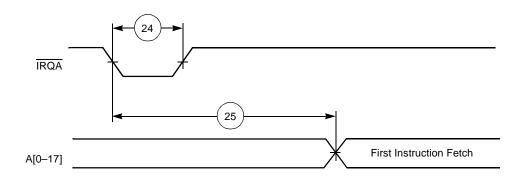

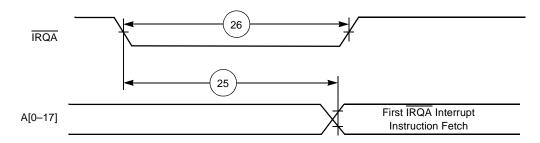

Figure 2-9. Recovery from Stop State Using IRQA

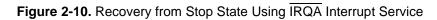

Figure 2-11. External Memory Access (DMA Source) Timing

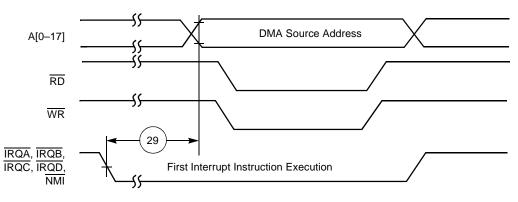

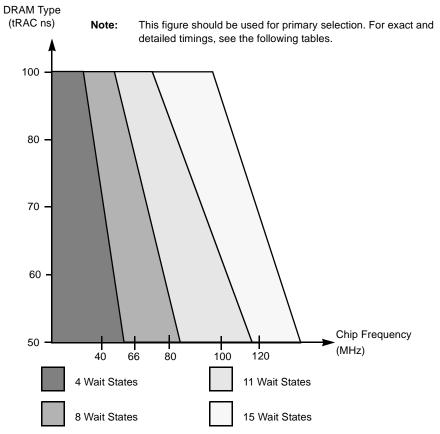

## 2.6.5.2 DRAM Timing

The selection guides in **Figure 2-14** and **Figure 2-17** are for primary selection only. Final selection should be based on the timing in the following tables. For example, the selection guide suggests that four wait states must be used for 100 MHz operation with Page Mode DRAM. However, consulting the appropriate table, a designer can evaluate whether fewer wait states might suffice by determining which timing prevents operation at 100 MHz, running the chip at a slightly lower frequency (for example, 95 MHz), using faster DRAM (if it becomes available), and manipulating control factors such as capacitive and resistive load to improve overall system performance.

Figure 2-14. DRAM Page Mode Wait State Selection Guide

Figure 2-17. DRAM Out-of-Page Wait State Selection Guide

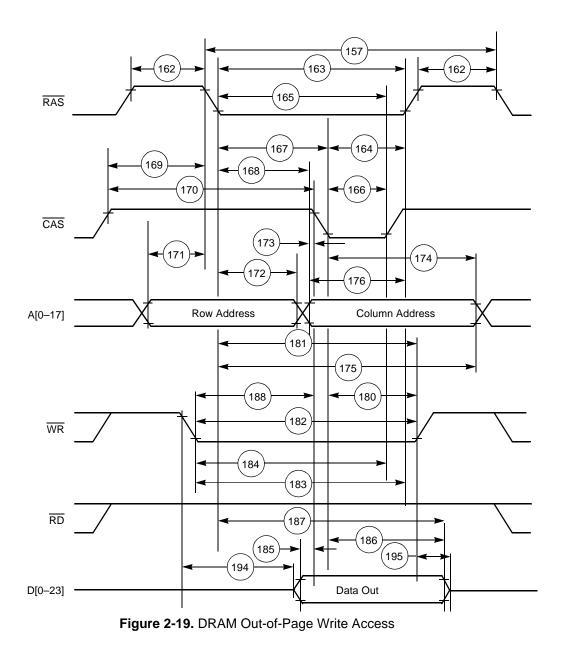

| No. | Characteristics                                    | Symbol           | Expression <sup>3</sup>    | 100 MHz |      | Unit |

|-----|----------------------------------------------------|------------------|----------------------------|---------|------|------|

| NO. |                                                    | Зушрог           | Expression                 | Min     | Max  | Unit |

| 157 | Random read or write cycle time                    | t <sub>RC</sub>  | $12 \times T_{C}$          | 120.0   | _    | ns   |

| 158 | RAS assertion to data valid (read)                 | t <sub>RAC</sub> | $6.25 	imes T_C - 7.0$     | —       | 55.5 | ns   |

| 159 | CAS assertion to data valid (read)                 | t <sub>CAC</sub> | $3.75 	imes T_{C} - 7.0$   | _       | 30.5 | ns   |

| 160 | Column address valid to data valid (read)          | t <sub>AA</sub>  | $4.5 	imes T_C - 7.0$      |         | 38.0 | ns   |

| 161 | CAS deassertion to data not valid (read hold time) | t <sub>OFF</sub> |                            | 0.0     |      | ns   |

| 162 | RAS deassertion to RAS assertion                   | t <sub>RP</sub>  | $4.25\times T_C-4.0$       | 38.5    |      | ns   |

| 163 | RAS assertion pulse width                          | t <sub>RAS</sub> | $7.75 	imes T_C - 4.0$     | 73.5    |      | ns   |

| 164 | CAS assertion to RAS deassertion                   | t <sub>RSH</sub> | $5.25 	imes T_C - 4.0$     | 48.5    | _    | ns   |

| 165 | RAS assertion to CAS deassertion                   | t <sub>CSH</sub> | $6.25\times T_C-4.0$       | 58.5    | _    | ns   |

| 166 | CAS assertion pulse width                          | t <sub>CAS</sub> | $3.75 	imes T_C - 4.0$     | 33.5    | _    | ns   |

| 167 | RAS assertion to CAS assertion                     | t <sub>RCD</sub> | $2.5\times T_{C}\pm 4.0$   | 21.0    | 29.0 | ns   |

| 168 | RAS assertion to column address valid              | t <sub>RAD</sub> | $1.75 	imes T_{C} \pm 4.0$ | 13.5    | 21.5 | ns   |

| 169 | CAS deassertion to RAS assertion                   | t <sub>CRP</sub> | $5.75	imes T_C-4.0$        | 53.5    | _    | ns   |

| 170 | CAS deassertion pulse width                        | t <sub>CP</sub>  | $4.25\times T_C-6.0$       | 36.5    | _    | ns   |

| Table 2-11. DRAW Out-of-Page and Refresh Timings, Eleven Walt States | Table 2-11. | DRAM Out-of-Page and Refresh Timings, Eleven Wait States <sup>1,2</sup> |

|----------------------------------------------------------------------|-------------|-------------------------------------------------------------------------|

|----------------------------------------------------------------------|-------------|-------------------------------------------------------------------------|

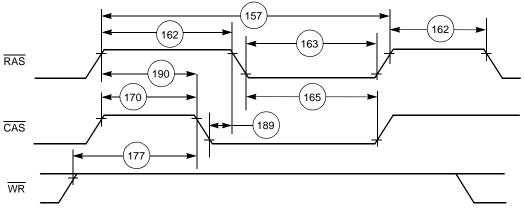

Figure 2-20. DRAM Refresh Access

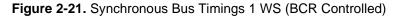

**Note**: Address lines A[0–17] hold their state after a read or write operation. AA[0–3] do not hold their state after a read or write operation.

**Note**: Address lines A[0–17] hold their state after a read or write operation. AA[0–3] do not hold their state after a read or write operation.

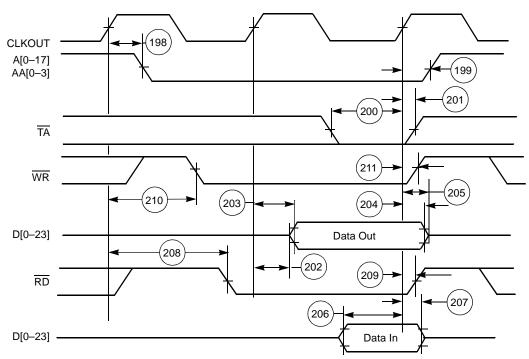

Figure 2-22. Synchronous Bus Timings 2 WS (TA Controlled)

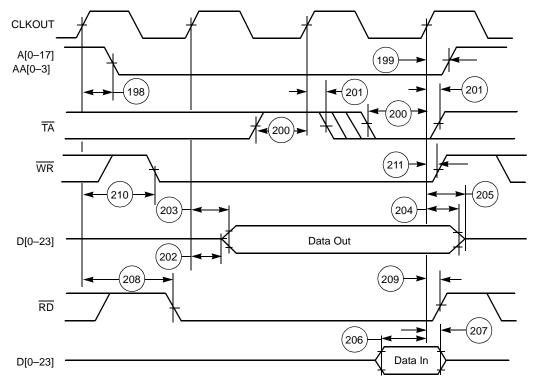

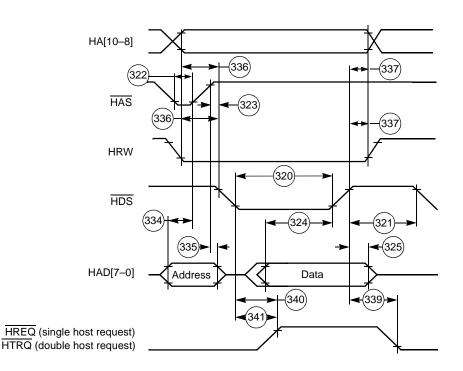

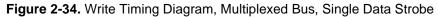

Figure 2-32. Read Timing Diagram, Multiplexed Bus, Single Data Strobe

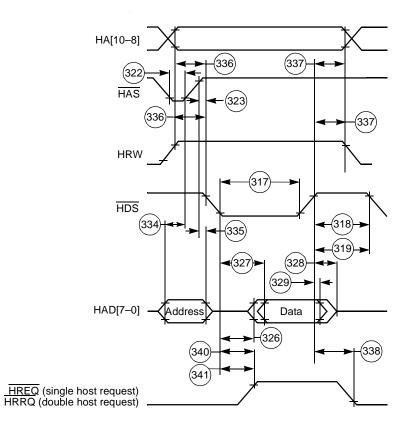

Figure 2-33. Read Timing Diagram, Multiplexed Bus, Double Data Strobe

Figure 2-35. Write Timing Diagram, Multiplexed Bus, Double Data Strobe

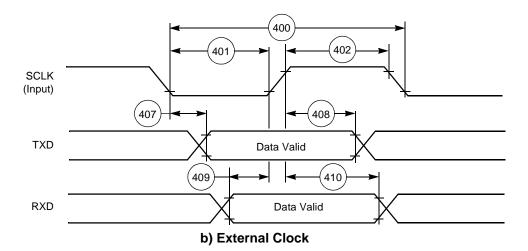

a) Internal Clock

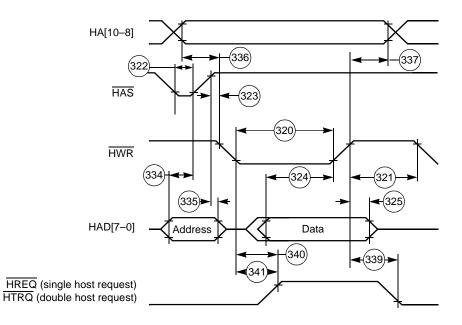

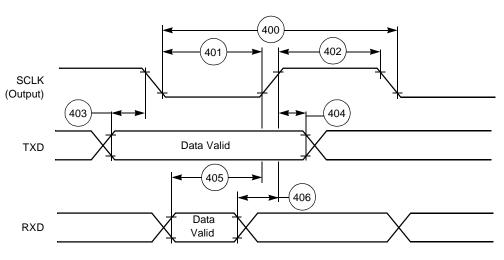

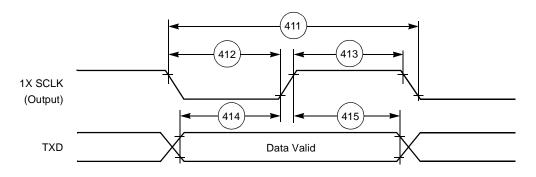

Figure 2-36. SCI Synchronous Mode Timing

Figure 2-37. SCI Asynchronous Mode Timing

| No    | Characteristics <sup>4, 5, 7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol                                                                                                                                                    | Expression <sup>9</sup>                                        | 100                            | MHz                                         | Cond-                            | Unit       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|---------------------------------------------|----------------------------------|------------|

| No.   | Characteristics 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                                                                                                                                                    | Expression                                                     | Min                            | Max                                         | ition <sup>5</sup>               | Unit       |

| 450   | TXC rising edge to FST out (word-length) high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                           |                                                                | _                              | 30.0<br>16.0                                | x ck<br>i ck                     | ns         |

| 451   | TXC rising edge to FST out (word-length) low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                           |                                                                | -                              | 31.0<br>17.0                                | x ck<br>i ck                     | ns         |

| 452   | TXC rising edge to data out enable from high impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                           |                                                                | _<br>_                         | 31.0<br>17.0                                | x ck<br>i ck                     | ns         |

| 453   | TXC rising edge to Transmitter #0 drive enable assertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |                                                                | _<br>_                         | 34.0<br>20.0                                | x ck<br>i ck                     | ns         |

| 454   | TXC rising edge to data out valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                                                                | _<br>_                         | 20.0 <sup>8</sup><br>10.0                   | x ck<br>i ck                     | ns         |

| 455   | TXC rising edge to data out high impedance <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                           |                                                                | _<br>_                         | 31.0<br>16.0                                | x ck<br>i ck                     | ns         |

| 456   | TXC rising edge to Transmitter #0 drive enable deassertion <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                           |                                                                | _<br>_                         | 34.0<br>20.0                                | x ck<br>i ck                     | ns         |

| 457   | FST input (bl, wr) setup time before TXC falling edge <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                | 2.0<br>21.0                    | _                                           | x ck<br>i ck                     | ns         |

| 458   | FST input (wl) to data out enable from high impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                                                | _                              | 27.0                                        | _                                | ns         |

| 459   | FST input (wl) to Transmitter #0 drive enable assertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                           |                                                                | —                              | 31.0                                        | —                                | ns         |

| 460   | FST input (wl) setup time before TXC falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                                                                | 2.5<br>21.0                    | _                                           | x ck<br>i ck                     | ns         |

| 461   | FST input hold time after TXC falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                           |                                                                | 4.0<br>0.0                     | _                                           | x ck<br>i ck                     | ns         |

| 462   | Flag output valid after TXC rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                           |                                                                | _                              | 32.0<br>18.0                                | x ck<br>i ck                     | ns         |

| Notes | <ul> <li>Register.</li> <li>2. The word-length-relative frame sync signal sync signal waveform, but spreads from on Length Frame Sync signal) until the one b</li> <li>3. Periodically sampled and not 100 percent</li> <li>4. V<sub>CC</sub> = 3.3 V ± 0.3 V; T<sub>J</sub> = -40°C to +100 °</li> <li>5. TXC (SCK Pin) = Transmit Clock<br/>RXC (SC0 or SCK Pin) = Receive Clock<br/>FST (SC2 Pin) = Transmit Frame Sync<br/>FSR (SC1 or SC2 Pin) Receive Frame Sy</li> <li>6. i ck = Internal Clock<br/>x ck = External Clock<br/>i ck a = Internal Clock, Asynchronous Mode<br/>(asynchronous implies that TXC and F</li> <li>7. bl = bit length; wl = word length; wr = word</li> <li>8. If the DSP core writes to the transmit regis<br/>the delay is 20 ns + (0.5 × T<sub>C</sub>).</li> </ul> | I waveform one serial cloc<br>efore last bit<br>tested<br>C, $C_L = 50 \text{ pf}$<br>nc<br>RXC are two<br>cXC are the s<br>length relativiter during the | e different clocks)<br>ame clock)<br>ve<br>e last cycle before | e way a<br>bit cloc<br>word in | as the bi<br>k (same<br>the frar<br>ng an u | t-length fr<br>e as the B<br>ne. | rame<br>it |

|       | <ul><li>9. An expression is used to compute the nun appropriate.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nber listed as                                                                                                                                            | the minimum or                                                 | maxim                          | um valu                                     | e as                             |            |

Table 2-18. ESSI Timings (Continued)

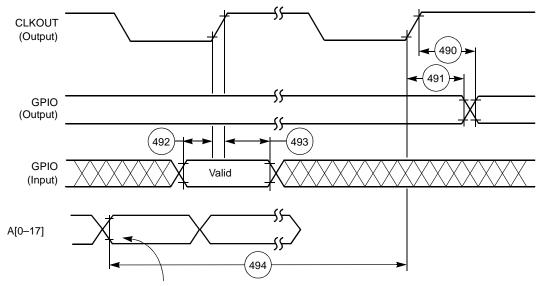

# 2.6.10 GPIO Timing

| No.   | Characteristics                                                   | Expression                   | 100  | Unit |      |

|-------|-------------------------------------------------------------------|------------------------------|------|------|------|

|       | onaracteristics                                                   | Expression                   | Min  | Max  | Onic |

| 490   | CLKOUT edge to GPIO out valid (GPIO out delay time)               |                              | _    | 8.5  | ns   |

| 491   | CLKOUT edge to GPIO out not valid (GPIO out hold time)            |                              | 0.0  | _    | ns   |

| 492   | GPIO In valid to CLKOUT edge (GPIO in set-up time)                |                              | 8.5  | —    | ns   |

| 493   | CLKOUT edge to GPIO in not valid (GPIO in hold time)              |                              | 0.0  | —    | ns   |

| 494   | Fetch to CLKOUT edge before GPIO change                           | Minimum: $6.75 \times T_{C}$ | 67.5 | —    | ns   |

| Note: | $V_{CC}$ = 3.3 V $\pm$ 0.3 V; T_J = -40°C to +100 °C, C_L = 50 pF |                              |      |      |      |

Fetch the instruction MOVE X0, X:(R0); X0 contains the new value of GPIO and R0 contains the address of the GPIO data register.

Figure 2-43. GPIO Timing

| Pin<br>No. | Signal Name                      | Pin<br>No. | Signal Name                  | Pin<br>No. | Signal Name      |

|------------|----------------------------------|------------|------------------------------|------------|------------------|

| 1          | SRD1 or PD4                      | 26         | GND <sub>S</sub>             | 51         | AA2/RAS2         |

| 2          | STD1 or PD5                      | 27         | TIO2                         | 52         | CAS              |

| 3          | SC02 or PC2                      | 28         | TIO1                         | 53         | XTAL             |

| 4          | SC01 or PC1                      | 29         | TIO0                         | 54         | GND <sub>Q</sub> |

| 5          | DE                               | 30         | HCS/HCS, HA10, or PB13       | 55         | EXTAL            |

| 6          | PINIT/NMI                        | 31         | HA2, HA9, or PB10            | 56         | V <sub>CCQ</sub> |

| 7          | SRD0 or PC4                      | 32         | HA1, HA8, or PB9             | 57         | V <sub>CCC</sub> |

| 8          | V <sub>CCS</sub>                 | 33         | HA0, HAS/HAS, or PB8         | 58         | GND <sub>C</sub> |

| 9          | GND <sub>S</sub>                 | 34         | H7, HAD7, or PB7             | 59         | CLKOUT           |

| 10         | STD0 or PC5                      | 35         | H6, HAD6, or PB6             | 60         | BCLK             |

| 11         | SC10 or PD0                      | 36         | H5, HAD5, or PB5             | 61         | BCLK             |

| 12         | SC00 or PC0                      | 37         | H4, HAD4, or PB4             | 62         | TA               |

| 13         | RXD or PE0                       | 38         | V <sub>CCH</sub>             | 63         | BR               |

| 14         | TXD or PE1                       | 39         | GND <sub>H</sub>             | 64         | BB               |

| 15         | SCLK or PE2                      | 40         | H3, HAD3, or PB3             | 65         | V <sub>CCC</sub> |

| 16         | SCK1 or PD3                      | 41         | H2, HAD2, or PB2             | 66         | GND <sub>C</sub> |

| 17         | SCK0 or PC3                      | 42         | H1, HAD1, or PB1             | 67         | WR               |

| 18         | V <sub>CCQ</sub>                 | 43         | H0, HAD0, or PB0             | 68         | RD               |

| 19         | GND <sub>Q</sub>                 | 44         | RESET                        | 69         | AA1/RAS1         |

| 20         | Not Connected (NC), reserved     | 45         | V <sub>CCP</sub>             | 70         | AA0/RAS0         |

| 21         | HDS/HDS, HWR/HWR, or<br>PB12     | 46         | PCAP                         | 71         | BG               |

| 22         | HRW, HRD/HRD, or PB11            | 47         | GND <sub>P</sub>             | 72         | AO               |

| 23         | HACK/HACK,<br>HRRQ/HRRQ, or PB15 | 48         | GND <sub>P1</sub>            | 73         | A1               |

| 24         | HREQ/HREQ,<br>HTRQ/HTRQ, or PB14 | 49         | Not Connected (NC), reserved | 74         | V <sub>CCA</sub> |

| 25         | V <sub>CCS</sub>                 | 50         | AA3/RAS3                     | 75         | GND <sub>A</sub> |

Table 3-1.

DSP56303 TQFP Signal Identification by Pin Number

# 4.4 PLL Performance Issues

The following explanations should be considered as general observations on expected PLL behavior. There is no test that replicates these exact numbers. These observations were measured on a limited number of parts and were not verified over the entire temperature and voltage ranges.

# 4.4.1 Phase Skew Performance

The phase skew of the PLL is defined as the time difference between the falling edges of EXTAL and CLKOUT for a given capacitive load on CLKOUT, over the entire process, temperature and voltage ranges. As defined in **Figure 2-2**, *External Clock Timing*, on page 2-5 for input frequencies greater than 15 MHz and the MF  $\leq$  4, this skew is greater than or equal to 0.0 ns and less than 1.8 ns; otherwise, this skew is not guaranteed. However, for MF < 10 and input frequencies greater than 10 MHz, this skew is between -1.4 ns and +3.2 ns.

## 4.4.2 Phase Jitter Performance

The phase jitter of the PLL is defined as the variations in the skew between the falling edges of EXTAL and CLKOUT for a given device in specific temperature, voltage, input frequency, MF, and capacitive load on CLKOUT. These variations are a result of the PLL locking mechanism. For input frequencies greater than 15 MHz and MF  $\leq$  4, this jitter is less than ±0.6 ns; otherwise, this jitter is not guaranteed. However, for MF < 10 and input frequencies greater than 10 MHz, this jitter is less than ±2 ns.

# 4.4.3 Frequency Jitter Performance

The frequency jitter of the PLL is defined as the variation of the frequency of CLKOUT. For small MF (MF < 10) this jitter is smaller than 0.5 percent. For mid-range MF (10 < MF < 500) this jitter is between 0.5 percent and approximately 2 percent. For large MF (MF > 500), the frequency jitter is 2–3 percent.

# 4.5 Input (EXTAL) Jitter Requirements

The allowed jitter on the frequency of EXTAL is 0.5 percent. If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the allowed jitter can be 2 percent. The phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed values.

| ;<br>sbr | clr<br>move<br>move<br>bset<br>dor<br>mac<br>add<br>mac<br>mac<br>move             | <pre>b #\$0,x0 #\$0,x1 #\$0,y0 #\$0,y1 #4,omr ; ebd #60,_end x0,y0,ax:(r0)+,x1 x1,y1,ax:(r0)+,x0 a,b x0,y0,ax:(r0)+,x1 x1,y1,a b1,x:\$ff</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | y:(r4)+,y1<br>y:(r4)+,y0<br>y:(r4)+,y0 |

|----------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| _end     | bra<br>nop<br>nop<br>nop                                                           | sbr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| PROG_E   | nop<br>IND                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|          | nop<br>nop                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| XDAT_S   | TART<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc<br>dc | x:0<br>\$262EB9<br>\$86F2FE<br>\$e56A5F<br>\$616CAC<br>\$8FD75<br>\$9210A<br>\$A06D7B<br>\$CEA798<br>\$BFD75<br>\$29210A<br>\$A0607B<br>\$CEA798<br>\$8DFBF1<br>\$A0603D6<br>\$6C6657<br>\$c2A544<br>\$A3662D<br>\$A4E762<br>\$A4E762<br>\$84F0F3<br>\$e6F1B0<br>\$B3829<br>\$8BF7AE<br>\$63394F<br>\$eF78DC<br>\$242DE5<br>\$A3E0BA<br>\$eBA86B<br>\$8726C8<br>\$cA361<br>\$2F6e866<br>\$A57347<br>\$4BE774<br>\$8F349D<br>\$A1ED12<br>\$4BF74<br>\$8F349D<br>\$A1ED12<br>\$4BFCE3<br>\$eA26e0<br>\$cD7D99<br>\$4BA85E<br>\$27A43F<br>\$A8B10C<br>\$D3A55<br>\$25EC6A<br>\$22A255B<br>\$A5F1F8<br>\$2426D1<br>\$A6536<br>\$CBBC37<br>\$6235A4<br>\$37F0D<br>\$63BEC2<br>\$A5E4D3<br>\$8CE810<br>\$3FF09<br>\$60E50E<br>\$CFFB2F |                                        |

|          | dc<br>dc<br>dc<br>dc                                                               | \$40753C<br>\$8262C5<br>\$CA641A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

interrupt signals 1-8 JTAG signals 1-18 mode control 1-8 OnCE signals 1-18 PLL signals 1-4 Reset timing 2-7, 2-9 synchronous 2-10 ROM, bootstrap iii

### S

Serial Communication Interface (SCI) iii, 1-1, 1-2, 1-16 Asynchronous mode timing 2-38 Synchronous mode timing 2-38 signal groupings 1-1 signals 1-1 functional grouping 1-2 Single Data Strobe 1-2 SRAM read access 2-15 support iv write access 2-15 Stop mode iv Stop state recovery from 2-12 Stop timing 2-7 supply voltage 2-2 Switch mode iii synchronous bus timings SRAM 2 wait states 2-26 SRAM 1 wait state (BCR controlled) 2-26 synchronous interrupt from Wait state timing 2-11 synchronous Reset timing 2-10

### Т

target applications iv Test Access Port (TAP) iii timing diagram 2-46 Test Clock (TCLK) input timing diagram 2-45 thermal design considerations 4-1 Timer event input restrictions 2-43 Timers 1-1, 1-2, 1-17 interrupt generation 2-43 **TQFP 3-1** mechanical drawing 3-9 pin list by name 3-6 pin list by number 3-4 pin-out drawing (bottom) 3-3 pin-out drawing (top) 3-2

### W

Wait mode iv World Wide Web iv

# Χ

X-data RAM iii

### Y

Y-data RAM iii