Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | CIP-51 8051                                                             |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 25MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SMBus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 4.25K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 15x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 24-WFQFN Exposed Pad                                                    |

| Supplier Device Package    | 24-QFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8sb20f16g-b-qfn24r |

### 1. Feature List

The EFM8SB2 highlighted features are listed below.

- · Core:

- · Pipelined CIP-51 Core

- · Fully compatible with standard 8051 instruction set

- · 70% of instructions execute in 1-2 clock cycles

- · 25 MHz maximum operating frequency

- · Memory:

- Up to 64 kB flash memory, in-system re-programmable from firmware.

- Up to 4352 bytes RAM (including 256 bytes standard 8051 RAM and 4096 bytes on-chip XRAM)

- · Power:

- · Internal LDO regulator for CPU core voltage

- · Power-on reset circuit and brownout detectors

- I/O: Up to 24 total multifunction I/O pins:

- · All pins 5 V tolerant under bias

- · Flexible peripheral crossbar for peripheral routing

- 5 mA source, 12.5 mA sink allows direct drive of LEDs

- · Clock Sources:

- Internal 20 MHz low power oscillator with ±10% accuracy

- Internal 24.5 MHz precision oscillator with ±2% accuracy

- · External RTC 32 kHz crystal

- External crystal, RC, C, and CMOS clock options

- Timers/Counters and PWM:

- 32-bit Real Time Clock (RTC)

- 6-channel programmable counter array (PCA) supporting PWM, capture/compare, and frequency output modes with watchdog timer function

- · 4 x 16-bit general-purpose timers

- · Communications and Digital Peripherals:

- UART

- 2 x SPI™ Master / Slave

- SMBus™/I2C™ Master / Slave

- · External Memory Interface (EMIF)

- 16-bit/32-bit CRC unit, supporting automatic CRC of flash at 1024-byte boundaries

- · Analog:

- Programmable current reference (IREF0)

- 10-Bit Analog-to-Digital Converter (ADC0)

- · 2 x Low-current analog comparators

- · On-Chip, Non-Intrusive Debugging

- · Full memory and register inspection

- · Four hardware breakpoints, single-stepping

- · Pre-loaded UART bootloader

- Temperature range -40 to 85 °C

- Single power supply 1.8 to 3.6 V

- · QFP32, QFN32, and QFN24 packages

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the EFM8SB2 devices are truly standalone system-on-a-chip solutions. The flash memory is reprogrammable in-circuit, providing non-volatile data storage and allowing field upgrades of the firmware. The on-chip debugging interface (C2) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging. Each device is specified for 1.8 to 3.6 V operation and is available in 24-pin QFN, 32-pin QFN, or 32-pin QFP packages. All package options are lead-free and RoHS compliant.

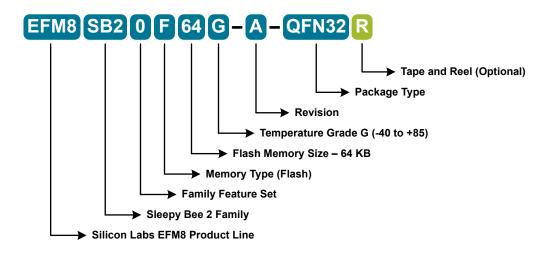

### 2. Ordering Information

Figure 2.1. EFM8SB2 Part Numbering

All EFM8SB2 family members have the following features:

- · CIP-51 Core running up to 25 MHz

- Three Internal Oscillators (24.5 MHz, 20 MHz, and 16 kHz)

- · SMBus / I2C

- 2 x SPI

- UART

- 6-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- · 4 16-bit Timers

- · 2 Analog Comparators

- · 6-bit programmable current reference

- 10-bit Analog-to-Digital Converter with integrated multiplexer, voltage reference, and temperature sensor

- · Low-current 32 kHz oscillator and Real Time Clock

- · 16-bit CRC Unit

- Pre-loaded UART bootloader

In addition to these features, each part number in the EFM8SB2 family has a set of features that vary across the product line. The product selection guide shows the features available on each family member.

**Table 2.1. Product Selection Guide**

| Ordering Part<br>Number | Flash<br>Memory (kB) | RAM (Bytes) | Digital Port<br>I/Os (Total) | ADC Channels | Comparator<br>Inputs | Pb-free<br>(RoHS Compliant) | Temperature<br>Range | Package |

|-------------------------|----------------------|-------------|------------------------------|--------------|----------------------|-----------------------------|----------------------|---------|

| EFM8SB20F64G-B-QFN32    | 64                   | 4352        | 24                           | 23           | 12                   | Yes                         | -40 to +85 C         | QFN32   |

| EFM8SB20F64G-B-QFP32    | 64                   | 4352        | 24                           | 23           | 12                   | Yes                         | -40 to +85 C         | QFP32   |

| EFM8SB20F64G-B-QFN24    | 64                   | 4352        | 16                           | 15           | 8                    | Yes                         | -40 to +85 C         | QFN24   |

| EFM8SB20F32G-B-QFN32    | 32                   | 4352        | 24                           | 23           | 12                   | Yes                         | -40 to +85 C         | QFN32   |

| EFM8SB20F32G-B-QFP32    | 32                   | 4352        | 24                           | 23           | 12                   | Yes                         | -40 to +85 C         | QFP32   |

| EFM8SB20F32G-B-QFN24    | 32                   | 4352        | 16                           | 15           | 8                    | Yes                         | -40 to +85 C         | QFN24   |

| Ordering Part Number | Flash<br>Memory (kB) | RAM (Bytes) | Digital Port<br>I/Os (Total) | ADC Channels | Comparator<br>Inputs | Pb-free<br>(RoHS Compliant) | Temperature<br>Range | Package |

|----------------------|----------------------|-------------|------------------------------|--------------|----------------------|-----------------------------|----------------------|---------|

| EFM8SB20F16G-B-QFN24 | 16                   | 4352        | 16                           | 15           | 8                    | Yes                         | -40 to +85 C         | QFN24   |

### 3. System Overview

### 3.1 Introduction

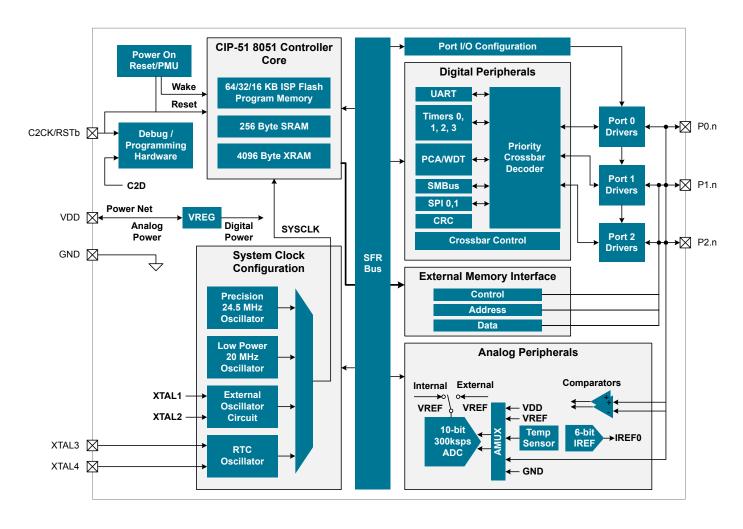

Figure 3.1. Detailed EFM8SB2 Block Diagram

This section describes the EFM8SB2 family at a high level. For more information on each module including register definitions, see the EFM8SB2 Reference Manual.

#### Watchdog Timer (WDT0)

The device includes a programmable watchdog timer (WDT) integrated within the PCA0 peripheral. A WDT overflow forces the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT overflows and causes a reset. Following a reset, the WDT is automatically enabled and running with the default maximum time interval. If needed, the WDT can be disabled by system software. The state of the RSTb pin is unaffected by this reset.

The Watchdog Timer integrated in the PCA0 peripheral has the following features:

- · Programmable timeout interval

- · Runs from the selected PCA clock source

- Automatically enabled after any system reset

### 3.6 Communications and Other Digital Peripherals

#### Universal Asynchronous Receiver/Transmitter (UART0)

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates. Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

The UART module provides the following features:

- · Asynchronous transmissions and receptions.

- · Baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive).

- 8- or 9-bit data.

- · Automatic start and stop generation.

- · Single-byte FIFO on transmit and receive.

#### Serial Peripheral Interface (SPI0 and SPI1)

The serial peripheral interface (SPI) module provides access to a flexible, full-duplex synchronous serial bus. The SPI can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select the SPI in slave mode, or to disable master mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a firmware-controlled chip-select output in master mode, or disabled to reduce the number of pins required. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

The SPI module includes the following features:

- Supports 3- or 4-wire operation in master or slave modes.

- Supports external clock frequencies up to SYSCLK / 2 in master mode and SYSCLK / 10 in slave mode.

- Support for four clock phase and polarity options.

- · 8-bit dedicated clock clock rate generator.

- Support for multiple masters on the same data lines.

### System Management Bus / I2C (SMB0)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the  $I^2C$  serial bus.

The SMBus module includes the following features:

- Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds.

- · Support for master, slave, and multi-master modes.

- · Hardware synchronization and arbitration for multi-master mode.

- Clock low extending (clock stretching) to interface with faster masters.

- · Hardware support for 7-bit slave and general call address recognition.

- · Firmware support for 10-bit slave address decoding.

- · Ability to inhibit all slave states.

- · Programmable data setup/hold times.

### 10-Bit Analog-to-Digital Converter (ADC0)

The ADC is a successive-approximation-register (SAR) ADC with 10- and 8-bit modes, integrated track-and hold and a programmable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer. The voltage reference for the ADC is selectable between internal and external reference sources.

- · Up to 22 external inputs.

- · Single-ended 10-bit mode.

- · Supports an output update rate of 300 ksps samples per second.

- · Operation in low power modes at lower conversion speeds.

- · Asynchronous hardware conversion trigger, selectable between software, external I/O and internal timer sources.

- Output data window comparator allows automatic range checking.

- Support for burst mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- · Conversion complete and window compare interrupts supported.

- · Flexible output data formatting.

- Includes an internal 1.65 V fast-settling reference and support for external reference.

- Integrated temperature sensor.

#### Low Current Comparators (CMP0, CMP1)

Analog comparators are used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. External input connections to device I/O pins and internal connections are available through separate multiplexers on the positive and negative inputs. Hysteresis, response time, and current consumption may be programmed to suit the specific needs of the application.

The comparator module includes the following features:

- · Up to 12 external positive inputs.

- · Up to 11 external negative inputs.

- · Additional input options:

- · Capacitive Sense Comparator output.

- VDD.

- · VDD divided by 2.

- · Internal connection to LDO output.

- · Direct connection to GND.

- · Synchronous and asynchronous outputs can be routed to pins via crossbar.

- Programmable hysteresis between 0 and +/-20 mV.

- · Programmable response time.

- · Interrupts generated on rising, falling, or both edges.

## 4. Electrical Specifications

### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in Table 4.1 Recommended Operating Conditions on page 12, unless stated otherwise.

## 4.1.1 Recommended Operating Conditions

**Table 4.1. Recommended Operating Conditions**

| Parameter                       | Symbol              | Test Condition    | Min | Тур | Max | Unit |

|---------------------------------|---------------------|-------------------|-----|-----|-----|------|

| Operating Supply Voltage on VDD | V <sub>DD</sub>     |                   | 1.8 | 2.4 | 3.6 | V    |

| Minimum RAM Data Retention      | V <sub>RAM</sub>    | Not in Sleep Mode | _   | 1.4 | _   | V    |

| Voltage on VDD <sup>1</sup>     |                     | Sleep Mode        | _   | 0.3 | 0.5 | V    |

| System Clock Frequency          | f <sub>SYSCLK</sub> |                   | 0   | _   | 25  | MHz  |

| Operating Ambient Temperature   | T <sub>A</sub>      |                   | -40 | _   | 85  | °C   |

<sup>1.</sup> All voltages with respect to GND.

# 4.1.2 Power Consumption

**Table 4.2. Power Consumption**

| Parameter                                                                                   | Symbol              | Conditions                                                              | Min | Тур  | Max | Units  |

|---------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------|-----|------|-----|--------|

| Digital Supply Current                                                                      |                     |                                                                         |     |      |     |        |

| Normal Mode supply current - Full speed with code executing from                            | I <sub>DD</sub>     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub><br>= 24.5 MHz          | _   | 4.1  | 5.0 | mA     |

| flash <sup>3, 4, 5</sup>                                                                    |                     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub> = 20<br>MHz            | _   | 3.5  | _   | mA     |

|                                                                                             |                     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub> = 32.768 kHz           | _   | 90   | _   | μА     |

| Normal Mode supply current frequency sensitivity <sup>1, 3, 5</sup>                         | I <sub>DDFREQ</sub> | V <sub>DD</sub> = 1.8–3.6 V, T = 25 °C,<br>f <sub>SYSCLK</sub> < 14 MHz | _   | 226  | _   | µA/MHz |

|                                                                                             |                     | V <sub>DD</sub> = 1.8–3.6 V, T = 25 °C,<br>f <sub>SYSCLK</sub> > 14 MHz | _   | 120  | _   | µA/MHz |

| Idle Mode supply current - Core halted with peripherals running <sup>4</sup> , <sup>6</sup> | I <sub>DD</sub>     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub> = 24.5<br>MHz          | _   | 2.5  | 3.0 | mA     |

|                                                                                             |                     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub> = 20<br>MHz            | _   | 1.8  | _   | mA     |

|                                                                                             |                     | V <sub>DD</sub> = 1.8–3.6 V, f <sub>SYSCLK</sub> = 32.768 kHz           | _   | 84   | _   | μА     |

| Idle Mode Supply Current Frequency Sensitivity <sup>1,6</sup>                               | I <sub>DDFREQ</sub> | V <sub>DD</sub> = 1.8–3.6 V, T = 25 °C                                  | _   | 95   | _   | µA/MHz |

| Suspend Mode Supply Current                                                                 | I <sub>DD</sub>     | V <sub>DD</sub> = 1.8–3.6 V                                             | _   | 77   | _   | μA     |

| Sleep Mode Supply Current with                                                              | I <sub>DD</sub>     | 1.8 V, T = 25 °C                                                        | _   | 0.60 | _   | μA     |

| RTC running from 32.768 kHz crystal                                                         |                     | 3.6 V, T = 25 °C                                                        | _   | 0.85 | _   | μA     |

|                                                                                             |                     | 1.8 V, T = 85 °C                                                        | _   | 1.30 | _   | μA     |

|                                                                                             |                     | 3.6 V, T = 85 °C                                                        | _   | 1.90 | _   | μA     |

| Sleep Mode Supply Current (RTC                                                              | I <sub>DD</sub>     | 1.8 V, T = 25 °C                                                        | _   | 0.05 | _   | μA     |

| off)                                                                                        |                     | 3.6 V, T = 25 °C                                                        | _   | 0.12 | _   | μA     |

|                                                                                             |                     | 1.8 V, T = 85 °C                                                        | _   | 0.75 | _   | μA     |

|                                                                                             |                     | 3.6 V, T = 85 °C                                                        | _   | 1.20 | _   | μA     |

| V <sub>DD</sub> Monitor Supply Current                                                      | I <sub>VMON</sub>   |                                                                         | _   | 7    | _   | μA     |

| Oscillator Supply Current                                                                   | I <sub>HFOSC0</sub> | 25 °C                                                                   | _   | 300  | _   | μA     |

| ADC0 Always-on Power Supply                                                                 | I <sub>ADC</sub>    | 300 ksps                                                                | _   | 800  | _   | μA     |

| Current <sup>7</sup>                                                                        |                     | V <sub>DD</sub> = 3.0 V                                                 |     |      |     |        |

|                                                                                             |                     | Tracking                                                                | _   | 680  | _   | μA     |

|                                                                                             |                     | V <sub>DD</sub> = 3.0 V                                                 |     |      |     |        |

## 4.1.3 Reset and Supply Monitor

Table 4.3. Reset and Supply Monitor

| Parameter                                                            | Symbol            | Test Condition                                          | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------|-----|------|------|------|

| VDD Supply Monitor Threshold                                         | $V_{VDDM}$        | Reset Trigger                                           | 1.7 | 1.75 | 1.8  | V    |

|                                                                      | V <sub>WARN</sub> | Early Warning                                           | 1.8 | 1.85 | 1.9  | V    |

| VDD Supply Monitor Turn-On Time                                      | t <sub>MON</sub>  |                                                         | _   | 300  | _    | ns   |

| Power-On Reset (POR) Monitor<br>Threshold                            | V <sub>POR</sub>  | Initial Power-On (Rising Voltage on V <sub>DD</sub> )   | _   | 0.75 | _    | V    |

|                                                                      |                   | Falling Voltage on V <sub>DD</sub>                      | 0.7 | 0.8  | 0.9  | V    |

|                                                                      |                   | Brownout Recovery (Rising Voltage on V <sub>DD</sub> )  | _   | 0.95 | _    | V    |

| V <sub>DD</sub> Ramp Time                                            | t <sub>RMP</sub>  | Time to V <sub>DD</sub> ≥ 1.8 V                         | _   | _    | 3    | ms   |

| Reset Delay from POR                                                 | t <sub>POR</sub>  | Relative to V <sub>DD</sub> > V <sub>POR</sub>          | 3   | 10   | 31   | ms   |

| Reset Delay                                                          | t <sub>RST</sub>  | Time between release of reset source and code execution | _   | 10   | _    | μs   |

| RST Low Time to Generate Reset                                       | t <sub>RSTL</sub> |                                                         | 15  | _    | _    | μs   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> > 1 MHz                             | 100 | 650  | 1000 | μs   |

| Missing Clock Detector Trigger Frequency                             | F <sub>MCD</sub>  |                                                         | _   | 7    | 10   | kHz  |

### 4.1.4 Flash Memory

Table 4.4. Flash Memory

| Parameter                      | Symbol             | Test Condition | Min | Тур  | Max | Units  |

|--------------------------------|--------------------|----------------|-----|------|-----|--------|

| Write Time <sup>1</sup>        | t <sub>WRITE</sub> | One Byte       | 57  | 64   | 71  | μs     |

| Erase Time <sup>1</sup>        | t <sub>ERASE</sub> | One Page       | 28  | 32   | 36  | ms     |

| Endurance (Write/Erase Cycles) | N <sub>WE</sub>    |                | 1 k | 30 k | _   | Cycles |

- 1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

- 2. Data Retention Information is published in the Quarterly Quality and Reliability Report.

## 4.1.9 ADC

Table 4.9. ADC

| Parameter                                        | Symbol              | Test Condition                    | Min    | Тур   | Max                  | Unit   |

|--------------------------------------------------|---------------------|-----------------------------------|--------|-------|----------------------|--------|

| Resolution                                       | N <sub>bits</sub>   |                                   |        | 10    |                      | Bits   |

| Throughput Rate                                  | f <sub>S</sub>      |                                   | _      | _     | 300                  | ksps   |

| Tracking Time                                    | t <sub>TRK</sub>    |                                   | 1.5    | _     | _                    | μs     |

| Power-On Time                                    | t <sub>PWR</sub>    |                                   | 1.5    | _     | _                    | μs     |

| SAR Clock Frequency                              | f <sub>SAR</sub>    | High Speed Mode,                  | _      | _     | 8.33                 | MHz    |

| Conversion Time                                  | T <sub>CNV</sub>    |                                   | 13     | _     | _                    | Clocks |

| Sample/Hold Capacitor                            | C <sub>SAR</sub>    | Gain = 1                          | _      | 30    | _                    | pF     |

|                                                  |                     | Gain = 0.5                        | _      | 28    | _                    | pF     |

| Input Pin Capacitance                            | C <sub>IN</sub>     |                                   | _      | 20    | _                    | pF     |

| Input Mux Impedance                              | R <sub>MUX</sub>    |                                   | _      | 5     | _                    | kΩ     |

| Voltage Reference Range                          | V <sub>REF</sub>    |                                   | 1      | _     | V <sub>DD</sub>      | V      |

| Input Voltage Range <sup>1</sup>                 | V <sub>IN</sub>     | Gain = 1                          | 0      | _     | V <sub>REF</sub>     | V      |

|                                                  |                     | Gain = 0.5                        | 0      | _     | 2 x V <sub>REF</sub> | V      |

| Power Supply Rejection Ratio                     | PSRR <sub>ADC</sub> | Internal High Speed VREF          | _      | 67    | _                    | dB     |

|                                                  |                     | External VREF                     | _      | 74    | _                    | dB     |

| DC Performance                                   | 1                   |                                   |        | 1     | 1                    |        |

| Integral Nonlinearity                            | INL                 |                                   | _      | ±0.5  | ±1                   | LSB    |

| Differential Nonlinearity (Guaranteed Monotonic) | DNL                 |                                   | _      | ±0.5  | ±1                   | LSB    |

| Offset Error                                     | E <sub>OFF</sub>    | VREF = 1.65 V                     | -2     | 0     | 2                    | LSB    |

| Offset Temperature Coefficient                   | TC <sub>OFF</sub>   |                                   | _      | 0.004 | _                    | LSB/°C |

| Slope Error                                      | E <sub>M</sub>      |                                   | _      | ±0.06 | ±0.24                | %      |

| Dynamic Performance 10 kHz Si                    | ne Wave Inp         | ut 1dB below full scale, Max thro | ughput |       | I                    |        |

| Signal-to-Noise                                  | SNR                 |                                   | 54     | 58    | _                    | dB     |

| Signal-to-Noise Plus Distortion                  | SNDR                |                                   | 54     | 58    | _                    | dB     |

| Total Harmonic Distortion (Up to 5th Harmonic)   | THD                 |                                   | _      | -73   | _                    | dB     |

| Spurious-Free Dynamic Range                      | SFDR                |                                   | _      | 75    | _                    | dB     |

## Note:

1. Absolute input pin voltage is limited by the  $V_{DD}$  supply.

### 5. Typical Connection Diagrams

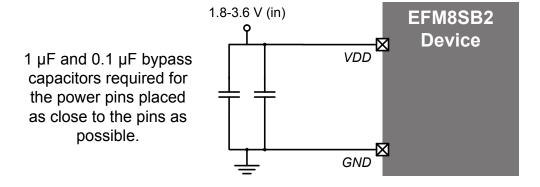

#### 5.1 Power

Figure 5.1 Power Connection Diagram on page 26 shows a typical connection diagram for the power pins of the EFM8SB2 devices.

Figure 5.1. Power Connection Diagram

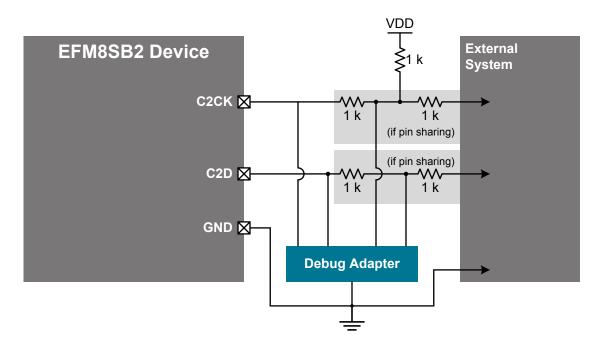

### 5.2 Debug

The diagram below shows a typical connection diagram for the debug connections pins. The pin sharing resistors are only required if the functionality on the C2D (a GPIO pin) and the C2CK (RSTb) is routed to external circuitry. For example, if the RSTb pin is connected to an external switch with debouncing filter or if the GPIO sharing with the C2D pin is connected to an external circuit, the pin sharing resistors and connections to the debug adapter must be placed on the hardware. Otherwise, these components and connections can be omitted.

For more information on debug connections, see the example schematics and information available in AN127: "Pin Sharing Techniques for the C2 Interface." Application notes can be found on the Silicon Labs website (http://www.silabs.com/8bit-appnotes) or in Simplicity Studio.

Figure 5.2. Debug Connection Diagram

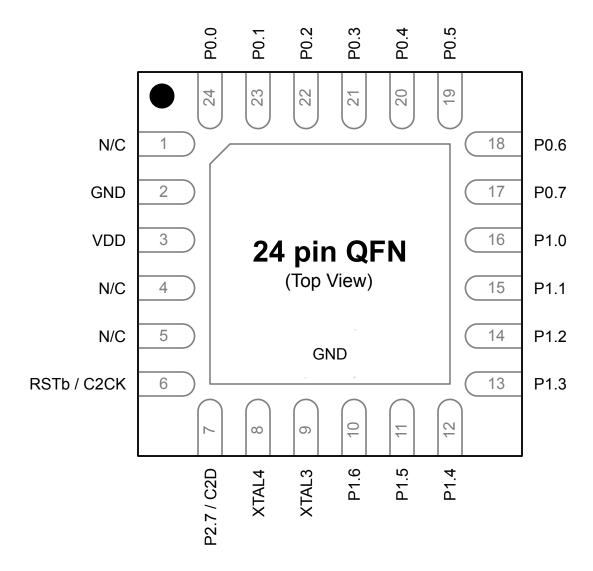

Figure 6.2. EFM8SB2x-QFN24 Pinout

Table 6.2. Pin Definitions for EFM8SB2x-QFN24

| Pin    | Pin Name | Description        | Crossbar Capability |           | Analog Functions |

|--------|----------|--------------------|---------------------|-----------|------------------|

| Number |          |                    |                     | Functions |                  |

| 1      | N/C      | No Connection      |                     |           |                  |

| 2      | GND      | Ground             |                     |           |                  |

| 3      | VDD      | Supply Power Input |                     |           |                  |

| 4      | N/C      | No Connection      |                     |           |                  |

| 5      | N/C      | No Connection      |                     |           |                  |

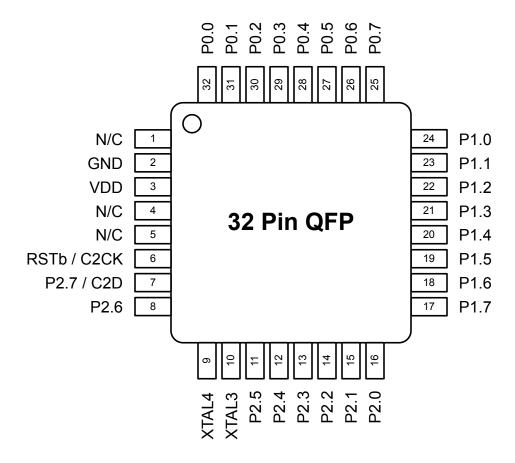

### 6.3 EFM8SB2x-QFP32 Pin Definitions

Figure 6.3. EFM8SB2x-QFP32 Pinout

Table 6.3. Pin Definitions for EFM8SB2x-QFP32

| Pin    | Pin Name | Description         | Crossbar Capability | Additional Digital | Analog Functions |

|--------|----------|---------------------|---------------------|--------------------|------------------|

| Number |          |                     |                     | Functions          |                  |

| 1      | N/C      | No Connection       |                     |                    |                  |

| 2      | GND      | Ground              |                     |                    |                  |

| 3      | VDD      | Supply Power Input  |                     |                    |                  |

| 4      | N/C      | No Connection       |                     |                    |                  |

| 5      | N/C      | No Connection       |                     |                    |                  |

| 6      | RSTb /   | Active-low Reset /  |                     |                    |                  |

|        | C2CK     | C2 Debug Clock      |                     |                    |                  |

| 7      | P2.7 /   | Multifunction I/O / |                     |                    |                  |

|        | C2D      | C2 Debug Data       |                     |                    |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 31            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                      | ADC0.1           |

|               |          |                   |                     | INT0.1                       | AGND             |

|               |          |                   |                     | INT1.1                       | CMP0N.0          |

|               |          |                   |                     |                              | CMP1N.0          |

| 32            | P0.0     | Multifunction I/O | Yes                 | P0MAT.0                      | ADC0.0           |

|               |          |                   |                     | INT0.0                       | CMP0P.0          |

|               |          |                   |                     | INT1.0                       | CMP1P.0          |

|               |          |                   |                     |                              | VREF             |

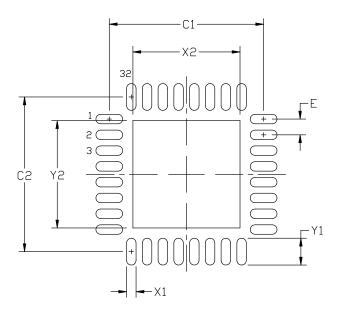

#### 7.2 QFN32 PCB Land Pattern

Figure 7.2. QFN32 PCB Land Pattern Drawing

Table 7.2. QFN32 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |

|-----------|------|------|

| C1        | 4.80 | 4.90 |

| C2        | 4.80 | 4.90 |

| E         | 0.50 | BSC  |

| X1        | 0.20 | 0.30 |

| X2        | 3.20 | 3.40 |

| Y1        | 0.75 | 0.85 |

| Y2        | 3.20 | 3.40 |

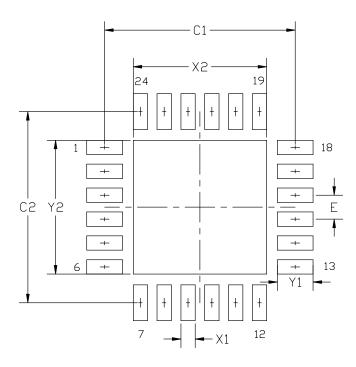

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 3 x 3 array of 1.0 mm x 1.0 mm openings on a 1.2 mm pitch should be used for the center pad.

- 8. A No-Clean, Type-3 solder paste is recommended.

- 9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

# 8. QFN24 Package Specifications

## 8.1 QFN24 Package Dimensions

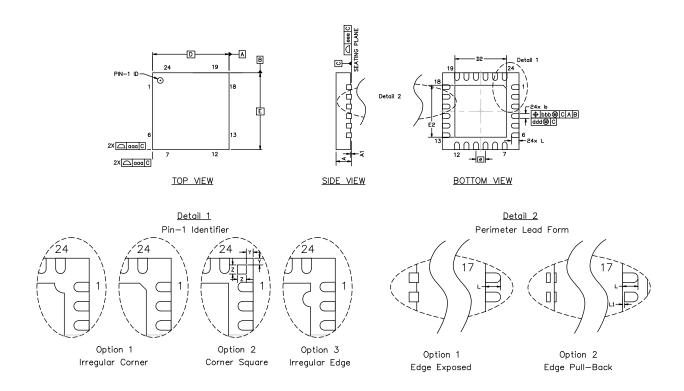

Figure 8.1. QFN24 Package Drawing

Table 8.1. QFN24 Package Dimensions

| Dimension | Min      | Тур  | Max  |  |  |  |  |  |  |  |  |

|-----------|----------|------|------|--|--|--|--|--|--|--|--|

| A         | 0.70     | 0.75 | 0.80 |  |  |  |  |  |  |  |  |

| A1        | 0.00     | 0.02 | 0.05 |  |  |  |  |  |  |  |  |

| b         | 0.18     | 0.25 | 0.30 |  |  |  |  |  |  |  |  |

| D         | 4.00 BSC |      |      |  |  |  |  |  |  |  |  |

| D2        | 2.55     | 2.70 | 2.80 |  |  |  |  |  |  |  |  |

| е         | 0.50 BSC |      |      |  |  |  |  |  |  |  |  |

| Е         | 4.00 BSC |      |      |  |  |  |  |  |  |  |  |

| E2        | 2.55     | 2.70 | 2.80 |  |  |  |  |  |  |  |  |

| L         | 0.30     | 0.40 | 0.50 |  |  |  |  |  |  |  |  |

| L1        | 0.00     | _    | 0.15 |  |  |  |  |  |  |  |  |

| ааа       | _        | _    | 0.15 |  |  |  |  |  |  |  |  |

| Dimension | Min | Тур  | Max  |

|-----------|-----|------|------|

| bbb       | _   | _    | 0.10 |

| ddd       | _   | _    | 0.05 |

| eee       | _   | _    | 0.08 |

| Z         | _   | 0.24 | _    |

| Υ         | _   | 0.18 | _    |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC Solid State Outline MO-220, variation WGGD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

## 8.2 QFN24 PCB Land Pattern

Figure 8.2. QFN24 PCB Land Pattern Drawing

Table 8.2. QFN24 PCB Land Pattern Dimensions

| Dimension | Min      | Max  |  |  |  |  |  |  |  |  |  |

|-----------|----------|------|--|--|--|--|--|--|--|--|--|

| C1        | 3.90     | 4.00 |  |  |  |  |  |  |  |  |  |

| C2        | 3.90     | 4.00 |  |  |  |  |  |  |  |  |  |

| E         | 0.50 BSC |      |  |  |  |  |  |  |  |  |  |

| X1        | 0.20     | 0.30 |  |  |  |  |  |  |  |  |  |

| X2        | 2.70     | 2.80 |  |  |  |  |  |  |  |  |  |

| Y1        | 0.65     | 0.75 |  |  |  |  |  |  |  |  |  |

| Y2        | 2.70     | 2.80 |  |  |  |  |  |  |  |  |  |

## 10. Revision History

### 10.1 Revision 1.2

Updated ordering part numbers to revision B.

Added Reset Delay from POR specification.

Added I/O 5 V tolerance to 1. Feature List.

Added information on the bootloader to 3.10 Bootloader.

Added a Debug Typical Connection Diagram to 5. Typical Connection Diagrams.

Added reference to the Reference Manual in 3.1 Introduction.

#### 10.2 Revision 1.1

Initial release.

|    | 6.2 EFM8SB2x-QFN24 Pin Defini | itions | S . |  |  |  |   |   |  |  |  |  |  |  | .32 |

|----|-------------------------------|--------|-----|--|--|--|---|---|--|--|--|--|--|--|-----|

|    | 6.3 EFM8SB2x-QFP32 Pin Defini | tions  | 3.  |  |  |  |   |   |  |  |  |  |  |  | .35 |

| 7. | QFN32 Package Specifications  |        |     |  |  |  |   |   |  |  |  |  |  |  | 39  |

|    | 7.1 QFN32 Package Dimensions  |        |     |  |  |  |   |   |  |  |  |  |  |  | .39 |

|    | 7.2 QFN32 PCB Land Pattern.   |        |     |  |  |  |   |   |  |  |  |  |  |  | .41 |

|    | 7.3 QFN32 Package Marking .   |        |     |  |  |  |   |   |  |  |  |  |  |  | .42 |

| 8. | QFN24 Package Specifications  |        |     |  |  |  |   |   |  |  |  |  |  |  | 43  |

|    | 8.1 QFN24 Package Dimensions  |        |     |  |  |  |   |   |  |  |  |  |  |  | .43 |

|    | 8.2 QFN24 PCB Land Pattern .  |        |     |  |  |  |   |   |  |  |  |  |  |  | .45 |

|    | 8.3 QFN24 Package Marking .   |        |     |  |  |  |   |   |  |  |  |  |  |  | .46 |

| 9. | QFP32 Package Specifications  |        |     |  |  |  |   |   |  |  |  |  |  |  | 47  |

|    | 9.1 QFP32 Package Dimensions  |        |     |  |  |  |   |   |  |  |  |  |  |  | .47 |

|    | 9.2 QFP32 PCB Land Pattern .  |        |     |  |  |  | - | - |  |  |  |  |  |  | .49 |

|    | 9.3 QFP32 Package Marking .   |        |     |  |  |  |   |   |  |  |  |  |  |  | .50 |

| 10 | . Revision History            |        |     |  |  |  |   |   |  |  |  |  |  |  | 51  |

|    | 10.1 Revision 1.2             |        |     |  |  |  |   |   |  |  |  |  |  |  | .51 |

|    | 10.2 Revision 1.1             |        |     |  |  |  |   |   |  |  |  |  |  |  | .51 |

| Та | ble of Contents               |        |     |  |  |  |   |   |  |  |  |  |  |  | 52  |