#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Detailo                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e600                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               |                                                                         |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | · · · · · · · · · · · · · · · · · · ·                                   |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | · · · · · · · · · · · · · · · · · · ·                                   |

| USB                             | · · · · · · · · · · · · · · · · · · ·                                   |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | <u>.</u>                                                                |

| Package / Case                  | 1023-BBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dhx1000gc |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1 Key Features

The following lists an overview of the MPC8641 key feature set:

- Major features of the e600 core are as follows:

- High-performance, 32-bit superscalar microprocessor that implements the PowerPC ISA

- Eleven independent execution units and three register files

- Branch processing unit (BPU)

- Four integer units (IUs) that share 32 GPRs for integer operands

- 64-bit floating-point unit (FPU)

- Four vector units and a 32-entry vector register file (VRs)

- Three-stage load/store unit (LSU)

- Three issue queues, FIQ, VIQ, and GIQ, can accept as many as one, two, and three instructions, respectively, in a cycle.

- Rename buffers

- Dispatch unit

- Completion unit

- Two separate 32-Kbyte instruction and data level 1 (L1) caches

- Integrated 1-Mbyte, eight-way set-associative unified instruction and data level 2 (L2) cache with ECC

- 36-bit real addressing

- Separate memory management units (MMUs) for instructions and data

- Multiprocessing support features

- Power and thermal management

- Performance monitor

- In-system testability and debugging features

- Reliability and serviceability

- MPX coherency module (MCM)

- Ten local address windows plus two default windows

- Optional low memory offset mode for core 1 to allow for address disambiguation

- Address translation and mapping units (ATMUs)

- Eight local access windows define mapping within local 36-bit address space

- Inbound and outbound ATMUs map to larger external address spaces

- Three inbound windows plus a configuration window on PCI Express

- Four inbound windows plus a default window on serial RapidIO

- Four outbound windows plus default translation for PCI Express

- Eight outbound windows plus default translation for serial RapidIO with segmentation and sub-segmentation support

2

2

2

4

5

0.08

0.70

0.66

0.10

0.45

12.00

9.80

7.70

0.0125

The maximum power dissipation for individual power supplies of the MPC8641D is shown in Table 5.

#### **Supply Voltage** Power **Component Description** Notes (Volts) (Watts) Per Core voltage Supply V<sub>DD</sub>\_Core0/V<sub>DD</sub>\_Core1 = 1.1 V @ 1500 MHz 21.00 Per Core PLL voltage supply AV<sub>DD</sub>\_Core0/AV<sub>DD</sub>\_Core1 = 1.1 V @ 1500 MHz 0.0125 Per Core voltage Supply V<sub>DD</sub>\_Core0/V<sub>DD</sub>\_Core1 = 1.05 V @ 1333 MHz 17.00 AV<sub>DD</sub>\_Core0/AV<sub>DD</sub>\_Core1 = 1.05 V @ 1333 MHz Per Core PLL voltage supply 0.0125 Per Core voltage Supply V<sub>DD</sub>\_Core0/V<sub>DD</sub>\_Core1 = 0.95 V @ 1000 MHz 11.50 5 AV<sub>DD</sub>\_Core0/AV<sub>DD</sub>\_Core1 = 0.95 V @ 1000 MHz Per Core PLL voltage supply 0.0125 5 DDR Controller I/O voltage supply Dn\_GV<sub>DD</sub> = 2.5 V @ 400 MHz 0.80 2 Dn\_GV<sub>DD</sub> = 1.8 V @ 533 MHz 2 0.68 Dn\_GV<sub>DD</sub> = 1.8 V @ 600 MHz 0.77 2 $L/TV_{DD} = 3.3 V$ 16-bit FIFO @ 200 MHz 2, 3 0.11

$L/TV_{DD} = 3.3 V$

$SV_{DD} = 1.1 V$

$XV_{DD}$ SRDSn = 1.1 V

$AV_{DD}$ SRDS1/ $AV_{DD}$ SRDS2 = 1.1 V

OV<sub>DD</sub> = 3.3 V

V<sub>DD</sub>\_PLAT = 1.1 V @ 600 MHz

V<sub>DD</sub>\_PLAT = 1.05 Vn @ 500 MHz

V<sub>DD</sub>\_PLAT = 1.05 Vn @ 400 MHz

$AV_{DD}$ PLAT,  $AV_{DD}$ LB = 1.1 V

# Table 5. MPC8641D Individual Supply Maximum Power Dissipation <sup>1</sup>

Platform source Supply Platform source Supply Platform, Local Bus PLL voltage Supply

eTsec 1&2/3&4 Voltage Supply non-FIFO eTsec*n* Voltage Supply

x8 SerDes transceiver Supply

x8 SerDes I/O Supply

SerDes PLL voltage supply Port 1 or 2

Platform I/O Supply

Platform source Supply

#### Notes:

1. This is a maximum power supply number which is provided for power supply and board design information. The numbers are based on 100% bus utilization for each component. The components listed are not expected to have 100% bus usage simultaneously for all components. Actual numbers may vary based on activity.

2. Number is based on a per port/interface value.

3. This is based on one eTSEC port used. Since 16-bit FIFO mode involves two ports, the number will need to be multiplied by two for the total. The other eTSEC protocols dissipate less than this number per port. Note that the power needs to be multiplied by the number of ports used for the protocol for the total eTSEC port power dissipation.

4. This includes Local Bus, DUART, I<sup>2</sup>C, DMA, Multiprocessor Interrupts, System Control & Clocking, Debug, Test, Power management, JTAG and Miscellaneous I/O voltage.

5. These power numbers are for Part Number MC8641xxx1000NX only.  $V_{DD}$ \_Coren = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V.

#### Power Characteristics

The power dissipation for the MPC8641 single core device is shown in Table 6.

| Power Mode | Core Frequency<br>(MHz) | Platform<br>Frequency (MHz) | V <sub>DD</sub> _Coren,<br>V <sub>DD</sub> _PLAT<br>(Volts) | Junction<br>Temperature | Power<br>(Watts) | Notes   |

|------------|-------------------------|-----------------------------|-------------------------------------------------------------|-------------------------|------------------|---------|

| Typical    |                         |                             |                                                             | 65 °C                   | 20.3             | 1, 2    |

| Thermal    | 1500 MHz                | 600 MHz                     | 1.1 V                                                       |                         | 25.2             | 1, 3    |

| Maxim      |                         |                             |                                                             | 105 °C                  | 28.9             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1333 MHz                | 533 MHz                     | 1.05 V                                                      | 0.5                     | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1250 MHz                | 500 MHz                     | 1.05 V                                                      | 0.5                     | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1000 MHz                | 400 MHz                     | 1.05 V                                                      | 0.5                     | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 11.6             | 1, 2, 5 |

| Thermal    | 1000 MHz                | 500 MHz                     | 0.95 V,<br>1.05 V                                           |                         | 14.4             | 1, 3, 5 |

| Maximum    |                         |                             |                                                             | 105 °C                  | 16.5             | 1, 4, 5 |

# Table 6. MPC8641 Power Dissipation (Single Core)

## Notes:

1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

2. Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>\_Core*n*) and 65°C junction temperature (see Table 2)while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz.

3. Thermal power is the average power measured at nominal core voltage (V<sub>DD</sub>\_Core*n*) and maximum operating junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz and a typical workload on platform interfaces.

4. Maximum power is the maximum power measured at nominal core voltage (V<sub>DD</sub>\_Coren) and maximum operating junction temperature (see Table 2) while running a test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep all the execution units maximally busy.

5. These power numbers are for Part Number MC8641xx1000NX only. V<sub>DD</sub>\_Coren = 0.95 V and V<sub>DD</sub>\_PLAT = 1.05 V.

# 4 Input Clocks

Table 7 provides the system clock (SYSCLK) DC specifications for the MPC8641.

# Table 7. SYSCLK DC Electrical Characteristics (OVDD = 3.3 V ± 165 mV)

| Parameter                                                               | Symbol          | Min  | Мах                    | Unit |

|-------------------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                                | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                 | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current<br>( $V_{IN}$ <sup>1</sup> = 0 V or $V_{IN}$ = $V_{DD}$ ) | Ι <sub>ΙΝ</sub> |      | ±5                     | μΑ   |

## Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

# 4.1 System Clock Timing

Table 8 provides the system clock (SYSCLK) AC timing specifications for the MPC8641.

# Table 8. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 V \pm 165 mV$ .

| Parameter/Condition       | Symbol                                | Min | Typical | Max    | Unit | Notes |

|---------------------------|---------------------------------------|-----|---------|--------|------|-------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 66  | _       | 166.66 | MHz  | 1     |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 6   | —       | _      | ns   | —     |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2    | ns   | 2     |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | —       | 60     | %    | 3     |

| SYSCLK jitter             | —                                     | _   | —       | 150    | ps   | 4, 5  |

Notes:

- Caution: The MPX clock to SYSCLK ratio and e600 core to MPX clock ratio settings must be chosen such that the resulting SYSCLK frequency, e600 (core) frequency, and MPX clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 18.2, "MPX to SYSCLK PLL Ratio," and Section 18.3, "e600 to MPX clock PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the short term jitter only and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter. Note that the frequency modulation for SYSCLK reduces significantly for the spread spectrum source case. This is to guarantee what is supported based on design.

# 4.1.1 SYSCLK and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 8 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the MPC8641. Note that DDR SDRAM is  $Dn_GV_{DD}(typ) = 2.5$  V and DDR2 SDRAM is  $Dn_GV_{DD}(typ) = 1.8$  V.

# 6.1 DDR SDRAM DC Electrical Characteristics

Table 13 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8641 when  $Dn_GV_{DD}(typ) = 1.8 \text{ V}$ .

| Parameter/Condition                              | Symbol               | Min                                       | Мах                                   | Unit | Notes |

|--------------------------------------------------|----------------------|-------------------------------------------|---------------------------------------|------|-------|

| I/O supply voltage                               | Dn_GV <sub>DD</sub>  | 1.71                                      | 1.89                                  | V    | 1     |

| I/O reference voltage                            | Dn_MV <sub>REF</sub> | $0.49 \times Dn_GV_{DD}$                  | $0.51 	imes Dn_{DD}$                  | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>      | D <i>n</i> _MV <sub>REF</sub> – 0.0<br>4  | D <i>n_</i> MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>      | D <i>n_</i> MV <sub>REF</sub> + 0.1<br>25 | D <i>n_</i> GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>      | -0.3                                      | D <i>n</i> _MV <sub>REF</sub> - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>      | -50                                       | 50                                    | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>      | -13.4                                     | _                                     | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>      | 13.4                                      | —                                     | mA   | —     |

Table 13. DDR2 SDRAM DC Electrical Characteristics for Dn\_GV<sub>DD</sub>(typ) = 1.8 V

#### Notes:

1.  $Dn_{GV_{DD}}$  is expected to be within 50 mV of the DRAM  $Dn_{GV_{DD}}$  at all times.

2.  $Dn_MV_{REF}$  is expected to be equal to  $0.5 \times Dn_GV_{DD}$ , and to track  $Dn_GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $Dn_MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to Dn\_MV<sub>REF</sub>. This rail should track variations in the DC level of Dn\_MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  Dn\_GV<sub>DD</sub>.

Table 14 provides the DDR2 capacitance when  $Dn_{GV_{DD}(typ)} = 1.8 \text{ V}$ .

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $Dn_GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = Dn_GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

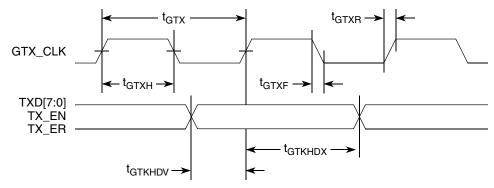

clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC $n_GTX_CLK$  pin (while transmit data appears on TSEC $n_TXD[7:0]$ , for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC $n_GTX_CLK$  as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 18.4.2, "Platform to FIFO Restrictions."

# NOTE

The phase between the output clocks TSEC1\_GTX\_CLK and TSEC2\_GTX\_CLK (ports 1 and 2) is no more than 100 ps. The phase between the output clocks TSEC3\_GTX\_CLK and TSEC4\_GTX\_CLK (ports 3 and 4) is no more than 100 ps.

A summary of the FIFO AC specifications appears in Table 26 and Table 27.

## Table 26. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                                    | Symbol                              | Min | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK clock period (GMII mode)               | t <sub>FIT</sub>                    | 7.0 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK clock period (Encoded mode)            | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK duty cycle                             | t <sub>FITH/</sub> t <sub>FIT</sub> | 45  | 50  | 55   | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>                   | _   | _   | 250  | ps   |

| Rise time TX_CLK (20%-80%)                             | t <sub>FITR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>                   | _   | _   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub>                  | 2.0 | _   | _    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub>                  | 0.5 |     | 3.0  | ns   |

## Table 27. FIFO Mode Receive AC Timing Specification

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol                              | Min | Тур | Мах  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period (GMII mode)             | t <sub>FIR</sub> 1                  | 7.0 | 8.0 | 100  | ns   |

| RX_CLK clock period (Encoded mode)          | t <sub>FIR</sub> 1                  | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | —   | —   | 250  | ps   |

| Rise time RX_CLK (20%-80%)                  | t <sub>FIRR</sub>                   | —   | _   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | —   | _   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | _   | —    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 | —   | —    | ns   |

±100 ppm tolerance on RX\_CLK frequency

## MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

1

## Table 28. GMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV\_{DD} of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                    | Symbol <sup>1</sup> | Min | Тур | Max | Unit |

|----------------------------------------|---------------------|-----|-----|-----|------|

| GTX_CLK data clock fall time (80%-20%) | t <sub>GTXF</sub> 2 |     | _   | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

2. Guaranteed by design.

Figure 10 shows the GMII transmit AC timing diagram.

Figure 10. GMII Transmit AC Timing Diagram

# 8.2.2.2 GMII Receive AC Timing Specifications

Table 29 provides the GMII receive AC timing specifications.

## Table 29. GMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub> 3                  | _   | 8.0 |     | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.5 | _   |     | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>GRXR</sub> 2                 | _   |     | 1.0 | ns   |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

# 8.2.3.2 MII Receive AC Timing Specifications

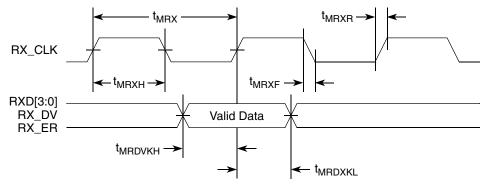

Table 31 provides the MII receive AC timing specifications.

# Table 31. MII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2,3                | —    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub> 3                  | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>MRXR</sub> 2                 | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | —   | 4.0 | ns   |

## Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

3. ±100 ppm tolerance on RX\_CLK frequency

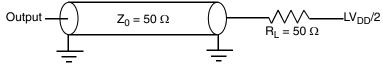

Figure 14 provides the AC test load for eTSEC.

Figure 14. eTSEC AC Test Load

Figure 15 shows the MII receive AC timing diagram.

Figure 15. MII Receive AC Timing Diagram

# 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

# 8.2.7.1 RMII Transmit AC Timing Specifications

The RMII transmit AC timing specifications are in Table 36.

## Table 36. RMII Transmit AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min | Тур  | Мах  | Unit |

|--------------------------------------------|-------------------------------------|-----|------|------|------|

| REF_CLK clock period                       | t <sub>RMT</sub>                    | _   | 20.0 | —    | ns   |

| REF_CLK duty cycle                         | t <sub>RMTH</sub> /t <sub>RMT</sub> | 35  | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                | t <sub>RMTJ</sub>                   | _   | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                | t <sub>RMTR</sub>                   | 1.0 | _    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                | t <sub>RMTF</sub>                   | 1.0 | _    | 2.0  | ns   |

| REF_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>                  | 1.0 | _    | 10.0 | ns   |

## Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

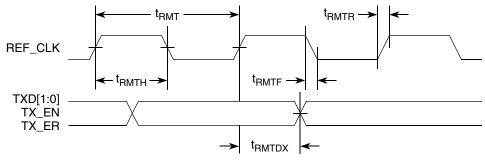

Figure 20 shows the RMII transmit AC timing diagram.

Figure 20. RMII Transmit AC Timing Diagram

Local Bus

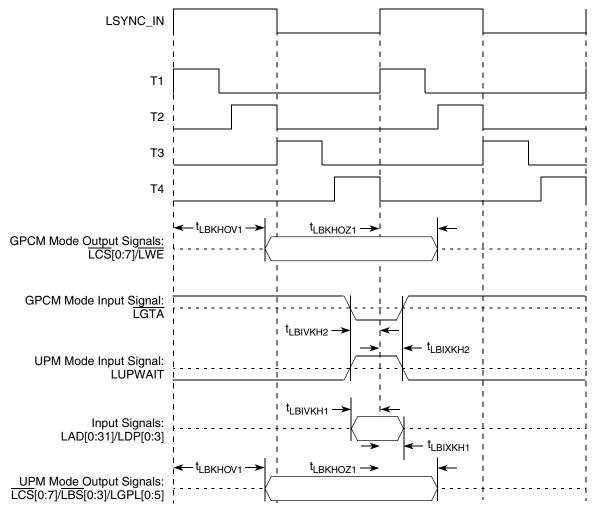

Figure 30. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 or 8 (clock ratio of 8 or 16) (PLL Enabled)

JTAG

# 11 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8641/D.

# **11.1 JTAG DC Electrical Characteristics**

Table 43 provides the DC electrical characteristics for the JTAG interface.

# Table 43. JTAG DC Electrical Characteristics

| Parameter                                                                        | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                                         | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                          | V <sub>IL</sub> | - 0.3                  | 0.8                    | V    |

| Input current<br>$(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$                | I <sub>IN</sub> | _                      | ±5                     | μΑ   |

| High-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OH</sub> = −100 μA) | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | —                      | V    |

| Low-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OL</sub> = 100 μA)   | V <sub>OL</sub> | —                      | 0.2                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 11.2 JTAG AC Electrical Specifications

Table 44 provides the JTAG AC timing specifications as defined in Figure 33 through Figure 35.

# Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 3).

| Parameter                                         | Symbol <sup>2</sup>                   | Min | Max  | Unit | Notes |

|---------------------------------------------------|---------------------------------------|-----|------|------|-------|

| JTAG external clock frequency of operation        | f <sub>JTG</sub>                      | 0   | 33.3 | MHz  | —     |

| JTAG external clock cycle time                    | t <sub>JTG</sub>                      | 30  | _    | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V | t <sub>JTKHKL</sub>                   | 15  | _    | ns   | _     |

| JTAG external clock rise and fall times           | t <sub>JTGR</sub> & t <sub>JTGF</sub> | 0   | 2    | ns   | 6     |

| TRST assert time                                  | t <sub>TRST</sub>                     | 25  | —    | ns   | 3     |

| Input setup times:                                |                                       |     |      | ns   |       |

| Boundary-scan data                                | t <sub>JTDVKH</sub>                   | 4   |      |      | 4     |

| TMS, TDI                                          | t <sub>JTIVKH</sub>                   | 0   | —    |      |       |

| Input hold times:                                 |                                       |     |      | ns   |       |

| Boundary-scan data                                | t <sub>JTDXKH</sub>                   | 20  | _    |      | 4     |

| TMS, TDI                                          | t <sub>JTIXKH</sub>                   | 25  | _    |      |       |

| Valid times:                                      |                                       |     |      | ns   |       |

| Boundary-scan data                                | t <sub>JTKLDV</sub>                   | 4   | 20   |      | 5     |

| TDO                                               | t <sub>JTKLOV</sub>                   | 4   | 25   |      |       |

PCI Express

# 14.1 DC Requirements for PCI Express SD*n*\_REF\_CLK and SD*n*\_REF\_CLK

For more information, see Section 13.2, "SerDes Reference Clocks."

# 14.2 AC Requirements for PCI Express SerDes Clocks

Table 48 lists AC requirements.

Table 48. SDn\_REF\_CLK and SDn\_REF\_CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10      | —   | ns    |       |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | —   | _       | 100 | ps    | _     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    |       |

# 14.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a +/-300 ppm tolerance.

# 14.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the Transport and Data Link layer please use the PCI EXPRESS Base Specification. REV. 1.0a document.

# 14.4.1 Differential Transmitter (TX) Output

Table 49 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

| Symbol                   | Parameter                                                   | Min    | Nom  | Max    | Units | Comments                                                                                                                                                           |

|--------------------------|-------------------------------------------------------------|--------|------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                       | Unit Interval                                               | 399.88 | 400  | 400.12 | ps    | Each UI is 400 ps $\pm$ 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1.                                                    |

| V <sub>TX-DIFFp-p</sub>  | Differential<br>Peak-to-Peak<br>Output Voltage              | 0.8    | _    | 1.2    | V     | $V_{TX-DIFFp-p} = 2^{*} V_{TX-D+} - V_{TX-D-} $ See Note 2.                                                                                                        |

| V <sub>TX-DE-RATIO</sub> | De- Emphasized<br>Differential<br>Output Voltage<br>(Ratio) | -3.0   | -3.5 | -4.0   | dB    | Ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 2. |

Table 49. Differential Transmitter (TX) Output Specifications

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Max  |        | Notes                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI p-p | _                                                                                |  |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/– 100 ppm                                                                      |  |

| Table 57. Long Run Transmitter AC Timing Specifications—3.125 GBaud |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

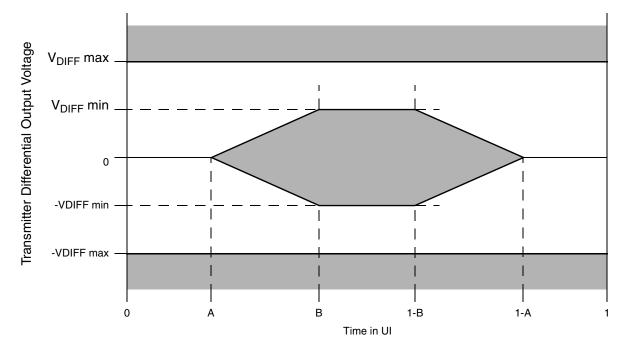

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the Transmitter Output Compliance Mask shown in Figure 54 with the parameters specified in Table 58 when measured at the output pins of the device and the device is driving a  $100 \Omega + -5\%$  differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized.

| Transmitter Type        | V <sub>DIFF</sub> min<br>(mV) | V <sub>DIFF</sub> max<br>(mV) | A (UI) | B (UI) |

|-------------------------|-------------------------------|-------------------------------|--------|--------|

| 1.25 GBaud short range  | 250                           | 500                           | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                           | 800                           | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                           | 500                           | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                           | 800                           | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                           | 500                           | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                           | 800                           | 0.175  | 0.39   |

Table 58. Transmitter Differential Output Eye Diagram Parameters

# 15.7 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to (0.8)\*(Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25 Ohm resistive for common mode.

| Characteristic                                     | Symbol          | Ra   | nge               | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit   | notes                                                        |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                         |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                         |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                         |

| Multiple Input Skew                                | S <sub>MI</sub> | _    | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | —                                                            |

| Unit Interval                                      | UI              | 800  | 800               | ps     | +/- 100 ppm                                                  |

Table 59. Receiver AC Timing Specifications—1.25 GBaud

## Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Continuous Jitter Test Pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 Volts differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100 \Omega$  resistive +/- 5% differential to 2.5 GHz.

# 15.9.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter Test Pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 Volts differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

# 15.9.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of 100  $\Omega$  resistive +/- 5% differential to 2.5 GHz.

# 15.9.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 8.6 and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 8-4 and Table 8-11. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 8.6 is then added to the signal and the test load is replaced by the receiver being tested.

| Name <sup>1</sup>  | Package Pin Number                                                                                                                                                      | Pin Type         | Power Supply     | Notes    |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------|

| TSEC3_TX_EN        | AH19                                                                                                                                                                    | 0                | TV <sub>DD</sub> | 36       |

| TSEC3_TX_ER        | AH17                                                                                                                                                                    | 0                | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK       | AH18                                                                                                                                                                    | I                | TV <sub>DD</sub> | 40       |

| TSEC3_GTX_CLK      | AG19                                                                                                                                                                    | 0                | TV <sub>DD</sub> | 41       |

| TSEC3_CRS          | AE15                                                                                                                                                                    | I/O              | TV <sub>DD</sub> | 37       |

| TSEC3_COL          | AF15                                                                                                                                                                    | I                | TV <sub>DD</sub> | —        |

| TSEC3_RXD[0:7]     | AJ17, AE16, AH16, AH14, AJ19, AH15, AG16, AE19                                                                                                                          | I                | TV <sub>DD</sub> | _        |

| TSEC3_RX_DV        | AG15                                                                                                                                                                    | I                | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER        | AF16                                                                                                                                                                    | I                | TV <sub>DD</sub> | _        |

| TSEC3_RX_CLK       | AJ18                                                                                                                                                                    | I                | TV <sub>DD</sub> | 40       |

|                    | eTSEC Port 4 Signa                                                                                                                                                      | als <sup>5</sup> | · · ·            |          |

| TSEC4_TXD[0:3]     | AC18, AC16, AD18, AD17                                                                                                                                                  | 0                | TV <sub>DD</sub> | 6        |

| TSEC4_TXD[4]       | AD16                                                                                                                                                                    | 0                | TV <sub>DD</sub> | 25       |

| TSEC4_TXD[5:7]     | AB18, AB17, AB16                                                                                                                                                        | 0                | TV <sub>DD</sub> | 6        |

| TSEC4_TX_EN        | AF17                                                                                                                                                                    | 0                | TV <sub>DD</sub> | 36       |

| TSEC4_TX_ER        | AF19                                                                                                                                                                    | 0                | TV <sub>DD</sub> | —        |

| TSEC4_TX_CLK       | AF18                                                                                                                                                                    | I                | TV <sub>DD</sub> | 40       |

| TSEC4_GTX_CLK      | AG17                                                                                                                                                                    | 0                | TV <sub>DD</sub> | 41       |

| TSEC4_CRS          | AB14                                                                                                                                                                    | I/O              | TV <sub>DD</sub> | 37       |

| TSEC4_COL          | AC13                                                                                                                                                                    | I                | TV <sub>DD</sub> | _        |

| TSEC4_RXD[0:7]     | AG14, AD13, AF13, AD14, AE14, AB15, AC14, AE17                                                                                                                          | I                | TV <sub>DD</sub> | _        |

| TSEC4_RX_DV        | AC15                                                                                                                                                                    | I                | TV <sub>DD</sub> |          |

| TSEC4_RX_ER        | AF14                                                                                                                                                                    | I                | TV <sub>DD</sub> |          |

| TSEC4_RX_CLK       | AG13                                                                                                                                                                    | I                | TV <sub>DD</sub> | 40       |

|                    | Local Bus Signals                                                                                                                                                       | s <sup>5</sup>   | · · ·            |          |

| LAD[0:31]          | A30, E29, C29, D28, D29, H25, B29, A29,<br>C28, L22, M22, A28, C27, H26, G26, B27,<br>B26, A27, E27, G25, D26, E26, G24, F27,<br>A26, A25, C25, H23, K22, D25, F25, H22 | I/O              | OV <sub>DD</sub> | 6        |

| LDP[0:3]           | A24, E24, C24, B24                                                                                                                                                      | I/O              | OV <sub>DD</sub> | 6, 22    |

| LA[27:31]          | J21, K21, G22, F24, G21                                                                                                                                                 | 0                | OV <sub>DD</sub> | 6, 22    |

| LCS[0:4]           | A22, C22, D23, E22, A23                                                                                                                                                 | 0                | OV <sub>DD</sub> | 7        |

| LCS[5]/DMA_DREQ[2] | B23                                                                                                                                                                     | 0                | OV <sub>DD</sub> | 7, 9, 10 |

# Table 63. MPC8641 Signal Reference by Functional Block (continued)

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup> Package Pin Number | Pin Type | Power Supply | Notes |

|--------------------------------------|----------|--------------|-------|

|--------------------------------------|----------|--------------|-------|

#### Note:

- 1. Multi-pin signals such as D1\_MDQ[0:63] and D2\_MDQ[0:63] have their physical package pin numbers listed in order corresponding to the signal names.

- 2. Stub Series Terminated Logic (SSTL-18 and SSTL-25) type pins.

- 3. If a DDR port is not used, it is possible to leave the related power supply (Dn\_GVDD, Dn\_MVREF) turned off at reset. Note that these power supplies can only be powered up again at reset for functionality to occur on the DDR port.

- 4. Low Voltage Differential Signaling (LVDS) type pins.

- 5. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 6. This pin is a reset configuration pin and appears again in the Reset Configuration Signals section of this table. See the Reset Configuration Signals section of this table for config name and connection details.

- 7. Recommend a weak pull-up resistor (1–10 k $\Omega$ ) be placed from this pin to its power supply.

- 8. Recommend a weak pull-down resistor (2–10 k $\Omega$ ) be placed from this pin to ground.

- 9. This multiplexed pin has input status in one mode and output in another

- 10. This pin is a multiplexed signal for different functional blocks and appears more than once in this table.

- 11. This pin is open drain signal.

- 12. Functional only on the MPC8641D.

- 13. These pins should be left floating.

- 14. These pins should be connected to SV<sub>DD</sub>.

- 15. These pins should be pulled to ground with a strong resistor (270- $\Omega$  to 330- $\Omega$ ).

- 16. These pins should be connected to OVDD.

- 17. This is a SerDes PLL/DLL digital test signal and is only for factory use.

- 18. This is a SerDes PLL/DLL analog test signal and is only for factory use.

- 19. This pin should be pulled to ground with a 100- $\Omega$  resistor.

- 20. The pins in this section are reset configuration pins. Each pin has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 21. Should be pulled down at reset if platform frequency is at 400 MHz.

- 22. These pins require 4.7-kΩ pull-up or pull-down resistors and must be driven as they are used to determine PLL configuration ratios at reset.

- 23. This output is actively driven during reset rather than being tri-stated during reset.

- 24 These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 25. This pin should NOT be pulled down (or driven low) during reset.

- 26. These are test signals for factory use only and must be pulled up (100- $\Omega$  to 1- k $\Omega$ ) to OVDD for normal machine operation.

- 27. Dn\_MDIC[0] should be connected to ground with an 18-Ω resistor +/- 1-Ω and Dn\_MDIC[1] should be connected Dn\_GVDD with an 18-Ω resistor +/- 1-Ω. These pins are used for automatic calibration of the DDR IOs.

- 28. Pin N18 is recommended as a reference point for determining the voltage of V<sub>DD</sub>\_PLAT and is hence considered as the V<sub>DD</sub>\_PLAT sensing voltage and is called SENSEVDD\_PLAT.

- 29. Pin P18 is recommended as the ground reference point for SENSEVDD\_PLAT and is called SENSEVSS\_PLAT.

- 30. This pin should be pulled to ground with a 200- $\Omega$  resistor.

- 31. These pins are connected to the power/ground planes internally and may be used by the core power supply to improve tracking and regulation.

- 32. Must be tied low if unused

- 33. These pins may be used as defined functional reset configuration pins in the future. Please include a resistor pull up/down option to allow flexibility of future designs.

- 34. Used as serial data output for SRIO 1x/4x link.

- 35. Used as serial data input for SRIO 1x/4x link.

- 36. This pin requires an external 4.7-kΩ pull-down resistor to pevent PHY from seeing a valid Transmit Enable before it is actively driven.

# **18.4.1 SYSCLK to Platform Frequency Options**

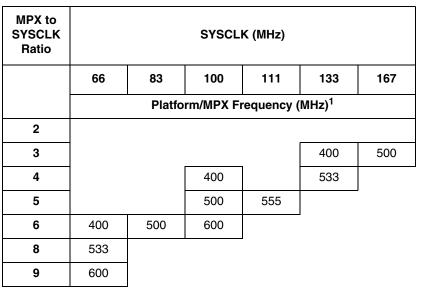

Table 70 shows some SYSCLK frequencies and the expected MPX frequency values based on the MPX clock to SYSCLK ratio. Note that frequencies between 400 MHz and 500 MHz are NOT supported on the platform. See note regarding *cfg\_platform\_freq* in Section 17, "Signal Listings," because it is a reset configuration pin that is related to platform frequency.

Table 70. Frequency Options of SYSCLK with Respect to Platform/MPX Clock Speed

SYSCLK frequency range is 66-167 MHz. Platform clock/ MPX frequency range is 400 MHz, 500-600 MHz.

# 18.4.2 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

```

FIFO TX/RX clock frequency <= platform clock frequency/4.2

```

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz

For FIFO encoded mode:

```

FIFO TX/RX clock frequency <= platform clock frequency/3.2

```

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

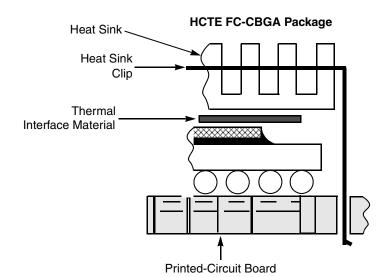

# Figure 59. FC-CBGA Package Exploded Cross-Sectional View with Several Heat Sink Options

There are several commercially-available heat sinks for the MPC8641 provided by the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                             | 603-224-9988    |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------|

| Advanced Thermal Solutions<br>89 Access Road #27.<br>Norwood, MA02062<br>Internet: www.qats.com                             | 781-769-2800    |

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                            | 408-749-7601    |

| Calgreg Thermal Solutions<br>60 Alhambra Road, Suite 1<br>Warwick, RI 02886<br>Internet: www.calgreg.com                    | 888-732-6100    |

| International Electronic Research Corporation (IEI<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com  | RC)818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-thermal.com | 408-436-8770    |

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com | 800-347-4572 |

|------------------------------------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801<br>Internet: www.chomerics.com                                    | 781-935-4850 |

| Dow-Corning Corporation<br>Corporate Center<br>PO Box 994<br>Midland, MI 48686-0994<br>Internet: www.dowcorning.com    | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                         | 888-642-7674 |

| Thermagon Inc.<br>4707 Detroit Ave.<br>Cleveland, OH 44102<br>Internet: www.thermagon.com                              | 888-246-9050 |

The following section provides a heat sink selection example using one of the commercially available heat sinks.

# **19.2.3 Heat Sink Selection Example**

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$T_j = T_i + T_r + (R_{\theta JC} + R_{\theta int} + R_{\theta sa}) \times P_d$

where:

T<sub>i</sub> is the die-junction temperature

T<sub>i</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$R_{\theta JC}$  is the junction-to-case thermal resistance

$R_{\theta int}$  is the adhesive or interface material thermal resistance

$R_{\theta sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation, the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_j)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material ( $R_{0int}$ ) is typically about 0.2°C/W. For