#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e600                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               |                                                                         |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | · ·                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | · ·                                                                     |

| USB                             | · ·                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 1023-BBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dhx1000ne |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**RESET Initialization**

# 5 **RESET** Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8641. Table 11 provides the RESET initialization AC timing specifications.

| Parameter/Condition                                                                                           | Min | Мах | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                             | 100 | —   | μs      | —     |

| Minimum assertion time for SRESET_0 & SRESET_1                                                                | 3   | —   | SYSCLKs | 1     |

| Platform PLL input setup time with stable SYSCLK before HRESET negation                                       | 100 | _   | μs      | 2     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET                   | 4   | _   | SYSCLKs | 1     |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET                 | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively<br>driven POR configs with respect to negation of<br>HRESET |     | 5   | SYSCLKs | 1     |

### Table 11. RESET Initialization Timing Specifications

### Notes:

1. SYSCLK is the primary clock input for the MPC8641.

2 This is related to HRESET assertion time. Stable PLL configuration inputs are required when a stable SYSCLK is applied. See the *MPC8641D Integrated Host Processor Reference Manual* for more details on the power-on reset sequence.

### Table 12 provides the PLL lock times.

### Table 12. PLL Lock Times

| Parameter/Condition                | Min | Мах | Unit | Notes |

|------------------------------------|-----|-----|------|-------|

| (Platform and E600) PLL lock times | —   | 100 | μs   | 1     |

| Local bus PLL                      | —   | 50  | μS   | —     |

### Note:

1. The PLL lock time for e600 PLLs require an additional 255 MPX\_CLK cycles.

### 6.2 DDR SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR SDRAM Input AC Timing Specifications

Table 18 provides the input AC timing specifications for the DDR2 SDRAM when  $Dn GV_{DD}(typ)=1.8 V$ .

### Table 18. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions

| Parameter                                        | Symbol | Min                                                                          | Мах                                                                          | Unit | Notes |

|--------------------------------------------------|--------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|-------|

| AC input low voltage<br>400, 533 MHz<br>600 MHz  |        | _                                                                            | D <i>n_</i> MV <sub>REF</sub> – 0.25<br>D <i>n_</i> MV <sub>REF</sub> – 0.20 | V    | _     |

| AC input high voltage<br>400, 533 MHz<br>600 MHz |        | D <i>n_</i> MV <sub>REF</sub> + 0.25<br>D <i>n_</i> MV <sub>REF</sub> + 0.20 | _                                                                            | V    | _     |

Table 19 provides the input AC timing specifications for the DDR SDRAM when  $Dn_GV_{DD}(typ)=2.5$  V.

Table 19. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions.

| Parameter             | Symbol          | Min                                  | Мах                                  | Unit | Notes |

|-----------------------|-----------------|--------------------------------------|--------------------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                                    | D <i>n</i> _MV <sub>REF</sub> – 0.31 | V    | _     |

| AC input high voltage | V <sub>IH</sub> | D <i>n</i> _MV <sub>REF</sub> + 0.31 | _                                    | V    | _     |

Table 20 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 20. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions.

| Parameter                            | Symbol              | Min  | Мах | Unit | Notes |

|--------------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for<br>MDQS—MDQ/MECC | <sup>t</sup> CISKEW | —    |     | ps   | 1, 2  |

| 600 MHz                              | —                   | -240 | 240 | —    | 3     |

| 533 MHz                              | —                   | -300 | 300 | —    | 3     |

| 400 MHz                              | —                   | -365 | 365 | —    |       |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

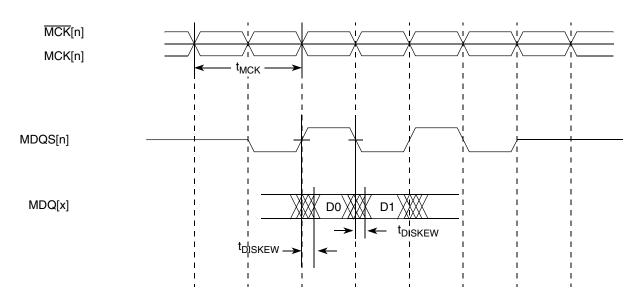

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> =+/-(T/4 - abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

- 3. Maximum DDR1 frequency is 400 MHz.

#### DDR and DDR2 SDRAM

Figure 4 shows the DDR SDRAM input timing for the MDQS to MDQ skew measurement (tDISKEW).

Figure 4. DDR Input Timing Diagram for tDISKEW

### 6.2.2 DDR SDRAM Output AC Timing Specifications

Table 21. DDR SDRAM Output AC Timing Specifications

At recommended operating conditions.

| Parameter                                       | Symbol <sup>1</sup>                 | Min              | Мах              | Unit | Notes       |

|-------------------------------------------------|-------------------------------------|------------------|------------------|------|-------------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing       | t <sub>MCK</sub>                    | 3                | 10               | ns   | 2           |

| MCK duty cycle<br>600 MHz<br>533 MHz<br>400 MHz | t <sub>MCKH</sub> /t <sub>MCK</sub> | 47.5<br>47<br>47 | 52.5<br>53<br>53 | %    | 8<br>9<br>9 |

| ADDR/CMD output setup with respect to MCK       | t <sub>DDKHAS</sub>                 |                  |                  | ns   | 3           |

| 600 MHz                                         |                                     | 1.10             | —                |      | 7           |

| 533 MHz                                         |                                     | 1.48             | _                |      | 7           |

| 400 MHz                                         |                                     | 1.95             | —                |      |             |

| ADDR/CMD output hold with respect to MCK        | t <sub>DDKHAX</sub>                 |                  |                  | ns   | 3           |

| 600 MHz                                         |                                     | 1.10             | —                |      | 7           |

| 533 MHz                                         |                                     | 1.48             | _                |      | 7           |

| 400 MHz                                         |                                     | 1.95             | —                |      |             |

| MCS[n] output setup with respect to MCK         | t <sub>DDKHCS</sub>                 |                  |                  | ns   | 3           |

| 600 MHz                                         |                                     | 1.10             | —                |      | 7           |

| 533 MHz                                         |                                     | 1.48             | _                |      | 7           |

| 400 MHz                                         |                                     | 1.95             | —                |      |             |

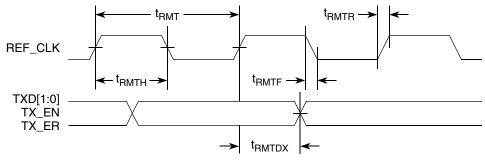

### 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

### 8.2.7.1 RMII Transmit AC Timing Specifications

The RMII transmit AC timing specifications are in Table 36.

### Table 36. RMII Transmit AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min | Тур  | Мах  | Unit |

|--------------------------------------------|-------------------------------------|-----|------|------|------|

| REF_CLK clock period                       | t <sub>RMT</sub>                    | _   | 20.0 | —    | ns   |

| REF_CLK duty cycle                         | t <sub>RMTH</sub> /t <sub>RMT</sub> | 35  | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                | t <sub>RMTJ</sub>                   | _   | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                | t <sub>RMTR</sub>                   | 1.0 | _    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                | t <sub>RMTF</sub>                   | 1.0 | _    | 2.0  | ns   |

| REF_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>                  | 1.0 | _    | 10.0 | ns   |

### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

Figure 20 shows the RMII transmit AC timing diagram.

Figure 20. RMII Transmit AC Timing Diagram

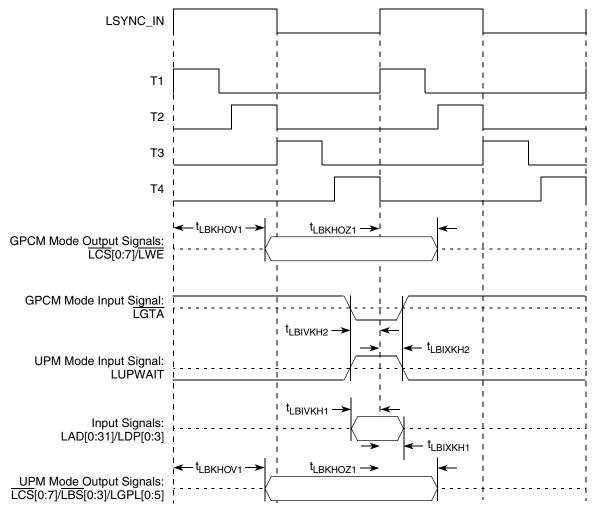

Local Bus

Figure 30. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 or 8 (clock ratio of 8 or 16) (PLL Enabled)

### Table 45. I<sup>2</sup>C DC Electrical Characteristics (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                    | Symbol | Min | Мах | Unit | Notes |

|------------------------------|--------|-----|-----|------|-------|

| Capacitance for each I/O pin | CI     | _   | 10  | pF   | —     |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8641 Integrated Host Processor Reference Manual for information on the digital filter used.

3. I/O pins will obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# 12.2 I<sup>2</sup>C AC Electrical Specifications

Table 46 provides the AC timing parameters for the  $I^2C$  interfaces.

### Table 46. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 45).

| Parameter                                                                                    | Symbol <sup>1</sup>   | Min                                  | Мах              | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>      | 0                                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub> 4   | 1.3                                  | _                | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub> 4   | 0.6                                  | _                | μs   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> 4 | 0.6                                  | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> 4 | 0.6                                  | _                | μS   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> 4 | 100                                  | _                | ns   |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>i2DXKL</sub>   | 0 <sup>2</sup>                       |                  | μs   |

| Rise time of both SDA and SCL signals                                                        | t <sub>I2CR</sub>     | 20 + 0.1 C <sub>B</sub> <sup>5</sup> | 300              | ns   |

| Fall time of both SDA and SCL signals                                                        | t <sub>I2CF</sub>     | 20 + 0.1 C <sub>b</sub> <sup>5</sup> | 300              | ns   |

| Data output delay time                                                                       | t <sub>I2OVKL</sub>   | —                                    | 0.9 <sup>3</sup> | μs   |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub>   | 0.6                                  | _                | μs   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>   | 1.3                                  | —                | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>       | $0.1 \times OV_{DD}$                 | _                | V    |

#### High-Speed Serial Interfaces (HSSI)

- The input amplitude requirement

- This requirement is described in detail in the following sections.

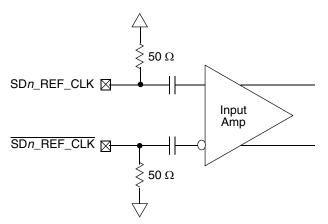

Figure 39. Receiver of SerDes Reference Clocks

### 13.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the MPC8641D SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below.

- Differential Mode

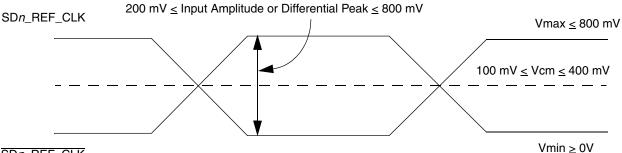

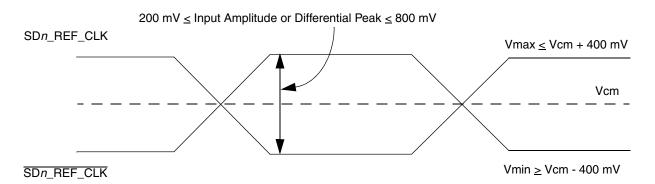

- The input amplitude of the differential clock must be between 400 mV and 1600 mV differential peak-peak (or between 200 mV and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 13.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 mV and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

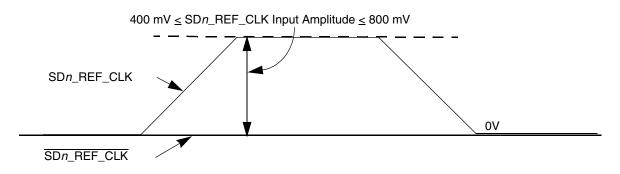

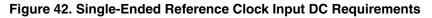

- Single-ended Mode

- The reference clock can also be single-ended. The SDn\_REF\_CLK input amplitude (single-ended swing) must be between 400 mV and 800 mV peak-peak (from Vmin to Vmax) with SDn\_REF\_CLK either left unconnected or tied to ground.

The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

— To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

SDn\_REF\_CLK

### Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

#### High-Speed Serial Interfaces (HSSI)

MPC8641D SerDes reference clock input's DC requirement, AC-coupling has to be used. Figure 45 assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from 140  $\Omega$  to 240  $\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8641D SerDes reference clock's differential input amplitude requirement (between 200 mV and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

| Symbol             | Parameter Description                                                                    | Min | Typical | Мах | Units | Comments                                                         |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10(8)   | —   | ns    | 8 ns applies only to serial RapidIO with 125-MHz reference clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | —   | —       | 80  | ps    | _                                                                |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -40 | —       | 40  | ps    | _                                                                |

Table 51. SDn\_REF\_CLK and SDn\_REF\_CLK AC Requirements

## 15.3 Signal Definitions

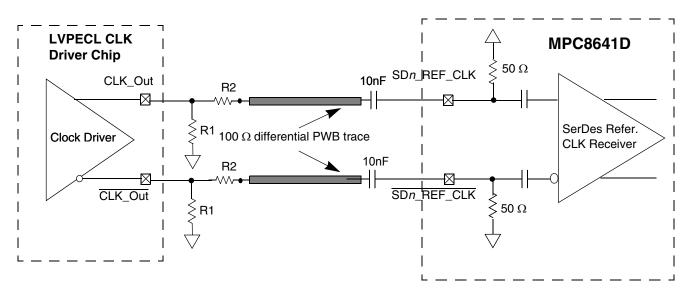

LP-Serial links use differential signaling. This section defines terms used in the description and specification of differential signals. Figure 53 shows how the signals are defined. The figures show waveforms for either a transmitter output (TD and  $\overline{\text{TD}}$ ) or a receiver input (RD and  $\overline{\text{RD}}$ ). Each signal swings between A Volts and B Volts where A > B. Using these waveforms, the definitions are as follows:

- 1. The transmitter output signals and the receiver input signals TD,  $\overline{\text{TD}}$ , RD and  $\overline{\text{RD}}$  each have a peak-to-peak swing of A B Volts

- 2. The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD}$ - $V_{\overline{TD}}$

- 3. The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$

- 4. The differential output signal of the transmitter and the differential input signal of the receiver each range from A B to -(A B) Volts

- 5. The peak value of the differential transmitter output signal and the differential receiver input signal is A B Volts

- 6. The peak-to-peak value of the differential transmitter output signal and the differential receiver input signal is 2 \* (A B) Volts

Figure 53. Differential Peak-Peak Voltage of Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (Current Mode Logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and TD, has a swing that goes between 2.5V and 2.0V. Using these values, the peak-to-peak voltage swing of the signals TD and TD is 500 mV p-p. The differential output signal ranges between 500 mV and -500 mV. The peak differential voltage is 500 mV. The peak-to-peak differential voltage is 1000 mV p-p.

| Characteristic              | Symbol              | R     | ange | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  |        | Notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 320   | 320  | ps     | +/– 100 ppm                                                                      |

| Table 57. Long Run Transmitter AC Timing Specifications—3.125 GBaud |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

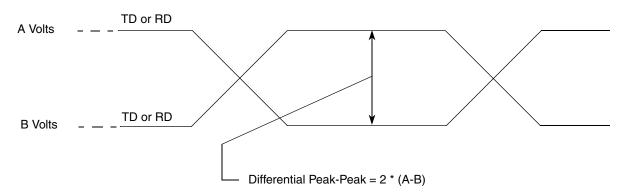

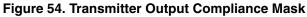

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the Transmitter Output Compliance Mask shown in Figure 54 with the parameters specified in Table 58 when measured at the output pins of the device and the device is driving a  $100 \Omega + -5\%$  differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized.

| Transmitter Type        | V <sub>DIFF</sub> min<br>(mV) | V <sub>DIFF</sub> max<br>(mV) | A (UI) | B (UI) |

|-------------------------|-------------------------------|-------------------------------|--------|--------|

| 1.25 GBaud short range  | 250                           | 500                           | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                           | 800                           | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                           | 500                           | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                           | 800                           | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                           | 500                           | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                           | 800                           | 0.175  | 0.39   |

Table 58. Transmitter Differential Output Eye Diagram Parameters

### 15.7 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to (0.8)\*(Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25 Ohm resistive for common mode.

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min   | Max               | Unit   | Notes                                                        |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200   | 1600              | mV p-p | Measured at receiver                                         |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | —                 | UI p-p | Measured at receiver                                         |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |  |

| Bit Error Rate                                     | BER             | —     | 10 <sup>-12</sup> | —      | —                                                            |  |

| Unit Interval                                      | UI              | 800   | 800               | ps     | +/- 100 ppm                                                  |  |

Table 59. Receiver AC Timing Specifications—1.25 GBaud

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Name <sup>1</sup> | Package Pin Number                          | Pin Type                | Power Supply     | Notes  |

|-------------------|---------------------------------------------|-------------------------|------------------|--------|

| SD1_PLL_TPA       | T28                                         | Analog                  | SV <sub>DD</sub> | 13, 18 |

| SD1_DLL_TPD       | N28                                         | 0                       | SV <sub>DD</sub> | 13, 17 |

| SD1_DLL_TPA       | P31                                         | Analog                  | SV <sub>DD</sub> | 13, 18 |

|                   | High Speed I/O Interface 2                  | (SERDES 2) <sup>4</sup> |                  |        |

| SD2_TX[0:3]       | Y24, AA27, AB25, AC27                       | 0                       | SV <sub>DD</sub> | _      |

| SD2_TX[4:7]       | AE27, AG27, AJ27, AL27                      | 0                       | SV <sub>DD</sub> | 34     |

| SD2_TX[0:3]       | Y25, AA28, AB26, AC28                       | 0                       | SV <sub>DD</sub> | _      |

| SD2_TX[4:7]       | AE28, AG28, AJ28, AL28                      | 0                       | SV <sub>DD</sub> | 34     |

| SD2_RX[0:3]       | Y30, AA32, AB30, AC32                       | I                       | SV <sub>DD</sub> | 32     |

| SD2_RX[4:7]       | AH30, AJ32, AK30, AL32                      | I                       | SV <sub>DD</sub> | 32, 35 |

| SD2_RX[0:3]       | Y29, AA31, AB29, AC31                       | I                       | SV <sub>DD</sub> | —      |

| SD2_RX[4:7]       | AH29, AJ31, AK29, AL31                      | I                       | SV <sub>DD</sub> | 35     |

| SD2_REF_CLK       | AE32                                        | I                       | SV <sub>DD</sub> | _      |

| SD2_REF_CLK       | AE31                                        | I                       | SV <sub>DD</sub> | _      |

| SD2_IMP_CAL_TX    | AM29                                        | Analog                  | SV <sub>DD</sub> | 19     |

| SD2_IMP_CAL_RX    | AA26                                        | Analog                  | SV <sub>DD</sub> | 30     |

| SD2_PLL_TPD       | AF29                                        | 0                       | SV <sub>DD</sub> | 13, 17 |

| SD2_PLL_TPA       | AF31                                        | Analog                  | SV <sub>DD</sub> | 13, 18 |

| SD2_DLL_TPD       | AD29                                        | 0                       | SV <sub>DD</sub> | 13, 17 |

| SD2_DLL_TPA       | AD30                                        | Analog                  | SV <sub>DD</sub> | 13, 18 |

|                   | Special Connection Requi                    | rement pins             |                  |        |

| No Connects       | K24, K25, P28, P29, W26, W27, AD25,<br>AD26 | _                       | -                | 13     |

| Reserved          | H30, R32, V28, AG32                         | _                       | —                | 14     |

| Reserved          | H29, R31, W28, AG31                         | —                       | _                | 15     |

| Reserved          | AD24, AG26                                  | —                       | _                | 16     |

|                   | Ethernet Miscellaneous                      | Signals <sup>5</sup>    | L                |        |

| EC1_GTX_CLK125    | AL23                                        | I                       | LV <sub>DD</sub> | 39     |

| EC2_GTX_CLK125    | AM23                                        | I                       | TV <sub>DD</sub> | 39     |

| EC_MDC            | G31                                         | 0                       | OV <sub>DD</sub> | _      |

| EC_MDIO           | G32                                         | I/O                     | OV <sub>DD</sub> |        |

|                   | eTSEC Port 1 Sign                           | als <sup>5</sup>        | I                |        |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>                | Package Pin Number         | Pin Type          | Power Supply     | Notes          |  |  |

|----------------------------------|----------------------------|-------------------|------------------|----------------|--|--|

| IRQ[9]/DMA_DREQ[3]               | B30                        | I                 | OV <sub>DD</sub> | 10             |  |  |

| IRQ[10]/DMA_DACK[3]              | C30                        | I                 | OV <sub>DD</sub> | 9, 10          |  |  |

| IRQ[11]/DMA_DDONE[3]             | D30                        | I                 | OV <sub>DD</sub> | 9, 10          |  |  |

| IRQ_OUT                          | J26                        | 0                 | OV <sub>DD</sub> | 7, 11          |  |  |

|                                  | DUART Signals <sup>5</sup> | 5                 |                  |                |  |  |

| UART_SIN[0:1]                    | B32, C32                   | I                 | OV <sub>DD</sub> | —              |  |  |

| UART_SOUT[0:1]                   | D31, A32                   | 0                 | OV <sub>DD</sub> | _              |  |  |

| UART_CTS[0:1]                    | A31, B31                   | I                 | OV <sub>DD</sub> | _              |  |  |

| UART_RTS[0:1]                    | C31, E30                   | 0                 | OV <sub>DD</sub> | _              |  |  |

|                                  | I <sup>2</sup> C Signals   |                   |                  |                |  |  |

| IIC1_SDA                         | A16                        | I/O               | OV <sub>DD</sub> | 7, 11          |  |  |

| IIC1_SCL                         | B17                        | I/O               | OV <sub>DD</sub> | 7, 11          |  |  |

| IIC2_SDA                         | A21                        | I/O               | OV <sub>DD</sub> | 7, 11          |  |  |

| IIC2_SCL                         | B21                        | I/O               | OV <sub>DD</sub> | 7, 11          |  |  |

|                                  | System Control Sigr        | nals <sup>5</sup> |                  |                |  |  |

| HRESET                           | B18                        | I                 | OV <sub>DD</sub> | _              |  |  |

| HRESET_REQ                       | K18                        | 0                 | OV <sub>DD</sub> | _              |  |  |

| SMI_0                            | L15                        | I                 | OV <sub>DD</sub> | _              |  |  |

| SMI_1                            | L16                        | I                 | OV <sub>DD</sub> | 12, <i>S</i> 4 |  |  |

| SRESET_0                         | C20                        | I                 | OV <sub>DD</sub> | _              |  |  |

| SRESET_1                         | C21                        | I                 | OV <sub>DD</sub> | 12, <i>S</i> 4 |  |  |

| CKSTP_IN                         | L18                        | I                 | OV <sub>DD</sub> | _              |  |  |

| CKSTP_OUT                        | L17                        | 0                 | OV <sub>DD</sub> | 7, 11          |  |  |

| READY/TRIG_OUT                   | J13                        | 0                 | OV <sub>DD</sub> | 10, 25         |  |  |

|                                  | Debug Signals <sup>5</sup> | I                 |                  |                |  |  |

| TRIG_IN                          | J14                        | I                 | OV <sub>DD</sub> |                |  |  |

| TRIG_OUT/READY                   | J13                        | 0                 | OV <sub>DD</sub> | 10, 25         |  |  |

| D1_MSRCID[0:1]/<br>LB_SRCID[0:1] | F15, K15                   | 0                 | OV <sub>DD</sub> | 6, 10          |  |  |

| D1_MSRCID[2]/<br>LB_SRCID[2]     | K14                        | 0                 | OV <sub>DD</sub> | 10, 25         |  |  |

| D1_MSRCID[3:4]/<br>LB_SRCID[3:4] | H15, G15                   | 0                 | OV <sub>DD</sub> | 10             |  |  |

| D2_MSRCID[0:4]                   | E16, C17, F16, H16, K16    | 0                 | OV <sub>DD</sub> | _              |  |  |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>                                   | Package Pin Number                                                                                                                                           | Pin Type                                                   | Power Supply     | Notes |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|-------|--|

| AGND_SRDS1                                          | P30                                                                                                                                                          | SerDes Port 1<br>Ground pin for<br>AV <sub>DD</sub> _SRDS1 |                  | _     |  |

| AGND_SRDS2                                          | AF30                                                                                                                                                         | SerDes Port 2<br>Ground pin for<br>AV <sub>DD</sub> _SRDS2 | —                | _     |  |

| SGND                                                | H28, H32, J30, K31, L28, L29, M32, N30,<br>R29, T32, U30, V31, W29,Y32 AA30, AB31,<br>AC29, AD32, AE30, AG29, AH32, AJ30,<br>AK31, AL29, AM32                | Ground pins for<br>SV <sub>DD</sub>                        | _                | _     |  |

| XGND                                                | XGND K27, L25, M26, N24, P27, R25, T26, U24, Groun<br>V27, W25, Y28, AA24, AB27, AC25, AD28, XV <sub>DD</sub><br>AE26, AF27, AH28, AJ26, AK27, AL26,<br>AM28 |                                                            | _                | _     |  |

|                                                     | Reset Configuration Si                                                                                                                                       | gnals <sup>20</sup>                                        |                  |       |  |

| TSEC1_TXD[0] /<br>cfg_alt_boot_vec                  | AF25                                                                                                                                                         | _                                                          | LV <sub>DD</sub> | _     |  |

| TSEC1_TXD[1]/<br>cfg_platform_freq                  | AC23                                                                                                                                                         | —                                                          | LV <sub>DD</sub> | 21    |  |

| TSEC1_TXD[2:4]/<br>cfg_device_id[5:7]               | AG24, AG23, AE24                                                                                                                                             | —                                                          | LV <sub>DD</sub> | _     |  |

| TSEC1_TXD[5]/<br>cfg_tsec1_reduce                   | AE23                                                                                                                                                         | —                                                          | LV <sub>DD</sub> | _     |  |

| TSEC1_TXD[6:7]/<br>cfg_tsec1_prtcl[0:1]             | AE22, AD22                                                                                                                                                   | —                                                          | LV <sub>DD</sub> | _     |  |

| TSEC2_TXD[0:3]/<br>cfg_rom_loc[0:3]                 | AB20, AJ23, AJ22, AD19                                                                                                                                       | —                                                          | LV <sub>DD</sub> | _     |  |

| TSEC2_TXD[4],<br>TSEC2_TX_ER/<br>cfg_dram_type[0:1] | AH23,<br>AB19                                                                                                                                                | _                                                          | LV <sub>DD</sub> | 38    |  |

| TSEC2_TXD[5]/<br>cfg_tsec2_reduce                   | AH21                                                                                                                                                         | _                                                          | LV <sub>DD</sub> | _     |  |

| TSEC2_TXD[6:7]/<br>cfg_tsec2_prtcl[0:1]             | AG22, AG21                                                                                                                                                   |                                                            | LV <sub>DD</sub> |       |  |

| TSEC3_TXD[0:1]/<br>cfg_spare[0:1]                   | AL21, AJ21                                                                                                                                                   | 0                                                          | TV <sub>DD</sub> | 33    |  |

| TSEC3_TXD[2]/<br>cfg_core1_enable                   | AM20                                                                                                                                                         | 0                                                          | TV <sub>DD</sub> | _     |  |

| TSEC3_TXD[3]/<br>cfg_core1_Im_offset                | AJ20                                                                                                                                                         | —                                                          | LV <sub>DD</sub> | _     |  |

| TSEC3_TXD[5]/<br>cfg_tsec3_reduce                   | AK21                                                                                                                                                         | _                                                          | LV <sub>DD</sub> |       |  |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

example, assuming a T<sub>i</sub> of 30°C, a T<sub>r</sub> of 5°C, a package  $R_{\theta JC} = 0.1$ , and a typical power consumption (P<sub>d</sub>) of 43.4 W, the following expression for T<sub>i</sub> is obtained:

Die-junction temperature:  $T_i = 30^{\circ}C + 5^{\circ}C + (0.1^{\circ}C/W + 0.2^{\circ}C/W + \theta_{sa}) \times 43.4 W$

For this example, a  $R_{\theta sa}$  value of 1.32 °C/W or less is required to maintain the die junction temperature below the maximum value of Table 2.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature—airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, and so on.

Due to the complexity and variety of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board as well as system-level designs.

For system thermal modeling, the MPC8641 thermal model is shown in Figure 62. Four cuboids are used to represent this device. The die is modeled as 12.4x15.3 mm at a thickness of 0.86 mm. See Section 3, "Power Characteristics" for power dissipation details. The substrate is modeled as a single block 33x33x1.2 mm with orthotropic conductivity:  $13.5 \text{ W/(m} \cdot \text{K})$  in the xy-plane and  $5.3 \text{ W/(m} \cdot \text{K})$  in the z-direction. The die is centered on the substrate. The bump/underfill layer is modeled as a collapsed thermal resistance between the die and substrate with a conductivity of  $5.3 \text{ W/(m} \cdot \text{K})$  in the thickness dimension of 0.07 mm. Because the bump/underfill is modeled with zero physical dimension (collapsed height), the die thickness was slightly enlarged to provide the correct height. The C5 solder layer is modeled as a cuboid with dimensions 33x33x0.4 mm and orthotropic thermal conductivity of  $0.034 \text{ W/(m} \cdot \text{K})$  in the xy-plane and  $9.6 \text{ W/(m} \cdot \text{K})$  in the z-direction. An LGA solder layer would be modeled as a collapsed thermal resistance with thermal conductivity of  $9.6 \text{W/(m} \cdot \text{K})$  and an effective height of 0.1 mm. The thermal model uses approximate dimensions to reduce grid. Please refer to the case outline for actual dimensions.

Top View of Model (Not to Scale)

Figure 62. Recommended Thermal Model of MPC8641

### 19.2.4 Temperature Diode

The MPC8641 has a temperature diode on the microprocessor that can be used in conjunction with other system temperature monitoring devices (such as Analog Devices, ADT7461<sup>TM</sup>). These devices use the negative temperature coefficient of a diode operated at a constant current to determine the temperature of the microprocessor and its environment. It is recommended that each device be individually calibrated.

The following are the specifications of the MPC8641 on-board temperature diode:

$V_{f} > 0.40 V$

$V_{f} < 0.90 V$

An approximate value of the ideality may be obtained by calibrating the device near the expected operating temperature.

Ideality factor is defined as the deviation from the ideal diode equation:

$$\mathbf{I}_{\text{fw}} = \mathbf{I}_{s} \left[ \mathbf{e}^{\frac{\mathbf{q}\mathbf{V}_{f}}{\mathbf{n}\mathbf{K}\mathbf{T}}} - \mathbf{1} \right]$$

For other pin pull-up or pull-down recommendations of signals, please see Section 17, "Signal Listings."

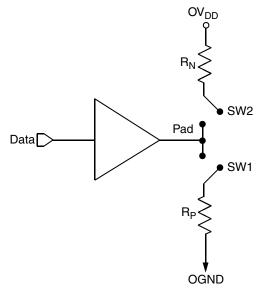

### 20.7 Output Buffer DC Impedance

The MPC8641 drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 66). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_p$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_p + R_N)/2$ .

Figure 66. Driver Impedance Measurement

Table 73 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | DUART, Control,<br>Configuration, Power<br>Management | PCI<br>Express | DDR DRAM  | Symbol         | Unit |

|----------------|-------------------------------------------------------|----------------|-----------|----------------|------|

| R <sub>N</sub> | 43 Target                                             | 25 Target      | 20 Target | Z <sub>0</sub> | W    |

| R <sub>P</sub> | 43 Target                                             | 25 Target      | 20 Target | Z <sub>0</sub> | W    |

**Table 73. Impedance Characteristics**

Note: Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

System Design Information

# 20.8 Configuration Pin Muxing

The MPC8641 provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 k $\Omega$ . This value should permit the 4.7-k $\Omega$  resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio and e600 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 20.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 68. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE 1149.1 specification, but is provided on all processors that implement the Power Architecture technology. The device requires TRST to be asserted during reset conditions to ensure the JTAG boundary logic does not interfere with normal chip operation. While it is possible to force the TAP controller to the reset state using only the TCK and TMS signals, more reliable power-on reset performance will be obtained if the TRST signal is asserted during power-on reset. Because the JTAG interface is also used for accessing the common on-chip processor (COP) function, simply tying TRST to HRESET is not practical.

The COP function of these processors allows a remote computer system (typically a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP port connects primarily through the JTAG interface of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 67 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

Ordering Information

# 21 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 21.1, "Part Numbers Fully Addressed by This Document."

# 21.1 Part Numbers Fully Addressed by This Document

Table 74 provides the Freescale part numbering nomenclature for the MPC8641. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MC              | nnnn               | x                                             | xx                                                                                                                                | nnnn                                              | x                                                                                    | x                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|--------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Core<br>Count                                 | Package <sup>1</sup>                                                                                                              | Core Processor<br>Frequency <sup>2</sup><br>(MHz) | DDR speed<br>(MHz)                                                                   | Product Revision Level                                                                                                                                                                                                                                                                                                                                                     |

| МС              | 8641               | Blank =<br>Single<br>Core<br>D = Dual<br>Core | HX = High-lead<br>HCTE FC-CBGA<br>VU = RoHS lead-free<br>HCTE FC-CBGA <sup>5</sup><br>VJ = lead-free HCTE<br>FC-CBGA <sup>6</sup> | 1000, 1250, 1333,<br>1500                         | N = 500 MHz <sup>4</sup><br>K = 600 MHz<br>J = 533 MHz<br>H = 500 MHz<br>G = 400 MHz | Revision B = 2.0<br>System Version Register<br>Value for Rev B:<br>$0x8090_0020 - MPC8641$<br>$0x8090_0120 - MPC8641D$<br>Revision C = 2.1<br>System Version Register<br>Value for Rev C:<br>$0x8090_0021 - MPC8641$<br>$0x8090_0121 - MPC8641D$<br>Revision E = 3.0<br>System Version Register<br>Value for Rev E:<br>$0x8090_0030 - MPC8641$<br>$0x8090_0130 - MPC8641D$ |

### Table 74. Part Numbering Nomenclature

### Notes:

- 1. See Section 16, "Package," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 3. The P prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

- 4. Part Number MC8641xxx1000NX is our low  $V_{DD}$ \_Core*n* device.  $V_{DD}$ \_Core*n* = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V.

- 5. VU part number is RoHS compliant with the permitted exception of the C4 die bumps.

- 6. VJ part number is entirely lead-free including the C4 die bumps.