#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| 2 0 1 1 1 0                     |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e600                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.25GHz                                                                 |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 1023-BBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dhx1250he |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

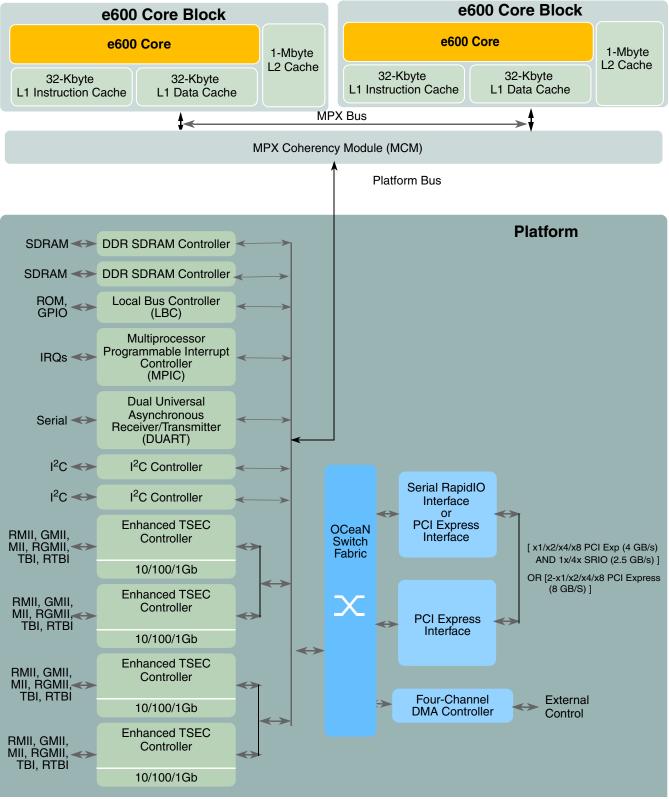

Overview

Figure 1. MPC8641 and MPC8641D

Overview

- DDR memory controllers

- Dual 64-bit memory controllers (72-bit with ECC)

- Support of up to a 300-MHz clock rate and a 600-MHz DDR2 SDRAM

- Support for DDR, DDR2 SDRAM

- Up to 16 Gbytes per memory controller

- Cache line and page interleaving between memory controllers.

- Serial RapidIO interface unit

- Supports *RapidIO Interconnect Specification*, Revision 1.2

- Both 1x and 4x LP-Serial link interfaces

- Transmission rates of 1.25-, 2.5-, and 3.125-Gbaud (data rates of 1.0-, 2.0-, and 2.5-Gbps) per lane

- RapidIO-compliant message unit

- RapidIO atomic transactions to the memory controller

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x1, x2, x4, and x8 link widths

- 2.5 Gbaud, 2.0 Gbps lane

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four IEEE 802.3, 802.3u, 802.3x, 802.3z, 802.3ac, 802.3ab-compatible controllers

- Support of the following physical interfaces: MII, RMII, GMII, RGMII, TBI, and RTBI

- Support a full-duplex FIFO mode for high-efficiency ASIC connectivity

- TCP/IP off-load

- Header parsing

- Quality of service support

- VLAN insertion and deletion

- MAC address recognition

- Buffer descriptors are backward compatible with PowerQUICC II and PowerQUICC III programming models

- RMON statistics support

- MII management interface for control and status

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts and 48 internal interrupts

- Eight global high resolution timers/counters that can generate interrupts

- Allows processors to interrupt each other with 32b messages

Electrical Characteristics

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8641. The MPC8641 is currently targeted to these specifications.

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Characteristic                                                                                                                                                         | Symbol                                              | Absolute Maximum<br>Value | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|------|-------|

| Cores supply voltages                                                                                                                                                  | V <sub>DD</sub> _Core0,<br>V <sub>DD</sub> _Core1   | -0.3 to 1.21 V            | V    | 2     |

| Cores PLL supply                                                                                                                                                       | AV <sub>DD</sub> _Core0,<br>AV <sub>DD</sub> _Core1 | -0.3 to 1.21 V            | V    | —     |

| SerDes Transceiver Supply (Ports 1 and 2)                                                                                                                              | SV <sub>DD</sub>                                    | -0.3 to 1.21 V            | V    | —     |

| SerDes Serial I/O Supply Port 1                                                                                                                                        | XV <sub>DD_</sub> SRDS1                             | -0.3 to 1.21V             | V    | —     |

| SerDes Serial I/O Supply Port 2                                                                                                                                        | XV <sub>DD_</sub> SRDS2                             | -0.3 to 1.21 V            | V    | —     |

| SerDes DLL and PLL supply voltage for Port 1 and Port 2                                                                                                                | AV <sub>DD</sub> _SRDS1,<br>AV <sub>DD</sub> _SRDS2 | -0.3 to 1.21V             | V    | —     |

| Platform Supply voltage                                                                                                                                                | V <sub>DD</sub> _PLAT                               | -0.3 to 1.21V             | V    | —     |

| Local Bus and Platform PLL supply voltage                                                                                                                              | AV <sub>DD</sub> _LB,<br>AV <sub>DD</sub> _PLAT     | -0.3 to 1.21V             | V    | —     |

| DDR and DDR2 SDRAM I/O supply voltages                                                                                                                                 | D1_GV <sub>DD,</sub>                                | -0.3 to 2.75 V            | V    | 3     |

|                                                                                                                                                                        | D2_GV <sub>DD</sub>                                 | –0.3 to 1.98 V            | V    | 3     |

| eTSEC 1 and 2 I/O supply voltage                                                                                                                                       | LV <sub>DD</sub>                                    | –0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                        |                                                     | -0.3 to 2.75 V            | V    | 4     |

| eTSEC 3 and 4 I/O supply voltage                                                                                                                                       | TV <sub>DD</sub>                                    | -0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                        |                                                     | -0.3 to 2.75 V            | V    | 4     |

| Local Bus, DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management, I <sup>2</sup> C, JTAG<br>and Miscellaneous I/O voltage | OV <sub>DD</sub>                                    | –0.3 to 3.63 V            | V    | —     |

| Characteristic               |                                                                                                                                                                              | Symbol                               | Absolute Maximum<br>Value                                          | Unit | Notes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|------|-------|

| Input voltage                | DDR and DDR2 SDRAM signals                                                                                                                                                   | D <i>n</i> _MV <sub>IN</sub>         | - 0.3 to (D <i>n</i> _GV <sub>DD</sub> + 0.3)                      | V    | 5     |

|                              | DDR and DDR2 SDRAM reference                                                                                                                                                 | D <i>n</i> _MV <sub>REF</sub>        | -0.3 to (D <i>n</i> _GV <sub>DD</sub> /2 + 0.3)                    | V    | —     |

| Three-speed Ethernet signals |                                                                                                                                                                              | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to (LV <sub>DD</sub> + 0.3)<br>GND to (TV <sub>DD</sub> + 0.3) | V    | 5     |

|                              | DUART, Local Bus, DMA,<br>Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test,<br>Power management, I <sup>2</sup> C, JTAG and<br>Miscellaneous I/O voltage | OV <sub>IN</sub>                     | GND to (OV <sub>DD</sub> + 0.3)                                    | V    | 5     |

| Storage temperature          | range                                                                                                                                                                        | T <sub>STG</sub>                     | -55 to 150                                                         | °C   | —     |

| Table 1. Absolute | Maximum | Ratings <sup>1</sup> | (continued) |

|-------------------|---------|----------------------|-------------|

|-------------------|---------|----------------------|-------------|

Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Core 1 characteristics apply only to MPC8641D. If two separate power supplies are used for V<sub>DD</sub>\_Core0 and V<sub>DD</sub>\_Core1, they must be kept within 100 mV of each other during normal run time.

- 3. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 4. The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 5. During run time (M,L,T,O)V<sub>IN</sub> and D*n*\_MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8641. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed. For details on order information and specific operating conditions for parts, see Section 21, "Ordering Information."

| Characteristic                            | Symbol                   | Recommended<br>Value | Unit | Notes    |

|-------------------------------------------|--------------------------|----------------------|------|----------|

| Cores supply voltages                     | V <sub>DD</sub> _Core0,  | 1.10 ± 50 mV         | V    | 1, 2, 8  |

|                                           | V <sub>DD</sub> _Core1   | 1.05 ± 50 mV         |      | 1, 2, 7  |

|                                           |                          | 0.95 ± 50 mV         |      | 1, 2, 12 |

| Cores PLL supply                          | AV <sub>DD</sub> _Core0, | 1.10 ± 50 mV         | V    | 8, 13    |

|                                           | AV <sub>DD</sub> _Core1  | 1.05 ± 50 mV         |      | 7, 13    |

|                                           |                          | 0.95 ± 50 mV         |      | 12, 13   |

| SerDes Transceiver Supply (Ports 1 and 2) | SV <sub>DD</sub>         | 1.10 ± 50 mV         | V    | 8, 11    |

|                                           |                          | 1.05 ± 50 mV         |      | 7, 11    |

### Table 2. Recommended Operating Conditions

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                                                                                                               | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                    | Notes   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------|---------|

| DDR1 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 2.5 V | 4, 9    |

| DDR2 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 1.8 V | 1, 5, 9 |

| Local Bus signals                                                                                                                         | 45<br>25                                | OV <sub>DD</sub> = 3.3 V             | 2, 6    |

| eTSEC/10/100 signals                                                                                                                      | 45                                      | T/LV <sub>DD</sub> = 3.3 V           | 6       |

|                                                                                                                                           | 30                                      | T/LV <sub>DD</sub> = 2.5 V           | 6       |

| DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management,<br>JTAG and Miscellaneous I/O voltage | 45                                      | OV <sub>DD</sub> = 3.3 V             | 6       |

| l <sup>2</sup> C                                                                                                                          | 150                                     | OV <sub>DD</sub> = 3.3 V             | 7       |

| SRIO, PCI Express                                                                                                                         | 100                                     | SV <sub>DD</sub> = 1.1/1.05 V        | 3, 8    |

### Table 3. Output Drive Capability

Notes:

- 1. See the DDR Control Driver registers in the MPC8641D reference manual for more information.

- 2. Only the following local bus signals have programmable drive strengths: LALE, LAD[0:31], LDP[0:3], LA[27:31], LCKE, LCS[1:2], LWE[0:3], LGPL1, LGPL2, LGPL3, LGPL4, LGPL5, LCLK[0:2]. The other local bus signals have a fixed drive strength of 45 Ω. See the POR Impedance Control register in the MPC8641D reference manual for more information about local bus signals and their drive strength programmability.

- 3. See Section 17, "Signal Listings," for details on resistor requirements for the calibration of SD*n*\_IMP\_CAL\_TX and SD*n*\_IMP\_CAL\_RX transmit and receive signals.

- 4. Stub Series Terminated Logic (SSTL-25) type pins.

- 5. Stub Series Terminated Logic (SSTL-18) type pins.

- 6. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 7. Open Drain type pins.

- 8. Low Voltage Differential Signaling (LVDS) type pins.

- 9. The drive strength of the DDR interface in half strength mode is at  $T_i = 105C$  and at  $Dn_GV_{DD}$  (min).

## 2.2 Power Up/Down Sequence

The MPC8641 requires its power rails to be applied in a specific sequence in order to ensure proper device operation.

### NOTE

The recommended maximum ramp up time for power supplies is 20 milliseconds.

The chronological order of power up is as follows:

1. All power rails other than DDR I/O ( $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$ ).

#### DDR and DDR2 SDRAM

Table 15 provides the recommended operating conditions for the DDR SDRAM component(s) when  $Dn_GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol               | Min                                               | Мах                                                                       | Unit | Notes |

|-------------------------------------------------|----------------------|---------------------------------------------------|---------------------------------------------------------------------------|------|-------|

| I/O supply voltage                              | Dn_GV <sub>DD</sub>  | 2.375                                             | 2.625                                                                     |      | 1     |

| I/O reference voltage                           | Dn_MV <sub>REF</sub> | $0.49 \times Dn_GV_{DD}$ $0.51 \times Dn_GV_{DD}$ |                                                                           | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>      | D <i>n</i> _MV <sub>REF</sub> – 0.04              | 0 <i>n_</i> MV <sub>REF</sub> - 0.04 D <i>n_</i> MV <sub>REF</sub> + 0.04 |      | 3     |

| Input high voltage                              | V <sub>IH</sub>      | D <i>n</i> _MV <sub>REF</sub> + 0.15              | D <i>n</i> _GV <sub>DD</sub> + 0.3                                        | V    |       |

| Input low voltage                               | V <sub>IL</sub>      | –0.3 D <i>n</i> _MV <sub>REF</sub> – 0.15         |                                                                           | V    | _     |

| Output leakage current                          | I <sub>OZ</sub>      | -50                                               | 50                                                                        | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>ОН</sub>      | -16.2                                             | _                                                                         | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>      | 16.2                                              | _                                                                         | mA   | _     |

#### Notes:

1.  $Dn_GV_{DD}$  is expected to be within 50 mV of the DRAM  $Dn_GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times Dn_{GV_{DD}}$ , and to track  $Dn_{GV_{DD}}$  DC variations as measured at the receiver. Peak-to-peak noise on  $Dn_{MV_{REF}}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to Dn\_MV<sub>REF</sub>. This rail should track variations in the DC level of Dn\_MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  Dn\_GV<sub>DD</sub>.

Table 16 provides the DDR capacitance when  $Dn \text{ } \text{GV}_{DD}$  (typ)=2.5 V.

### Table 16. DDR SDRAM Capacitance for Dn\_GV<sub>DD</sub> (typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $Dn_GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = Dn_GVDD/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

### Table 17 provides the current draw characteristics for $MV_{REF}$ .

#### Table 17. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1    |

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

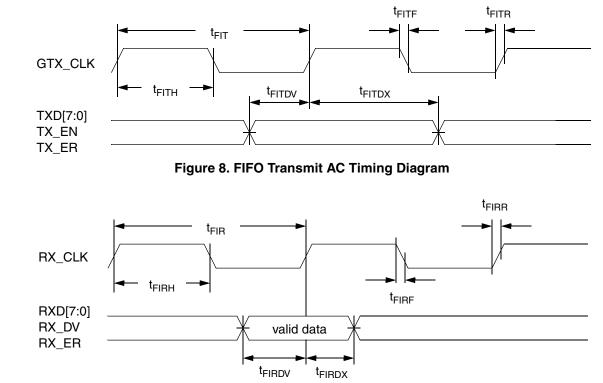

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

Timing diagrams for FIFO appear in Figure 8 and Figure 9.

Figure 9. FIFO Receive AC Timing Diagram

## 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

### 8.2.2.1 GMII Transmit AC Timing Specifications

Table 28 provides the GMII transmit AC timing specifications.

#### Table 28. GMII Transmit AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                               |                                | Min | Тур | Max | Unit |

|---------------------------------------------------|--------------------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>            | 2.5 | _   | _   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX            | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%-80%)            | t <sub>GTXR</sub> <sup>2</sup> | _   |     | 1.0 | ns   |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

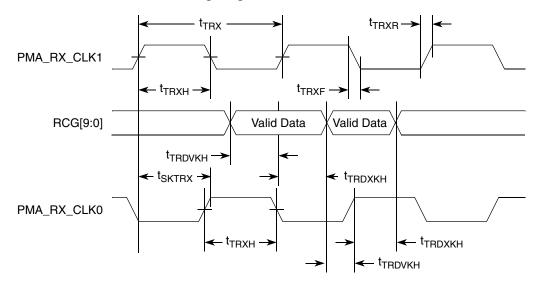

## 8.2.4.2 TBI Receive AC Timing Specifications

Table 33 provides the TBI receive AC timing specifications.

#### Table 33. TBI Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                       | Symbol <sup>1</sup>                 | Min | Тур  | Мах | Unit |

|-------------------------------------------|-------------------------------------|-----|------|-----|------|

| PMA_RX_CLK[0:1] clock period              | t <sub>TRX</sub> 3                  | —   | 16.0 | _   | ns   |

| PMA_RX_CLK[0:1] skew                      | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   |

| PMA_RX_CLK[0:1] duty cycle                | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    |

| RCG[9:0] setup time to rising PMA_RX_CLK  | t <sub>TRDVKH</sub>                 | 2.5 | —    | —   | ns   |

| RCG[9:0] hold time to rising PMA_RX_CLK   | t <sub>TRDXKH</sub>                 | 1.5 | —    | —   | ns   |

| PMA_RX_CLK[0:1] clock rise time (20%-80%) | t <sub>TRXR</sub> <sup>2</sup>      | 0.7 | —    | 2.4 | ns   |

| PMA_RX_CLK[0:1] clock fall time (80%-20%) | t <sub>TRXF</sub> <sup>2</sup>      | 0.7 | —    | 2.4 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub></sub>

2. Guaranteed by design.

3. ±100 ppm tolerance on PMA\_RX\_CLK[0:1] frequency

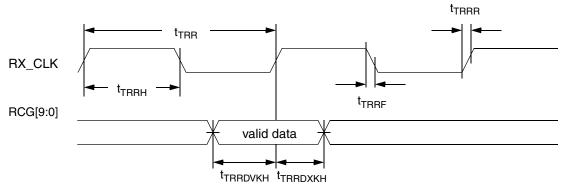

Figure 17 shows the TBI receive AC timing diagram.

Figure 17. TBI Receive AC Timing Diagram

## 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1 a 125-MHz TBI receive clock is supplied on TSEC $n_RX_CLK$  pin (no receive clock is used on TSEC $n_TX_CLK$  in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC GTX CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 34.

Table 34. TBI single-clock Mode Receive AC Timing Specification

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                       | Symbol                              | Min | Тур | Мах | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRR</sub> <sup>1</sup>       | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH/</sub> t <sub>TRR</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>                   | _   | —   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>                   |     | —   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>                   | _   | —   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDVKH</sub>                | 2.0 | —   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDXKH</sub>                | 1.0 |     |     | ns   |

<sup>1</sup> ±100 ppm tolerance on RX\_CLK frequency

A timing diagram for TBI receive appears in Figure 18.

Figure 18. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.2.6 RGMII and RTBI AC Timing Specifications

Table 35 presents the RGMII and RTBI AC timing specifications.

### Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $L/TV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>  | Min  | Тур | Мах | Unit |

|-----------------------------------------------------|----------------------|------|-----|-----|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub> 5 | -500 | 0   | 500 | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>   | 1.0  | _   | 2.8 | ns   |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

## 8.2.7.2 RMII Receive AC Timing Specifications

### Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition                                       | Symbol <sup>1</sup>                 | Min  | Тур  | Мах  | Unit |

|-----------------------------------------------------------|-------------------------------------|------|------|------|------|

| REF_CLK clock period                                      | t <sub>RMR</sub>                    | 15.0 | 20.0 | 25.0 | ns   |

| REF_CLK duty cycle                                        | t <sub>RMRH</sub> /t <sub>RMR</sub> | 35   | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                               | t <sub>RMRJ</sub>                   | _    | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                               | t <sub>RMRR</sub>                   | 1.0  | —    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                               | t <sub>RMRF</sub>                   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>                  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>                  | 2.0  | _    |      | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

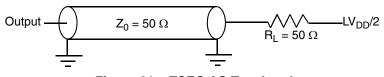

Figure 21 provides the AC test load for eTSEC.

Figure 21. eTSEC AC Test Load

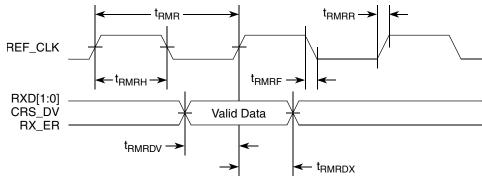

Figure 22 shows the RMII receive AC timing diagram.

Figure 22. RMII Receive AC Timing Diagram

# 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8641.

## **10.1 Local Bus DC Electrical Characteristics**

Table 40 provides the DC electrical characteristics for the local bus interface operating at  $OV_{DD} = 3.3 \text{ V}$  DC.

| Parameter                                                                      | Symbol          | Min                    | Мах                    | Unit |

|--------------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                                       | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = OV_{DD})$                | I <sub>IN</sub> | _                      | ±5                     | μΑ   |

| High-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OH</sub> = −2 mA) | V <sub>OH</sub> | OV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub> |                        | 0.2                    | V    |

Table 40. Local Bus DC Electrical Characteristics (3.3 V DC)

#### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

## **10.2 Local Bus AC Electrical Specifications**

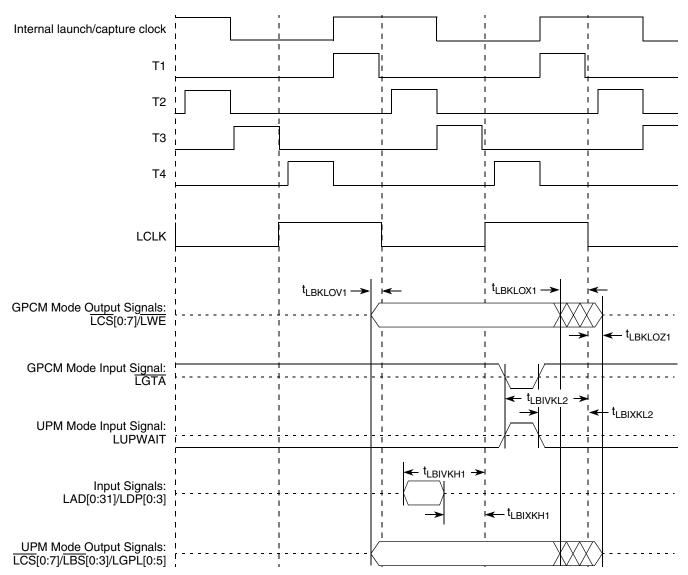

Table 41 describes the timing parameters of the local bus interface at  $OV_{DD} = 3.3$  V with PLL enabled. For information about the frequency range of local bus see Section 18.1, "Clock Ranges."

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | —   | ns   | 2     |

| Local Bus Duty Cycle                                                  | t <sub>LBKH</sub> /t <sub>LBK</sub> | 45  | 55  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                  | t <sub>LBIVKH1</sub>                | 1.8 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.7 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.0 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.0 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | _   | 2.0 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                |     | 2.2 | ns   | —     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | _   | 2.3 | ns   | —     |

Table 41. Local Bus Timing Parameters (OV<sub>DD</sub> = 3.3 V)m - PLL Enabled

Figure 31. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 or 8 (clock ratio of 8 or 16) (PLL Bypass Mode)

### Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

At recommended operating conditions (see Table 3).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|---------|------|-------|

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 30<br>30 |         | ns   | 5, 6  |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9 | ns   | 5, 6  |

Notes:

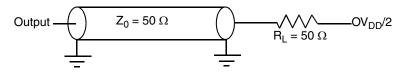

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 32). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to  $t_{TCLK}$ .

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 32 provides the AC test load for TDO and the boundary-scan outputs.

Figure 32. AC Test Load for the JTAG Interface

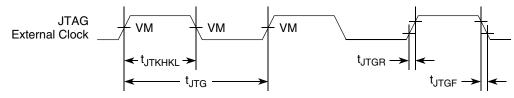

Figure 33 provides the JTAG clock input timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 33. JTAG Clock Input Timing Diagram

### Table 45. I<sup>2</sup>C DC Electrical Characteristics (continued)

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                    | Symbol | Min | Мах | Unit | Notes |

|------------------------------|--------|-----|-----|------|-------|

| Capacitance for each I/O pin | CI     | _   | 10  | pF   | —     |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8641 Integrated Host Processor Reference Manual for information on the digital filter used.

3. I/O pins will obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# 12.2 I<sup>2</sup>C AC Electrical Specifications

Table 46 provides the AC timing parameters for the  $I^2C$  interfaces.

### Table 46. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 45).

| Parameter                                                                                    | Symbol <sup>1</sup>   | Min                                  | Мах              | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>      | 0                                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub> 4   | 1.3                                  | _                | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub> 4   | 0.6                                  | _                | μs   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> 4 | 0.6                                  | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> 4 | 0.6                                  | _                | μS   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> 4 | 100                                  | _                | ns   |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>i2DXKL</sub>   | 0 <sup>2</sup>                       |                  | μs   |

| Rise time of both SDA and SCL signals                                                        | t <sub>I2CR</sub>     | 20 + 0.1 C <sub>B</sub> <sup>5</sup> | 300              | ns   |

| Fall time of both SDA and SCL signals                                                        | t <sub>I2CF</sub>     | 20 + 0.1 C <sub>b</sub> <sup>5</sup> | 300              | ns   |

| Data output delay time                                                                       | t <sub>I2OVKL</sub>   | —                                    | 0.9 <sup>3</sup> | μs   |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub>   | 0.6                                  | _                | μs   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>   | 1.3                                  | —                | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>       | $0.1 \times OV_{DD}$                 | _                | V    |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

I<sup>2</sup>C

High-Speed Serial Interfaces (HSSI)

## **13.2.3** Interfacing With Other Differential Signaling Levels

With on-chip termination to SGND, the differential reference clocks inputs are HCSL (High-Speed Current Steering Logic) compatible DC-coupled.

Many other low voltage differential type outputs like LVDS (Low Voltage Differential Signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

### NOTE

Figure 43 to Figure 46 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8641D SerDes reference clock receiver requirement provided in this document.

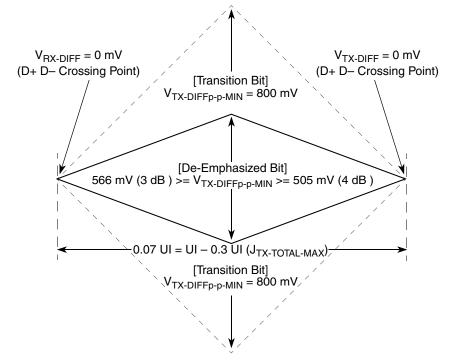

### 14.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 50 is specified using the passive compliance/test measurement load (see Figure 52) in place of any real PCI Express interconnect + RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams will differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit will always be relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (that is, least squares and median deviation fits).

Figure 50. Minimum Transmitter Timing and Voltage Output Compliance Specifications

### Table 54. Short Run Transmitter AC Timing Specifications—3.125 GBaud (continued)

| Characteristic       | Symbol          | Range |      | Unit | Notes                                                                  |

|----------------------|-----------------|-------|------|------|------------------------------------------------------------------------|

|                      | Symbol          | Min   | Max  | Onne | Notes                                                                  |

| Multiple output skew | S <sub>MO</sub> | _     | 1000 | ps   | Skew at the transmitter output<br>between lanes of a multilane<br>link |

| Unit Interval        | UI              | 320   | 320  | ps   | +/– 100 ppm                                                            |

### Table 55. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Unaracteristic              | Symbol              | Min   | Мах  | Onic   | Notes                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | _                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | _                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/– 100 ppm                                                                      |

#### Table 56. Long Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | R     | ange | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Glaracteristic              | Symbol              | Min   | Max  |        | Notes                                                                            |

| Output Voltage,             | V <sub>O</sub>      | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | -     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/– 100 ppm                                                                      |

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                              |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------------|--|

| Characteristic                                     |                 | Min   | Мах               | Onit   | Notes                                                              |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200   | 1600              | mV p-p | Measured at receiver                                               |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37  | _                 | UI p-p | Measured at receiver                                               |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55  | _                 | UI p-p | Measured at receiver                                               |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | —                 | UI p-p | Measured at receiver                                               |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |

| Bit Error Rate                                     | BER             | —     | 10 <sup>-12</sup> | _      | _                                                                  |  |

| Unit Interval                                      | UI              | 400   | 400               | ps     | +/- 100 ppm                                                        |  |

| Table 60. Receive | r AC Timing | Specifications- | –2.5 GBaud |

|-------------------|-------------|-----------------|------------|

|-------------------|-------------|-----------------|------------|

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Table 61. Receiver AC Timing Speci | ifications—3.125 GBaud |

|------------------------------------|------------------------|

|------------------------------------|------------------------|

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                              |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------------|--|

|                                                    |                 | Min   | Max               | Onit   |                                                                    |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200   | 1600              | mV p-p | Measured at receiver                                               |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                               |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55  | _                 | UI p-p | Measured at receiver                                               |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | —                 | UI p-p | Measured at receiver                                               |  |

| Multiple Input Skew                                | S <sub>MI</sub> | —     | 22                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |

| Bit Error Rate                                     | BER             | —     | 10 <sup>-12</sup> | _      | —                                                                  |  |

| Unit Interval                                      | UI              | 320   | 320               | ps     | +/– 100 ppm                                                        |  |

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Serial RapidIO

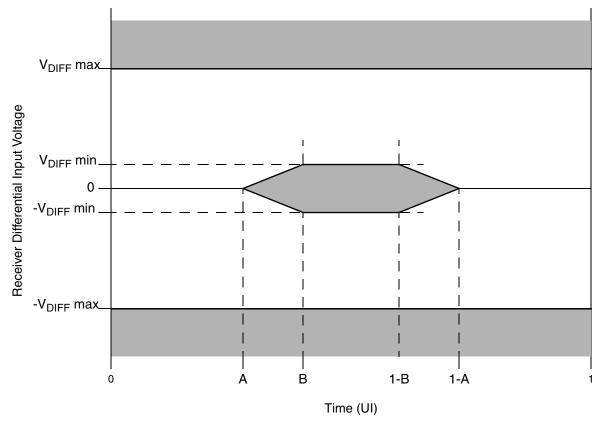

Figure 56. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |

|---------------|----------------------------|----------------------------|--------|--------|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |

Table 62. Receiver Input Compliance Mask Parameters Exclusive of Sinusoidal Jitter

## **15.9 Measurement and Test Requirements**

Since the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. In addition, the CJPAT test pattern defined in Annex 48A of IEEE 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

## 15.9.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (Baud Frequency)/1667 is applied to the jitter. The data pattern for template measurements is the

| Name <sup>1</sup>    | Package Pin Number                                                                                                                                                                                                                                                                                              | Pin Type                           | Power Supply           | Notes  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------|--------|

| D2_MDQ[0:63]         | A7, B7, C5, D5, C8, D8, D6, A5, C4, A3, D3,<br>D2, A4, B4, C2, C1, E3, E1, H4, G1, D1, E4,<br>G3, G2, J4, J2, L1, L3, H3, H1, K1, L4, AA4,<br>AA2, AD1, AD2, Y1, AA1, AC1, AC3, AD5,<br>AE1, AG1, AG2, AC4, AD4, AF3, AF4, AH3,<br>AJ1, AM1, AM3, AH1, AH2, AL2, AL3, AK5,<br>AL5, AK7, AM7, AK4, AM4, AM6, AJ7 | I/O                                | D2_GV <sub>DD</sub>    | _      |

| D2_MECC[0:7]         | H6, J5, M5, M4, G6, H7, M2, M1                                                                                                                                                                                                                                                                                  | I/O                                | D2_GV <sub>DD</sub>    | —      |

| D2_MDM[0:8]          | C7, B3, F4, J1, AB1, AE2, AK1, AM5, K6                                                                                                                                                                                                                                                                          | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MDQS[0:8]         | B6, B1, F1, K2, AB3, AF1, AL1, AL6, L6                                                                                                                                                                                                                                                                          | I/O                                | D2_GV <sub>DD</sub>    | —      |

| D2_MDQS[0:8]         | A6, A2, F2, K3, AB2, AE3, AK2, AJ6, K5                                                                                                                                                                                                                                                                          | I/O                                | D2_GV <sub>DD</sub>    | —      |

| D2_MBA[0:2]          | W5, V5, P3                                                                                                                                                                                                                                                                                                      | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MA[0:15]          | W1, U4, U3, T1, T2, T3, T5, R2, R1, R5, V4,<br>R4, P1, AH5, P4, N1                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MWE               | Y4                                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MRAS              | W3                                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCAS              | AB5                                                                                                                                                                                                                                                                                                             | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCS[0:3]          | Y3, AF6, AA5, AF7                                                                                                                                                                                                                                                                                               | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCKE[0:3]         | N6, N5, N2, N3                                                                                                                                                                                                                                                                                                  | 0                                  | D2_GV <sub>DD</sub>    | 23     |

| D2_MCK[0:5]          | U1, F5, AJ3, V2, E7, AG4                                                                                                                                                                                                                                                                                        | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCK[0:5]          | V1, G5, AJ4, W2, E6, AG5                                                                                                                                                                                                                                                                                        | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MODT[0:3]         | AE6, AG7, AE5, AH6                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MDIC[0:1]         | F8, F7                                                                                                                                                                                                                                                                                                          | 10                                 | D2_GV <sub>DD</sub>    | 27     |

| D2_MV <sub>REF</sub> | A18                                                                                                                                                                                                                                                                                                             | DDR Port 2<br>reference<br>voltage | D2_GV <sub>DD</sub> /2 | 3      |

|                      | High Speed I/O Interface 1 (                                                                                                                                                                                                                                                                                    | SERDES 1) <sup>4</sup>             |                        |        |

| SD1_TX[0:7]          | L26, M24, N26, P24, R26, T24, U26, V24                                                                                                                                                                                                                                                                          | 0                                  | SV <sub>DD</sub>       | —      |

| SD1_TX[0:7]          | L27, M25, N27, P25, R27, T25, U27, V25                                                                                                                                                                                                                                                                          | 0                                  | SV <sub>DD</sub>       | —      |

| SD1_RX[0:7]          | J32, K30, L32, M30, T30, U32, V30, W32                                                                                                                                                                                                                                                                          | Ι                                  | SV <sub>DD</sub>       | —      |

| SD1_RX[0:7]          | J31, K29, L31, M29, T29, U31, V29, W31                                                                                                                                                                                                                                                                          | I                                  | SV <sub>DD</sub>       | _      |

| SD1_REF_CLK          | N32                                                                                                                                                                                                                                                                                                             | I                                  | SV <sub>DD</sub>       | _      |

| SD1_REF_CLK          | N31                                                                                                                                                                                                                                                                                                             | Ι                                  | SV <sub>DD</sub>       | —      |

| SD1_IMP_CAL_TX       | Y26                                                                                                                                                                                                                                                                                                             | Analog                             | SV <sub>DD</sub>       | 19     |

| SD1_IMP_CAL_RX       | J28                                                                                                                                                                                                                                                                                                             | Analog                             | SV <sub>DD</sub>       | 30     |

| SD1_PLL_TPD          | U28                                                                                                                                                                                                                                                                                                             | 0                                  | SV <sub>DD</sub>       | 13, 17 |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)