#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e600                                                            |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 1023-BBGA, FCBGA                                                        |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dhx1333jb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.1 Key Features

The following lists an overview of the MPC8641 key feature set:

- Major features of the e600 core are as follows:

- High-performance, 32-bit superscalar microprocessor that implements the PowerPC ISA

- Eleven independent execution units and three register files

- Branch processing unit (BPU)

- Four integer units (IUs) that share 32 GPRs for integer operands

- 64-bit floating-point unit (FPU)

- Four vector units and a 32-entry vector register file (VRs)

- Three-stage load/store unit (LSU)

- Three issue queues, FIQ, VIQ, and GIQ, can accept as many as one, two, and three instructions, respectively, in a cycle.

- Rename buffers

- Dispatch unit

- Completion unit

- Two separate 32-Kbyte instruction and data level 1 (L1) caches

- Integrated 1-Mbyte, eight-way set-associative unified instruction and data level 2 (L2) cache with ECC

- 36-bit real addressing

- Separate memory management units (MMUs) for instructions and data

- Multiprocessing support features

- Power and thermal management

- Performance monitor

- In-system testability and debugging features

- Reliability and serviceability

- MPX coherency module (MCM)

- Ten local address windows plus two default windows

- Optional low memory offset mode for core 1 to allow for address disambiguation

- Address translation and mapping units (ATMUs)

- Eight local access windows define mapping within local 36-bit address space

- Inbound and outbound ATMUs map to larger external address spaces

- Three inbound windows plus a configuration window on PCI Express

- Four inbound windows plus a default window on serial RapidIO

- Four outbound windows plus default translation for PCI Express

- Eight outbound windows plus default translation for serial RapidIO with segmentation and sub-segmentation support

Electrical Characteristics

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8641. The MPC8641 is currently targeted to these specifications.

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Characteristic                                                                                                                                                         | Symbol                                              | Absolute Maximum<br>Value | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|------|-------|

| Cores supply voltages                                                                                                                                                  | V <sub>DD</sub> _Core0,<br>V <sub>DD</sub> _Core1   | -0.3 to 1.21 V            | V    | 2     |

| Cores PLL supply                                                                                                                                                       | AV <sub>DD</sub> _Core0,<br>AV <sub>DD</sub> _Core1 | -0.3 to 1.21 V            | V    | —     |

| SerDes Transceiver Supply (Ports 1 and 2)                                                                                                                              | SV <sub>DD</sub>                                    | -0.3 to 1.21 V            | V    | —     |

| SerDes Serial I/O Supply Port 1                                                                                                                                        | XV <sub>DD_</sub> SRDS1                             | -0.3 to 1.21V             | V    | —     |

| SerDes Serial I/O Supply Port 2                                                                                                                                        | XV <sub>DD_</sub> SRDS2                             | -0.3 to 1.21 V            | V    | —     |

| SerDes DLL and PLL supply voltage for Port 1 and Port 2                                                                                                                | AV <sub>DD</sub> _SRDS1,<br>AV <sub>DD</sub> _SRDS2 | -0.3 to 1.21V             | V    | —     |

| Platform Supply voltage                                                                                                                                                | V <sub>DD</sub> _PLAT                               | -0.3 to 1.21V             | V    | —     |

| Local Bus and Platform PLL supply voltage                                                                                                                              | AV <sub>DD</sub> _LB,<br>AV <sub>DD</sub> _PLAT     | -0.3 to 1.21V             | V    | —     |

| DDR and DDR2 SDRAM I/O supply voltages                                                                                                                                 | D1_GV <sub>DD,</sub><br>D2_GV <sub>DD</sub>         | -0.3 to 2.75 V            | V    | 3     |

|                                                                                                                                                                        |                                                     | –0.3 to 1.98 V            | V    | 3     |

| eTSEC 1 and 2 I/O supply voltage                                                                                                                                       | LV <sub>DD</sub>                                    | –0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                        |                                                     | -0.3 to 2.75 V            | V    | 4     |

| eTSEC 3 and 4 I/O supply voltage                                                                                                                                       | TV <sub>DD</sub>                                    | -0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                        |                                                     | -0.3 to 2.75 V            | V    | 4     |

| Local Bus, DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management, I <sup>2</sup> C, JTAG<br>and Miscellaneous I/O voltage | OV <sub>DD</sub>                                    | –0.3 to 3.63 V            | V    | —     |

### 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                                                                                                               | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                    | Notes   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------|---------|

| DDR1 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 2.5 V | 4, 9    |

| DDR2 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 1.8 V | 1, 5, 9 |

| Local Bus signals                                                                                                                         | 45<br>25                                | OV <sub>DD</sub> = 3.3 V             | 2, 6    |

| eTSEC/10/100 signals                                                                                                                      | 45                                      | T/LV <sub>DD</sub> = 3.3 V           | 6       |

|                                                                                                                                           | 30                                      | T/LV <sub>DD</sub> = 2.5 V           | 6       |

| DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management,<br>JTAG and Miscellaneous I/O voltage | 45                                      | OV <sub>DD</sub> = 3.3 V             | 6       |

| l <sup>2</sup> C                                                                                                                          | 150                                     | OV <sub>DD</sub> = 3.3 V             | 7       |

| SRIO, PCI Express                                                                                                                         | 100                                     | SV <sub>DD</sub> = 1.1/1.05 V        | 3, 8    |

### Table 3. Output Drive Capability

Notes:

- 1. See the DDR Control Driver registers in the MPC8641D reference manual for more information.

- 2. Only the following local bus signals have programmable drive strengths: LALE, LAD[0:31], LDP[0:3], LA[27:31], LCKE, LCS[1:2], LWE[0:3], LGPL1, LGPL2, LGPL3, LGPL4, LGPL5, LCLK[0:2]. The other local bus signals have a fixed drive strength of 45 Ω. See the POR Impedance Control register in the MPC8641D reference manual for more information about local bus signals and their drive strength programmability.

- 3. See Section 17, "Signal Listings," for details on resistor requirements for the calibration of SD*n*\_IMP\_CAL\_TX and SD*n*\_IMP\_CAL\_RX transmit and receive signals.

- 4. Stub Series Terminated Logic (SSTL-25) type pins.

- 5. Stub Series Terminated Logic (SSTL-18) type pins.

- 6. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 7. Open Drain type pins.

- 8. Low Voltage Differential Signaling (LVDS) type pins.

- 9. The drive strength of the DDR interface in half strength mode is at  $T_i = 105C$  and at  $Dn_GV_{DD}$  (min).

### 2.2 Power Up/Down Sequence

The MPC8641 requires its power rails to be applied in a specific sequence in order to ensure proper device operation.

### NOTE

The recommended maximum ramp up time for power supplies is 20 milliseconds.

The chronological order of power up is as follows:

1. All power rails other than DDR I/O ( $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$ ).

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

This section provides the AC and DC electrical characteristics for enhanced three-speed and MII management.

## 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII and TBI interfaces can be operated at 3.3 or 2.5 V. Whether the GMII or TBI interface is operated at 3.3 or 2.5 V, the timing is compatible with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998). The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 eTSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, RMII and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 24 and Table 25. The potential applied to the input of a GMII, MII, TBI, RGMII, RMII or RTBI receiver may exceed the potential of the receiver's power supply (that is, a GMII driver powered from a 3.6-V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5-V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                                                    | Symbol                               | Min   | Мах   | Unit | Notes  |

|----------------------------------------------------------------------------------------------|--------------------------------------|-------|-------|------|--------|

| Supply voltage 3.3 V                                                                         | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.135 | 3.465 | V    | 1, 2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OH</sub> = -4.0 mA) | V <sub>OH</sub>                      | 2.40  | _     | V    |        |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 4.0 \text{ mA})$                        | V <sub>OL</sub>                      | —     | 0.50  | V    | —      |

| Input high voltage                                                                           | V <sub>IH</sub>                      | 2.0   | —     | V    | —      |

| Input low voltage                                                                            | V <sub>IL</sub>                      | —     | 0.90  | V    | —      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$                                    | Ι <sub>ΙΗ</sub>                      | _     | 40    | μΑ   | 1, 2,3 |

Table 24. GMII, MII, RMII, TBI and FIFO DC Electrical Characteristics

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

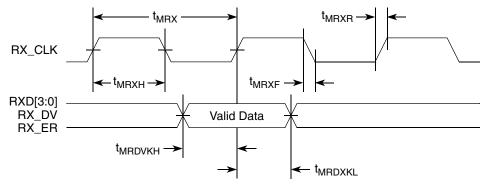

### 8.2.3.2 MII Receive AC Timing Specifications

Table 31 provides the MII receive AC timing specifications.

### Table 31. MII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2,3                | —    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub> <sup>3</sup>       | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  |     | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

3. ±100 ppm tolerance on RX\_CLK frequency

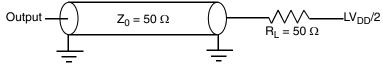

Figure 14 provides the AC test load for eTSEC.

Figure 14. eTSEC AC Test Load

Figure 15 shows the MII receive AC timing diagram.

Figure 15. MII Receive AC Timing Diagram

Local Bus

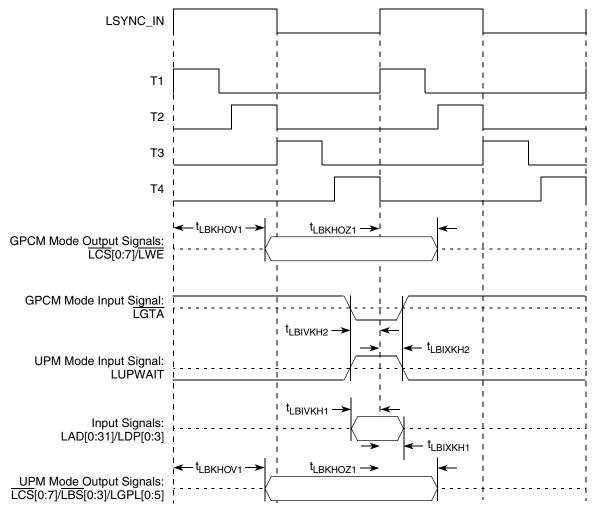

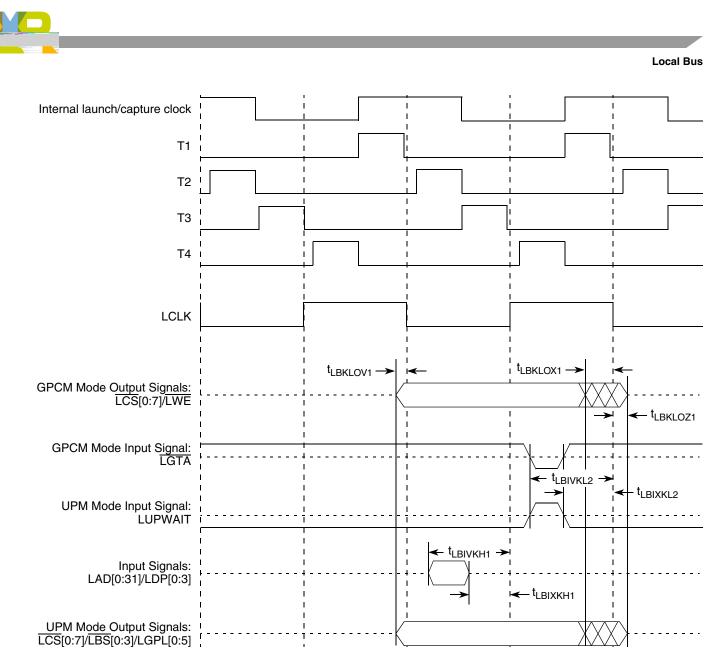

Figure 30. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 or 8 (clock ratio of 8 or 16) (PLL Enabled)

Figure 31. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 or 8 (clock ratio of 8 or 16) (PLL Bypass Mode)

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

This section provides the AC and DC electrized entities for entitled and MII management.

## 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified hereal guidy bit mediadependent in target (GMII), media independent interface) (Mehn-bit interface (TBI), reduiged it media independent interface (RGMII), reduced ten-bit interface (RTBI), durated emedia independent interface (RMII) signals except management duptat/output (MDIO) and grament data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII rated falses can be operated at 3.3 or 2.5 V. Whether the GMII or TBI interface is operated at 3.3 thre 2.5 ming is compatible with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduigrabit Media-Independent efface (RGMII) Specification Version 1.3 (12/10/2000). Time extension the IRM model and MDC are specified in Section 9, Ethernet Managementate electrical haracteristics.

### 8.1.1 eTSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, RMII and RTBI drivers and receivensply with the DC parametric attributes specifiedate 24 and Table 25 The potential applied toin that of a GMII, MII, TBI, RGMII, RMII or RTBI receiver may exceed thetized teen the receiver s posweeply (that is, a GMII driver powered from 3.6-V supply driving HV into a GMII receiver proved from a 2.5-V supply). Tolerance for dissimilar GMII driver receiver supply postentis implicit in the specifications. The RGMII and RTBI signals are based on a QNIOS interface voltage defined by JEDEC EIA/JESD8-5.

| Parameter                                                                       | Symbol                               | Min   | Max   | Unit | Notes  |

|---------------------------------------------------------------------------------|--------------------------------------|-------|-------|------|--------|

| Supply voltage 3.3 V                                                            | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.135 | 3.465 | V    | 1, 2   |

| Output high voltage<br>( $LV_{DD}/TV_{DD} = Min$ , $I_{OH} = -4.0 \text{ mA}$ ) | V <sub>OH</sub>                      | 2.40  | _     | V    |        |

| Output low voltage<br>( $LV_{DD}/TV_{DD} = Min, I_{OL} = 4.0 \text{ mA}$ )      | V <sub>OL</sub>                      |       | 0.50  | V    |        |

| Input high voltage                                                              | V <sub>IH</sub>                      | 2.0   | _     | V    | _      |

| Input low voltage                                                               | V <sub>IL</sub>                      | _     | 0.90  | V    | _      |

| Input high current<br>( $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ )               | I <sub>IH</sub>                      |       | 40    | PA   | 1, 2,3 |

Table 24. GMII, MII, RMII, TBI and FIFO DC Electrical Characteristics

Printed-Circuit Board

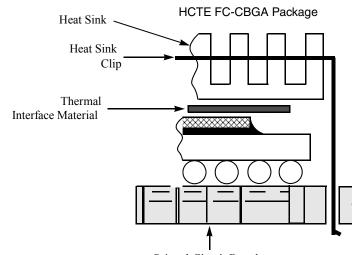

Figure 59. FC-CBGA Package Exploded Cross-Sect ional View with Several Heat Sink Options

There are several commenzational ble heat sinks for MARE8641 provided by the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                                    | 603-224-9988       |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Advanced Thermal Solutions<br>89 Access Road #27.<br>Norwood, MA02062<br>Internet: www.qats.com                                    | 781-769-2800       |

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                                   | 408-749-7601       |

| Calgreg Thermal Solutions<br>60 Alhambra Road, Suite 1<br>Warwick, RI 02886<br>Internet: www.calgreg.com                           | 888-732-6100       |

| International Electronic Resteatorporation<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com                 | (IERC)818-842-7277 |

| Millennium Elec <b>t</b> nics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-thermal.com | 408-436-8770       |