#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | PowerPC e600                                                             |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                           |

| Speed                           | 1.25GHz                                                                  |

| Co-Processors/DSP               | ·                                                                        |

| RAM Controllers                 | DDR, DDR2                                                                |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (4)                                                      |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                        |

| Package / Case                  | 1023-BBGA, FCBGA                                                         |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dthx1250hc |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Electrical Characteristics

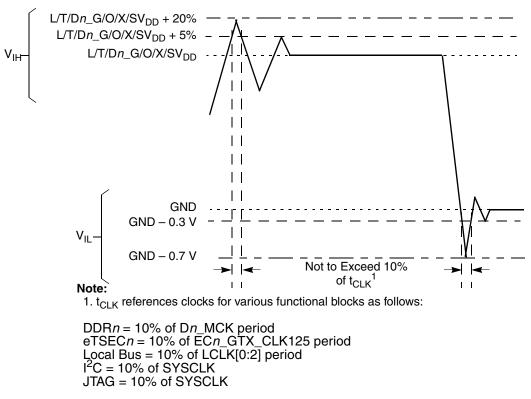

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8641.

Figure 2. Overshoot/Undershoot Voltage for Dn\_M/O/L/TV<sub>IN</sub>

The MPC8641 core voltage must always be provided at nominal  $V_{DD}$ \_Core*n* (See Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $L/TV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced to each externally supplied  $Dn_MV_{REF}$  signal (nominally set to  $Dn_GV_{DD}/2$ ) as is appropriate for the (SSTL-18 and SSTL-25) electrical signaling standards.

# 6.2 DDR SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

## 6.2.1 DDR SDRAM Input AC Timing Specifications

Table 18 provides the input AC timing specifications for the DDR2 SDRAM when  $Dn GV_{DD}(typ)=1.8 V$ .

#### Table 18. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions

| Parameter                                        | Symbol | Min                                                                          | Мах                                                                          | Unit | Notes |

|--------------------------------------------------|--------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|-------|

| AC input low voltage<br>400, 533 MHz<br>600 MHz  |        | _                                                                            | D <i>n_</i> MV <sub>REF</sub> – 0.25<br>D <i>n_</i> MV <sub>REF</sub> – 0.20 | V    | _     |

| AC input high voltage<br>400, 533 MHz<br>600 MHz |        | D <i>n_</i> MV <sub>REF</sub> + 0.25<br>D <i>n_</i> MV <sub>REF</sub> + 0.20 | _                                                                            | V    | _     |

Table 19 provides the input AC timing specifications for the DDR SDRAM when  $Dn_GV_{DD}(typ)=2.5$  V.

Table 19. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions.

| Parameter             | Symbol          | Min                                  | Мах                                  | Unit | Notes |

|-----------------------|-----------------|--------------------------------------|--------------------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                                    | D <i>n</i> _MV <sub>REF</sub> – 0.31 | V    | _     |

| AC input high voltage | V <sub>IH</sub> | D <i>n</i> _MV <sub>REF</sub> + 0.31 | _                                    | V    | _     |

Table 20 provides the input AC timing specifications for the DDR SDRAM interface.

#### Table 20. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions.

| Parameter                            | Symbol              | Min  | Мах | Unit | Notes |

|--------------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for<br>MDQS—MDQ/MECC | <sup>t</sup> CISKEW | —    |     | ps   | 1, 2  |

| 600 MHz                              | —                   | -240 | 240 | —    | 3     |

| 533 MHz                              | —                   | -300 | 300 | —    | 3     |

| 400 MHz                              | —                   | -365 | 365 | —    |       |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> =+/-(T/4 - abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

- 3. Maximum DDR1 frequency is 400 MHz.

#### Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

#### Table 24. GMII, MII, RMII, TBI and FIFO DC Electrical Characteristics (continued)

| Parameter                                    | Symbol          | Min  | Мах | Unit | Notes |

|----------------------------------------------|-----------------|------|-----|------|-------|

| Input low current<br>(V <sub>IN</sub> = GND) | I <sub>IL</sub> | -600 | _   | μA   | 3     |

Notes:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4.

<sup>3</sup> The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

#### Table 25. GMII, RGMII, RTBI, TBI and FIFO DC Electrical Characteristics

| Parameters                                                                                       | Symbol                             | Min   | Мах   | Unit | Notes  |

|--------------------------------------------------------------------------------------------------|------------------------------------|-------|-------|------|--------|

| Supply voltage 2.5 V                                                                             | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.375 | 2.625 | V    | 1,2    |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OH</sub> = -1.0 mA)     | V <sub>OH</sub>                    | 2.00  | _     | V    | —      |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA)       | V <sub>OL</sub>                    | —     | 0.40  | V    | —      |

| Input high voltage                                                                               | V <sub>IH</sub>                    | 1.70  | —     | V    | —      |

| Input low voltage                                                                                | V <sub>IL</sub>                    | —     | 0.90  | V    | —      |

| Input high current<br>(V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> ) | IIH                                | —     | 10    | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                                                     | Ι <sub>IL</sub>                    | -15   | _     | μA   | 3      |

Note:

$^1\,$  LV\_{DD} supports eTSECs 1 and 2.

<sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4.

<sup>3</sup> Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

### 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

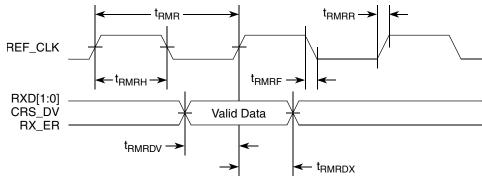

# 8.2.7.2 RMII Receive AC Timing Specifications

#### Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition                                       | Symbol <sup>1</sup>                 | Min  | Тур  | Мах  | Unit |

|-----------------------------------------------------------|-------------------------------------|------|------|------|------|

| REF_CLK clock period                                      | t <sub>RMR</sub>                    | 15.0 | 20.0 | 25.0 | ns   |

| REF_CLK duty cycle                                        | t <sub>RMRH</sub> /t <sub>RMR</sub> | 35   | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                               | t <sub>RMRJ</sub>                   | _    | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                               | t <sub>RMRR</sub>                   | 1.0  | —    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                               | t <sub>RMRF</sub>                   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>                  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>                  | 2.0  | _    |      | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

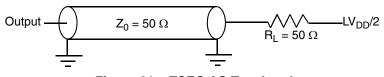

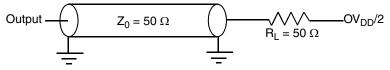

Figure 21 provides the AC test load for eTSEC.

Figure 21. eTSEC AC Test Load

Figure 22 shows the RMII receive AC timing diagram.

Figure 22. RMII Receive AC Timing Diagram

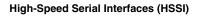

l<sup>2</sup>C

#### Table 46. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 45).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                  | Мах | Unit |

|---------------------------------------------------------------------------------|---------------------|----------------------|-----|------|

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times OV_{DD}$ | —   | V    |

#### Note:

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>12PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. As a transmitter, the MPC8641 provides a delay time of at least 300 ns for the SDA signal (referred to the Vihmin of the SCL signal) to bridge the undefined region of the falling edge of SCL to avoid unintended generation of Start or Stop condition. When MPC8641 acts as the I<sup>2</sup>C bus master while transmitting, MPC8641 drives both SCL and SDA. As long as the load on SCL and SDA are balanced, MPC8641 would not cause unintended generation of Start or Stop condition. Therefore, the 300 ns SDA output delay time is not a concern. If, under some rare condition, the 300 ns SDA output delay time is required for MPC8641 as transmitter, the following setting is recommended for the FDR bit field of the I2CFDR register to ensure both the desired I<sup>2</sup>C SCL clock frequency and SDA output delay time are achieved, assuming that the desired I<sup>2</sup>C SCL clock frequency is 400 KHz and the Digital Filter Sampling Rate Register (I2CDFSRR) is programmed with its default setting of 0x10 (decimal 16):

| I <sup>2</sup> C Source Clock Frequency         | 333 MHz | 266 MHz | 200 MHz | 133 MHz |

|-------------------------------------------------|---------|---------|---------|---------|

| FDR Bit Setting                                 | 0x2A    | 0x05    | 0x26    | 0x00    |

| Actual FDR Divider Selected                     | 896     | 704     | 512     | 384     |

| Actual I <sup>2</sup> C SCL Frequency Generated | 371 KHz | 378 KHz | 390 KHz | 346 KHz |

For the detail of I<sup>2</sup>C frequency calculation, refer to the application note AN2919 "Determining the I<sup>2</sup>C Frequency Divider Ratio for SCL". Note that the I<sup>2</sup>C Source Clock Frequency is half of the MPX clock frequency for MPC8641.

- 3. The maximum t<sub>I2DXKL</sub> has only to be met if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. Guaranteed by design.

- 5.  $C_B$  = capacitance of one bus line in pF.

Figure 32 provides the AC test load for the  $I^2C$ .

Figure 36. I<sup>2</sup>C AC Test Load

Figure 37 shows the AC timing diagram for the  $I^2C$  bus.

Figure 37. I<sup>2</sup>C Bus AC Timing Diagram

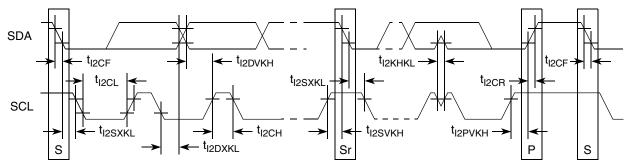

# 13 High-Speed Serial Interfaces (HSSI)

The MPC8641D features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface is dedicated for PCI Express data transfers. The SerDes2 can be used for PCI Express and/or Serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 13.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD*n*\_TX and  $\overline{SDn}_T\overline{X}$ ) or a receiver input (SD*n*\_RX and  $\overline{SDn}_R\overline{X}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals  $SDn_TX$ ,  $\overline{SDn_TX}$ ,  $SDn_RX$  and  $\overline{SDn_RX}$  each have a peak-to-peak swing of A – B Volts. This is also referred as each signal wire's Single-Ended Swing.

### 2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

Serial RapidIO

| Characteristic              | Symbol              | Ra    | inge | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | onic   | NOICES                                                                           |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/– 100 ppm                                                                      |

#### Table 52. Short Run Transmitter AC Timing Specifications—1.25 GBaud

#### Table 53. Short Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|

|                             | Symbol              | Min   | Max  | onit   | NOICS                                                                            |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                                |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                                |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                                |

| Multiple Output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/- 100 ppm                                                                      |

#### Table 54. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                            |     |       |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|-----|-------|

|                             | Symbol              | Min   | Мах  | Unit   | Onit                                                                             | Onn | NOICS |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |     |       |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                                |     |       |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |     |       |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |     |       |

| Transmitter Type        | V <sub>DIFF</sub> min<br>(mV) | V <sub>DIFF</sub> max<br>(mV) | A (UI) | B (UI) |

|-------------------------|-------------------------------|-------------------------------|--------|--------|

| 1.25 GBaud short range  | 250                           | 500                           | 0.175  | 0.39   |

| 1.25 GBaud long range   | 400                           | 800                           | 0.175  | 0.39   |

| 2.5 GBaud short range   | 250                           | 500                           | 0.175  | 0.39   |

| 2.5 GBaud long range    | 400                           | 800                           | 0.175  | 0.39   |

| 3.125 GBaud short range | 250                           | 500                           | 0.175  | 0.39   |

| 3.125 GBaud long range  | 400                           | 800                           | 0.175  | 0.39   |

Table 58. Transmitter Differential Output Eye Diagram Parameters

# 15.7 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to (0.8)\*(Baud Frequency). This includes contributions from on-chip circuitry, the chip package and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100 Ohm resistive for differential return loss and 25 Ohm resistive for common mode.

| Characteristic                                     | Range           |      | nge<br>Unit       |        | Notes                                                        |  |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min  | Max               | Unit   | notes                                                        |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                         |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                         |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                         |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _    | 24                | ns     | Skew at the receiver input between lanes of a multilane link |  |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | —                                                            |  |

| Unit Interval                                      | UI              | 800  | 800               | ps     | +/- 100 ppm                                                  |  |

Table 59. Receiver AC Timing Specifications—1.25 GBaud

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Characteristic                                     | Range Symbol    |      | nge               | Unit   | Notes                                                              |  |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min  | Мах               | Onit   | Notes                                                              |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                               |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | _                 | UI p-p | Measured at receiver                                               |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | _                 | UI p-p | Measured at receiver                                               |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                               |  |

| Multiple Input Skew                                | S <sub>MI</sub> | _    | 24                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | _      | _                                                                  |  |

| Unit Interval                                      | UI              | 400  | 400               | ps     | +/- 100 ppm                                                        |  |

| Table 60. Receiver | AC Timing | Specifications—2.5 GBaud |

|--------------------|-----------|--------------------------|

|--------------------|-----------|--------------------------|

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

| Table 61. Receiver AC Timing Speci | ifications—3.125 GBaud |

|------------------------------------|------------------------|

|------------------------------------|------------------------|

| Characteristic                                     | Range Symbol    |      | uge Unit          |        | Notes                                                              |  |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------------|--|

| Characteristic                                     | Cymbol          | Min  | Max               | Onit   | noico                                                              |  |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV p-p | Measured at receiver                                               |  |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                               |  |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 | _                 | UI p-p | Measured at receiver                                               |  |

| Total Jitter Tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                               |  |

| Multiple Input Skew                                | S <sub>MI</sub> | —    | 22                | ns     | Skew at the receiver input<br>between lanes of a multilane<br>link |  |

| Bit Error Rate                                     | BER             | —    | 10 <sup>-12</sup> | _      | —                                                                  |  |

| Unit Interval                                      | UI              | 320  | 320               | ps     | +/– 100 ppm                                                        |  |

Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 55. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

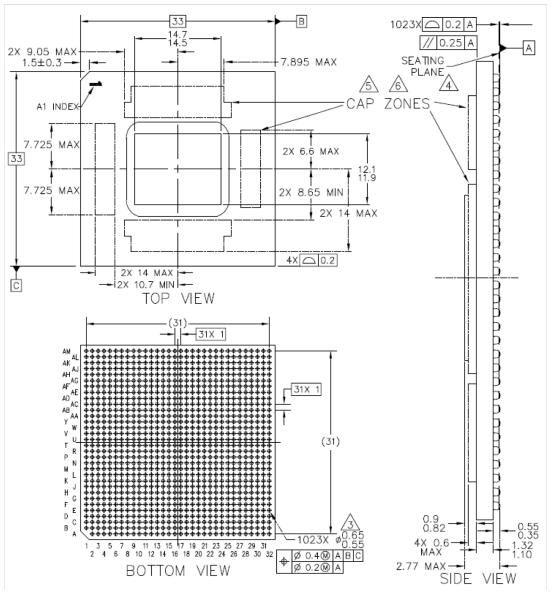

8. Note that for MPC8641 (single core) the solder balls for the following signals/pins are not populated in the package: VDD\_Core1 (R16, R18, R20, T17, T19, T21, T23, U16, U18, U22, V17, V19, V21, V23, W16, W18, W20, W22, Y17, Y19, Y21, Y23, AA16, AA18, AA20, AA22, AB23, AC24) and SENSEVDD\_Core1 (U20).

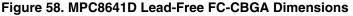

#### NOTES for Figure 58

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or expose metal capacitor pads on package top.

- 7. All dimensions symmetrical about centerlines unless otherwise specified.

- Note that for MPC8641 (single core) the solder balls for the following signals/pins are not populated in the package: VDD\_Core1 (R16, R18, R20, T17, T19, T21, T23, U16, U18, U22, V17, V19, V21, V23, W16, W18, W20, W22, Y17, Y19, Y21, Y23, AA16, AA18, AA20, AA22, AB23, AC24) and SENSEVDD\_Core1 (U20).

| Name <sup>1</sup>    | Package Pin Number                                                                                                                                                                                                                                                                                              | Pin Type                           | Power Supply           | Notes  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------|--------|

| D2_MDQ[0:63]         | A7, B7, C5, D5, C8, D8, D6, A5, C4, A3, D3,<br>D2, A4, B4, C2, C1, E3, E1, H4, G1, D1, E4,<br>G3, G2, J4, J2, L1, L3, H3, H1, K1, L4, AA4,<br>AA2, AD1, AD2, Y1, AA1, AC1, AC3, AD5,<br>AE1, AG1, AG2, AC4, AD4, AF3, AF4, AH3,<br>AJ1, AM1, AM3, AH1, AH2, AL2, AL3, AK5,<br>AL5, AK7, AM7, AK4, AM4, AM6, AJ7 | I/O                                | D2_GV <sub>DD</sub>    | _      |

| D2_MECC[0:7]         | H6, J5, M5, M4, G6, H7, M2, M1                                                                                                                                                                                                                                                                                  | I/O                                | $D2_GV_{DD}$           | —      |

| D2_MDM[0:8]          | C7, B3, F4, J1, AB1, AE2, AK1, AM5, K6                                                                                                                                                                                                                                                                          | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MDQS[0:8]         | B6, B1, F1, K2, AB3, AF1, AL1, AL6, L6                                                                                                                                                                                                                                                                          | I/O                                | D2_GV <sub>DD</sub>    | _      |

| D2_MDQS[0:8]         | A6, A2, F2, K3, AB2, AE3, AK2, AJ6, K5                                                                                                                                                                                                                                                                          | I/O                                | D2_GV <sub>DD</sub>    | _      |

| D2_MBA[0:2]          | W5, V5, P3                                                                                                                                                                                                                                                                                                      | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MA[0:15]          | W1, U4, U3, T1, T2, T3, T5, R2, R1, R5, V4,<br>R4, P1, AH5, P4, N1                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MWE               | Y4                                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MRAS              | W3                                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCAS              | AB5                                                                                                                                                                                                                                                                                                             | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCS[0:3]          | Y3, AF6, AA5, AF7                                                                                                                                                                                                                                                                                               | 0                                  | D2_GV <sub>DD</sub>    | _      |

| D2_MCKE[0:3]         | N6, N5, N2, N3                                                                                                                                                                                                                                                                                                  | 0                                  | D2_GV <sub>DD</sub>    | 23     |

| D2_MCK[0:5]          | U1, F5, AJ3, V2, E7, AG4                                                                                                                                                                                                                                                                                        | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MCK[0:5]          | V1, G5, AJ4, W2, E6, AG5                                                                                                                                                                                                                                                                                        | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MODT[0:3]         | AE6, AG7, AE5, AH6                                                                                                                                                                                                                                                                                              | 0                                  | D2_GV <sub>DD</sub>    | —      |

| D2_MDIC[0:1]         | F8, F7                                                                                                                                                                                                                                                                                                          | IO                                 | D2_GV <sub>DD</sub>    | 27     |

| D2_MV <sub>REF</sub> | A18                                                                                                                                                                                                                                                                                                             | DDR Port 2<br>reference<br>voltage | D2_GV <sub>DD</sub> /2 | 3      |

|                      | High Speed I/O Interface 1 (                                                                                                                                                                                                                                                                                    | SERDES 1) <sup>4</sup>             |                        |        |

| SD1_TX[0:7]          | L26, M24, N26, P24, R26, T24, U26, V24                                                                                                                                                                                                                                                                          | 0                                  | SV <sub>DD</sub>       | —      |

| SD1_TX[0:7]          | L27, M25, N27, P25, R27, T25, U27, V25                                                                                                                                                                                                                                                                          | 0                                  | SV <sub>DD</sub>       | —      |

| SD1_RX[0:7]          | J32, K30, L32, M30, T30, U32, V30, W32                                                                                                                                                                                                                                                                          | Ι                                  | SV <sub>DD</sub>       | —      |

| SD1_RX[0:7]          | J31, K29, L31, M29, T29, U31, V29, W31                                                                                                                                                                                                                                                                          | I                                  | SV <sub>DD</sub>       | —      |

| SD1_REF_CLK          | N32                                                                                                                                                                                                                                                                                                             | I                                  | SV <sub>DD</sub>       | —      |

| SD1_REF_CLK          | N31                                                                                                                                                                                                                                                                                                             | I                                  | SV <sub>DD</sub>       | —      |

| SD1_IMP_CAL_TX       | Y26                                                                                                                                                                                                                                                                                                             | Analog                             | SV <sub>DD</sub>       | 19     |

| SD1_IMP_CAL_RX       | J28                                                                                                                                                                                                                                                                                                             | Analog                             | SV <sub>DD</sub>       | 30     |

| SD1_PLL_TPD          | U28                                                                                                                                                                                                                                                                                                             | 0                                  | SV <sub>DD</sub>       | 13, 17 |

#### Table 63. MPC8641 Signal Reference by Functional Block (continued)

Signal Listings

| Name <sup>1</sup>               | Package Pin Number                             | Pin Type         | Power Supply     | Notes    |

|---------------------------------|------------------------------------------------|------------------|------------------|----------|

| TSEC1_TXD[0:7]/<br>GPOUT[0:7]   | AF25, AC23, AG24, AG23, AE24, AE23, AE22, AD22 | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC1_TX_EN                     | AB22                                           | 0                | LV <sub>DD</sub> | 36       |

| TSEC1_TX_ER                     | AH26                                           | 0                | LV <sub>DD</sub> | _        |

| TSEC1_TX_CLK                    | AC22                                           | I                | LV <sub>DD</sub> | 40       |

| TSEC1_GTX_CLK                   | AH25                                           | 0                | LV <sub>DD</sub> | 41       |

| TSEC1_CRS                       | AM24                                           | I/O              | LV <sub>DD</sub> | 37       |

| TSEC1_COL                       | AM25                                           | I                | LV <sub>DD</sub> | _        |

| TSEC1_RXD[0:7]/<br>GPIN[0:7]    | AL25, AL24, AK26, AK25, AM26, AF26, AH24, AG25 | I                | LV <sub>DD</sub> | 10       |

| TSEC1_RX_DV                     | AJ24                                           | I                | LV <sub>DD</sub> | —        |

| TSEC1_RX_ER                     | AJ25                                           | I                | LV <sub>DD</sub> | —        |

| TSEC1_RX_CLK                    | AK24                                           | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 2 Sign                              | als <sup>5</sup> |                  |          |

| TSEC2_TXD[0:3]/<br>GPOUT[8:15]  | AB20, AJ23, AJ22, AD19                         | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TXD[4]/<br>GPOUT[12]      | AH23                                           | 0                | LV <sub>DD</sub> | 6,10, 38 |

| TSEC2_TXD[5:7]/<br>GPOUT[13:15] | AH21, AG22, AG21                               | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TX_EN                     | AB21                                           | 0                | LV <sub>DD</sub> | 36       |

| TSEC2_TX_ER                     | AB19                                           | 0                | LV <sub>DD</sub> | 6, 38    |

| TSEC2_TX_CLK                    | AC21                                           | I                | LV <sub>DD</sub> | 40       |

| TSEC2_GTX_CLK                   | AD20                                           | 0                | LV <sub>DD</sub> | 41       |

| TSEC2_CRS                       | AE20                                           | I/O              | LV <sub>DD</sub> | 37       |

| TSEC2_COL                       | AE21                                           | I                | LV <sub>DD</sub> |          |

| TSEC2_RXD[0:7]/<br>GPIN[8:15]   | AL22, AK22, AM21, AH20, AG20, AF20, AF23, AF22 | I                | LV <sub>DD</sub> | 10       |

| TSEC2_RX_DV                     | AC19                                           | I                | LV <sub>DD</sub> | _        |

| TSEC2_RX_ER                     | AD21                                           | I                | LV <sub>DD</sub> | _        |

| TSEC2_RX_CLK                    | AM22                                           | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 3 Sign                              | als <sup>5</sup> | 1                |          |

| TSEC3_TXD[0:3]                  | AL21, AJ21, AM20, AJ20                         | 0                | TV <sub>DD</sub> | 6        |

| TSEC3_TXD[4]/                   | AM19                                           | 0                | TV <sub>DD</sub> | _        |

| TSEC3_TXD[5:7]                  | AK21, AL20, AL19                               | 0                | TV <sub>DD</sub> | 6        |

#### Table 63. MPC8641 Signal Reference by Functional Block (continued)

Signal Listings

| Name <sup>1</sup>              | Package Pin Number                             | Pin Type                              | Power Supply     | Notes            |

|--------------------------------|------------------------------------------------|---------------------------------------|------------------|------------------|

| D1_MDVAL/LB_DVAL               | J16                                            | 0                                     | OV <sub>DD</sub> | 10               |

| D2_MDVAL                       | D19                                            | 0                                     | OV <sub>DD</sub> | _                |

|                                | Power Management S                             | Signals <sup>5</sup>                  |                  |                  |

| ASLEEP                         | C19                                            | 0                                     | OV <sub>DD</sub> | —                |

|                                | System Clocking Si                             | gnals <sup>5</sup>                    |                  |                  |

| SYSCLK                         | G16                                            | I                                     | OV <sub>DD</sub> | —                |

| RTC                            | K17                                            | I                                     | OV <sub>DD</sub> | 32               |

| CLK_OUT                        | B16                                            | 0                                     | OV <sub>DD</sub> | 23               |

|                                | Test Signals <sup>5</sup>                      |                                       | - <b>I</b>       |                  |

| LSSD_MODE                      | C18                                            | I                                     | OV <sub>DD</sub> | 26               |

| TEST_MODE[0:3]                 | C16, E17, D18, D16                             | I                                     | OV <sub>DD</sub> | 26               |

|                                | JTAG Signals <sup>5</sup>                      | 5                                     | · · ·            |                  |

| ТСК                            | H18                                            | I                                     | OV <sub>DD</sub> |                  |

| TDI                            | J18                                            | I                                     | OV <sub>DD</sub> | 24               |

| TDO                            | G18                                            | 0                                     | OV <sub>DD</sub> | 23               |

| TMS                            | F18                                            | I                                     | OV <sub>DD</sub> | 24               |

| TRST                           | A17                                            | I                                     | OV <sub>DD</sub> | 24               |

|                                | Miscellaneous                                  | 5                                     | · · ·            |                  |

| Spare                          | J17                                            | _                                     | —                | 13               |

| GPOUT[0:7]/<br>TSEC1_TXD[0:7]  | AF25, AC23, AG24, AG23, AE24, AE23, AE22, AD22 | 0                                     | OV <sub>DD</sub> | 6, 10            |

| GPIN[0:7]/<br>TSEC1_RXD[0:7]   | AL25, AL24, AK26, AK25, AM26, AF26, AH24, AG25 | I                                     | OV <sub>DD</sub> | 10               |

| GPOUT[8:15]/<br>TSEC2_TXD[0:7] | AB20, AJ23, AJ22, AD19, AH23, AH21, AG22, AG21 | 0                                     | OV <sub>DD</sub> | 10               |

| GPIN[8:15]/<br>TSEC2_RXD[0:7]  | AL22, AK22, AM21, AH20, AG20, AF20, AF23, AF22 | I                                     | OV <sub>DD</sub> | 10               |

|                                | Additional Analog S                            | ignals                                | - <b>I</b>       |                  |

| TEMP_ANODE                     | AA11                                           | Thermal                               | —                |                  |

| TEMP_CATHODE                   | Y11                                            | Thermal                               | —                |                  |

|                                | Sense, Power and GNI                           | ) Signals                             |                  |                  |

| SENSEV <sub>DD</sub> _Core0    | M14                                            | V <sub>DD</sub> _Core0<br>sensing pin | -                | 31               |

| SENSEV <sub>DD</sub> Core1     | U20                                            | V <sub>DD</sub> _Core1<br>sensing pin | -                | 12,31, <i>S1</i> |

| Name <sup>1</sup>           | Package Pin Number                                                                                                                                                  | Pin Type                                                                                                                                                                                                | Power Supply                                       | Notes             |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|

| SENSEV <sub>SS</sub> _Core0 | P14                                                                                                                                                                 | Core0 GND sensing pin                                                                                                                                                                                   | —                                                  | 31                |

| SENSEV <sub>SS</sub> _Core1 | V20                                                                                                                                                                 | Core1 GND sensing pin                                                                                                                                                                                   | —                                                  | 12, 31, <i>S3</i> |

| SENSEV <sub>DD</sub> _PLAT  | N18                                                                                                                                                                 | V <sub>DD</sub> _PLAT<br>sensing pin                                                                                                                                                                    | —                                                  | 28                |

| SENSEV <sub>SS</sub> _PLAT  | P18                                                                                                                                                                 | Platform GND sensing pin                                                                                                                                                                                | _                                                  | 29                |

| D1_GV <sub>DD</sub>         | B11, B14, D10, D13, F9, F12, H8, H11,<br>H14, K10, K13, L8, P8, R6, U8, V6, W10,<br>Y8, AA6, AB10, AC8, AD12, AE10, AF8,<br>AG12, AH10, AJ8, AJ14, AK12, AL10, AL16 | SDRAM 1 I/O<br>supply                                                                                                                                                                                   | D1_GV <sub>DD</sub><br>2.5 - DDR<br>1.8 DDR2       | _                 |

| D2_GV <sub>DD</sub>         | B2, B5, B8, D4, D7, E2, F6, G4, H2, J6, K4,<br>L2, M6, N4, P2, T4, U2, W4, Y2, AB4, AC2,<br>AD6, AE4, AF2, AG6, AH4, AJ2, AK6, AL4,<br>AM2                          | SDRAM 2 I/O<br>supply                                                                                                                                                                                   | D2_GV <sub>DD</sub><br>2.5 V - DDR<br>1.8 V - DDR2 | _                 |

| OV <sub>DD</sub>            | B22, B25, B28, D17, D24, D27, F19, F22,<br>F26, F29, G17, H21, H24, K19, K23, M21,<br>AM30                                                                          | DUART, Local<br>Bus, DMA,<br>Multiprocessor<br>Interrupts,<br>System Control<br>& Clocking,<br>Debug, Test,<br>JTAG, Power<br>management,<br>I <sup>2</sup> C, JTAG and<br>Miscellaneous<br>I/O voltage | OV <sub>DD</sub><br>3.3 V                          | _                 |

| LV <sub>DD</sub>            | AC20, AD23, AH22                                                                                                                                                    | TSEC1 and<br>TSEC2 I/O<br>voltage                                                                                                                                                                       | LV <sub>DD</sub><br>2.5/3.3 V                      | _                 |

| TV <sub>DD</sub>            | AC17, AG18, AK20                                                                                                                                                    | TSEC3 and<br>TSEC4 I/O<br>voltage                                                                                                                                                                       | TV <sub>DD</sub><br>2.5/3.3 V                      | _                 |

| SV <sub>DD</sub>            | H31, J29, K28, K32, L30, M28, M31, N29,<br>R30, T31, U29, V32, W30, Y31, AA29,<br>AB32, AC30, AD31, AE29, AG30, AH31,<br>AJ29, AK32, AL30, AM31                     | Transceiver<br>Power Supply<br>SerDes                                                                                                                                                                   | SV <sub>DD</sub><br>1.05/1.1 V                     |                   |

| XV <sub>DD</sub> _SRDS1     | K26, L24, M27, N25, P26, R24, R28, T27,<br>U25, V26                                                                                                                 | Serial I/O<br>Power Supply<br>for SerDes<br>Port 1                                                                                                                                                      | XV <sub>DD</sub> _SRDS1<br>1.05/1.1 V              | _                 |

Signal Listings

| Name <sup>1</sup>                         | Package Pin Number                                                                                                                                                      | Pin Type | Power Supply     | Notes |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| TSEC3_TXD[6:7]/<br>cfg_tsec3_prtcl[0:1]   | AL20, AL19                                                                                                                                                              |          | LV <sub>DD</sub> | _     |

| TSEC4_TXD[0:3]/<br>cfg_io_ports[0:3]      | AC18, AC16, AD18, AD17                                                                                                                                                  | _        | LV <sub>DD</sub> | —     |

| TSEC4_TXD[5]/<br>cfg_tsec4_reduce         | AB18                                                                                                                                                                    | _        | LV <sub>DD</sub> | _     |

| TSEC4_TXD[6:7]/<br>cfg_tsec4_prtcl[0:1]   | AB17, AB16                                                                                                                                                              | _        | LV <sub>DD</sub> | _     |

| LAD[0:31]/<br>cfg_gpporcr[0:31]           | A30, E29, C29, D28, D29, H25, B29, A29,<br>C28, L22, M22, A28, C27, H26, G26, B27,<br>B26, A27, E27, G25, D26, E26, G24, F27,<br>A26, A25, C25, H23, K22, D25, F25, H22 | _        | OV <sub>DD</sub> | _     |

| LWE[0]/cfg_cpu_boot                       | E21                                                                                                                                                                     | _        | OV <sub>DD</sub> | —     |

| LWE[1]/cfg_rio_sys_size                   | F21                                                                                                                                                                     | —        | OV <sub>DD</sub> | _     |

| LWE[2:3]/<br>cfg_host_agt[0:1]            | D22, E20                                                                                                                                                                | —        | OV <sub>DD</sub> | _     |

| LDP[0:3], LA[27] /<br>cfg_core_pll[0:4]   | A24, E24, C24, B24,<br>J21                                                                                                                                              | _        | OV <sub>DD</sub> | 22    |

| LA[28:31]/<br>cfg_sys_pll[0:3]            | K21, G22, F24, G21                                                                                                                                                      |          | OV <sub>DD</sub> | 22    |

| LGPL[3],<br>LGPL[5]/<br>cfg_boot_seq[0:1] | K20,<br>J19                                                                                                                                                             | _        | OV <sub>DD</sub> | _     |

| D1_MSRCID[0]/<br>cfg_mem_debug            | F15                                                                                                                                                                     | _        | OV <sub>DD</sub> | _     |

| D1_MSRCID[1]/<br>cfg_ddr_debug            | K15                                                                                                                                                                     | _        | OV <sub>DD</sub> | _     |

Table 63. MPC8641 Signal Reference by Functional Block (continued)

# 19 Thermal

This section describes the thermal specifications of the MPC8641.

# **19.1 Thermal Characteristics**

Table 71 provides the package thermal characteristics for the MPC8641.

#### Table 71. Package Thermal Characteristics<sup>1</sup>

| Characteristic                                                                      | Symbol              | Value | Unit | Notes |

|-------------------------------------------------------------------------------------|---------------------|-------|------|-------|

| Junction-to-ambient thermal resistance, natural convection, single-layer (1s) board | $R_{	ext{	heta}JA}$ | 18    | °C/W | 1, 2  |

| Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board | $R_{	ext{	heta}JA}$ | 13    | °C/W | 1, 3  |

| Junction-to-ambient thermal resistance, 200 ft/min airflow, single-layer (1s) board | $R_{\thetaJMA}$     | 13    | °C/W | 1, 3  |

| Junction-to-ambient thermal resistance, 200 ft/min airflow, four-layer (2s2p) board | $R_{\thetaJMA}$     | 9     | °C/W | 1, 3  |

| Junction-to-board thermal resistance                                                | $R_{\thetaJB}$      | 5     | °C/W | 4     |

| Junction-to-case thermal resistance                                                 | $R_{	ext{	heta}JC}$ | < 0.1 | °C/W | 5     |

#### Notes:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- 3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. This is the thermal resistance between die and case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1 °C/W.

# **19.2 Thermal Management Information**

This section provides thermal management information for the high coefficient of thermal expansion (HCTE) package for air-cooled applications. Proper thermal control design is primarily dependent on the system-level design—the heat sink, airflow, and thermal interface material. The MPC8641 implements several features designed to assist with thermal management, including the temperature diode. The temperature diode allows an external device to monitor the die temperature in order to detect excessive temperature conditions and alert the system; see Section 19.2.4, "Temperature Diode," for more information.

To reduce the die-junction temperature, heat sinks are required; due to the potential large mass of the heat sink, attachment through the printed-circuit board is suggested. In any implementation of a heat sink solution, the force on the die should not exceed ten pounds force (45 newtons). Figure 59 shows a spring clip through the board. Occasionally the spring clip is attached to soldered hooks or to a plastic backing structure. Screw and spring arrangements are also frequently used.

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com | 800-347-4572 |

|------------------------------------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801<br>Internet: www.chomerics.com                                    | 781-935-4850 |

| Dow-Corning Corporation<br>Corporate Center<br>PO Box 994<br>Midland, MI 48686-0994<br>Internet: www.dowcorning.com    | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                         | 888-642-7674 |

| Thermagon Inc.<br>4707 Detroit Ave.<br>Cleveland, OH 44102<br>Internet: www.thermagon.com                              | 888-246-9050 |

The following section provides a heat sink selection example using one of the commercially available heat sinks.

# **19.2.3 Heat Sink Selection Example**

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$T_j = T_i + T_r + (R_{\theta JC} + R_{\theta int} + R_{\theta sa}) \times P_d$

where:

T<sub>i</sub> is the die-junction temperature

T<sub>i</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$R_{\theta JC}$  is the junction-to-case thermal resistance

$R_{\theta int}$  is the adhesive or interface material thermal resistance

$R_{\theta sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation, the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_j)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material ( $R_{0int}$ ) is typically about 0.2°C/W. For

#### System Design Information

designer place at least one decoupling capacitor at each  $OV_{DD}$ ,  $Dn_GV_{DD}$ ,  $LV_{DD}$ ,  $TV_{DD}$ ,  $V_{DD}_{DD}$ . Coren, and  $V_{DD}_{DD}_{PLAT}$  pin of the device. These decoupling capacitors should receive their power from separate  $OV_{DD}$ ,  $Dn_GV_{DD}$ ,  $LV_{DD}$ ,  $TV_{DD}$ ,  $V_{DD}_{DD}_{DD}_{PLAT}$  and GND power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $OV_{DD}$ ,  $Dn_GV_{DD}$ ,  $LV_{DD}$ ,  $TV_{DD}$ ,  $V_{DD}$ . Coren, and  $V_{DD}$ \_PLAT planes, to enable quick recharging of the smaller chip capacitors. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330 µF (AVX TPS tantalum or Sanyo OSCON).

# 20.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power ( $SV_{DD}$  and  $XV_{DD}$ \_SRDS*n*) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 x 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there should be a  $1-\mu F$  ceramic chip capacitor on each side of the device. This should be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there should be a  $10-\mu$ F, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a  $100-\mu$ F, low ESR SMT tantalum chip capacitor. This should be done for all SerDes supplies.

# 20.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. In general all unused active low inputs should be tied to  $OV_{DD}$ ,  $Dn_GV_{DD}$ ,  $LV_{DD}$ ,  $TV_{DD}$ ,  $V_{DD}$ \_Coren, and  $V_{DD}_{DD}$ \_PLAT,  $XV_{DD}_{DD}$ \_SRDSn, and  $SV_{DD}$  as required and unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Special cases:

DDR - If one of the DDR ports is not being used the power supply pins for that port can be connected to ground so that there is no need to connect the individual unused inputs of that port to ground. Note that these power supplies can only be powered up again at reset for functionality to occur on the DDR port. Power supplies for other functional buses should remain powered.

#### System Design Information

The following pins must be connected to GND:

- SD*n*\_RX[7:0]

- $\overline{\text{SD}n \text{ RX}}[7:0]$

- SD*n*\_REF\_CLK

- SDn\_REF\_CLK

### NOTE

It is recommended to power down the unused lane through SRDS1CR1[0:7] register (offset =  $0xE_0F08$ ) and SRDS2CR1[0:7] register (offset =  $0xE_0F44$ .) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

For other directions on reserved or no-connects pins see Section 17, "Signal Listings."

# 20.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8641 requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on all open drain type pins.

The following pins must NOT be pulled down during power-on reset: TSEC4\_TXD[4], LGPL0/LSDA10, LGPL1/LSDWE, TRIG\_OUT/READY, and D1\_MSRCID[2].

The following are factory test pins and require strong pull up resistors (100  $\Omega$  –1 k $\Omega$ ) to OVDD

LSSD\_MODE, TEST\_MODE[0:3]. The following pins require weak pull up resistors (2–10 kΩ) to their specific power supplies: LCS[0:4], LCS[5]/DMA\_DREQ2, LCS[6]/DMA\_DACK[2], LCS[7]/DMA\_DDONE[2], IRQ\_OUT, IIC1\_SDA, IIC1\_SCL, IIC2\_SDA, IIC2\_SCL, and CKSTP\_OUT.

The following pins should be pulled to ground with a 100- $\Omega$  resistor: SD1\_IMP\_CAL\_TX, SD2\_IMP\_CAL\_TX. The following pins should be pulled to ground with a 200- $\Omega$  resistor: SD1\_IMP\_CAL\_RX, SD2\_IMP\_CAL\_RX.

TSEC*n*\_TX\_EN signals require an external 4.7-k $\Omega$  pull down resistor to prevent PHY from seeing a valid Transmit Enable before it is actively driven.

When the platform frequency is 400 MHz, TSEC1\_TXD[1] must be pulled down at reset.

TSEC2\_TXD[4] and TSEC2\_TX\_ER pins function as cfg\_dram\_type[0 or 1] at reset and MUST BE VALID BEFORE HRESET ASSERTION when coming out of device sleep mode.

# 20.6.1 Special instructions for Single Core device

The mechanical drawing for the single core device does not have all the solder balls that exist on the single core device. This includes all the balls for VDD\_Core1 and SENSEV<sub>DD</sub>\_Core1 which exist on the package for the dual core device, but not on the single core package. A solder ball is present for SENSEV<sub>SS</sub>\_Core1 and needs to be connected to ground with a weak (2-10 k $\Omega$ ) pull down resistor. Likewise, AV<sub>DD</sub>\_Core1 needs to be pulled to ground as shown in Figure 64.

The mechanical drawing for the single core device is located in Section 16.2, "Mechanical Dimensions of the MPC8641 FC-CBGA."

Ordering Information

# 21 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 21.1, "Part Numbers Fully Addressed by This Document."

# 21.1 Part Numbers Fully Addressed by This Document

Table 74 provides the Freescale part numbering nomenclature for the MPC8641. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MC              | nnnn               | x                                             | xx                                                                                                                                | nnnn                                              | x                                                                                    | x                                                                                                                                                                                                                                                                                                                                                                          |