Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                          |

|---------------------------------|--------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                 |

| Core Processor                  | PowerPC e600                                                             |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                           |

| Speed                           | 1.333GHz                                                                 |

| Co-Processors/DSP               | -                                                                        |

| RAM Controllers                 | DDR, DDR2                                                                |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (4)                                                      |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                        |

| Package / Case                  | 1023-BCBGA, FCCBGA                                                       |

| Supplier Device Package         | 1023-FCCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641dtvj1333je |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Electrical Characteristics**

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8641. The MPC8641 is currently targeted to these specifications.

# 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings<sup>1</sup>

| Characteristic                                                                                                                                                   | Symbol                                              | Absolute Maximum<br>Value | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|------|-------|

| Cores supply voltages                                                                                                                                            | V <sub>DD</sub> Core0,<br>V <sub>DD</sub> Core1     | -0.3 to 1.21 V            | V    | 2     |

| Cores PLL supply                                                                                                                                                 | AV <sub>DD</sub> _Core0,<br>AV <sub>DD</sub> _Core1 | -0.3 to 1.21 V            | V    | _     |

| SerDes Transceiver Supply (Ports 1 and 2)                                                                                                                        | SV <sub>DD</sub>                                    | -0.3 to 1.21 V            | V    | _     |

| SerDes Serial I/O Supply Port 1                                                                                                                                  | XV <sub>DD_</sub> SRDS1                             | -0.3 to 1.21V             | V    | _     |

| SerDes Serial I/O Supply Port 2                                                                                                                                  | XV <sub>DD_</sub> SRDS2                             | -0.3 to 1.21 V            | V    | _     |

| SerDes DLL and PLL supply voltage for Port 1 and Port 2                                                                                                          | AV <sub>DD</sub> SRDS1,<br>AV <sub>DD</sub> SRDS2   | -0.3 to 1.21V             | V    | _     |

| Platform Supply voltage                                                                                                                                          | V <sub>DD</sub> PLAT                                | -0.3 to 1.21V             | V    | _     |

| Local Bus and Platform PLL supply voltage                                                                                                                        | AV <sub>DD</sub> LB,<br>AV <sub>DD</sub> PLAT       | -0.3 to 1.21V             | V    | _     |

| DDR and DDR2 SDRAM I/O supply voltages                                                                                                                           | D1_GV <sub>DD,</sub>                                | -0.3 to 2.75 V            | V    | 3     |

|                                                                                                                                                                  | D2_GV <sub>DD</sub>                                 | -0.3 to 1.98 V            | V    | 3     |

| eTSEC 1 and 2 I/O supply voltage                                                                                                                                 | LV <sub>DD</sub>                                    | -0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                  |                                                     | –0.3 to 2.75 V            | V    | 4     |

| eTSEC 3 and 4 I/O supply voltage                                                                                                                                 | TV <sub>DD</sub>                                    | -0.3 to 3.63 V            | V    | 4     |

|                                                                                                                                                                  |                                                     | -0.3 to 2.75 V            | V    | 4     |

| Local Bus, DUART, DMA, Multiprocessor Interrupts, System Control & Clocking, Debug, Test, Power management, I <sup>2</sup> C, JTAG and Miscellaneous I/O voltage | OV <sub>DD</sub>                                    | -0.3 to 3.63 V            | V    | _     |

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Table 3. Output Drive Capability**

| Driver Type                                                                                                                               | Programmable Output Impedance (Ω) | Supply<br>Voltage                    | Notes   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|---------|

| DDR1 signal                                                                                                                               | 18<br>36 (half strength mode)     | D <i>n</i> _GV <sub>DD</sub> = 2.5 V | 4, 9    |

| DDR2 signal                                                                                                                               | 18<br>36 (half strength mode)     | D <i>n</i> _GV <sub>DD</sub> = 1.8 V | 1, 5, 9 |

| Local Bus signals                                                                                                                         | 45<br>25                          | OV <sub>DD</sub> = 3.3 V             | 2, 6    |

| eTSEC/10/100 signals                                                                                                                      | 45                                | T/LV <sub>DD</sub> = 3.3 V           | 6       |

|                                                                                                                                           | 30                                | T/LV <sub>DD</sub> = 2.5 V           | 6       |

| DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management,<br>JTAG and Miscellaneous I/O voltage | 45                                | OV <sub>DD</sub> = 3.3 V             | 6       |

| I <sup>2</sup> C                                                                                                                          | 150                               | OV <sub>DD</sub> = 3.3 V             | 7       |

| SRIO, PCI Express                                                                                                                         | 100                               | SV <sub>DD</sub> = 1.1/1.05 V        | 3, 8    |

#### Notes:

- 1. See the DDR Control Driver registers in the MPC8641D reference manual for more information.

- 2. Only the following local bus signals have programmable drive strengths: LALE, LAD[0:31], LDP[0:3], LA[27:31], LCKE, LCS[1:2], LWE[0:3], LGPL1, LGPL2, LGPL3, LGPL4, LGPL5, LCLK[0:2]. The other local bus signals have a fixed drive strength of 45 Ω. See the POR Impedance Control register in the MPC8641D reference manual for more information about local bus signals and their drive strength programmability.

- 3. See Section 17, "Signal Listings," for details on resistor requirements for the calibration of SD*n\_*IMP\_CAL\_TX and SD*n\_*IMP\_CAL\_RX transmit and receive signals.

- 4. Stub Series Terminated Logic (SSTL-25) type pins.

- 5. Stub Series Terminated Logic (SSTL-18) type pins.

- 6. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 7. Open Drain type pins.

- 8. Low Voltage Differential Signaling (LVDS) type pins.

- 9. The drive strength of the DDR interface in half strength mode is at  $T_i = 105C$  and at  $Dn_GV_{DD}$  (min).

# 2.2 Power Up/Down Sequence

The MPC8641 requires its power rails to be applied in a specific sequence in order to ensure proper device operation.

## NOTE

The recommended maximum ramp up time for power supplies is 20 milliseconds.

The chronological order of power up is as follows:

1. All power rails other than DDR I/O ( $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$ ).

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

#### **Electrical Characteristics**

## **NOTE**

There is no required order sequence between the individual rails for this item (# 1). However,  $V_{DD}$ \_PLAT,  $AV_{DD}$ \_PLAT rails must reach 90% of their recommended value before the rail for  $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$  (in next step) reaches 10% of their recommended value.  $AV_{DD}$  type supplies must be delayed with respect to their source supplies by the RC time constant of the PLL filter circuit described in Section 20.2.1, "PLL Power Supply Filtering."

2.  $Dn_GV_{DD}$ ,  $Dn_MV_{REF}$

## NOTE

It is possible to leave the related power supply (Dn\_GV<sub>DD</sub>, Dn\_MV<sub>REF</sub>) turned off at reset for a DDR port that will not be used. Note that these power supplies can only be powered up again at reset for functionality to occur on the DDR port.

3. SYSCLK

The recommended order of power down is as follows:

- 1.  $Dn_GV_{DD}$ ,  $Dn_MV_{REF}$

- 2. All power rails other than DDR I/O (Dn\_GV<sub>DD</sub>, Dn\_MV<sub>REF</sub>).

#### NOTE

SYSCLK may be powered down simultaneous to either of item # 1 or # 2 in the power down sequence. Beyond this, the power supplies may power down simultaneously if the preservation of DDRn memory is not a concern.

See Figure 3 for more details on the Power and Reset Sequencing details.

The maximum power dissipation for individual power supplies of the MPC8641D is shown in Table 5.

Table 5. MPC8641D Individual Supply Maximum Power Dissipation <sup>1</sup>

| Component Description                                 | Supply Voltage<br>(Volts)                                           | Power<br>(Watts) | Notes |

|-------------------------------------------------------|---------------------------------------------------------------------|------------------|-------|

| Per Core voltage Supply                               | V <sub>DD</sub> _Core0/V <sub>DD</sub> _Core1 = 1.1 V @ 1500 MHz    | 21.00            |       |

| Per Core PLL voltage supply                           | AV <sub>DD</sub> _Core0/AV <sub>DD</sub> _Core1 = 1.1 V @ 1500 MHz  | 0.0125           |       |

| Per Core voltage Supply                               | V <sub>DD</sub> _Core0/V <sub>DD</sub> _Core1 = 1.05 V @ 1333 MHz   | 17.00            |       |

| Per Core PLL voltage supply                           | AV <sub>DD</sub> _Core0/AV <sub>DD</sub> _Core1 = 1.05 V @ 1333 MHz | 0.0125           |       |

| Per Core voltage Supply                               | V <sub>DD</sub> _Core0/V <sub>DD</sub> _Core1 = 0.95 V @ 1000 MHz   | 11.50            | 5     |

| Per Core PLL voltage supply                           | AV <sub>DD</sub> _Core0/AV <sub>DD</sub> _Core1 = 0.95 V @ 1000 MHz | 0.0125           | 5     |

| DDR Controller I/O voltage supply                     | Dn_GV <sub>DD</sub> = 2.5 V @ 400 MHz                               | 0.80             | 2     |

|                                                       | D <i>n</i> _GV <sub>DD</sub> = 1.8 V @ 533 MHz                      | 0.68             | 2     |

|                                                       | Dn_GV <sub>DD</sub> = 1.8 V @ 600 MHz                               | 0.77             | 2     |

| 16-bit FIFO @ 200 MHz<br>eTsec 1&2/3&4 Voltage Supply | L/TV <sub>DD</sub> = 3.3 V                                          | 0.11             | 2, 3  |

| non-FIFO eTsecn Voltage Supply                        | L/TV <sub>DD</sub> = 3.3 V                                          | 0.08             | 2     |

| x8 SerDes transceiver Supply                          | SV <sub>DD</sub> = 1.1 V                                            | 0.70             | 2     |

| x8 SerDes I/O Supply                                  | $XV_{DD}$ SRDS $n = 1.1 V$                                          | 0.66             | 2     |

| SerDes PLL voltage supply Port 1 or 2                 | AV <sub>DD</sub> _SRDS1/AV <sub>DD</sub> _SRDS2 = 1.1 V             | 0.10             |       |

| Platform I/O Supply                                   | OV <sub>DD</sub> = 3.3 V                                            | 0.45             | 4     |

| Platform source Supply                                | V <sub>DD</sub> _PLAT = 1.1 V @ 600 MHz                             | 12.00            |       |

| Platform source Supply                                | V <sub>DD</sub> _PLAT = 1.05 Vn @ 500 MHz                           | 9.80             | 5     |

| Platform source Supply                                | V <sub>DD</sub> _PLAT = 1.05 Vn @ 400 MHz                           | 7.70             |       |

| Platform, Local Bus PLL voltage Supply                | AV <sub>DD</sub> _PLAT, AV <sub>DD</sub> _LB = 1.1 V                | 0.0125           |       |

#### Notes:

- 1. This is a maximum power supply number which is provided for power supply and board design information. The numbers are based on 100% bus utilization for each component. The components listed are not expected to have 100% bus usage simultaneously for all components. Actual numbers may vary based on activity.

- 2. Number is based on a per port/interface value.

- 3. This is based on one eTSEC port used. Since 16-bit FIFO mode involves two ports, the number will need to be multiplied by two for the total. The other eTSEC protocols dissipate less than this number per port. Note that the power needs to be multiplied by the number of ports used for the protocol for the total eTSEC port power dissipation.

- 4.This includes Local Bus, DUART, I<sup>2</sup>C, DMA, Multiprocessor Interrupts, System Control & Clocking, Debug, Test, Power management, JTAG and Miscellaneous I/O voltage.

- 5. These power numbers are for Part Number MC8641xxx1000NX only.  $V_{DD}$ \_Core n = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V.

| Parameter/Condition                                              | Symbol                                | Min      | Typical | Max      | Unit | Notes |

|------------------------------------------------------------------|---------------------------------------|----------|---------|----------|------|-------|

| ECn_GTX_CLK125 duty cycle  GMII, TBI  1000Base-T for RGMII, RTBI | <sup>t</sup> G125H <sup>/t</sup> G125 | 45<br>47 | _       | 55<br>53 | %    | 1, 2  |

#### Notes:

- 1. Timing is guaranteed by design and characterization.

- 2. ECn\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. ECn\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

- 3. ±100 ppm tolerance on ECn\_GTX\_CLK125 frequency

## NOTE

The phase between the output clocks TSEC1\_GTX\_CLK and TSEC2\_GTX\_CLK (ports 1 and 2) is no more than 100 ps. The phase between the output clocks TSEC3\_GTX\_CLK and TSEC4\_GTX\_CLK (ports 3 and 4) is no more than 100 ps.

# 4.4 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The MPX platform clock frequency must be considered for proper operation of the high-speed PCI Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the MPX clock frequency must be greater than or equal to:

Note that at MPX = 400 MHz, cfg\_plat\_freq = 0 and at MPX > 400 MHz, cfg\_plat\_freq = 1. Therefore, when operating PCI Express in x8 link width, the MPX platform frequency must be 400 MHz with cfg\_plat\_freq = 0 or greater than or equal to 527 MHz with cfg\_plat\_freq = 1.

For proper Serial RapidIO operation, the MPX clock frequency must be greater than or equal to:

$\underline{2\times(0.8512)\times(\text{Serial RapidIO interface frequency})\times(\text{Serial RapidIO link width})}$

64

# 4.5 Other Input Clocks

For information on the input clocks of other functional blocks of the platform such as SerDes, and eTSEC, see the specific section of this document.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the MPC8641. Note that DDR SDRAM is  $Dn_GV_{DD}(typ) = 2.5 \text{ V}$  and DDR2 SDRAM is  $Dn_GV_{DD}(typ) = 1.8 \text{ V}$ .

## 6.1 DDR SDRAM DC Electrical Characteristics

Table 13 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8641 when Dn  $GV_{DD}(typ) = 1.8 \text{ V}$ .

Table 13. DDR2 SDRAM DC Electrical Characteristics for  $Dn_GV_{DD}(typ) = 1.8 \text{ V}$

| Parameter/Condition                              | Symbol               | Min                                       | Max                                   | Unit | Notes |

|--------------------------------------------------|----------------------|-------------------------------------------|---------------------------------------|------|-------|

| I/O supply voltage                               | Dn_GV <sub>DD</sub>  | 1.71                                      | 1.89                                  | V    | 1     |

| I/O reference voltage                            | Dn_MV <sub>REF</sub> | 0.49 × D <i>n</i> _GV <sub>DD</sub>       | 0.51 × D <i>n</i> _GV <sub>DD</sub>   | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>      | D <i>n</i> _MV <sub>REF</sub> - 0.0       | Dn_MV <sub>REF</sub> + 0.04           | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>      | D <i>n</i> _MV <sub>REF</sub> + 0.1<br>25 | D <i>n</i> _GV <sub>DD</sub> + 0.3    | V    | _     |

| Input low voltage                                | V <sub>IL</sub>      | -0.3                                      | D <i>n</i> _MV <sub>REF</sub> - 0.125 | V    | _     |

| Output leakage current                           | I <sub>OZ</sub>      | -50                                       | 50                                    | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>OH</sub>      | -13.4                                     | _                                     | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>      | 13.4                                      | _                                     | mA   | _     |

#### Notes:

- 1.  $Dn\_GV_{DD}$  is expected to be within 50 mV of the DRAM  $Dn\_GV_{DD}$  at all times.

- 2.  $Dn_MV_{REF}$  is expected to be equal to  $0.5 \times Dn_GV_{DD}$ , and to track  $Dn_GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $Dn_MV_{REF}$  may not exceed  $\pm 2\%$  of the DC value.

- 3.  $V_{TT}$  is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to  $Dn_MV_{REF}$ . This rail should track variations in the DC level of  $Dn_MV_{REF}$ .

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  Dn\_GV<sub>DD</sub>.

Table 14 provides the DDR2 capacitance when  $Dn_GV_{DD}(typ) = 1.8 \text{ V}$ .

Table 14. DDR2 SDRAM Capacitance for Dn\_GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $Dn_GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = Dn_GV_{DD}/2$ ,  $V_{OUT}/2$

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

Table 24. GMII, MII, RMII, TBI and FIFO DC Electrical Characteristics (continued)

| Parameter                                 | Symbol          | Min  | Max | Unit | Notes |

|-------------------------------------------|-----------------|------|-----|------|-------|

| Input low current (V <sub>IN</sub> = GND) | I <sub>IL</sub> | -600 | _   | μΑ   | 3     |

## Notes:

Table 25. GMII, RGMII, RTBI, TBI and FIFO DC Electrical Characteristics

| Parameters                                                      | Symbol                             | Min   | Max   | Unit | Notes  |

|-----------------------------------------------------------------|------------------------------------|-------|-------|------|--------|

| Supply voltage 2.5 V                                            | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.375 | 2.625 | V    | 1,2    |

| Output high voltage $(LV_{DD}/TV_{DD} = Min, I_{OH} = -1.0 mA)$ | V <sub>OH</sub>                    | 2.00  | _     | V    | _      |

| Output low voltage $(LV_{DD}/TV_{DD} = Min, I_{OL} = 1.0 mA)$   | V <sub>OL</sub>                    | _     | 0.40  | V    | _      |

| Input high voltage                                              | V <sub>IH</sub>                    | 1.70  | _     | V    | _      |

| Input low voltage                                               | V <sub>IL</sub>                    | _     | 0.90  | V    | _      |

| Input high current $(V_{IN} = LV_{DD}, V_{IN} = TV_{DD})$       | I <sub>IH</sub>                    | _     | 10    | μА   | 1, 2,3 |

| Input low current (V <sub>IN</sub> = GND)                       | I <sub>IL</sub>                    | -15   | _     | μА   | 3      |

#### Note:

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSECn's TSECn\_TX\_CLK, while the receive clock must be applied to pin TSECn\_RX\_CLK. The eTSEC internally uses the transmit

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>&</sup>lt;sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4.

$<sup>^3</sup>$  The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

<sup>&</sup>lt;sup>1</sup> LV<sub>DD</sub> supports eTSECs 1 and 2.

<sup>&</sup>lt;sup>2</sup> TV<sub>DD</sub> supports eTSECs 3 and 4.

$<sup>^3</sup>$  Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbols referenced in Table 1 and Table 2.

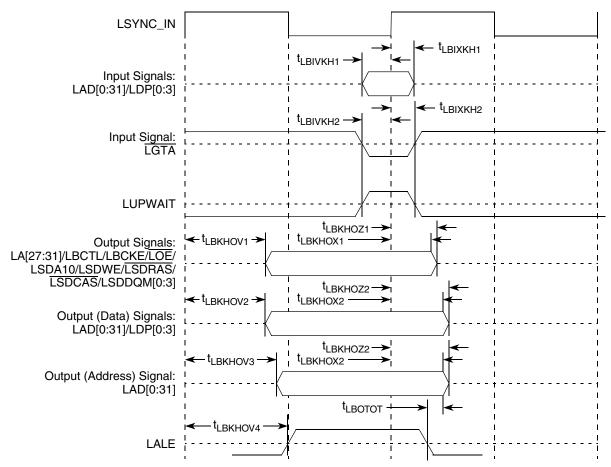

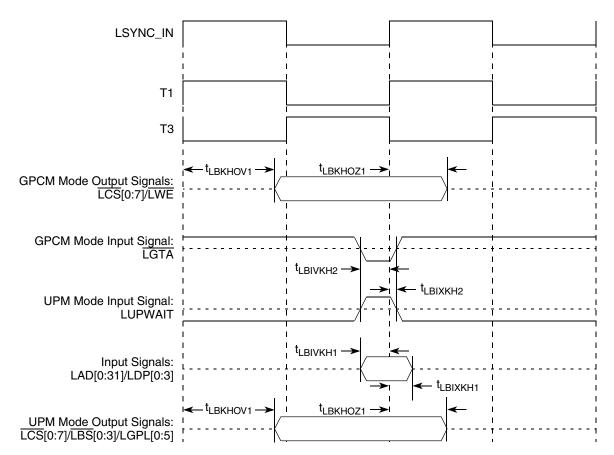

Figure 26 to Figure 31 show the local bus signals.

Figure 26. Local Bus Signals (PLL Enabled)

#### NOTE

PLL bypass mode is recommended when LBIU frequency is at or below 83 MHz. When LBIU operates above 83 MHz, LBIU PLL is recommended to be enabled.

Table 42 describes the general timing parameters of the local bus interface at  $OV_{DD} = 3.3 \text{ V}$  with PLL bypassed.

Symbol 1 **Parameter** Min Max Unit **Notes** Local bus cycle time 12 2  $t_{LBK}$ ns Local bus duty cycle 45 % 55 t<sub>LBKH</sub>/t<sub>LBK</sub> Internal launch/capture clock to LCLK delay 2.3 3.9 8 ns t<sub>LBKHKT</sub> Input setup to local bus clock (except LGTA/LUPWAIT) 5.7 4, 5 ns t<sub>LBIVKH1</sub> LGTA/LUPWAIT input setup to local bus clock 4, 5 t<sub>LBIVKL2</sub> 5.6 ns Input hold from local bus clock (except LGTA/LUPWAIT) 4, 5 -1.8t<sub>LBIXKH1</sub> ns

Table 42. Local Bus Timing Parameters—PLL Bypassed

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

#### **Local Bus**

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (clock ratio of 4) (PLL Enabled)

## Table 44. JTAG AC Timing Specifications (Independent of SYSCLK) <sup>1</sup> (continued)

At recommended operating conditions (see Table 3).

| Parameter                                                              | Symbol <sup>2</sup>                        | Min      | Max     | Unit | Notes |

|------------------------------------------------------------------------|--------------------------------------------|----------|---------|------|-------|

| Output hold times:  Boundary-scan data TDO                             | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 30<br>30 | _<br>_  | ns   | 5, 6  |

| JTAG external clock to output high impedance:  Boundary-scan data  TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3<br>3   | 19<br>9 | ns   | 5, 6  |

#### Notes:

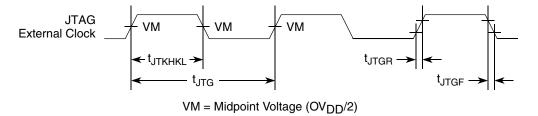

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question.

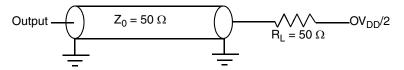

The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 32).

Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 32 provides the AC test load for TDO and the boundary-scan outputs.

Figure 32. AC Test Load for the JTAG Interface

Figure 33 provides the JTAG clock input timing diagram.

Figure 33. JTAG Clock Input Timing Diagram

Table 49. Differential Transmitter (TX) Output Specifications (continued)

| Symbol                                       | Parameter                                                                                    | Min   | Nom | Max  | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|----------------------------------------------------------------------------------------------|-------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>TX-EYE</sub>                          | Minimum TX Eye<br>Width                                                                      | 0.70  | _   | _    | UI    | The maximum Transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI. See Notes 2 and 3.                                                                                                                                                                                                                                                                                                                                                         |

| T <sub>TX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |       |     | 0.15 | UI    | Jitter is defined as the measurement variation of the crossing points ( $V_{TX-DIFFp-p}=0$ V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2 and 3.                                                                                                          |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | D+/D-TX Output<br>Rise/Fall Time                                                             | 0.125 | _   | _    | UI    | See Notes 2 and 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>TX-CM-ACp</sub>                       | RMS AC Peak<br>Common Mode<br>Output Voltage                                                 | _     | _   | 20   | mV    | $\begin{split} &V_{TX\text{-CM-ACp}} = \text{RMS}( V_{TXD+} + V_{TXD-} /2 - V_{TX\text{-CM-DC}}) \\ &V_{TX\text{-CM-DC}} = \text{DC}_{(avg)} \text{ of }  V_{TX\text{-D+}} + V_{TX\text{-D-}} /2 \\ &\text{See Note 2} \end{split}$                                                                                                                                                                                                                                        |

| V <sub>TX-CM-DC-ACTIVE-</sub> IDLE-DELTA     | Absolute Delta of<br>DC Common<br>Mode Voltage<br>During L0 and<br>Electrical Idle           | 0     | _   | 100  | mV    | $\begin{split} & V_{TX\text{-}CM\text{-}DC}\text{ (during L0)} - V_{TX\text{-}CM\text{-}Idle\text{-}DC}\text{ (During Electrical Inlet)}  <= &100\text{ mV}\\ &V_{TX\text{-}CM\text{-}DC} = &DC_{(avg)}\text{ of } V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2\text{ [L0]}\\ &V_{TX\text{-}CM\text{-}Idle\text{-}DC} = &DC_{(avg)}\text{ of } V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2\\ &[\text{Electrical Idle}]\\ &\text{See Note 2}. \end{split}$ |

| V <sub>TX-CM-DC-LINE-DELTA</sub>             | Absolute Delta of<br>DC Common<br>Mode between<br>D+ and D-                                  | 0     | _   | 25   | mV    | $\begin{aligned} & V_{TX\text{-}CM\text{-}DC\text{-}D\text{+}} - V_{TX\text{-}CM\text{-}DC\text{-}D\text{-}}  <= 25 \text{ mV} \\ &V_{TX\text{-}CM\text{-}DC\text{-}D\text{+}} = DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{+}}  \\ &V_{TX\text{-}CM\text{-}DC\text{-}D\text{-}} = DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{-}}  \\ &\text{See Note 2}. \end{aligned}$                                                                                                 |

| V <sub>TX-IDLE-DIFFp</sub>                   | Electrical Idle<br>differential Peak<br>Output Voltage                                       | 0     | _   | 20   | mV    | $V_{TX-IDLE-DIFFp} = IV_{TX-IDLE-D+} - V_{TX-IDLE-D-}I \le 20 \text{ mV}$<br>See Note 2.                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>TX-RCV-DETECT</sub>                   | The amount of voltage change allowed during Receiver Detection                               | _     | _   | 600  | mV    | The total amount of voltage change that a transmitter can apply to sense whether a low impedance Receiver is present. See Note 6.                                                                                                                                                                                                                                                                                                                                          |

| V <sub>TX-DC-CM</sub>                        | The TX DC<br>Common Mode<br>Voltage                                                          | 0     | _   | 3.6  | ٧     | The allowed DC Common Mode voltage under any conditions. See Note 6.                                                                                                                                                                                                                                                                                                                                                                                                       |

| I <sub>TX-SHORT</sub>                        | TX Short Circuit<br>Current Limit                                                            | _     | _   | 90   | mA    | The total current the Transmitter can provide when shorted to its ground                                                                                                                                                                                                                                                                                                                                                                                                   |

| T <sub>TX-IDLE-MIN</sub>                     | Minimum time<br>spent in<br>Electrical Idle                                                  | 50    | _   | _    | UI    | Minimum time a Transmitter must be in Electrical Idle Utilized by the Receiver to start looking for an Electrical Idle Exit after successfully receiving an Electrical Idle ordered set                                                                                                                                                                                                                                                                                    |

#### **PCI Express**

# 14.4.3 Differential Receiver (RX) Input Specifications

Table 50 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

Table 50. Differential Receiver (RX) Input Specifications

| Symbol                                       | Parameter                                                                                    | Min    | Nom | Max    | Units | Comments                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--------|-----|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit Interval                                                                                | 399.88 | 400 | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1.                                                                                                                                                                                                                                                            |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>Peak-to-Peak<br>Output Voltage                                               | 0.175  | _   | _      | V     | $V_{RX-DIFFp-p} = 2*IV_{RX-D+} - V_{RX-D-}I$<br>See Note 2.                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>Receiver Eye<br>Width                                                             | 0.4    | _   | _      | UI    | The maximum interconnect media and Transmitter jitter that can be tolerated by the Receiver can be derived as T <sub>RX-MAX-JITTER</sub> = 1 - T <sub>RX-EYE</sub> = 0.6 UI. See Notes 2 and 3.                                                                                                                                                                        |

| T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum<br>deviation from<br>the median. |        | _   | 0.3    | UI    | Jitter is defined as the measurement variation of the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2, 3 and 7. |

| V <sub>RX-CM-ACp</sub>                       | AC Peak<br>Common Mode<br>Input Voltage                                                      | _      | _   | 150    | mV    | $\begin{aligned} &V_{\text{RX-CM-ACp}} =  V_{\text{RXD+}} - V_{\text{RXD-}} /2 - V_{\text{RX-CM-DC}} \\ &V_{\text{RX-CM-DC}} = DC_{(\text{avg})} \text{ of }  V_{\text{RX-D+}} - V_{\text{RX-D-}} /2 \\ &\text{See Note 2} \end{aligned}$                                                                                                                              |

| RL <sub>RX-DIFF</sub>                        | Differential<br>Return Loss                                                                  | 15     | _   | _      | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at +300 mV and -300 mV, respectively. See Note 4                                                                                                                                                                                                                                                      |

| RL <sub>RX-CM</sub>                          | Common Mode<br>Return Loss                                                                   | 6      | _   | _      | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at 0 V. See Note 4                                                                                                                                                                                                                                                                                    |

| Z <sub>RX-DIFF-DC</sub>                      | DC Differential Input Impedance                                                              | 80     | 100 | 120    | Ω     | RX DC Differential mode impedance. See Note 5                                                                                                                                                                                                                                                                                                                          |

| Z <sub>RX-DC</sub>                           | DC Input<br>Impedance                                                                        | 40     | 50  | 60     | Ω     | Required RX D+ as well as D– DC Impedance (50 ± 20% tolerance). See Notes 2 and 5.                                                                                                                                                                                                                                                                                     |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Powered Down<br>DC Input<br>Impedance                                                        | 200 k  | _   | _      | Ω     | Required RX D+ as well as D– DC Impedance when the Receiver terminations do not have power. See Note 6.                                                                                                                                                                                                                                                                |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>             | Electrical Idle<br>Detect Threshold                                                          | 65     | _   | _      | mV    | $V_{RX-IDLE-DET-DIFFp-p} = 2*IV_{RX-D+} - V_{RX-D-}I$<br>Measured at the package pins of the Receiver                                                                                                                                                                                                                                                                  |

## **Signal Listings**

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>              | Package Pin Number                                | Pin Type                           | Power Supply     | Notes            |  |  |

|--------------------------------|---------------------------------------------------|------------------------------------|------------------|------------------|--|--|

| D1_MDVAL/LB_DVAL               | J16                                               | 0                                  | OV <sub>DD</sub> | 10               |  |  |

| D2_MDVAL                       | D19                                               | 0                                  | OV <sub>DD</sub> | _                |  |  |

|                                | Power Management S                                | ignals <sup>5</sup>                |                  |                  |  |  |

| ASLEEP                         | C19                                               | 0                                  | OV <sub>DD</sub> | _                |  |  |

|                                | System Clocking Sig                               | ınals <sup>5</sup>                 |                  |                  |  |  |

| SYSCLK                         | G16                                               | ı                                  | OV <sub>DD</sub> | _                |  |  |

| RTC                            | K17                                               | I                                  | OV <sub>DD</sub> | 32               |  |  |

| CLK_OUT                        | B16                                               | 0                                  | OV <sub>DD</sub> | 23               |  |  |

|                                | Test Signals <sup>5</sup>                         | 1                                  | 1                |                  |  |  |

| LSSD_MODE                      | C18                                               | ı                                  | OV <sub>DD</sub> | 26               |  |  |

| TEST_MODE[0:3]                 | C16, E17, D18, D16                                | ı                                  | OV <sub>DD</sub> | 26               |  |  |

|                                | JTAG Signals <sup>5</sup>                         | 1                                  | 1                |                  |  |  |

| TCK                            | H18                                               | I                                  | OV <sub>DD</sub> | _                |  |  |

| TDI                            | J18                                               | I                                  | OV <sub>DD</sub> | 24               |  |  |

| TDO                            | G18                                               | 0                                  | OV <sub>DD</sub> | 23               |  |  |

| TMS                            | F18                                               | I                                  | OV <sub>DD</sub> | 24               |  |  |

| TRST                           | A17                                               | ı                                  | OV <sub>DD</sub> | 24               |  |  |

|                                | Miscellaneous <sup>5</sup>                        | ;                                  | 1                |                  |  |  |

| Spare                          | J17                                               | _                                  | _                | 13               |  |  |

| GPOUT[0:7]/<br>TSEC1_TXD[0:7]  | AF25, AC23, AG24, AG23, AE24, AE23, AE22, AD22    | 0                                  | OV <sub>DD</sub> | 6, 10            |  |  |

| GPIN[0:7]/<br>TSEC1_RXD[0:7]   | AL25, AL24, AK26, AK25, AM26, AF26,<br>AH24, AG25 | I                                  | OV <sub>DD</sub> | 10               |  |  |

| GPOUT[8:15]/<br>TSEC2_TXD[0:7] | AB20, AJ23, AJ22, AD19, AH23, AH21,<br>AG22, AG21 | 0                                  | OV <sub>DD</sub> | 10               |  |  |

| GPIN[8:15]/<br>TSEC2_RXD[0:7]  | AL22, AK22, AM21, AH20, AG20, AF20,<br>AF23, AF22 | ı                                  | OV <sub>DD</sub> | 10               |  |  |

|                                | Additional Analog Signals                         |                                    |                  |                  |  |  |

| TEMP_ANODE                     | AA11                                              | Thermal                            | _                | _                |  |  |

| TEMP_CATHODE                   | Y11                                               | Thermal                            | _                | _                |  |  |

|                                | Sense, Power and GND                              | Signals                            | · '              |                  |  |  |

| SENSEV <sub>DD</sub> Core0     | M14                                               | V <sub>DD</sub> _Core0 sensing pin | _                | 31               |  |  |

| SENSEV <sub>DD</sub> Core1     | U20                                               | V <sub>DD</sub> _Core1 sensing pin | _                | 12,31, <i>S1</i> |  |  |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>           | Package Pin Number                                                                                                                                                  | Pin Type                                                                                                                                                                                                | Power Supply                                       | Notes             |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|

| SENSEV <sub>SS</sub> _Core0 | P14                                                                                                                                                                 | Core0 GND sensing pin                                                                                                                                                                                   | _                                                  | 31                |

| SENSEV <sub>SS</sub> _Core1 | V20                                                                                                                                                                 | Core1 GND sensing pin                                                                                                                                                                                   | _                                                  | 12, 31, <i>S3</i> |

| SENSEV <sub>DD</sub> PLAT   | N18                                                                                                                                                                 | V <sub>DD</sub> PLAT sensing pin                                                                                                                                                                        | _                                                  | 28                |

| SENSEV <sub>SS</sub> _PLAT  | P18                                                                                                                                                                 | Platform GND sensing pin                                                                                                                                                                                | _                                                  | 29                |

| D1_GV <sub>DD</sub>         | B11, B14, D10, D13, F9, F12, H8, H11,<br>H14, K10, K13, L8, P8, R6, U8, V6, W10,<br>Y8, AA6, AB10, AC8, AD12, AE10, AF8,<br>AG12, AH10, AJ8, AJ14, AK12, AL10, AL16 | SDRAM 1 I/O<br>supply                                                                                                                                                                                   | D1_GV <sub>DD</sub><br>2.5 - DDR<br>1.8 DDR2       |                   |

| D2_GV <sub>DD</sub>         | B2, B5, B8, D4, D7, E2, F6, G4, H2, J6, K4, L2, M6, N4, P2, T4, U2, W4, Y2, AB4, AC2, AD6, AE4, AF2, AG6, AH4, AJ2, AK6, AL4, AM2                                   | SDRAM 2 I/O<br>supply                                                                                                                                                                                   | D2_GV <sub>DD</sub><br>2.5 V - DDR<br>1.8 V - DDR2 |                   |

| OV <sub>DD</sub>            | B22, B25, B28, D17, D24, D27, F19, F22, F26, F29, G17, H21, H24, K19, K23, M21, AM30                                                                                | DUART, Local<br>Bus, DMA,<br>Multiprocessor<br>Interrupts,<br>System Control<br>& Clocking,<br>Debug, Test,<br>JTAG, Power<br>management,<br>I <sup>2</sup> C, JTAG and<br>Miscellaneous<br>I/O voltage | OV <sub>DD</sub><br>3.3 V                          |                   |

| LV <sub>DD</sub>            | AC20, AD23, AH22                                                                                                                                                    | TSEC1 and<br>TSEC2 I/O<br>voltage                                                                                                                                                                       | LV <sub>DD</sub><br>2.5/3.3 V                      | _                 |

| TV <sub>DD</sub>            | AC17, AG18, AK20                                                                                                                                                    | TSEC3 and<br>TSEC4 I/O<br>voltage                                                                                                                                                                       | TV <sub>DD</sub><br>2.5/3.3 V                      | _                 |

| SV <sub>DD</sub>            | H31, J29, K28, K32, L30, M28, M31, N29, R30, T31, U29, V32, W30, Y31, AA29, AB32, AC30, AD31, AE29, AG30, AH31, AJ29, AK32, AL30, AM31                              | Transceiver<br>Power Supply<br>SerDes                                                                                                                                                                   | SV <sub>DD</sub><br>1.05/1.1 V                     | _                 |

| XV <sub>DD</sub> _SRDS1     | K26, L24, M27, N25, P26, R24, R28, T27, U25, V26                                                                                                                    | Serial I/O<br>Power Supply<br>for SerDes<br>Port 1                                                                                                                                                      | XV <sub>DD</sub> _SRDS1<br>1.05/1.1 V              | _                 |

## **Signal Listings**

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>                         | Package Pin Number                                                                                                                                             | Pin Type | Power Supply     | Notes |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| TSEC3_TXD[6:7]/<br>cfg_tsec3_prtcl[0:1]   | AL20, AL19                                                                                                                                                     | _        | LV <sub>DD</sub> | _     |

| TSEC4_TXD[0:3]/<br>cfg_io_ports[0:3]      | AC18, AC16, AD18, AD17                                                                                                                                         | _        | LV <sub>DD</sub> | _     |

| TSEC4_TXD[5]/<br>cfg_tsec4_reduce         | AB18                                                                                                                                                           | _        | LV <sub>DD</sub> | _     |

| TSEC4_TXD[6:7]/<br>cfg_tsec4_prtcl[0:1]   | AB17, AB16                                                                                                                                                     | _        | LV <sub>DD</sub> | _     |

| LAD[0:31]/<br>cfg_gpporcr[0:31]           | A30, E29, C29, D28, D29, H25, B29, A29, C28, L22, M22, A28, C27, H26, G26, B27, B26, A27, E27, G25, D26, E26, G24, F27, A26, A25, C25, H23, K22, D25, F25, H22 | _        | OV <sub>DD</sub> | _     |

| TWE[0]/<br>cfg_cpu_boot                   | E21                                                                                                                                                            | _        | OV <sub>DD</sub> | _     |

| TWE[1]/ cfg_rio_sys_size                  | F21                                                                                                                                                            | _        | OV <sub>DD</sub> | _     |

| LWE[2:3]/<br>cfg_host_agt[0:1]            | D22, E20                                                                                                                                                       | _        | OV <sub>DD</sub> | _     |

| LDP[0:3], LA[27] / cfg_core_pll[0:4]      | A24, E24, C24, B24,<br>J21                                                                                                                                     | _        | OV <sub>DD</sub> | 22    |

| LA[28:31]/<br>cfg_sys_pll[0:3]            | K21, G22, F24, G21                                                                                                                                             | _        | OV <sub>DD</sub> | 22    |

| LGPL[3],<br>LGPL[5]/<br>cfg_boot_seq[0:1] | K20,<br>J19                                                                                                                                                    | _        | OV <sub>DD</sub> | -     |

| D1_MSRCID[0]/<br>cfg_mem_debug            | F15                                                                                                                                                            | _        | OV <sub>DD</sub> | _     |

| D1_MSRCID[1]/<br>cfg_ddr_debug            | K15                                                                                                                                                            | _        | $OV_DD$          | _     |

|                            |                           | ocessor Core<br>uency |     |       |

|----------------------------|---------------------------|-----------------------|-----|-------|

| Characteristic             | 1000, 1250, 1333, 1500MHz |                       |     | Notes |

|                            | Min                       | Max                   |     |       |

| Memory bus clock frequency | 200                       | 300                   | MHz | 1, 2  |

#### Notes:

- Caution: The MPX clock to SYSCLK ratio and e600 core to MPX clock ratio settings must be chosen such that the resulting SYSCLK frequency, e600 (core) frequency, and MPX clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 18.2, "MPX to SYSCLK PLL Ratio," and Section 18.3, "e600 to MPX clock PLL Ratio," for ratio settings.

- 2. The memory bus clock speed is half the DDR/DDR2 data rate, hence, half the MPX clock frequency.

Table 66. Platform/MPX bus Clocking Specifications

|                                  |                           | ocessor Core<br>Jency | Unit |       |

|----------------------------------|---------------------------|-----------------------|------|-------|

| Characteristic                   | 1000, 1250, 1333, 1500MHz |                       |      | Notes |

|                                  | Min                       | Max                   |      |       |

| Platform/MPX bus clock frequency | 400                       | 500-600               | MHz  | 1, 2  |

#### Notes:

- Caution: The MPX clock to SYSCLK ratio and e600 core to MPX clock ratio settings must be chosen such that the resulting SYSCLK frequency, e600 (core) frequency, and MPX clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 18.2, "MPX to SYSCLK PLL Ratio," and Section 18.3, "e600 to MPX clock PLL Ratio," for ratio settings.

- 2. Platform/MPX frequencies between 400 and 500 MHz are not supported.

**Table 67. Local Bus Clocking Specifications**

|                                                  |                           | ocessor Core<br>uency |      |       |

|--------------------------------------------------|---------------------------|-----------------------|------|-------|

| Characteristic                                   | 1000, 1250, 1333, 1500MHz |                       | Unit | Notes |

|                                                  | Min                       | Max                   |      |       |

| Local bus clock speed (for Local Bus Controller) | 25                        | 133                   | MHz  | 1     |

#### Notes:

1. The Local bus clock speed on LCLK[0:2] is determined by MPX clock divided by the Local Bus PLL ratio programmed in LCRR[CLKDIV]. See the reference manual for the MPC8641D for more information on this.

## 18.2 MPX to SYSCLK PLL Ratio

The MPX clock is the clock that drives the MPX bus, and is also called the platform clock. The frequency of the MPX is set using the following reset signals, as shown in Table 68:

SYSCLK input signal

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

example, assuming a  $T_i$  of 30°C, a  $T_r$  of 5°C, a package  $R_{\theta JC}$  = 0.1, and a typical power consumption ( $P_d$ ) of 43.4 W, the following expression for  $T_i$  is obtained:

Die-junction temperature:  $T_i = 30^{\circ}\text{C} + 5^{\circ}\text{C} + (0.1^{\circ}\text{C/W} + 0.2^{\circ}\text{C/W} + \theta_{sa}) \times 43.4 \text{ W}$

For this example, a  $R_{\theta sa}$  value of 1.32 °C/W or less is required to maintain the die junction temperature below the maximum value of Table 2.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature—airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, and so on.

Due to the complexity and variety of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board as well as system-level designs.

For system thermal modeling, the MPC8641 thermal model is shown in Figure 62. Four cuboids are used to represent this device. The die is modeled as 12.4x15.3 mm at a thickness of 0.86 mm. See Section 3, "Power Characteristics" for power dissipation details. The substrate is modeled as a single block 33x3x1.2 mm with orthotropic conductivity: 13.5 W/(m • K) in the xy-plane and 5.3 W/(m • K) in the z-direction. The die is centered on the substrate. The bump/underfill layer is modeled as a collapsed thermal resistance between the die and substrate with a conductivity of 5.3 W/(m • K) in the thickness dimension of 0.07 mm. Because the bump/underfill is modeled with zero physical dimension (collapsed height), the die thickness was slightly enlarged to provide the correct height. The C5 solder layer is modeled as a cuboid with dimensions 33x33x0.4 mm and orthotropic thermal conductivity of 0.034 W/(m • K) in the xy-plane and 9.6 W/(m • K) in the z-direction. An LGA solder layer would be modeled as a collapsed thermal resistance with thermal conductivity of 9.6W/(m • K) and an effective height of 0.1 mm. The thermal model uses approximate dimensions to reduce grid. Please refer to the case outline for actual dimensions.

For other pin pull-up or pull-down recommendations of signals, please see Section 17, "Signal Listings."

# 20.7 Output Buffer DC Impedance

The MPC8641 drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

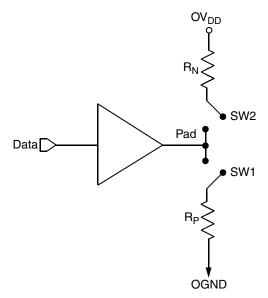

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 66). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 66. Driver Impedance Measurement

Table 73 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | DUART, Control,<br>Configuration, Power<br>Management | PCI<br>Express | DDR DRAM  | Symbol | Unit |

|----------------|-------------------------------------------------------|----------------|-----------|--------|------|

| R <sub>N</sub> | 43 Target                                             | 25 Target      | 20 Target | $Z_0$  | W    |

| R <sub>P</sub> | 43 Target                                             | 25 Target      | 20 Target | $Z_0$  | W    |

**Table 73. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105$ °C.

#### Notes:

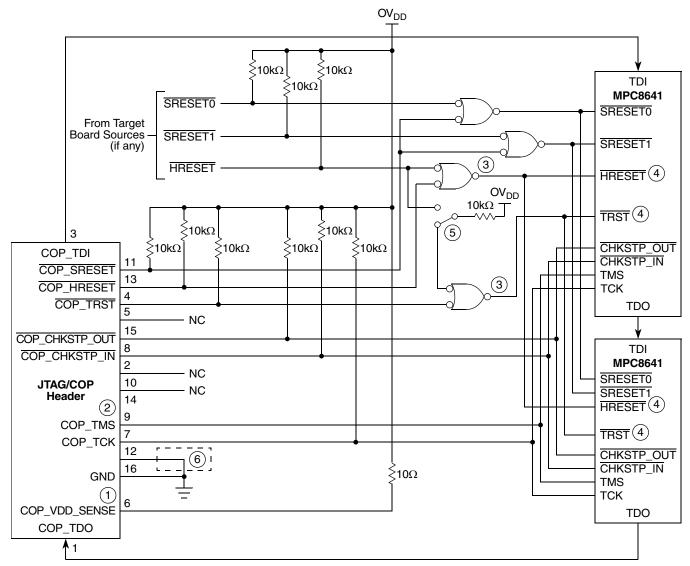

- 1. Populate this with a  $10\Omega$  resistor for short circuit/current-limiting protection.

- 2. KEY location; pin 14 is not physically present on the COP header.

- 3. Use a AND gate with sufficient drive strength to drive two inputs.

- 4. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown above.

- 5. This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 6. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

Figure 69. JTAG/COP Interface Connection for Multiple MPC8641 Devices in Daisy Chain Configuration

Table 75 shows the parts that are available for ordering and their operating conditions.

**Table 75. Part Offerings and Operating Conditions**

| Part Offerings <sup>1</sup> | Operating Conditions                                                              |

|-----------------------------|-----------------------------------------------------------------------------------|

| MC8641Dxx1500KX             | Dual core Max CPU speed = 1500 MHz, Max DDR = 600 MHz Core Voltage = 1.1 volts    |

| MC8641Dxx1333JX             | Dual core Max CPU speed = 1333 MHz, Max DDR = 533 MHz Core Voltage = 1.05 volts   |

| MC8641Dxx1250HX             | Dual core Max CPU speed = 1250 MHz, Max DDR = 500 MHz Core Voltage = 1.05 volts   |

| MC8641Dxx1000GX             | Dual core Max CPU speed = 1000 MHz, Max DDR = 400 MHz Core Voltage = 1.05 volts   |

| MC8641Dxx1000NX             | Dual core MAX CPU speed = 1000 MHz, MAX DDR = 500 MHz Core Voltage = 0.95 volts   |

| MC8641xx1500KX              | Single core Max CPU speed = 1500 MHz, Max DDR = 600 MHz Core Voltage = 1.1 volts  |

| MC8641xx1333JX              | Single core Max CPU speed = 1333 MHz, Max DDR = 533 MHz Core Voltage = 1.05 volts |

| MC8641xx1250HX              | Single core Max CPU speed = 1250 MHz, Max DDR = 500 MHz Core Voltage = 1.05 volts |

| MC8641xx1000HX              | Single core Max CPU speed = 1000 MHz, Max DDR = 400 MHz Core Voltage = 1.05 volts |

| MC8641xx1000NX              | Single core Max CPU speed = 1000 MHz, Max DDR = 500 MHz Core Voltage = 0.95 volts |

Note that the "xx" in the part marking represents the package option. The upper case "X" represents the revision letter. For more information see Table 74.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3