#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e600                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 994-BCBGA, FCCBGA                                                      |

| Supplier Device Package         | 994-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641hx1000gb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. Recommended Operating Conditions (continued)

| Characteristic             | Symbol         | Recommended<br>Value | Unit | Notes |

|----------------------------|----------------|----------------------|------|-------|

| Junction temperature range | Τ <sub>J</sub> | 0 to 105             | °C   | —     |

Notes:

- 1. Core 1 characteristics apply only to MPC8641D

- 2. If two separate power supplies are used for V<sub>DD</sub>\_Core0 and V<sub>DD</sub>\_Core1, they must be at the same nominal voltage and the individual power supplies must be tracked and kept within 100 mV of each other during normal run time.

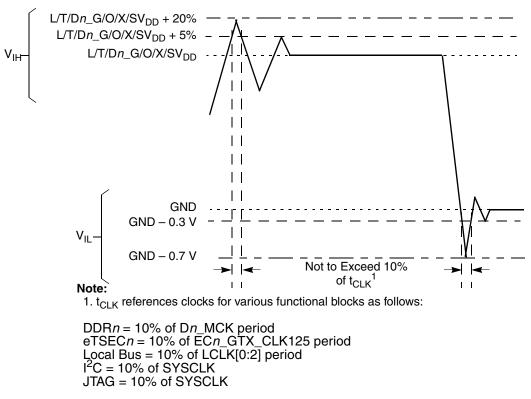

- 3. Caution: Dn\_MV<sub>IN</sub> must meet the overshoot/undershoot requirements for Dn\_GV<sub>DD</sub> as shown in Figure 2.

- 4. Caution: L/TV<sub>IN</sub> must meet the overshoot/undershoot requirements for L/TV<sub>DD</sub> as shown in Figure 2 during regular run time.

- 5. Caution: OV<sub>IN</sub> must meet the overshoot/undershoot requirements for OV<sub>DD</sub> as shown in Figure 2 during regular run time.

- 6. Timing limitations for M,L,T,O)V<sub>IN</sub> and Dn\_MV<sub>REF</sub> during regular run time is provided in Figure 2

- 7. Applies to devices marked with a core frequency of 1333 MHz and below. Refer to Table 74 Part Numbering Nomenclature to determine if the device has been marked for a core frequency of 1333 MHz and below.

- 8. Applies to devices marked with a core frequency above 1333 MHz. Refer to Table 74 Part Numbering Nomenclature to determine if the device has been marked for a core frequency above 1333 MHz.

- 9. The 2.5 V  $\pm$  125 mV range is for DDR and 1.8 V  $\pm$  90 mV range is for DDR2.

- 10. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 11. The PCI Express interface of the device is expected to receive signals from 0.175 to 1.2 V. For more information refer to Section 14.4.3, "Differential Receiver (RX) Input Specifications."

- 12. Applies to Part Number MC8641xxx1000NX only.  $V_{DD}$ \_Core n = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V devices. Refer to Table 74 Part Numbering Nomenclature to determine if the device has been marked for  $V_{DD}$ \_Core n = 0.95 V.

- 13. This voltage is the input to the filter discussed in Section 20.2, "Power Supply Design and Sequencing," and not necessarily the voltage at the AV<sub>DD</sub>\_Core*n* pin, which may be reduced from V<sub>DD</sub>\_Core*n* by the filter.

#### Electrical Characteristics

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8641.

Figure 2. Overshoot/Undershoot Voltage for Dn\_M/O/L/TV<sub>IN</sub>

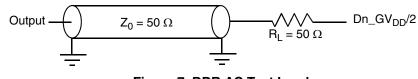

The MPC8641 core voltage must always be provided at nominal  $V_{DD}$ \_Core*n* (See Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $L/TV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced to each externally supplied  $Dn_MV_{REF}$  signal (nominally set to  $Dn_GV_{DD}/2$ ) as is appropriate for the (SSTL-18 and SSTL-25) electrical signaling standards.

# 6.2 DDR SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

# 6.2.1 DDR SDRAM Input AC Timing Specifications

Table 18 provides the input AC timing specifications for the DDR2 SDRAM when  $Dn GV_{DD}(typ)=1.8 V$ .

# Table 18. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions

| Parameter                                        | Symbol | Min                                                                          | Мах                                                                          | Unit | Notes |

|--------------------------------------------------|--------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|-------|

| AC input low voltage<br>400, 533 MHz<br>600 MHz  |        | _                                                                            | D <i>n_</i> MV <sub>REF</sub> – 0.25<br>D <i>n_</i> MV <sub>REF</sub> – 0.20 | V    | _     |

| AC input high voltage<br>400, 533 MHz<br>600 MHz |        | D <i>n_</i> MV <sub>REF</sub> + 0.25<br>D <i>n_</i> MV <sub>REF</sub> + 0.20 | _                                                                            | V    | _     |

Table 19 provides the input AC timing specifications for the DDR SDRAM when  $Dn_GV_{DD}(typ)=2.5$  V.

Table 19. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions.

| Parameter             | Symbol          | Min                                  | Мах                                  | Unit | Notes |

|-----------------------|-----------------|--------------------------------------|--------------------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                                    | D <i>n</i> _MV <sub>REF</sub> – 0.31 | V    | _     |

| AC input high voltage | V <sub>IH</sub> | D <i>n</i> _MV <sub>REF</sub> + 0.31 | _                                    | V    | _     |

Table 20 provides the input AC timing specifications for the DDR SDRAM interface.

## Table 20. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions.

| Parameter                            | Symbol              | Min  | Мах | Unit | Notes |

|--------------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for<br>MDQS—MDQ/MECC | <sup>t</sup> CISKEW | —    |     | ps   | 1, 2  |

| 600 MHz                              | —                   | -240 | 240 | —    | 3     |

| 533 MHz                              | —                   | -300 | 300 | —    | 3     |

| 400 MHz                              | —                   | -365 | 365 | —    |       |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> =+/-(T/4 - abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

- 3. Maximum DDR1 frequency is 400 MHz.

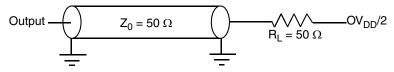

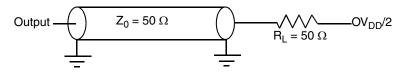

Figure 7 provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8641.

# 7.1 DUART DC Electrical Characteristics

Table 22 provides the DC electrical characteristics for the DUART interface.

| Parameter                                                                    | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                                     | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                      | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current<br>$(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$            | I <sub>IN</sub> | _                      | ±5                     | μΑ   |

| High-level output voltage $(OV_{DD} = min, I_{OH} = -100 \ \mu A)$           | V <sub>OH</sub> | OV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage<br>(OV <sub>DD</sub> = min, $I_{OL}$ = 100 $\mu$ A) | V <sub>OL</sub> | _                      | 0.2                    | V    |

# Table 22. DUART DC Electrical Characteristics

## Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 7.2 DUART AC Electrical Specifications

Table 23 provides the AC timing parameters for the DUART interface.

# Table 23. DUART AC Timing Specifications

| Parameter         | Value               | Unit | Notes |

|-------------------|---------------------|------|-------|

| Minimum baud rate | MPX clock/1,048,576 | baud | 1,2   |

| Maximum baud rate | MPX clock/16        | baud | 1,3   |

| Oversample rate   | 16                  |      | 1,4   |

## Notes:

1. Guaranteed by design.

- 2. MPX clock refers to the platform clock.

- 3. Actual attainable baud rate will be limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

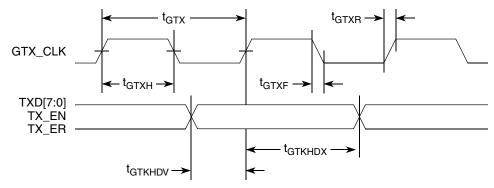

#### Table 28. GMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                    | Symbol <sup>1</sup> | Min | Тур | Max | Unit |

|----------------------------------------|---------------------|-----|-----|-----|------|

| GTX_CLK data clock fall time (80%-20%) | t <sub>GTXF</sub> 2 |     | _   | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

2. Guaranteed by design.

Figure 10 shows the GMII transmit AC timing diagram.

Figure 10. GMII Transmit AC Timing Diagram

# 8.2.2.2 GMII Receive AC Timing Specifications

Table 29 provides the GMII receive AC timing specifications.

### Table 29. GMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub> 3                  | _   | 8.0 |     | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.5 | _   |     | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>GRXR</sub> 2                 | _   |     | 1.0 | ns   |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

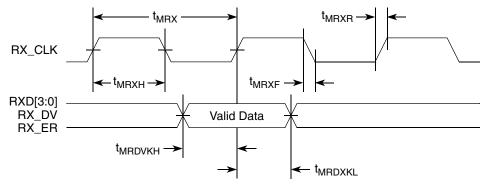

# 8.2.3.2 MII Receive AC Timing Specifications

Table 31 provides the MII receive AC timing specifications.

## Table 31. MII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2,3                | —    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub> 3                  | _    | 40  | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>MRXR</sub> 2                 | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | —   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

3. ±100 ppm tolerance on RX\_CLK frequency

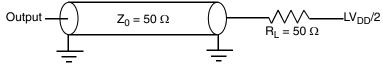

Figure 14 provides the AC test load for eTSEC.

Figure 14. eTSEC AC Test Load

Figure 15 shows the MII receive AC timing diagram.

Figure 15. MII Receive AC Timing Diagram

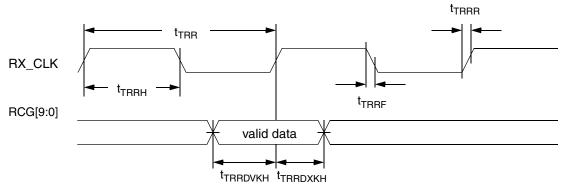

# 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1 a 125-MHz TBI receive clock is supplied on TSEC $n_RX_CLK$  pin (no receive clock is used on TSEC $n_TX_CLK$  in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC GTX CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 34.

Table 34. TBI single-clock Mode Receive AC Timing Specification

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                       | Symbol                              | Min | Тур | Мах | Unit |

|-------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRR</sub> <sup>1</sup>       | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH/</sub> t <sub>TRR</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>                   | _   | —   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>                   |     | —   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>                   | _   | —   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDVKH</sub>                | 2.0 | —   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDXKH</sub>                | 1.0 |     |     | ns   |

<sup>1</sup> ±100 ppm tolerance on RX\_CLK frequency

A timing diagram for TBI receive appears in Figure 18.

Figure 18. TBI Single-Clock Mode Receive AC Timing Diagram

# 8.2.6 RGMII and RTBI AC Timing Specifications

Table 35 presents the RGMII and RTBI AC timing specifications.

## Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $L/TV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>  | Min  | Тур | Мах | Unit |

|-----------------------------------------------------|----------------------|------|-----|-----|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub> ⁵ | -500 | 0   | 500 | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>   | 1.0  | _   | 2.8 | ns   |

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

# 8.2.7.2 RMII Receive AC Timing Specifications

# Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5%.

| Parameter/Condition                                       | Symbol <sup>1</sup>                 | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|-------------------------------------|------|------|------|------|

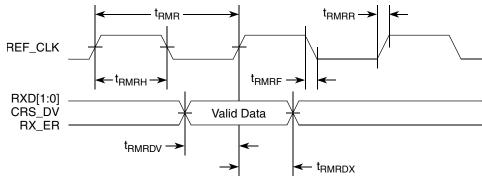

| REF_CLK clock period                                      | t <sub>RMR</sub>                    | 15.0 | 20.0 | 25.0 | ns   |

| REF_CLK duty cycle                                        | t <sub>RMRH</sub> /t <sub>RMR</sub> | 35   | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                               | t <sub>RMRJ</sub>                   | _    | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                               | t <sub>RMRR</sub>                   | 1.0  | _    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                               | t <sub>RMRF</sub>                   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>                  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>                  | 2.0  |      |      | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

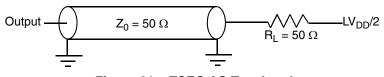

Figure 21 provides the AC test load for eTSEC.

Figure 21. eTSEC AC Test Load

Figure 22 shows the RMII receive AC timing diagram.

Figure 22. RMII Receive AC Timing Diagram

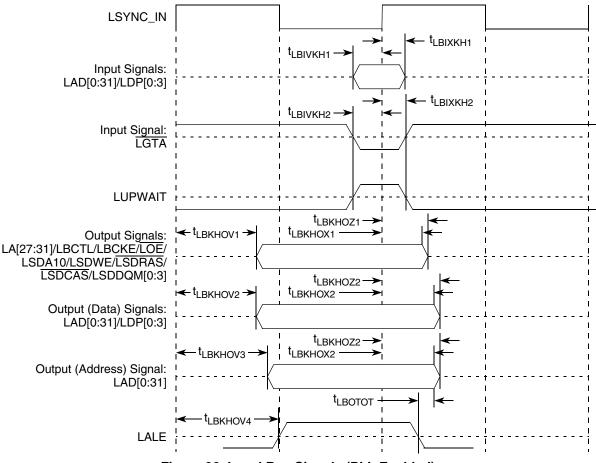

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to LALE assertion                                  | t <sub>LBKHOV4</sub> | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKHOX1</sub> | 0.7 | —   | ns   | —     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.7 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | _   | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> | _   | 2.5 | ns   | 5     |

#### Table 41. Local Bus Timing Parameters (OV<sub>DD</sub> = 3.3 V)m - PLL Enabled (continued)

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Figure 25 provides the AC test load for the local bus.

Figure 25. Local Bus AC Test Load

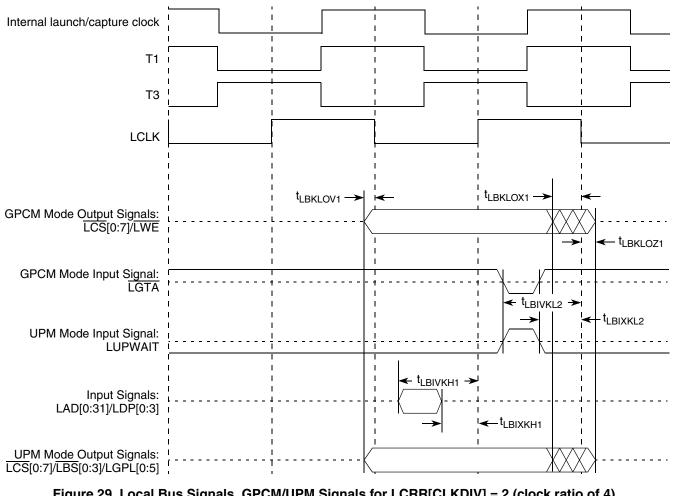

Figure 26 to Figure 31 show the local bus signals.

Figure 26. Local Bus Signals (PLL Enabled)

NOTE

PLL bypass mode is recommended when LBIU frequency is at or below 83 MHz. When LBIU operates above 83 MHz, LBIU PLL is recommended to be enabled.

Table 42 describes the general timing parameters of the local bus interface at  $OV_{DD} = 3.3$  V with PLL bypassed.

| Table 42. Local Bus | Timing Parameters—I | PLL Bypassed |

|---------------------|---------------------|--------------|

|---------------------|---------------------|--------------|

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Мах | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 45   | 55  | %    | _     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 3.9 | ns   | 8     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 5.7  | _   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 5.6  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.8 | _   | ns   | 4, 5  |

Figure 29. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (clock ratio of 4) (PLL Bypass Mode)

# Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

At recommended operating conditions (see Table 3).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах     | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|---------|------|-------|

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 30<br>30 |         | ns   | 5, 6  |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9 | ns   | 5, 6  |

Notes:

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 32). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to  $t_{TCLK}$ .

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 32 provides the AC test load for TDO and the boundary-scan outputs.

Figure 32. AC Test Load for the JTAG Interface

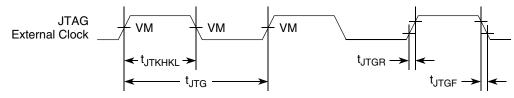

Figure 33 provides the JTAG clock input timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 33. JTAG Clock Input Timing Diagram

PCI Express

| Table 49. Differential Transmitter | (TX) Output Specifications | (continued) |

|------------------------------------|----------------------------|-------------|

|------------------------------------|----------------------------|-------------|

| Symbol                            | Parameter                                                                                                         | Min | Nom | Max           | Units | Comments                                                                                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>TX-IDLE</sub> -SET-TO-IDLE | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | _   | _   | 20            | UI    | After sending an Electrical Idle ordered set, the<br>Transmitter must meet all Electrical Idle Specifications<br>within this time. This is considered a debounce time<br>for the Transmitter to meet Electrical Idle after<br>transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   | _   | _   | 20            | UI    | Maximum time to meet all TX specifications when<br>transitioning from Electrical Idle to sending differential<br>data. This is considered a debounce time for the TX to<br>meet all TX specifications after leaving Electrical Idle                  |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | —   | —             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | —   | —             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential<br>TX Impedance                                                                                   | 80  | 100 | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                                |

| Z <sub>TX-DC</sub>                | Transmitter DC<br>Impedance                                                                                       | 40  | —   | —             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                                          |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       |     | _   | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                                   |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | _   | _             | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                                   |

| T <sub>crosslink</sub>            | Crosslink<br>Random<br>Timeout                                                                                    | 0   | —   | —             | ms    | This random timeout helps resolve conflicts in<br>crosslink configuration by eventually resulting in only<br>one Downstream and one Upstream Port. See Note 7.                                                                                       |

### Notes:

1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 52 and measured over any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 50)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The Transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50  $\Omega$  to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes—see Figure 52). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20-80% at transmitter package pins into a test load as shown in Figure 52 for both  $V_{TX-D+}$  and  $V_{TX-D-}$ .

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a

- 8. MPC8641D SerDes transmitter does not have C<sub>TX</sub> built-in. An external AC Coupling capacitor is required.

Local Bus - If parity is not used, tie LDP[0:3] to ground via a 4.7 k $\Omega$  resistor, tie LPBSE to OV<sub>DD</sub> via a 4.7 k $\Omega$  resistor (pull-up resistor). For systems which boot from Local Bus (GPCM)-controlled flash, a pullup on LGPL4 is required.

SerDes - Receiver lanes configured for PCI Express are allowed to be disconnected (as would occur when a PCI Express slot is connected but not populated). Directions for terminating the SerDes signals is discussed in Section 20.5.1, "Guidelines for High-Speed Interface Termination."

# 20.5.1 Guidelines for High-Speed Interface Termination

# 20.5.1.1 SerDes Interface

The high-speed SerDes interface can be disabled through the POR input cfg\_io\_ports[0:3] and through the DEVDISR register in software. If a SerDes port is disabled through the POR input the user can not enable it through the DEVDISR register in software. However, if a SerDes port is enabled through the POR input the user can disable it through the DEVDISR register in software. Disabling a SerDes port through software should be done on a temporary basis. Power is always required for the SerDes interface, even if the port is disabled through either mechanism. Table 72 describes the possible enabled/disabled scenarios for a SerDes port. The termination recommendations must be followed for each port.

|                          | Disabled through POR input                                                                                                            | Enabled through POR input                                                                                                                                                               |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enabled through DEVDISR  | SerDes port is disabled (and cannot be<br>enabled through DEVDISR)<br>Complete termination required<br>(Reference Clock not required) | SerDes port is enabled<br>Partial termination may be required <sup>1</sup><br>(Reference Clock is required)                                                                             |

| Disabled through DEVDISR | SerDes port is disabled (through POR<br>input)<br>Complete termination required<br>(Reference Clock not required)                     | SerDes port is disabled after software<br>disables port<br>Same termination requirements as when<br>the port is enabled through POR input <sup>2</sup><br>(Reference Clock is required) |

### Notes:

- <sup>1</sup> Partial Termination when a SerDes port is enabled through both POR input and DEVDISR is determined by the SerDes port mode. If the port is in x8 PCI Express mode, no termination is required because all pins are being used. If the port is in x1/x2/x4 PCI Express mode, termination is required on the unused pins. If the port is in x4 Serial RapidIO mode termination is required on the unused pins.

- <sup>2</sup> If a SerDes port is enabled through the POR input and then disabled through DEVDISR, no hardware changes are required. Termination of the SerDes port should follow what is required when the port is enabled through both POR input and DEVDISR. See Note 1 for more information.

If the high-speed SerDes port requires complete or partial termination, the unused pins should be terminated as described in this section.

The following pins must be left unconnected (floating):

- SD*n*\_TX[7:0]

- $\overline{\text{SD}n_\text{TX}}[7:0]$

System Design Information

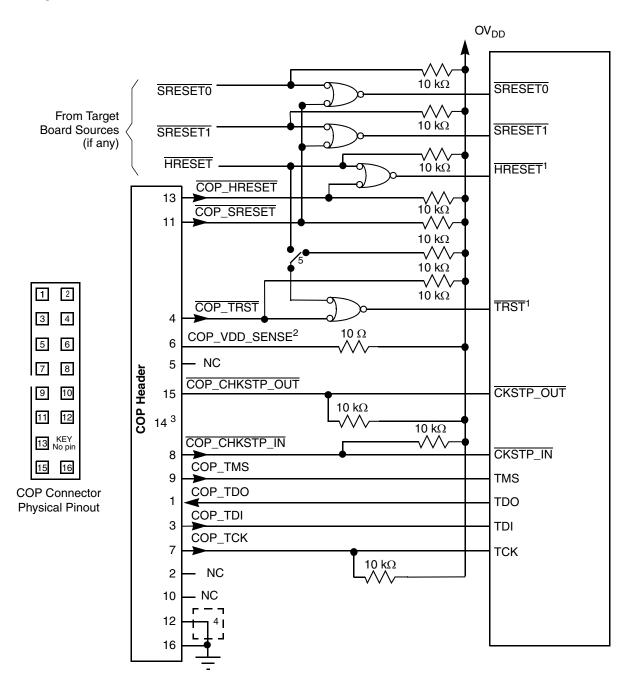

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

### Figure 68. JTAG/COP Interface Connection for one MPC8641 device