#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e600                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.333GHz                                                               |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 994-BCBGA, FCCBGA                                                      |

| Supplier Device Package         | 994-FCCBGA (33x33)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641hx1333jb |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Key Features

The following lists an overview of the MPC8641 key feature set:

- Major features of the e600 core are as follows:

- High-performance, 32-bit superscalar microprocessor that implements the PowerPC ISA

- Eleven independent execution units and three register files

- Branch processing unit (BPU)

- Four integer units (IUs) that share 32 GPRs for integer operands

- 64-bit floating-point unit (FPU)

- Four vector units and a 32-entry vector register file (VRs)

- Three-stage load/store unit (LSU)

- Three issue queues, FIQ, VIQ, and GIQ, can accept as many as one, two, and three instructions, respectively, in a cycle.

- Rename buffers

- Dispatch unit

- Completion unit

- Two separate 32-Kbyte instruction and data level 1 (L1) caches

- Integrated 1-Mbyte, eight-way set-associative unified instruction and data level 2 (L2) cache with ECC

- 36-bit real addressing

- Separate memory management units (MMUs) for instructions and data

- Multiprocessing support features

- Power and thermal management

- Performance monitor

- In-system testability and debugging features

- Reliability and serviceability

- MPX coherency module (MCM)

- Ten local address windows plus two default windows

- Optional low memory offset mode for core 1 to allow for address disambiguation

- Address translation and mapping units (ATMUs)

- Eight local access windows define mapping within local 36-bit address space

- Inbound and outbound ATMUs map to larger external address spaces

- Three inbound windows plus a configuration window on PCI Express

- Four inbound windows plus a default window on serial RapidIO

- Four outbound windows plus default translation for PCI Express

- Eight outbound windows plus default translation for serial RapidIO with segmentation and sub-segmentation support

|                           | Characteristic                                                                                                                                                               | Symbol                               | Absolute Maximum<br>Value                                          | Unit | Notes |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|------|-------|

| Input voltage             | DDR and DDR2 SDRAM signals                                                                                                                                                   | D <i>n</i> _MV <sub>IN</sub>         | - 0.3 to (D <i>n</i> _GV <sub>DD</sub> + 0.3)                      | V    | 5     |

|                           | DDR and DDR2 SDRAM reference                                                                                                                                                 | D <i>n</i> _MV <sub>REF</sub>        | -0.3 to (D <i>n</i> _GV <sub>DD</sub> /2 + 0.3)                    | V    | —     |

|                           | Three-speed Ethernet signals                                                                                                                                                 | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to (LV <sub>DD</sub> + 0.3)<br>GND to (TV <sub>DD</sub> + 0.3) | V    | 5     |

|                           | DUART, Local Bus, DMA,<br>Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test,<br>Power management, I <sup>2</sup> C, JTAG and<br>Miscellaneous I/O voltage | OV <sub>IN</sub>                     | GND to (OV <sub>DD</sub> + 0.3)                                    | V    | 5     |

| Storage temperature range |                                                                                                                                                                              | T <sub>STG</sub>                     | -55 to 150                                                         | °C   | —     |

| Table 1. Absolute | Maximum | Ratings <sup>1</sup> | (continued) |

|-------------------|---------|----------------------|-------------|

|-------------------|---------|----------------------|-------------|

Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Core 1 characteristics apply only to MPC8641D. If two separate power supplies are used for V<sub>DD</sub>\_Core0 and V<sub>DD</sub>\_Core1, they must be kept within 100 mV of each other during normal run time.

- 3. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 4. The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

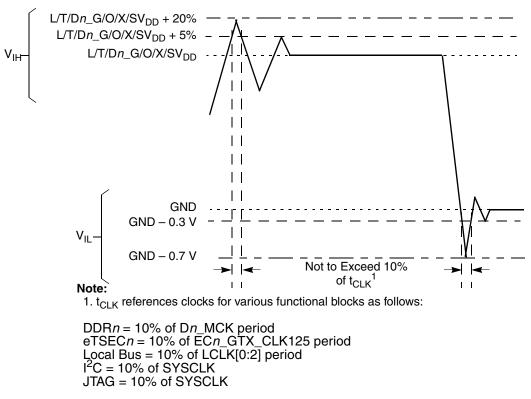

- 5. During run time (M,L,T,O)V<sub>IN</sub> and D*n*\_MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

### 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8641. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed. For details on order information and specific operating conditions for parts, see Section 21, "Ordering Information."

| Characteristic                            | Symbol                   | Recommended<br>Value | Unit | Notes    |

|-------------------------------------------|--------------------------|----------------------|------|----------|

| Cores supply voltages                     | V <sub>DD</sub> _Core0,  | 1.10 ± 50 mV         | V    | 1, 2, 8  |

|                                           | V <sub>DD</sub> _Core1   | 1.05 ± 50 mV         |      | 1, 2, 7  |

|                                           |                          | 0.95 ± 50 mV         |      | 1, 2, 12 |

| Cores PLL supply                          | AV <sub>DD</sub> _Core0, | 1.10 ± 50 mV         | V    | 8, 13    |

|                                           | AV <sub>DD</sub> _Core1  | 1.05 ± 50 mV         |      | 7, 13    |

|                                           |                          | 0.95 ± 50 mV         |      | 12, 13   |

| SerDes Transceiver Supply (Ports 1 and 2) | SV <sub>DD</sub>         | 1.10 ± 50 mV         | V    | 8, 11    |

|                                           |                          | 1.05 ± 50 mV         |      | 7, 11    |

### Table 2. Recommended Operating Conditions

### Electrical Characteristics

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8641.

Figure 2. Overshoot/Undershoot Voltage for Dn\_M/O/L/TV<sub>IN</sub>

The MPC8641 core voltage must always be provided at nominal  $V_{DD}$ \_Core*n* (See Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $L/TV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced to each externally supplied  $Dn_MV_{REF}$  signal (nominally set to  $Dn_GV_{DD}/2$ ) as is appropriate for the (SSTL-18 and SSTL-25) electrical signaling standards.

### 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                                                                                                               | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                    | Notes   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------|---------|

| DDR1 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 2.5 V | 4, 9    |

| DDR2 signal                                                                                                                               | 18<br>36 (half strength mode)           | D <i>n_</i> GV <sub>DD</sub> = 1.8 V | 1, 5, 9 |

| Local Bus signals                                                                                                                         | 45<br>25                                | OV <sub>DD</sub> = 3.3 V             | 2, 6    |

| eTSEC/10/100 signals                                                                                                                      | 45                                      | T/LV <sub>DD</sub> = 3.3 V           | 6       |

|                                                                                                                                           | 30                                      | T/LV <sub>DD</sub> = 2.5 V           | 6       |

| DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management,<br>JTAG and Miscellaneous I/O voltage | 45                                      | OV <sub>DD</sub> = 3.3 V             | 6       |

| l <sup>2</sup> C                                                                                                                          | 150                                     | OV <sub>DD</sub> = 3.3 V             | 7       |

| SRIO, PCI Express                                                                                                                         | 100                                     | SV <sub>DD</sub> = 1.1/1.05 V        | 3, 8    |

### Table 3. Output Drive Capability

Notes:

- 1. See the DDR Control Driver registers in the MPC8641D reference manual for more information.

- 2. Only the following local bus signals have programmable drive strengths: LALE, LAD[0:31], LDP[0:3], LA[27:31], LCKE, LCS[1:2], LWE[0:3], LGPL1, LGPL2, LGPL3, LGPL4, LGPL5, LCLK[0:2]. The other local bus signals have a fixed drive strength of 45 Ω. See the POR Impedance Control register in the MPC8641D reference manual for more information about local bus signals and their drive strength programmability.

- 3. See Section 17, "Signal Listings," for details on resistor requirements for the calibration of SD*n*\_IMP\_CAL\_TX and SD*n*\_IMP\_CAL\_RX transmit and receive signals.

- 4. Stub Series Terminated Logic (SSTL-25) type pins.

- 5. Stub Series Terminated Logic (SSTL-18) type pins.

- 6. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 7. Open Drain type pins.

- 8. Low Voltage Differential Signaling (LVDS) type pins.

- 9. The drive strength of the DDR interface in half strength mode is at  $T_i = 105C$  and at  $Dn_GV_{DD}$  (min).

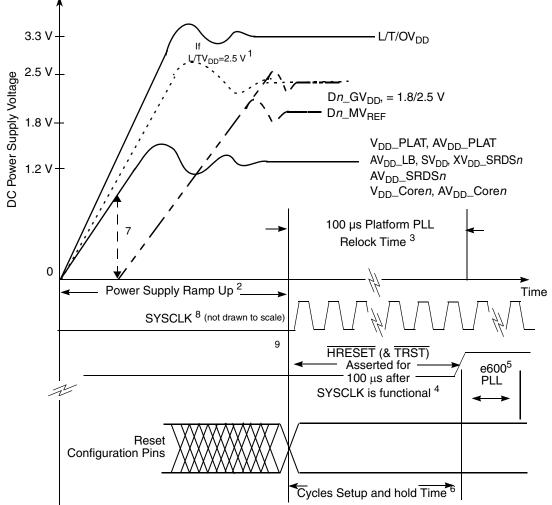

### 2.2 Power Up/Down Sequence

The MPC8641 requires its power rails to be applied in a specific sequence in order to ensure proper device operation.

### NOTE

The recommended maximum ramp up time for power supplies is 20 milliseconds.

The chronological order of power up is as follows:

1. All power rails other than DDR I/O ( $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$ ).

#### Notes:

- 1. Dotted waveforms correspond to optional supply values for a specified power supply. See Table 2.

- 2. The recommended maximum ramp up time for power supplies is 20 milliseconds.

- 3. Refer to Section 5, "RESET Initialization" for additional information on PLL relock and reset signal assertion timing requirements.

- 4. Refer to Table 11 for additional information on reset configuration pin setup timing requirements. In addition see Figure 68 regarding HRESET and JTAG connection details including TRST.

- 5. e600 PLL relock time is 100 microseconds maximum plus 255 MPX\_clk cycles.

- 6. Stable PLL configuration signals are required as stable SYSCLK is applied. All other POR configuration inputs are required 4 SYSCLK cycles before HRESET negation and are valid at least 2 SYSCLK cycles after HRESET has negated (hold requirement). See Section 5, "RESET Initialization" for more information on setup and hold time of reset configuration signals.

- V<sub>DD</sub>\_PLAT, AV<sub>DD</sub>\_PLAT must strictly reach 90% of their recommended voltage before the rail for Dn\_GV<sub>DD</sub>, and Dn\_MV<sub>REF</sub> reaches 10% of their recommended voltage.

- 8. SYSCLK must be driven only AFTER the power for the various power supplies is stable.

- In device sleep mode, the reset configuration signals for DRAM types (TSEC2\_TXD[4],TSEC2\_TX\_ER) must be valid BEFORE HRESET is asserted.

#### Figure 3. MPC8641 Power-Up and Reset Sequence

### Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

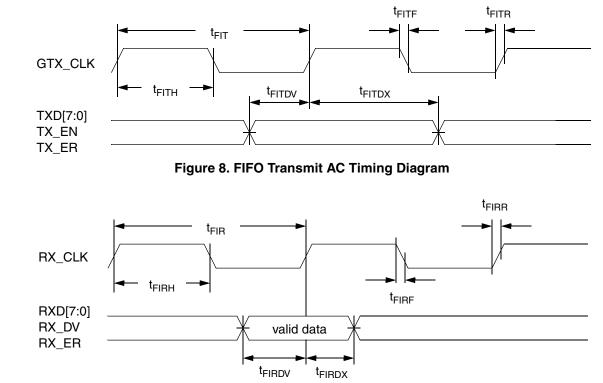

Timing diagrams for FIFO appear in Figure 8 and Figure 9.

Figure 9. FIFO Receive AC Timing Diagram

### 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

### 8.2.2.1 GMII Transmit AC Timing Specifications

Table 28 provides the GMII transmit AC timing specifications.

### Table 28. GMII Transmit AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                               | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|---------------------------------------------------|--------------------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>            | 2.5 | _   | _   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX            | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%-80%)            | t <sub>GTXR</sub> <sup>2</sup> | _   |     | 1.0 | ns   |

### 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.3.1 MII Transmit AC Timing Specifications

Table 30 provides the MII transmit AC timing specifications.

### Table 30. MII Transmit AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | —   | 400 | —   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | —   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise time (20%-80%)           | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall time (80%-20%)           | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 |     | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

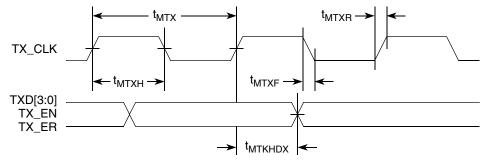

Figure 13 shows the MII transmit AC timing diagram.

Figure 13. MII Transmit AC Timing Diagram

### 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 8.2.4.1 TBI Transmit AC Timing Specifications

Table 32 provides the TBI transmit AC timing specifications.

### Table 32. TBI Transmit AC Timing Specifications

At recommended operating conditions with L/TV\_DD of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Мах | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | —   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | —   | ns   |

| GTX_CLK rise time (20%-80%)                | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%-20%)                | t <sub>TTXF</sub> 2            | _   | _   | 1.0 | ns   |

### Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Guaranteed by design.

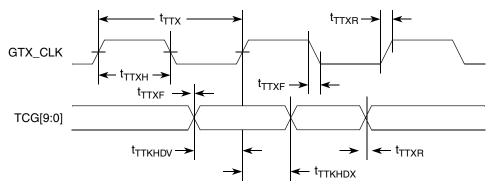

Figure 16 shows the TBI transmit AC timing diagram.

Figure 16. TBI Transmit AC Timing Diagram

## 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI and RTBI are specified in "Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management."

## 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 38.

| Parameter                                                                  | Symbol           | Min   | Мах   | Unit |

|----------------------------------------------------------------------------|------------------|-------|-------|------|

| Supply voltage (3.3 V)                                                     | OV <sub>DD</sub> | 3.135 | 3.465 | V    |

| Output high voltage<br>(OV <sub>DD</sub> = Min, I <sub>OH</sub> = -1.0 mA) | V <sub>OH</sub>  | 2.10  | _     | V    |

| Output low voltage<br>(OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA)    | V <sub>OL</sub>  | _     | 0.50  | V    |

| Input high voltage                                                         | V <sub>IH</sub>  | 1.70  | _     | V    |

| Input low voltage                                                          | V <sub>IL</sub>  | _     | 0.90  | V    |

| Input high current<br>( $OV_{DD} = Max, V_{IN}^{1} = 2.1 V$ )              | IIH              | _     | 40    | μΑ   |

| Input low current<br>(OV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V)     | IIL              | -600  | _     | μΑ   |

Table 38. MII Management DC Electrical Characteristics

### Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

## 9.2 MII Management AC Electrical Specifications

Table 39 provides the MII management AC timing specifications.

Table 39. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter/Condition        | Symbol <sup>1</sup> | Min                    | Тур | Max                    | Unit | Notes |

|----------------------------|---------------------|------------------------|-----|------------------------|------|-------|

| MDC frequency              | f <sub>MDC</sub>    | 2.5                    | —   | 9.3                    | MHz  | 2, 4  |

| MDC period                 | t <sub>MDC</sub>    | 80                     | —   | 400                    | ns   | —     |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                     | —   | _                      | ns   | —     |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | 16*t <sub>MPXCLK</sub> | —   | _                      | ns   | 5     |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10                     | —   | 16*t <sub>MPXCLK</sub> | ns   | 3, 5  |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5                      | —   | _                      | ns   | —     |

PCI Express

| Symbol                            | Parameter                                                                                                         | Min | Nom | Max           | Units | Comments                                                                                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>TX-IDLE</sub> -SET-TO-IDLE | Maximum time to<br>transition to a<br>valid Electrical<br>idle after sending<br>an Electrical Idle<br>ordered set | _   | _   | 20            | UI    | After sending an Electrical Idle ordered set, the<br>Transmitter must meet all Electrical Idle Specifications<br>within this time. This is considered a debounce time<br>for the Transmitter to meet Electrical Idle after<br>transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to<br>transition to valid<br>TX specifications<br>after leaving an<br>Electrical idle<br>condition   | _   | _   | 20            | UI    | Maximum time to meet all TX specifications when<br>transitioning from Electrical Idle to sending differential<br>data. This is considered a debounce time for the TX to<br>meet all TX specifications after leaving Electrical Idle                  |

| RL <sub>TX-DIFF</sub>             | Differential<br>Return Loss                                                                                       | 12  | —   | —             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | —   | —             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                                         |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential<br>TX Impedance                                                                                   | 80  | 100 | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                                |

| Z <sub>TX-DC</sub>                | Transmitter DC<br>Impedance                                                                                       | 40  | —   | —             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                                          |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       |     | _   | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                                   |

| C <sub>TX</sub>                   | AC Coupling<br>Capacitor                                                                                          | 75  | _   | _             | nF    | All Transmitters shall be AC coupled. The AC coupling<br>is required either within the media or within the<br>transmitting component itself. See Note 8.                                                                                             |

| T <sub>crosslink</sub>            | Crosslink<br>Random<br>Timeout                                                                                    | 0   | —   | —             | ms    | This random timeout helps resolve conflicts in<br>crosslink configuration by eventually resulting in only<br>one Downstream and one Upstream Port. See Note 7.                                                                                       |

### Notes:

1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 52 and measured over any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 50)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The Transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50  $\Omega$  to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes—see Figure 52). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20-80% at transmitter package pins into a test load as shown in Figure 52 for both  $V_{TX-D+}$  and  $V_{TX-D-}$ .

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a

- 8. MPC8641D SerDes transmitter does not have C<sub>TX</sub> built-in. An external AC Coupling capacitor is required.

Serial RapidIO

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Max  |        | Notes                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 800   | 800  | ps     | +/– 100 ppm                                                                      |  |

### Table 52. Short Run Transmitter AC Timing Specifications—1.25 GBaud

### Table 53. Short Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

|                             | Symbol              | Min   | Max  | Onic   | Notes                                                                            |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                                |  |

| Multiple Output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output<br>between lanes of a multilane<br>link           |  |

| Unit Interval               | UI                  | 400   | 400  | ps     | +/- 100 ppm                                                                      |  |

### Table 54. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                            |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------------|--|

|                             | Symbol              | Min   | Мах  |        |                                                                                  |  |

| Output Voltage,             | Vo                  | -0.40 | 2.30 | Volts  | Voltage relative to COMMON<br>of either signal comprising a<br>differential pair |  |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                                |  |

| Deterministic Jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                                |  |

| Total Jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                                |  |

Signal Listings

| Name <sup>1</sup>               | Package Pin Number                             | Pin Type         | Power Supply     | Notes    |

|---------------------------------|------------------------------------------------|------------------|------------------|----------|

| TSEC1_TXD[0:7]/<br>GPOUT[0:7]   | AF25, AC23, AG24, AG23, AE24, AE23, AE22, AD22 | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC1_TX_EN                     | AB22                                           | 0                | LV <sub>DD</sub> | 36       |

| TSEC1_TX_ER                     | AH26                                           | 0                | LV <sub>DD</sub> | _        |

| TSEC1_TX_CLK                    | AC22                                           | I                | LV <sub>DD</sub> | 40       |

| TSEC1_GTX_CLK                   | AH25                                           | 0                | LV <sub>DD</sub> | 41       |

| TSEC1_CRS                       | AM24                                           | I/O              | LV <sub>DD</sub> | 37       |

| TSEC1_COL                       | AM25                                           | I                | LV <sub>DD</sub> | _        |

| TSEC1_RXD[0:7]/<br>GPIN[0:7]    | AL25, AL24, AK26, AK25, AM26, AF26, AH24, AG25 | I                | LV <sub>DD</sub> | 10       |

| TSEC1_RX_DV                     | AJ24                                           | I                | LV <sub>DD</sub> | _        |

| TSEC1_RX_ER                     | AJ25                                           | I                | LV <sub>DD</sub> | _        |

| TSEC1_RX_CLK                    | AK24                                           | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 2 Sign                              | als <sup>5</sup> | - <b>I</b>       |          |

| TSEC2_TXD[0:3]/<br>GPOUT[8:15]  | AB20, AJ23, AJ22, AD19                         | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TXD[4]/<br>GPOUT[12]      | AH23                                           | 0                | LV <sub>DD</sub> | 6,10, 38 |

| TSEC2_TXD[5:7]/<br>GPOUT[13:15] | AH21, AG22, AG21                               | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TX_EN                     | AB21                                           | 0                | LV <sub>DD</sub> | 36       |

| TSEC2_TX_ER                     | AB19                                           | 0                | LV <sub>DD</sub> | 6, 38    |

| TSEC2_TX_CLK                    | AC21                                           | I                | LV <sub>DD</sub> | 40       |

| TSEC2_GTX_CLK                   | AD20                                           | 0                | LV <sub>DD</sub> | 41       |

| TSEC2_CRS                       | AE20                                           | I/O              | LV <sub>DD</sub> | 37       |

| TSEC2_COL                       | AE21                                           | I                | LV <sub>DD</sub> | _        |

| TSEC2_RXD[0:7]/<br>GPIN[8:15]   | AL22, AK22, AM21, AH20, AG20, AF20, AF23, AF22 | I                | LV <sub>DD</sub> | 10       |

| TSEC2_RX_DV                     | AC19                                           | I                | LV <sub>DD</sub> | _        |

| TSEC2_RX_ER                     | AD21                                           | l                | LV <sub>DD</sub> |          |

| TSEC2_RX_CLK                    | AM22                                           | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 3 Sign                              | als <sup>5</sup> | 1                |          |

| TSEC3_TXD[0:3]                  | AL21, AJ21, AM20, AJ20                         | 0                | TV <sub>DD</sub> | 6        |

| TSEC3_TXD[4]/                   | AM19                                           | 0                | TV <sub>DD</sub> | _        |

| TSEC3_TXD[5:7]                  | AK21, AL20, AL19                               | 0                | TV <sub>DD</sub> | 6        |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

Signal Listings

| Name <sup>1</sup>                                   | Package Pin Number                             | Pin Type                    | Power Supply     | Notes         |

|-----------------------------------------------------|------------------------------------------------|-----------------------------|------------------|---------------|

| LCS[6]/DMA_DACK[2]                                  | E23                                            | 0                           | OV <sub>DD</sub> | 7, 10         |

| LCS[7]/DMA_DDONE[2]                                 | F23                                            | 0                           | OV <sub>DD</sub> | 7, 10         |

| LWE[0:3]/           LSDDQM[0:3]/           LBS[0:3] | E21, F21, D22, E20                             | 0                           | OV <sub>DD</sub> | 6             |

| LBCTL                                               | D21                                            | 0                           | OV <sub>DD</sub> | —             |

| LALE                                                | E19                                            | 0                           | OV <sub>DD</sub> | —             |

| LGPL0/LSDA10                                        | F20                                            | 0                           | OV <sub>DD</sub> | 25            |

| LGPL1/LSDWE                                         | H20                                            | 0                           | OV <sub>DD</sub> | 25            |

| LGPL2/ <u>LOE</u> /<br>LSDRAS                       | J20                                            | 0                           | OV <sub>DD</sub> | _             |

| LGPL3/LSDCAS                                        | К20                                            | 0                           | OV <sub>DD</sub> | 6             |

| LGPL4/ <del>LGTA</del> /<br>LUPWAIT/LPBSE           | L21                                            | I/O                         | OV <sub>DD</sub> | 42            |

| LGPL5                                               | J19                                            | 0                           | OV <sub>DD</sub> | 6             |

| LCKE                                                | H19                                            | 0                           | OV <sub>DD</sub> | —             |

| LCLK[0:2]                                           | G19, L19, M20                                  | 0                           | OV <sub>DD</sub> | —             |

| LSYNC_IN                                            | M19                                            | I                           | OV <sub>DD</sub> | _             |

| LSYNC_OUT                                           | D20                                            | 0                           | OV <sub>DD</sub> | _             |

|                                                     | DMA Signals <sup>5</sup>                       |                             |                  |               |

| DMA_DREQ[0:1]                                       | E31, E32                                       | I                           | OV <sub>DD</sub> | _             |

| DMA_DREQ[2]/LCS[5]                                  | B23                                            | I                           | OV <sub>DD</sub> | 9, 10         |

| DMA_DREQ[3]/IRQ[9]                                  | B30                                            | I                           | OV <sub>DD</sub> | 10            |

| DMA_DACK[0:1]                                       | D32, F30                                       | 0                           | OV <sub>DD</sub> | _             |

| DMA_DACK[2]/LCS[6]                                  | E23                                            | 0                           | OV <sub>DD</sub> | 10            |

| DMA_DACK[3]/IRQ[10]                                 | C30                                            | 0                           | OV <sub>DD</sub> | 9, 10         |

| DMA_DDONE[0:1]                                      | F31, F32                                       | 0                           | OV <sub>DD</sub> | _             |

| DMA_DDONE[2]/LCS[7]                                 | F23                                            | 0                           | OV <sub>DD</sub> | 10            |

| DMA_DDONE[3]/IRQ[11]                                | D30                                            | 0                           | OV <sub>DD</sub> | 9, 10         |

|                                                     | Programmable Interrupt Cont                    | roller Signals <sup>5</sup> | ·                |               |

| MCP_0                                               | F17                                            | I                           | OV <sub>DD</sub> | —             |

| MCP_1                                               | H17                                            | I                           | OV <sub>DD</sub> | 12, <i>S4</i> |

| IRQ[0:8]                                            | G28, G29, H27, J23, M23, J27, F28, J24,<br>L23 | Ι                           | OV <sub>DD</sub> | _             |

Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>                                   | Package Pin Number                                                                                                                            | Pin Type                                                   | Power Supply     | Notes |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|-------|

| AGND_SRDS1                                          | P30                                                                                                                                           | SerDes Port 1<br>Ground pin for<br>AV <sub>DD</sub> _SRDS1 | _                | _     |

| AGND_SRDS2                                          | AF30                                                                                                                                          | SerDes Port 2<br>Ground pin for<br>AV <sub>DD</sub> _SRDS2 | —                | _     |

| SGND                                                | H28, H32, J30, K31, L28, L29, M32, N30,<br>R29, T32, U30, V31, W29,Y32 AA30, AB31,<br>AC29, AD32, AE30, AG29, AH32, AJ30,<br>AK31, AL29, AM32 | Ground pins for<br>SV <sub>DD</sub>                        | _                | _     |

| XGND                                                | K27, L25, M26, N24, P27, R25, T26, U24,<br>V27, W25, Y28, AA24, AB27, AC25, AD28,<br>AE26, AF27, AH28, AJ26, AK27, AL26,<br>AM28              | Ground pins for XV <sub>DD</sub> _SRDS <i>n</i>            | _                | _     |

|                                                     | Reset Configuration Si                                                                                                                        | gnals <sup>20</sup>                                        |                  |       |

| TSEC1_TXD[0] /<br>cfg_alt_boot_vec                  | AF25                                                                                                                                          | _                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[1]/<br>cfg_platform_freq                  | AC23                                                                                                                                          | —                                                          | LV <sub>DD</sub> | 21    |

| TSEC1_TXD[2:4]/<br>cfg_device_id[5:7]               | AG24, AG23, AE24                                                                                                                              | —                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[5]/<br>cfg_tsec1_reduce                   | AE23                                                                                                                                          | —                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[6:7]/<br>cfg_tsec1_prtcl[0:1]             | AE22, AD22                                                                                                                                    | —                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[0:3]/<br>cfg_rom_loc[0:3]                 | AB20, AJ23, AJ22, AD19                                                                                                                        | —                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[4],<br>TSEC2_TX_ER/<br>cfg_dram_type[0:1] | AH23,<br>AB19                                                                                                                                 | _                                                          | LV <sub>DD</sub> | 38    |

| TSEC2_TXD[5]/<br>cfg_tsec2_reduce                   | AH21                                                                                                                                          | _                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[6:7]/<br>cfg_tsec2_prtcl[0:1]             | AG22, AG21                                                                                                                                    |                                                            | LV <sub>DD</sub> |       |

| TSEC3_TXD[0:1]/<br>cfg_spare[0:1]                   | AL21, AJ21                                                                                                                                    | 0                                                          | TV <sub>DD</sub> | 33    |

| TSEC3_TXD[2]/<br>cfg_core1_enable                   | AM20                                                                                                                                          | 0                                                          | TV <sub>DD</sub> | _     |

| TSEC3_TXD[3]/<br>cfg_core1_Im_offset                | AJ20                                                                                                                                          | —                                                          | LV <sub>DD</sub> | _     |

| TSEC3_TXD[5]/<br>cfg_tsec3_reduce                   | AK21                                                                                                                                          | _                                                          | LV <sub>DD</sub> |       |

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

### Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup> Package Pin Number | Pin Type | Power Supply | Notes |

|--------------------------------------|----------|--------------|-------|

|--------------------------------------|----------|--------------|-------|

#### Note:

- 1. Multi-pin signals such as D1\_MDQ[0:63] and D2\_MDQ[0:63] have their physical package pin numbers listed in order corresponding to the signal names.

- 2. Stub Series Terminated Logic (SSTL-18 and SSTL-25) type pins.

- 3. If a DDR port is not used, it is possible to leave the related power supply (Dn\_GVDD, Dn\_MVREF) turned off at reset. Note that these power supplies can only be powered up again at reset for functionality to occur on the DDR port.

- 4. Low Voltage Differential Signaling (LVDS) type pins.

- 5. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 6. This pin is a reset configuration pin and appears again in the Reset Configuration Signals section of this table. See the Reset Configuration Signals section of this table for config name and connection details.

- 7. Recommend a weak pull-up resistor (1–10 k $\Omega$ ) be placed from this pin to its power supply.

- 8. Recommend a weak pull-down resistor (2–10 k $\Omega$ ) be placed from this pin to ground.

- 9. This multiplexed pin has input status in one mode and output in another

- 10. This pin is a multiplexed signal for different functional blocks and appears more than once in this table.

- 11. This pin is open drain signal.

- 12. Functional only on the MPC8641D.

- 13. These pins should be left floating.

- 14. These pins should be connected to SV<sub>DD</sub>.

- 15. These pins should be pulled to ground with a strong resistor (270- $\Omega$  to 330- $\Omega$ ).

- 16. These pins should be connected to OVDD.

- 17. This is a SerDes PLL/DLL digital test signal and is only for factory use.

- 18. This is a SerDes PLL/DLL analog test signal and is only for factory use.

- 19. This pin should be pulled to ground with a 100- $\Omega$  resistor.

- 20. The pins in this section are reset configuration pins. Each pin has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 21. Should be pulled down at reset if platform frequency is at 400 MHz.

- 22. These pins require 4.7-kΩ pull-up or pull-down resistors and must be driven as they are used to determine PLL configuration ratios at reset.

- 23. This output is actively driven during reset rather than being tri-stated during reset.

- 24 These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 25. This pin should NOT be pulled down (or driven low) during reset.

- 26. These are test signals for factory use only and must be pulled up (100- $\Omega$  to 1- k $\Omega$ ) to OVDD for normal machine operation.

- 27. Dn\_MDIC[0] should be connected to ground with an 18-Ω resistor +/- 1-Ω and Dn\_MDIC[1] should be connected Dn\_GVDD with an 18-Ω resistor +/- 1-Ω. These pins are used for automatic calibration of the DDR IOs.

- 28. Pin N18 is recommended as a reference point for determining the voltage of V<sub>DD</sub>\_PLAT and is hence considered as the V<sub>DD</sub>\_PLAT sensing voltage and is called SENSEVDD\_PLAT.

- 29. Pin P18 is recommended as the ground reference point for SENSEVDD\_PLAT and is called SENSEVSS\_PLAT.

- 30. This pin should be pulled to ground with a 200- $\Omega$  resistor.

- 31. These pins are connected to the power/ground planes internally and may be used by the core power supply to improve tracking and regulation.

- 32. Must be tied low if unused

- 33. These pins may be used as defined functional reset configuration pins in the future. Please include a resistor pull up/down option to allow flexibility of future designs.

- 34. Used as serial data output for SRIO 1x/4x link.

- 35. Used as serial data input for SRIO 1x/4x link.

- 36. This pin requires an external 4.7-kΩ pull-down resistor to pevent PHY from seeing a valid Transmit Enable before it is actively driven.

## **18.4.1 SYSCLK to Platform Frequency Options**

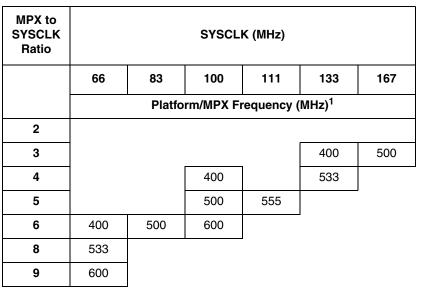

Table 70 shows some SYSCLK frequencies and the expected MPX frequency values based on the MPX clock to SYSCLK ratio. Note that frequencies between 400 MHz and 500 MHz are NOT supported on the platform. See note regarding *cfg\_platform\_freq* in Section 17, "Signal Listings," because it is a reset configuration pin that is related to platform frequency.

Table 70. Frequency Options of SYSCLK with Respect to Platform/MPX Clock Speed

SYSCLK frequency range is 66-167 MHz. Platform clock/ MPX frequency range is 400 MHz, 500-600 MHz.

### 18.4.2 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

```

FIFO TX/RX clock frequency <= platform clock frequency/4.2

```

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz

For FIFO encoded mode:

```

FIFO TX/RX clock frequency <= platform clock frequency/3.2

```

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

System Design Information

# 20 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8641.

## 20.1 System Clocking

This device includes six PLLs, as follows:

- 1. The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 18.2, "MPX to SYSCLK PLL Ratio."

- 2. The dual e600 Core PLLs generate the e600 clock from the externally supplied input.

- 3. The local bus PLL generates the clock for the local bus.

- 4. There are two internal PLLs for the SerDes block.

## 20.2 Power Supply Design and Sequencing

## 20.2.1 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins.

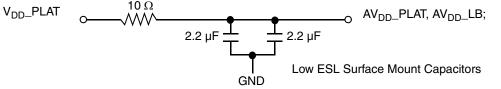

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 64, one to each of the  $AV_{DD}$  type pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  type pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  type pin, which is on the periphery of the footprint, without the inductance of vias.

Figure 63 and Figure 64 show the PLL power supply filter circuits for the platform and cores, respectively.

Figure 63. MPC8641 PLL Power Supply Filter Circuit (for platform and Local Bus)

System Design Information

#### Notes:

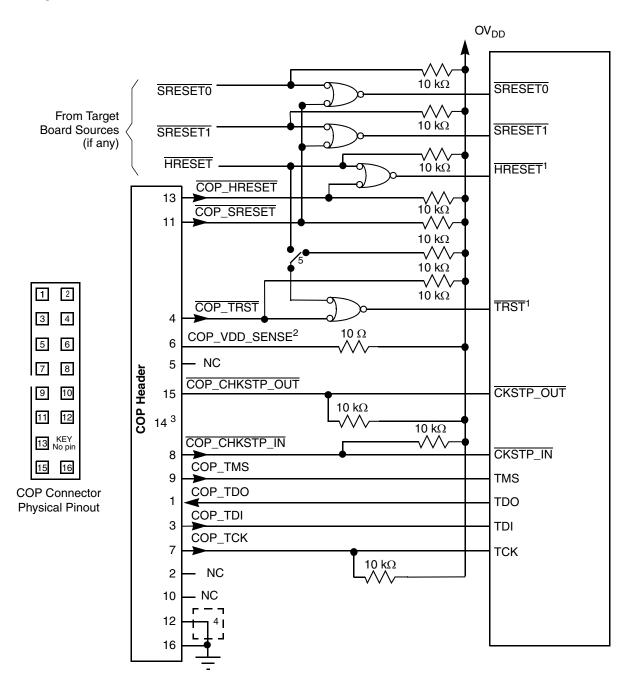

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

### Figure 68. JTAG/COP Interface Connection for one MPC8641 device

Document Revision History

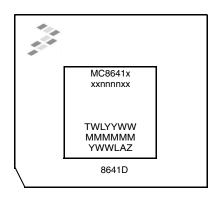

## 21.2 Part Marking

Parts are marked as the example shown in Figure 70.

NOTE: TWLYYWW is the test code MMMMMM is the M00 (mask) number. YWWLAZ is the assembly traceability code.

### Figure 70. Part Marking for FC-CBGA Device

# 22 Document Revision History

Table 76 provides a revision history for the MPC8641D hardware specification.

### Table 76. Document Revision History

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 05/2014 | <ul> <li>Updated the Serial RapidIO equation in Section 4.4, "Platform Frequency Requirements for PCI-Express and Serial RapidIO"</li> <li>Updated Section 19.2.4, "Temperature Diode," by removing the ideality factor value.</li> <li>Added VJ package type designator and footnotes to Table 74, "Part Numbering Nomenclature" and Section 16.1, "Package Parameters for the MPC8641."</li> </ul>          |

| 2        | 07/2009 | <ul> <li>Added note 8 to Table 49, "Differential Transmitter (TX) Output Specifications."</li> <li>Added Revision E to Table 74, "Part Numbering Nomenclature."</li> </ul>                                                                                                                                                                                                                                    |

| 1        | 11/2008 | <ul> <li>Added Section 4.4, "Platform Frequency Requirements for PCI-Express and Serial RapidIO."</li> <li>Removed the statement "Note that core processor speed of 1500 MHz is only available for the MPC8641D (dual core)" from Note 2 in Table 74 because a 1500 MHz core is offered for both MPC8641D (dual core) and MPC8641 (single core).</li> <li>Added Note 8 to Figure 57 and Figure 58.</li> </ul> |

| 0        | 07/2008 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                               |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, and PowerQUICC, are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QUICC Engine is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2008-2014 Freescale Semiconductor, Inc.

Document Number: MPC8641D Rev. 3 05/2014