Welcome to **E-XFL.COM**

## **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e600                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 994-BCBGA, FCCBGA                                                       |

| Supplier Device Package         | 994-FCCBGA (33x33)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc8641tvu1333jc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- DDR memory controllers

- Dual 64-bit memory controllers (72-bit with ECC)

- Support of up to a 300-MHz clock rate and a 600-MHz DDR2 SDRAM

- Support for DDR, DDR2 SDRAM

- Up to 16 Gbytes per memory controller

- Cache line and page interleaving between memory controllers.

- Serial RapidIO interface unit

- Supports RapidIO Interconnect Specification, Revision 1.2

- Both 1x and 4x LP-Serial link interfaces

- Transmission rates of 1.25-, 2.5-, and 3.125-Gbaud (data rates of 1.0-, 2.0-, and 2.5-Gbps) per lane

- RapidIO-compliant message unit

- RapidIO atomic transactions to the memory controller

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x1, x2, x4, and x8 link widths

- 2.5 Gbaud, 2.0 Gbps lane

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four IEEE 802.3, 802.3u, 802.3x, 802.3z, 802.3ac, 802.3ab-compatible controllers

- Support of the following physical interfaces: MII, RMII, GMII, RGMII, TBI, and RTBI

- Support a full-duplex FIFO mode for high-efficiency ASIC connectivity

- TCP/IP off-load

- Header parsing

- Quality of service support

- VLAN insertion and deletion

- MAC address recognition

- Buffer descriptors are backward compatible with PowerQUICC II and PowerQUICC III programming models

- RMON statistics support

- MII management interface for control and status

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts and 48 internal interrupts

- Eight global high resolution timers/counters that can generate interrupts

- Allows processors to interrupt each other with 32b messages

| Table 1. Absolute Maximum Ratings <sup>1</sup> (continu | ed) |

|---------------------------------------------------------|-----|

|---------------------------------------------------------|-----|

| Characteristic            |                                                                                                                                                                              | Symbol                               | Absolute Maximum<br>Value                                          | Unit | Notes |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|------|-------|

| Input voltage             | DDR and DDR2 SDRAM signals                                                                                                                                                   | D <i>n</i> _MV <sub>IN</sub>         | - 0.3 to (D <i>n</i> _GV <sub>DD</sub> + 0.3)                      | V    | 5     |

|                           | DDR and DDR2 SDRAM reference                                                                                                                                                 | Dn_MV <sub>REF</sub>                 | - 0.3 to (D <i>n</i> _GV <sub>DD</sub> /2 + 0.3)                   | V    | _     |

|                           | Three-speed Ethernet signals                                                                                                                                                 | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to (LV <sub>DD</sub> + 0.3)<br>GND to (TV <sub>DD</sub> + 0.3) | V    | 5     |

|                           | DUART, Local Bus, DMA,<br>Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test,<br>Power management, I <sup>2</sup> C, JTAG and<br>Miscellaneous I/O voltage | OV <sub>IN</sub>                     | GND to (OV <sub>DD</sub> + 0.3)                                    | V    | 5     |

| Storage temperature range | )                                                                                                                                                                            | T <sub>STG</sub>                     | -55 to 150                                                         | °C   | _     |

#### Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Core 1 characteristics apply only to MPC8641D. If two separate power supplies are used for V<sub>DD</sub>\_Core0 and V<sub>DD</sub>\_Core1, they must be kept within 100 mV of each other during normal run time.

- 3. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 4. The 3.63V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 5. During run time (M,L,T,O)V<sub>IN</sub> and D*n*\_MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

# 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8641. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed. For details on order information and specific operating conditions for parts, see Section 21, "Ordering Information."

**Table 2. Recommended Operating Conditions**

| Characteristic                            | Symbol                                            | Recommended<br>Value | Unit | Notes    |

|-------------------------------------------|---------------------------------------------------|----------------------|------|----------|

| Cores supply voltages                     | V <sub>DD</sub> _Core0,                           | 1.10 ± 50 mV         | V    | 1, 2, 8  |

|                                           | V <sub>DD</sub> Core1                             | 1.05 ± 50 mV         |      | 1, 2, 7  |

|                                           |                                                   | 0.95 ± 50 mV         |      | 1, 2, 12 |

| Cores PLL supply                          | AV <sub>DD</sub> Core0,<br>AV <sub>DD</sub> Core1 | 1.10 ± 50 mV         | V    | 8, 13    |

|                                           |                                                   | 1.05 ± 50 mV         |      | 7, 13    |

|                                           |                                                   | 0.95 ± 50 mV         |      | 12, 13   |

| SerDes Transceiver Supply (Ports 1 and 2) | SV <sub>DD</sub>                                  | 1.10 ± 50 mV         | V    | 8, 11    |

|                                           |                                                   | 1.05 ± 50 mV         |      | 7, 11    |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Table 3. Output Drive Capability**

| Driver Type                                                                                                                               | Programmable Output Impedance (Ω) | Supply<br>Voltage                    | Notes   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|---------|

| DDR1 signal                                                                                                                               | 18<br>36 (half strength mode)     | D <i>n</i> _GV <sub>DD</sub> = 2.5 V | 4, 9    |

| DDR2 signal                                                                                                                               | 18<br>36 (half strength mode)     | D <i>n</i> _GV <sub>DD</sub> = 1.8 V | 1, 5, 9 |

| Local Bus signals                                                                                                                         | 45<br>25                          | OV <sub>DD</sub> = 3.3 V             | 2, 6    |

| eTSEC/10/100 signals                                                                                                                      | 45                                | T/LV <sub>DD</sub> = 3.3 V           | 6       |

|                                                                                                                                           | 30                                | T/LV <sub>DD</sub> = 2.5 V           | 6       |

| DUART, DMA, Multiprocessor Interrupts, System<br>Control & Clocking, Debug, Test, Power management,<br>JTAG and Miscellaneous I/O voltage | 45                                | OV <sub>DD</sub> = 3.3 V             | 6       |

| I <sup>2</sup> C                                                                                                                          | 150                               | OV <sub>DD</sub> = 3.3 V             | 7       |

| SRIO, PCI Express                                                                                                                         | 100                               | SV <sub>DD</sub> = 1.1/1.05 V        | 3, 8    |

#### Notes:

- 1. See the DDR Control Driver registers in the MPC8641D reference manual for more information.

- 2. Only the following local bus signals have programmable drive strengths: LALE, LAD[0:31], LDP[0:3], LA[27:31], LCKE, LCS[1:2], LWE[0:3], LGPL1, LGPL2, LGPL3, LGPL4, LGPL5, LCLK[0:2]. The other local bus signals have a fixed drive strength of 45 Ω. See the POR Impedance Control register in the MPC8641D reference manual for more information about local bus signals and their drive strength programmability.

- 3. See Section 17, "Signal Listings," for details on resistor requirements for the calibration of SD*n\_*IMP\_CAL\_TX and SD*n\_*IMP\_CAL\_RX transmit and receive signals.

- 4. Stub Series Terminated Logic (SSTL-25) type pins.

- 5. Stub Series Terminated Logic (SSTL-18) type pins.

- 6. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 7. Open Drain type pins.

- 8. Low Voltage Differential Signaling (LVDS) type pins.

- 9. The drive strength of the DDR interface in half strength mode is at  $T_i = 105C$  and at  $Dn_GV_{DD}$  (min).

# 2.2 Power Up/Down Sequence

The MPC8641 requires its power rails to be applied in a specific sequence in order to ensure proper device operation.

## NOTE

The recommended maximum ramp up time for power supplies is 20 milliseconds.

The chronological order of power up is as follows:

1. All power rails other than DDR I/O ( $Dn_GV_{DD}$ , and  $Dn_MV_{REF}$ ).

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# 4 Input Clocks

Table 7 provides the system clock (SYSCLK) DC specifications for the MPC8641.

Table 7. SYSCLK DC Electrical Characteristics (OVDD = 3.3 V ± 165 mV)

| Parameter                                                                               | Symbol          | Min  | Max                    | Unit |

|-----------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                                                | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                 | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current (V <sub>IN</sub> <sup>1</sup> = 0 V or V <sub>IN</sub> = V <sub>DD)</sub> | I <sub>IN</sub> | _    | ±5                     | μА   |

#### Note:

# 4.1 System Clock Timing

Table 8 provides the system clock (SYSCLK) AC timing specifications for the MPC8641.

## **Table 8. SYSCLK AC Timing Specifications**

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition       | Symbol                                | Min | Typical | Max    | Unit | Notes |

|---------------------------|---------------------------------------|-----|---------|--------|------|-------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 66  | _       | 166.66 | MHz  | 1     |

| SYSCLK cycle time         | tsysclk                               | 6   | _       | _      | ns   | _     |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2    | ns   | 2     |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | _       | 60     | %    | 3     |

| SYSCLK jitter             | _                                     | _   | _       | 150    | ps   | 4, 5  |

## Notes:

- 1. Caution: The MPX clock to SYSCLK ratio and e600 core to MPX clock ratio settings must be chosen such that the resulting SYSCLK frequency, e600 (core) frequency, and MPX clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 18.2, "MPX to SYSCLK PLL Ratio," and Section 18.3, "e600 to MPX clock PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the short term jitter only and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter. Note that the frequency modulation for SYSCLK reduces significantly for the spread spectrum source case. This is to guarantee what is supported based on design.

# 4.1.1 SYSCLK and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 8 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

<sup>1.</sup> Note that the symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

#### **Input Clocks**

should meet the MPC8641 input cycle-to-cycle jitter requirement. Frequency modulation and spread are separate concerns, and the MPC8641 is compatible with spread spectrum sources if the recommendations listed in Table 9 are observed.

**Table 9. Spread Spectrum Clock Source Recommendations**

At recommended operating conditions. See Table 2.

| Parameter            | Min | Max | Unit | Notes |

|----------------------|-----|-----|------|-------|

| Frequency modulation | _   | 50  | kHz  | 1     |

| Frequency spread     | _   | 1.0 | %    | 1, 2  |

## Notes:

- 1. Guaranteed by design.

- 2. SYSCLK frequencies resulting from frequency spreading, and the resulting core and VCO frequencies, must meet the minimum and maximum specifications given in Table 8.

It is imperative to note that the processor's minimum and maximum SYSCLK, core, and VCO frequencies must not be exceeded regardless of the type of clock source. Therefore, systems in which the processor is operated at its maximum rated e600 core frequency should avoid violating the stated limits by using down-spreading only.

$SDn_REF_CLK$  and  $\overline{SDn_REF_CLK}$  was designed to work with a spread spectrum clock (+0 to 0.5% spreading at 30–33kHz rate is allowed), assuming both ends have same reference clock. For better results use a source without significant unintended modulation.

# 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (MPX clock). The output of the sampling latch is then used as an input to the counters of the PIC. There is no jitter specification. The minimum pulse width of the RTC signal should be greater than 2x the period of the MPX clock. That is, minimum clock high time is  $2 \times t_{MPX}$ , and minimum clock low time is  $2 \times t_{MPX}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

# 4.3 eTSEC Gigabit Reference Clock Timing

Table 10 provides the eTSEC gigabit reference clocks (EC1\_GTX\_CLK125 and EC2\_GTX\_CLK125) AC timing specifications for the MPC8641.

Table 10. ECn\_GTX\_CLK125 AC Timing Specifications

| Parameter/Condition                | Symbol              | Min | Typical         | Max | Unit | Notes |

|------------------------------------|---------------------|-----|-----------------|-----|------|-------|

| ECn_GTX_CLK125 frequency           | f <sub>G125</sub>   | _   | 125 ±100<br>ppm | _   | MHz  | 3     |

| ECn_GTX_CLK125 cycle time          | t <sub>G125</sub>   | _   | 8               | _   | ns   | _     |

| ECn_GTX_CLK125 peak-to-peak jitter | t <sub>G125</sub> J | _   | _               | 250 | ps   | 1     |

## **DDR and DDR2 SDRAM**

Table 15 provides the recommended operating conditions for the DDR SDRAM component(s) when  $Dn_GV_{DD}(typ) = 2.5 \text{ V}$ .

Table 15. DDR SDRAM DC Electrical Characteristics for  $Dn_GV_{DD}$  (typ) = 2.5 V

| Parameter/Condition                             | Symbol Min           |                                      | Max                                  | Unit | Notes |

|-------------------------------------------------|----------------------|--------------------------------------|--------------------------------------|------|-------|

| I/O supply voltage                              | Dn_GV <sub>DD</sub>  | 2.375                                | 2.625                                | V    | 1     |

| I/O reference voltage                           | Dn_MV <sub>REF</sub> | 0.49 × D <i>n</i> _GV <sub>DD</sub>  | 0.51 × D <i>n</i> _GV <sub>DD</sub>  | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>      | D <i>n</i> _MV <sub>REF</sub> - 0.04 | D <i>n</i> _MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>      | D <i>n</i> _MV <sub>REF</sub> + 0.15 | D <i>n</i> _GV <sub>DD</sub> + 0.3   | V    | _     |

| Input low voltage                               | V <sub>IL</sub>      | -0.3                                 | D <i>n</i> _MV <sub>REF</sub> - 0.15 | V    | _     |

| Output leakage current                          | I <sub>OZ</sub>      | -50                                  | 50                                   | μА   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | Іон                  | -16.2                                | _                                    | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>      | 16.2                                 | _                                    | mA   | _     |

## Notes:

- 1.  $Dn_GV_{DD}$  is expected to be within 50 mV of the DRAM  $Dn_GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times Dn_{C}V_{DD}$ , and to track  $Dn_{C}V_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $Dn_{C}V_{REF}$  may not exceed  $\pm 2\%$  of the DC value.

- V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to Dn\_MV<sub>RFF</sub>. This rail should track variations in the DC level of Dn\_MV<sub>RFF</sub>.

- 4. Output leakage is measured with all outputs disabled,  $0 \text{ V} \leq \text{V}_{\text{OUT}} \leq \text{D}n_{\text{DD}}$ .

Table 16 provides the DDR capacitance when  $Dn_GV_{DD}$  (typ)=2.5 V.

Table 16. DDR SDRAM Capacitance for  $Dn_GV_{DD}$  (typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $Dn_GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = Dn_GVDD/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

Table 17 provides the current draw characteristics for MV<sub>REF</sub>.

Table 17. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μΑ   | 1    |

1. The voltage regulator for MV<sub>REF</sub> must be able to supply up to 500  $\mu$ A current.

#### **DUART**

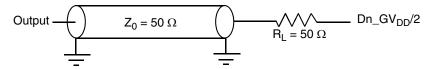

Figure 7 provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8641.

## 7.1 DUART DC Electrical Characteristics

Table 22 provides the DC electrical characteristics for the DUART interface.

**Parameter Symbol** Min Unit 2  $OV_{DD} + 0.3$ ٧ High-level input voltage  $V_{IH}$  $\mathsf{V}_{\mathsf{IL}}$ Low-level input voltage -0.3V 8.0 Input current ±5 μΑ  $I_{IN}$  $(V_{IN}^{1} = 0 \ V \ or \ V_{IN} = V_{DD})$ High-level output voltage ٧  $V_{OH}$  $OV_{DD} - 0.2$  $(OV_{DD} = min, I_{OH} = -100 \mu A)$ Low-level output voltage ٧  $V_{OL}$ 0.2  $(OV_{DD} = min, I_{OL} = 100 \mu A)$

Table 22. DUART DC Electrical Characteristics

#### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 7.2 DUART AC Electrical Specifications

Table 23 provides the AC timing parameters for the DUART interface.

**Table 23. DUART AC Timing Specifications**

| Parameter         | Value               | Unit | Notes |

|-------------------|---------------------|------|-------|

| Minimum baud rate | MPX clock/1,048,576 | baud | 1,2   |

| Maximum baud rate | MPX clock/16        | baud | 1,3   |

| Oversample rate   | 16                  |      | 1,4   |

## Notes:

- 1. Guaranteed by design.

- 2. MPX clock refers to the platform clock.

- 3. Actual attainable baud rate will be limited by the latency of interrupt processing.

- 4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

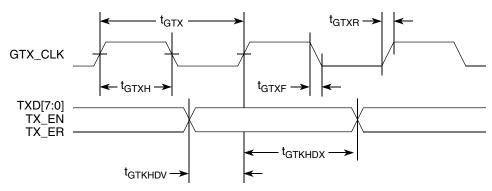

## Table 28. GMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                    | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|----------------------------------------|--------------------------------|-----|-----|-----|------|

| GTX_CLK data clock fall time (80%-20%) | t <sub>GTXF</sub> <sup>2</sup> |     | 1   | 1.0 | ns   |

#### Notes:

- 1. The symbols used for timing specifications herein follow the pattern  $t_{(first\ two\ letters\ of\ functional\ block)(signal)(state)}$  (reference)(state) for inputs and  $t_{(first\ two\ letters\ of\ functional\ block)(reference)(state)(signal)(state)}$  for outputs. For example,  $t_{GTKHDV}$  symbolizes GMII transmit timing (GT) with respect to the  $t_{GTX}$  clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also,  $t_{GTKHDX}$  symbolizes GMII transmit timing (GT) with respect to the  $t_{GTX}$  clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of  $t_{GTX}$  represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Figure 10 shows the GMII transmit AC timing diagram.

Figure 10. GMII Transmit AC Timing Diagram

# 8.2.2.2 GMII Receive AC Timing Specifications

Table 29 provides the GMII receive AC timing specifications.

## **Table 29. GMII Receive AC Timing Specifications**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub> 3                  | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | _   | 60  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.5 | _   | _   | ns   |

| RX_CLK clock rise time (20%-80%)            | t <sub>GRXR</sub> 2                 | _   | _   | 1.0 | ns   |

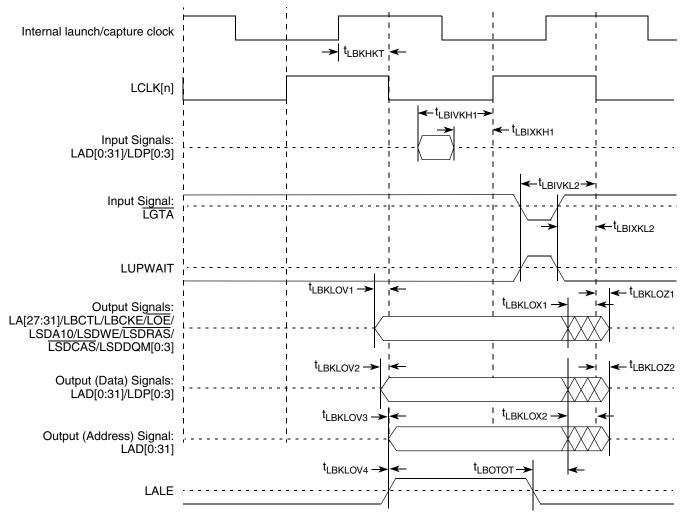

Figure 27. Local Bus Signals (PLL Bypass Mode)

## **NOTE**

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of t<sub>LBKHKT</sub>. In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock, with the exception of the LGTA/LUPWAIT signal, which is captured at the rising edge of the internal clock.

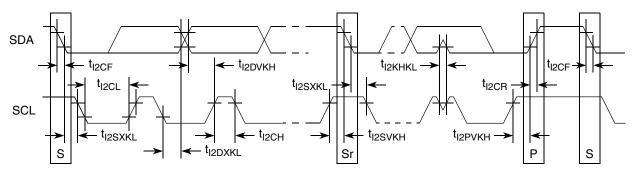

Figure 37 shows the AC timing diagram for the I<sup>2</sup>C bus.

Figure 37. I<sup>2</sup>C Bus AC Timing Diagram

# 13 High-Speed Serial Interfaces (HSSI)

The MPC8641D features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface is dedicated for PCI Express data transfers. The SerDes2 can be used for PCI Express and/or Serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 13.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD $n_TX$  and  $\overline{SD}n_TX$ ) or a receiver input (SD $n_RX$  and  $\overline{SD}n_RX$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

## 1. Single-Ended Swing

The transmitter output signals and the receiver input signals  $SDn_TX$ ,  $\overline{SDn_TX}$ ,  $SDn_RX$  and  $\overline{SDn_RX}$  each have a peak-to-peak swing of A – B Volts. This is also referred as each signal wire's Single-Ended Swing.

## 2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn\_TX} - V_{\overline{SDn\_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage,  $V_{ID}$  (or Differential Input Swing):

## **High-Speed Serial Interfaces (HSSI)**

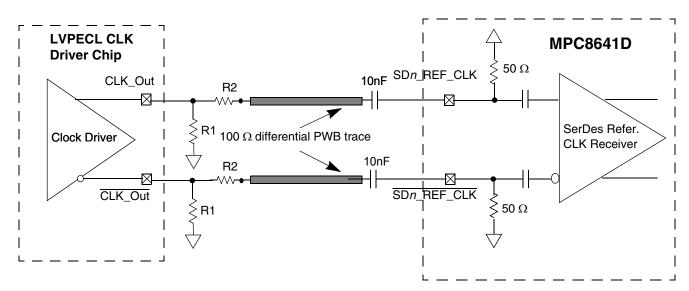

MPC8641D SerDes reference clock input's DC requirement, AC-coupling has to be used. Figure 45 assumes that the LVPECL clock driver's output impedance is  $50 \Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140 \Omega$  to  $240 \Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8641D SerDes reference clock's differential input amplitude requirement (between 200 mV and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires  $R2 = 25 \Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

**PCI Express**

# 14.1 DC Requirements for PCI Express SD*n*\_REF\_CLK and SD*n*\_REF\_CLK

For more information, see Section 13.2, "SerDes Reference Clocks."

# 14.2 AC Requirements for PCI Express SerDes Clocks

Table 48 lists AC requirements.

Table 48. SDn\_REF\_CLK and SDn\_REF\_CLK AC Requirements

| Symbol             | Parameter Description                                                                    |                 | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----------------|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _               | 10      | _   | ns    | _     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _               | _       | 100 | ps    | _     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | <del>-</del> 50 | _       | 50  | ps    | _     |

# 14.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm$  300 ppm tolerance.

# 14.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the Transport and Data Link layer please use the PCI EXPRESS Base Specification. REV. 1.0a document.

# 14.4.1 Differential Transmitter (TX) Output

Table 49 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

Table 49. Differential Transmitter (TX) Output Specifications

| Symbol                   | Parameter                                                   | Min    | Nom  | Max    | Units | Comments                                                                                                                                                                         |

|--------------------------|-------------------------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                       | Unit Interval                                               | 399.88 | 400  | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1.                                                                      |

| V <sub>TX-DIFFp-p</sub>  | Differential<br>Peak-to-Peak<br>Output Voltage              | 0.8    | _    | 1.2    | V     | $V_{TX-DIFFp-p} = 2*IV_{TX-D+} - V_{TX-D-}I$ See Note 2.                                                                                                                         |

| V <sub>TX-DE-RATIO</sub> | De- Emphasized<br>Differential<br>Output Voltage<br>(Ratio) | -3.0   | -3.5 | -4.0   | dB    | Ratio of the $V_{TX\text{-DIFFp-p}}$ of the second and following bits after a transition divided by the $V_{TX\text{-DIFFp-p}}$ of the first bit after a transition. See Note 2. |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

## **PCI Express**

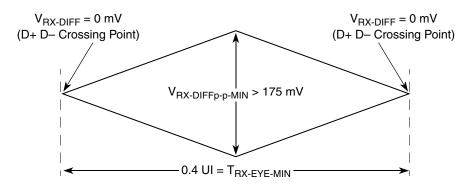

provide additional margin to adequately compensate for the degraded minimum Receiver eye diagram (shown in Figure 51) expected at the input Receiver based on some adequate combination of system simulations and the Return Loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

## NOTE

The reference impedance for return loss measurements is  $50\Omega$  to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with  $50\Omega$  probes—see Figure 52). Note that the series capacitors,  $C_{TX}$ , are optional for the return loss measurement.

Figure 51. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 14.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 52.

## NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

#### **Equalization** 15.4

With the use of high speed serial links, the interconnect media will cause degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eve opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

#### **Explanatory Note on Transmitter and Receiver Specifications** 15.5

AC electrical specifications are given for transmitter and receiver. Long run and short run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to serial RapidIO, as described in Section 8.1. The goal of this standard is that electrical designs for serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

#### 15.6 **Transmitter Specifications**

LP-Serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case shall be better than

- -10 dB for (Baud Frequency)/10 < Freq(f) < 625 MHz, and

- $-10 \text{ dB} + 10\log(f/625 \text{ MHz}) \text{ dB for } 625 \text{ MHz} \leq \text{Freq}(f) \leq \text{Baud Frequency}$

The reference impedance for the differential return loss measurements is 100 Ohm resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%–80% rise/fall time of the transmitter, as measured at the transmitter output, in each case have a minimum value 60 ps.

It is recommended that the timing skew at the output of an LP-Serial transmitter between the two signals that comprise a differential pair not exceed 25 ps at 1.25 GB, 20 ps at 2.50 GB and 15 ps at 3.125 GB.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3 Freescale Semiconductor 79

Package

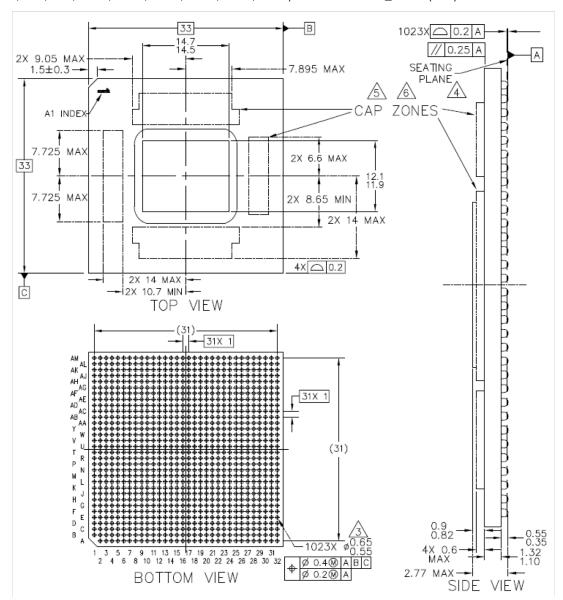

# 16 Package

This section details package parameters and dimensions.

# 16.1 Package Parameters for the MPC8641

The package parameters are as provided in the following list. The package type is  $33 \text{ mm} \times 33 \text{ mm}$ , 1023 pins. There are two package options: high-lead Flip Chip-Ceramic Ball Grid Array (FC-CBGA), and lead-free (FC-CBGA).

For all package types:

Die size  $12.1 \text{ mm} \times 14.7 \text{ mm}$ Package outline  $33 \text{ mm} \times 33 \text{ mm}$

Interconnects 1023

Pitch 1 mm

Total Capacitor count 43 caps; 100 nF each

For high-lead FC-CBGA (package option: HCTE<sup>1</sup> HX)

Maximum module height 2.97 mm Minimum module height 2.47 mm

Solder Balls 89.5% Pb 10.5% Sn

Ball diameter (typical<sup>2</sup>) 0.60 mm

For RoHS lead-free FC-CBGA (package option:  $HCTE^1 VU$ ) and lead-free FC-CBGA (package option:  $HCTE^1 VJ$ )

Maximum module height 2.77 mm

Minimum module height 2.27 mm

Solder Balls 95.5% Sn 4.0% Ag 0.5% Cu

Ball diameter (typical<sup>2</sup>) 0.60 mm

<sup>&</sup>lt;sup>1</sup> High-coefficient of thermal expansion

<sup>&</sup>lt;sup>2</sup> Typical ball diameter is before reflow

#### **Package**

Note that for MPC8641 (single core) the solder balls for the following signals/pins are not populated in the package: VDD\_Core1 (R16, R18, R20, T17, T19, T21, T23, U16, U18, U22, V17, V19, V21, V23, W16, W18, W20, W22, Y17, Y19, Y21, Y23, AA16, AA18, AA20, AA22, AB23, AC24) and SENSEVDD\_Core1 (U20).

Figure 58. MPC8641D Lead-Free FC-CBGA Dimensions

## **NOTES for Figure 58**

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- Caution must be taken not to short capacitors or expose metal capacitor pads on package top.

- 7. All dimensions symmetrical about centerlines unless otherwise specified.

- 8. Note that for MPC8641 (single core) the solder balls for the following signals/pins are not populated in the package: VDD\_Core1 (R16, R18, R20, T17, T19, T21, T23, U16, U18, U22, V17, V19, V21, V23, W16, W18, W20, W22, Y17, Y19, Y21, Y23, AA16, AA18, AA20, AA22, AB23, AC24) and SENSEVDD\_Core1 (U20).

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# 17 Signal Listings

Table 63 provides the pin assignments for the signals. Notes for the signal changes on the single core device (MPC8641) are italicized and prefixed by "S".

Table 63. MPC8641 Signal Reference by Functional Block

| Name <sup>1</sup>                             | Package Pin Number                                                                                                                                                                                                                                                                                                                      | Pin Type                           | Power Supply           | Notes |  |  |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------|-------|--|--|--|--|

| DDR Memory Interface 1 Signals <sup>2,3</sup> |                                                                                                                                                                                                                                                                                                                                         |                                    |                        |       |  |  |  |  |

| D1_MDQ[0:63]                                  | D15, A14, B12, D12, A15, B15, B13, C13, C11, D11, D9, A8, A12, A11, A9, B9, F11, G12, K11, K12, E10, E9, J11, J10, G8, H10, L9, L7, F10, G9, K9, K8, AC6, AC7, AG8, AH9, AB6, AB8, AE9, AF9, AL8, AM8, AM10, AK11, AH8, AK8, AJ10, AK10, AL12, AJ12, AL14, AM14, AL11, AM11, AM13, AK14, AM15, AJ16, AK18, AL18, AJ15, AL15, AL17, AM17 | I/O                                | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MECC[0:7]                                  | M8, M7, R8, T10, L11, L10, P9, R10                                                                                                                                                                                                                                                                                                      | I/O                                | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MDM[0:8]                                   | C14, A10, G11, H9, AD7, AJ9, AM12, AK16, N10                                                                                                                                                                                                                                                                                            | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MDQS[0:8]                                  | A13, C10, H12, J7, AE8, AM9, AK13, AK17, N9                                                                                                                                                                                                                                                                                             | I/O                                | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MDQS[0:8]                                  | D14, B10, H13, J8, AD8, AL9, AJ13, AM16, P10                                                                                                                                                                                                                                                                                            | I/O                                | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MBA[0:2]                                   | AA8, AA10, T9                                                                                                                                                                                                                                                                                                                           | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MA[0:15]                                   | Y10, W8, W9, V7, V8, U6, V10, U9, U7, U10, Y9, T6, T8, AE12, R7, P6                                                                                                                                                                                                                                                                     | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MWE                                        | AB11                                                                                                                                                                                                                                                                                                                                    | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MRAS                                       | AB12                                                                                                                                                                                                                                                                                                                                    | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MCAS                                       | AC10                                                                                                                                                                                                                                                                                                                                    | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MCS[0:3]                                   | AB9, AD10, AC12, AD11                                                                                                                                                                                                                                                                                                                   | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MCKE[0:3]                                  | P7, M10, N8, M11                                                                                                                                                                                                                                                                                                                        | 0                                  | D1_GV <sub>DD</sub>    | 23    |  |  |  |  |

| D1_MCK[0:5]                                   | W6, E13, AH11, Y7, F14, AG10                                                                                                                                                                                                                                                                                                            | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MCK[0:5]                                   | Y6, E12, AH12, AA7, F13, AG11                                                                                                                                                                                                                                                                                                           | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MODT[0:3]                                  | AC9, AF12, AE11, AF10                                                                                                                                                                                                                                                                                                                   | 0                                  | D1_GV <sub>DD</sub>    | _     |  |  |  |  |

| D1_MDIC[0:1]                                  | E15, G14                                                                                                                                                                                                                                                                                                                                | Ю                                  | D1_GV <sub>DD</sub>    | 27    |  |  |  |  |

| D1_MV <sub>REF</sub>                          | AM18                                                                                                                                                                                                                                                                                                                                    | DDR Port 1<br>reference<br>voltage | D1_GV <sub>DD</sub> /2 | 3     |  |  |  |  |

|                                               | DDR Memory Interface 2                                                                                                                                                                                                                                                                                                                  | Signals <sup>2,3</sup>             |                        |       |  |  |  |  |

## **Signal Listings**

# Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>               | Package Pin Number                                | Pin Type         | Power Supply     | Notes    |

|---------------------------------|---------------------------------------------------|------------------|------------------|----------|

| TSEC1_TXD[0:7]/<br>GPOUT[0:7]   | AF25, AC23,AG24, AG23, AE24, AE23,<br>AE22, AD22  | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC1_TX_EN                     | AB22                                              | 0                | LV <sub>DD</sub> | 36       |

| TSEC1_TX_ER                     | AH26                                              | 0                | LV <sub>DD</sub> | _        |

| TSEC1_TX_CLK                    | AC22                                              | I                | LV <sub>DD</sub> | 40       |

| TSEC1_GTX_CLK                   | AH25                                              | 0                | LV <sub>DD</sub> | 41       |

| TSEC1_CRS                       | AM24                                              | I/O              | LV <sub>DD</sub> | 37       |

| TSEC1_COL                       | AM25                                              | I                | LV <sub>DD</sub> | _        |

| TSEC1_RXD[0:7]/<br>GPIN[0:7]    | AL25, AL24, AK26, AK25, AM26, AF26,<br>AH24, AG25 | I                | LV <sub>DD</sub> | 10       |

| TSEC1_RX_DV                     | AJ24                                              | I                | LV <sub>DD</sub> | _        |

| TSEC1_RX_ER                     | AJ25                                              | I                | LV <sub>DD</sub> | _        |

| TSEC1_RX_CLK                    | AK24                                              | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 2 Sign                                 | als <sup>5</sup> | <u> </u>         |          |

| TSEC2_TXD[0:3]/<br>GPOUT[8:15]  | AB20, AJ23, AJ22, AD19                            | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TXD[4]/<br>GPOUT[12]      | AH23                                              | 0                | LV <sub>DD</sub> | 6,10, 38 |

| TSEC2_TXD[5:7]/<br>GPOUT[13:15] | AH21, AG22, AG21                                  | 0                | LV <sub>DD</sub> | 6, 10    |

| TSEC2_TX_EN                     | AB21                                              | 0                | LV <sub>DD</sub> | 36       |

| TSEC2_TX_ER                     | AB19                                              | 0                | LV <sub>DD</sub> | 6, 38    |

| TSEC2_TX_CLK                    | AC21                                              | I                | LV <sub>DD</sub> | 40       |

| TSEC2_GTX_CLK                   | AD20                                              | 0                | LV <sub>DD</sub> | 41       |

| TSEC2_CRS                       | AE20                                              | I/O              | LV <sub>DD</sub> | 37       |

| TSEC2_COL                       | AE21                                              | I                | LV <sub>DD</sub> | _        |

| TSEC2_RXD[0:7]/<br>GPIN[8:15]   | AL22, AK22, AM21, AH20, AG20, AF20,<br>AF23, AF22 | ı                | LV <sub>DD</sub> | 10       |

| TSEC2_RX_DV                     | AC19                                              | I                | LV <sub>DD</sub> | _        |

| TSEC2_RX_ER                     | AD21                                              | I                | LV <sub>DD</sub> | _        |

| TSEC2_RX_CLK                    | AM22                                              | I                | LV <sub>DD</sub> | 40       |

|                                 | eTSEC Port 3 Sign                                 | als <sup>5</sup> | -                |          |

| TSEC3_TXD[0:3]                  | AL21, AJ21, AM20, AJ20                            | 0                | TV <sub>DD</sub> | 6        |

| TSEC3_TXD[4]/                   | AM19                                              | 0                | TV <sub>DD</sub> | _        |

| TSEC3_TXD[5:7]                  | AK21, AL20, AL19                                  | 0                | TV <sub>DD</sub> | 6        |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>                             | Package Pin Number                                                                                                                    | Pin Type                                                   | Power Supply     | Notes |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|-------|

| AGND_SRDS1                                    | P30                                                                                                                                   | SerDes Port 1<br>Ground pin for<br>AV <sub>DD</sub> _SRDS1 | _                | _     |

| AGND_SRDS2                                    | AF30                                                                                                                                  | SerDes Port 2<br>Ground pin for<br>AV <sub>DD</sub> SRDS2  | _                | _     |

| SGND                                          | H28, H32, J30, K31, L28, L29, M32, N30, R29, T32, U30, V31, W29, Y32 AA30, AB31, AC29, AD32, AE30, AG29, AH32, AJ30, AK31, AL29, AM32 | Ground pins for SV <sub>DD</sub>                           | _                | _     |

| XGND                                          | K27, L25, M26, N24, P27, R25, T26, U24,<br>V27, W25, Y28, AA24, AB27, AC25, AD28,<br>AE26, AF27, AH28, AJ26, AK27, AL26,<br>AM28      | Ground pins for XV <sub>DD</sub> _SRDS <i>n</i>            | _                | _     |

|                                               | Reset Configuration Si                                                                                                                | gnals <sup>20</sup>                                        |                  |       |

| TSEC1_TXD[0] / cfg_alt_boot_vec               | AF25                                                                                                                                  | _                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[1]/<br>cfg_platform_freq            | AC23                                                                                                                                  | _                                                          | LV <sub>DD</sub> | 21    |

| TSEC1_TXD[2:4]/<br>cfg_device_id[5:7]         | AG24, AG23, AE24                                                                                                                      | _                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[5]/<br>cfg_tsec1_reduce             | AE23                                                                                                                                  | _                                                          | LV <sub>DD</sub> | _     |

| TSEC1_TXD[6:7]/<br>cfg_tsec1_prtcl[0:1]       | AE22, AD22                                                                                                                            | _                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[0:3]/<br>cfg_rom_loc[0:3]           | AB20, AJ23, AJ22, AD19                                                                                                                | _                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[4], TSEC2_TX_ER/ cfg_dram_type[0:1] | AH23,<br>AB19                                                                                                                         | _                                                          | LV <sub>DD</sub> | 38    |

| TSEC2_TXD[5]/<br>cfg_tsec2_reduce             | AH21                                                                                                                                  | _                                                          | LV <sub>DD</sub> | _     |

| TSEC2_TXD[6:7]/<br>cfg_tsec2_prtcl[0:1]       | AG22, AG21                                                                                                                            | _                                                          | LV <sub>DD</sub> | _     |

| TSEC3_TXD[0:1]/<br>cfg_spare[0:1]             | AL21, AJ21                                                                                                                            | 0                                                          | TV <sub>DD</sub> | 33    |

| TSEC3_TXD[2]/<br>cfg_core1_enable             | AM20                                                                                                                                  | 0                                                          | TV <sub>DD</sub> | _     |

| TSEC3_TXD[3]/<br>cfg_core1_lm_offset          | AJ20                                                                                                                                  | _                                                          | LV <sub>DD</sub> | _     |

| TSEC3_TXD[5]/<br>cfg_tsec3_reduce             | AK21                                                                                                                                  | _                                                          | LV <sub>DD</sub> | _     |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# 18.4.1 SYSCLK to Platform Frequency Options

Table 70 shows some SYSCLK frequencies and the expected MPX frequency values based on the MPX clock to SYSCLK ratio. Note that frequencies between 400 MHz and 500 MHz are NOT supported on the platform. See note regarding *cfg\_platform\_freq* in Section 17, "Signal Listings," because it is a reset configuration pin that is related to platform frequency.

MPX to **SYSCLK** SYSCLK (MHz) Ratio 66 83 100 111 133 167 Platform/MPX Frequency (MHz)<sup>1</sup> 2 3 400 500 4 400 533 5 555 500 400 500 6 600

Table 70. Frequency Options of SYSCLK with Respect to Platform/MPX Clock Speed

## 18.4.2 Platform to FIFO Restrictions

8

9

533

600

Please note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency <= platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 127 MHz

For FIFO encoded mode:

FIFO TX/RX clock frequency <= platform clock frequency/3.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

SYSCLK frequency range is 66-167 MHz. Platform clock/ MPX frequency range is 400 MHz, 500-600 MHz.