Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Core Processor                  | PowerPC e600                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.333GHz                                                    |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 994-BCBGA, FCCBGA                                           |

| Supplier Device Package         | 994-FCCBGA (33x33)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc8641vu1333je |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

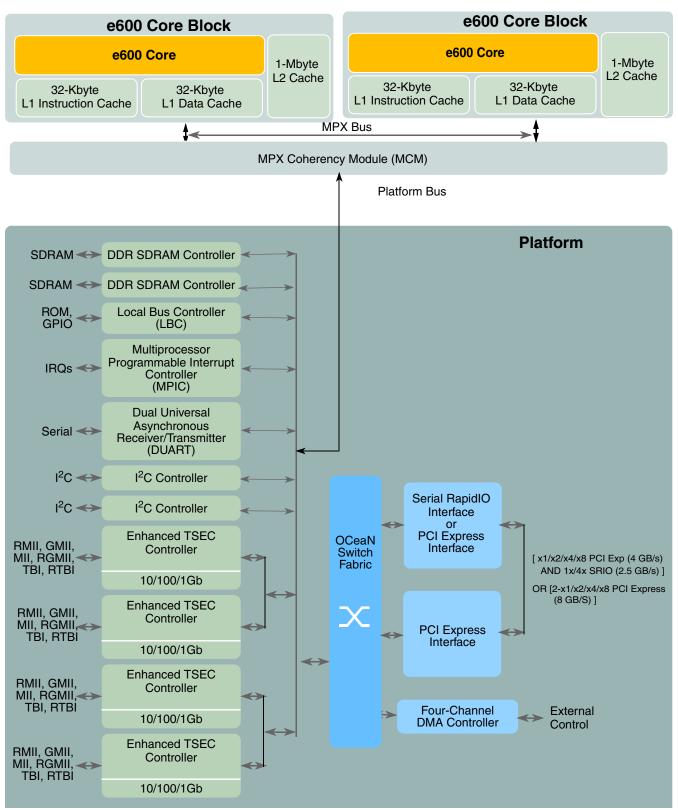

Figure 1. MPC8641 and MPC8641D

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

- Support for PCI-Express message-shared interrupts (MSIs)

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and the remote masters

- Supports transfers to or from any local memory or I/O port

- Ability to start and flow control each DMA channel from external 3-pin interface

- Device performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the 8 counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- Dual I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- IEEE 1149.1-compatible, JTAG boundary scan

- Available as 1023 pin Hi-CTE flip chip ceramic ball grid array (FC-CBGA)

**Power Characteristics**

#### **Power Characteristics** 3

The power dissipation for the dual core MPC8641D device is shown in Table 4.

Table 4. MPC8641D Power Dissipation (Dual Core)

| Power Mode | Core Frequency<br>(MHz) | Platform<br>Frequency (MHz) | V <sub>DD</sub> _Coren,<br>V <sub>DD</sub> _PLAT<br>(Volts) | Junction<br>Temperature | Power<br>(Watts) | Notes   |

|------------|-------------------------|-----------------------------|-------------------------------------------------------------|-------------------------|------------------|---------|

| Typical    |                         |                             |                                                             | 65 °C                   | 32.1             | 1, 2    |

| Thermal    | 1500 MHz                | 600 MHz                     | 1.1 V                                                       |                         | 43.4             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 49.9             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 23.9             | 1, 2    |

| Thermal    | 1333 MHz                | 533 MHz                     | 1.05 V                                                      |                         | 30.0             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 34.1             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 23.9             | 1, 2    |

| Thermal    | 1250 MHz                | 500 MHz                     | 1.05 V                                                      |                         | 30.0             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 34.1             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 23.9             | 1, 2    |

| Thermal    | 1000 MHz                | 400 MHz                     | 1.05 V                                                      | 0.5                     | 30.0             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 34.1             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 16.2             | 1, 2, 5 |

| Thermal    | 1000 MHz                | 500 MHz                     | 0.95 V,<br>1.05 V                                           | 107.00                  | 21.8             | 1, 3, 5 |

| Maximum    | ]                       |                             |                                                             | 105 °C                  | 25.0             | 1, 4, 5 |

#### Notes:

- 1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- 2. Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>Coren) and 65°C junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz with one core at 100% efficiency and the second core at 65% efficiency.

- 3. Thermal power is the average power measured at nominal core voltage (VDD\_Coren) and maximum operating junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz on both cores and a typical workload on platform interfaces.

- 4. Maximum power is the maximum power measured at nominal core voltage (VDD\_Coren) and maximum operating junction temperature (see Table 2) while running a test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep all the execution units maximally busy on both cores.

- 5. These power numbers are for Part Number MC8641Dxx1000NX only.  $V_{DD}$ \_Core n = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3 14 Freescale Semiconductor

#### **Power Characteristics**

The power dissipation for the MPC8641 single core device is shown in Table 6.

Table 6. MPC8641 Power Dissipation (Single Core)

| Power Mode | Core Frequency<br>(MHz) | Platform<br>Frequency (MHz) | V <sub>DD</sub> _Coren,<br>V <sub>DD</sub> _PLAT<br>(Volts) | Junction<br>Temperature | Power<br>(Watts) | Notes   |

|------------|-------------------------|-----------------------------|-------------------------------------------------------------|-------------------------|------------------|---------|

| Typical    |                         |                             |                                                             | 65 °C                   | 20.3             | 1, 2    |

| Thermal    | 1500 MHz                | 600 MHz                     | 1.1 V                                                       |                         | 25.2             | 1, 3    |

| Maxim      |                         |                             |                                                             | 105 °C                  | 28.9             | 1, 4    |

| Typical    |                         |                             |                                                             | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1333 MHz                | 533 MHz                     | 1.05 V                                                      |                         | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    | 4050 141                |                             | 4.05.14                                                     | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1250 MHz                | 500 MHz                     | 1.05 V                                                      |                         | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    | 4000 1411               | 400 144                     | 4.05.14                                                     | 65 °C                   | 16.3             | 1, 2    |

| Thermal    | 1000 MHz                | 400 MHz                     | 1.05 V                                                      |                         | 20.2             | 1, 3    |

| Maximum    |                         |                             |                                                             | 105 °C                  | 23.2             | 1, 4    |

| Typical    | 4000 141                | 500 141                     | 0.05.17                                                     | 65 °C                   | 11.6             | 1, 2, 5 |

| Thermal    | 1000 MHz                | 500 MHz                     | 0.95 V,<br>1.05 V                                           | 10= 00                  | 14.4             | 1, 3, 5 |

| Maximum    |                         |                             |                                                             | 105 °C                  | 16.5             | 1, 4, 5 |

### Notes:

- 1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- 2. Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>\_Core*n*) and 65°C junction temperature (see Table 2)while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz.

- 3. Thermal power is the average power measured at nominal core voltage (V<sub>DD</sub>\_Core*n*) and maximum operating junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz and a typical workload on platform interfaces.

- 4. Maximum power is the maximum power measured at nominal core voltage (V<sub>DD</sub>\_Coren) and maximum operating junction temperature (see Table 2) while running a test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep all the execution units maximally busy.

- 5. These power numbers are for Part Number MC8641xx1000NX only.  $V_{DD}$ \_Core n = 0.95 V and  $V_{DD}$ \_PLAT = 1.05 V.

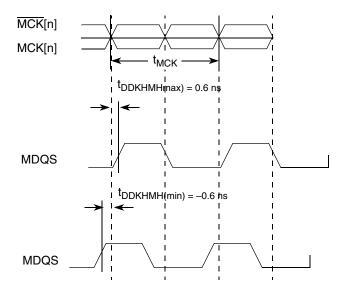

Figure 5 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (tDDKHMH).

Figure 5. Timing Diagram for tDDKHMH

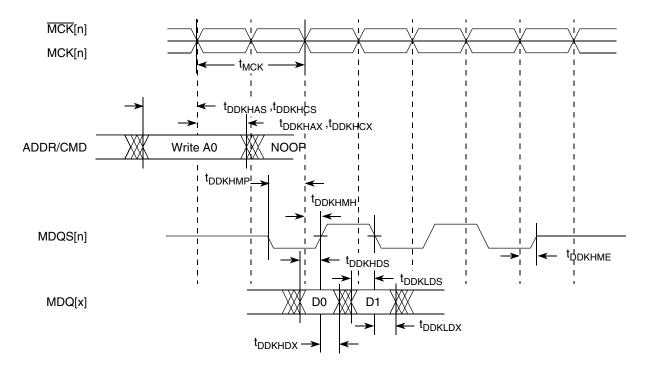

Figure 6 shows the DDR SDRAM output timing diagram.

Figure 6. DDR SDRAM Output Timing Diagram

clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 18.4.2, "Platform to FIFO Restrictions."

#### NOTE

The phase between the output clocks TSEC1\_GTX\_CLK and TSEC2\_GTX\_CLK (ports 1 and 2) is no more than 100 ps. The phase between the output clocks TSEC3\_GTX\_CLK and TSEC4\_GTX\_CLK (ports 3 and 4) is no more than 100 ps.

A summary of the FIFO AC specifications appears in Table 26 and Table 27.

### **Table 26. FIFO Mode Transmit AC Timing Specification**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                                    | Symbol                              | Min | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK clock period (GMII mode)               | t <sub>FIT</sub>                    | 7.0 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK clock period (Encoded mode)            | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK duty cycle                             | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55   | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>                   | _   | _   | 250  | ps   |

| Rise time TX_CLK (20%–80%)                             | t <sub>FITR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>                   | _   | _   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub>                  | 2.0 | _   | _    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub>                  | 0.5 | _   | 3.0  | ns   |

### **Table 27. FIFO Mode Receive AC Timing Specification**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% and 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol                              | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period (GMII mode)             | t <sub>FIR</sub> 1                  | 7.0 | 8.0 | 100  | ns   |

| RX_CLK clock period (Encoded mode)          | t <sub>FIR</sub> 1                  | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | _   | _   | 250  | ps   |

| Rise time RX_CLK (20%–80%)                  | t <sub>FIRR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | _   | _   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | _   | _    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 | _   | _    | ns   |

<sup>±100</sup> ppm tolerance on RX\_CLK frequency

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

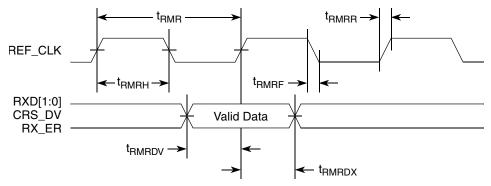

### 8.2.7.2 RMII Receive AC Timing Specifications

### **Table 37. RMII Receive AC Timing Specifications**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                                       | Symbol <sup>1</sup>                 | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|-------------------------------------|------|------|------|------|

| REF_CLK clock period                                      | t <sub>RMR</sub>                    | 15.0 | 20.0 | 25.0 | ns   |

| REF_CLK duty cycle                                        | t <sub>RMRH</sub> /t <sub>RMR</sub> | 35   | 50   | 65   | %    |

| REF_CLK peak-to-peak jitter                               | t <sub>RMRJ</sub>                   | _    | _    | 250  | ps   |

| Rise time REF_CLK (20%–80%)                               | t <sub>RMRR</sub>                   | 1.0  | _    | 2.0  | ns   |

| Fall time REF_CLK (80%–20%)                               | t <sub>RMRF</sub>                   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>                  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>                  | 2.0  | _    | _    | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

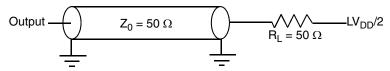

Figure 21 provides the AC test load for eTSEC.

Figure 21. eTSEC AC Test Load

Figure 22 shows the RMII receive AC timing diagram.

Figure 22. RMII Receive AC Timing Diagram

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

I<sup>2</sup>C

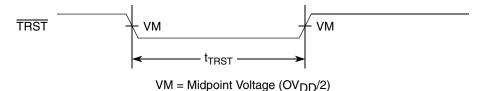

Figure 34 provides the TRST timing diagram.

Figure 34. TRST Timing Diagram

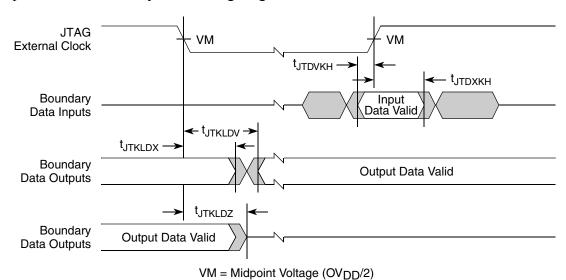

Figure 35 provides the boundary-scan timing diagram.

Figure 35. Boundary-Scan Timing Diagram

# 12 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8641.

# 12.1 I<sup>2</sup>C DC Electrical Characteristics

Table 45 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

Table 45. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter                                                                                                              | Symbol              | Min                                | Max                                | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                               | V <sub>IH</sub>     | $0.7 \times \text{OV}_{\text{DD}}$ | OV <sub>DD</sub> + 0.3             | V    | _     |

| Input low voltage level                                                                                                | V <sub>IL</sub>     | -0.3                               | $0.3 \times \text{OV}_{\text{DD}}$ | V    | _     |

| Low level output voltage                                                                                               | V <sub>OL</sub>     | 0                                  | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                                     | t <sub>I2KHKL</sub> | 0                                  | 50                                 | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times \text{OV}_{DD}$ and $0.9 \times \text{OV}_{DD}$ (max) | I <sub>I</sub>      | -10                                | 10                                 | μΑ   | 3     |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

# Table 45. I<sup>2</sup>C DC Electrical Characteristics (continued)

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter                    | Symbol | Min | Max | Unit | Notes |

|------------------------------|--------|-----|-----|------|-------|

| Capacitance for each I/O pin | CI     | _   | 10  | pF   | _     |

#### Notes:

- 1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. Refer to the MPC8641 Integrated Host Processor Reference Manual for information on the digital filter used.

- 3. I/O pins will obstruct the SDA and SCL lines if  ${\rm OV}_{\rm DD}$  is switched off.

# 12.2 I<sup>2</sup>C AC Electrical Specifications

Table 46 provides the AC timing parameters for the I<sup>2</sup>C interfaces.

## Table 46. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $\rm V_{IH}$  (min) and  $\rm V_{IL}$  (max) levels (see Table 45).

| Parameter                                                                                    | Symbol <sup>1</sup>   | Min                                  | Max              | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>      | 0                                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub> 4   | 1.3                                  | _                | μS   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub> 4   | 0.6                                  | _                | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> 4 | 0.6                                  | _                | μS   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> 4 | 0.6                                  | _                | μS   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> 4 | 100                                  | _                | ns   |

| Data input hold time:  CBUS compatible masters  I <sup>2</sup> C bus devices                 | t <sub>I2DXKL</sub>   |                                      |                  | μS   |

| Rise time of both SDA and SCL signals                                                        | t <sub>I2CR</sub>     | 20 + 0.1 C <sub>B</sub> <sup>5</sup> | 300              | ns   |

| Fall time of both SDA and SCL signals                                                        | t <sub>l2CF</sub>     | 20 + 0.1 C <sub>b</sub> <sup>5</sup> | 300              | ns   |

| Data output delay time                                                                       | t <sub>I2OVKL</sub>   | _                                    | 0.9 <sup>3</sup> | μS   |

| Set-up time for STOP condition                                                               | t <sub>l2PVKH</sub>   | 0.6                                  | _                | μS   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>   | 1.3                                  | _                | μS   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>       | 0.1 × OV <sub>DD</sub>               | _                | V    |

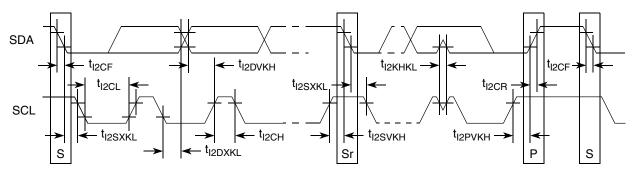

Figure 37 shows the AC timing diagram for the I<sup>2</sup>C bus.

Figure 37. I<sup>2</sup>C Bus AC Timing Diagram

# 13 High-Speed Serial Interfaces (HSSI)

The MPC8641D features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface is dedicated for PCI Express data transfers. The SerDes2 can be used for PCI Express and/or Serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 13.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

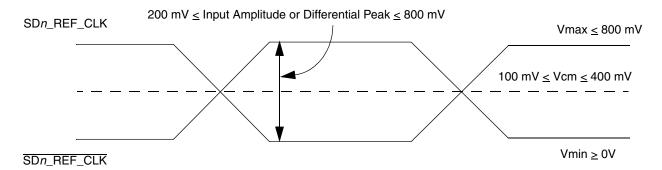

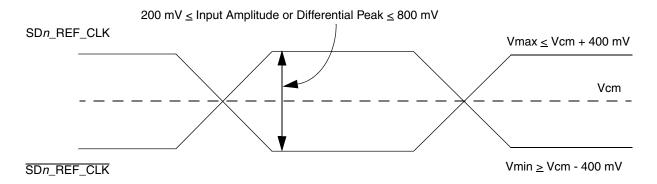

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD $n_TX$  and  $\overline{SD}n_TX$ ) or a receiver input (SD $n_RX$  and  $\overline{SD}n_RX$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals  $SDn_TX$ ,  $\overline{SDn_TX}$ ,  $SDn_RX$  and  $\overline{SDn_RX}$  each have a peak-to-peak swing of A – B Volts. This is also referred as each signal wire's Single-Ended Swing.

### 2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn\_TX} - V_{\overline{SDn\_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

3. Differential Input Voltage,  $V_{ID}$  (or Differential Input Swing):

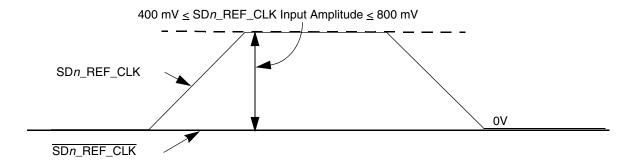

- The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

Figure 41. Differential Reference Clock Input DC Requirements (External AC-Coupled)

Figure 42. Single-Ended Reference Clock Input DC Requirements

**High-Speed Serial Interfaces (HSSI)**

# 13.2.3 Interfacing With Other Differential Signaling Levels

With on-chip termination to SGND, the differential reference clocks inputs are HCSL (High-Speed Current Steering Logic) compatible DC-coupled.

Many other low voltage differential type outputs like LVDS (Low Voltage Differential Signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

### **NOTE**

Figure 43 to Figure 46 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8641D SerDes reference clock receiver requirement provided in this document.

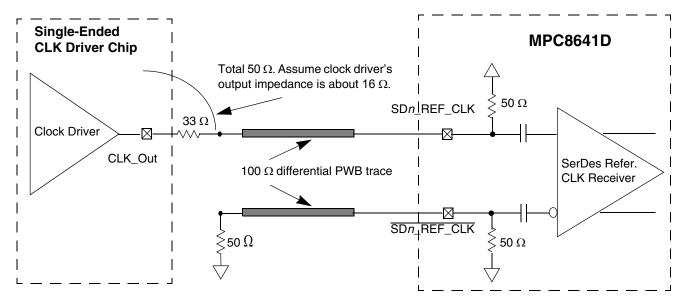

Figure 46 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8641D SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

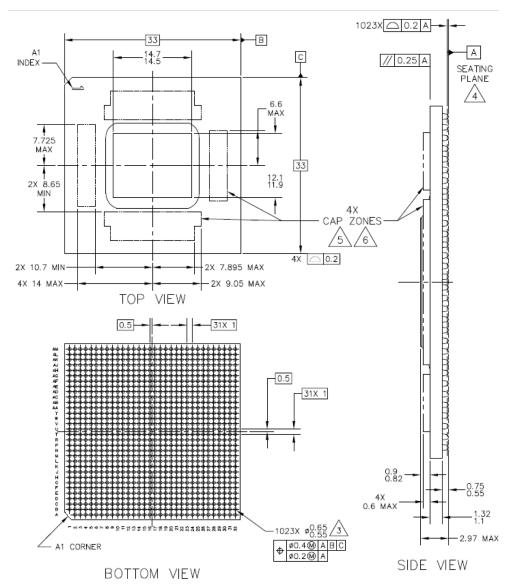

## 16.2 Mechanical Dimensions of the MPC8641 FC-CBGA

The mechanical dimensions and bottom surface nomenclature of the MPC8641D (dual core) and MPC8641 (single core) high-lead FC-CBGA (package option: HCTE HX) and lead-free FC-CBGA (package option: HCTE VU) are shown respectfully in Figure 57 and Figure 58.

Figure 57. MPC8641D High-Head FC-CBGA Dimensions

#### **NOTES for Figure 57**

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or expose metal capacitor pads on package top.

- 7. All dimensions symmetrical about centerlines unless otherwise specified.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

### **Signal Listings**

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>               | Package Pin Number                                | Pin Type         | Power Supply     | Notes    |  |  |  |

|---------------------------------|---------------------------------------------------|------------------|------------------|----------|--|--|--|

| TSEC1_TXD[0:7]/<br>GPOUT[0:7]   | AF25, AC23,AG24, AG23, AE24, AE23,<br>AE22, AD22  | 0                | LV <sub>DD</sub> | 6, 10    |  |  |  |

| TSEC1_TX_EN                     | AB22                                              | 0                | LV <sub>DD</sub> | 36       |  |  |  |

| TSEC1_TX_ER                     | AH26                                              | 0                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC1_TX_CLK                    | AC22                                              | I                | LV <sub>DD</sub> | 40       |  |  |  |

| TSEC1_GTX_CLK                   | AH25                                              | 0                | LV <sub>DD</sub> | 41       |  |  |  |

| TSEC1_CRS                       | AM24                                              | I/O              | LV <sub>DD</sub> | 37       |  |  |  |

| TSEC1_COL                       | AM25                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC1_RXD[0:7]/<br>GPIN[0:7]    | AL25, AL24, AK26, AK25, AM26, AF26,<br>AH24, AG25 | I                | LV <sub>DD</sub> | 10       |  |  |  |

| TSEC1_RX_DV                     | AJ24                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC1_RX_ER                     | AJ25                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC1_RX_CLK                    | AK24                                              | I                | LV <sub>DD</sub> | 40       |  |  |  |

|                                 | eTSEC Port 2 Sign                                 | als <sup>5</sup> | <u> </u>         |          |  |  |  |

| TSEC2_TXD[0:3]/<br>GPOUT[8:15]  | AB20, AJ23, AJ22, AD19                            | 0                | LV <sub>DD</sub> | 6, 10    |  |  |  |

| TSEC2_TXD[4]/<br>GPOUT[12]      | AH23                                              | 0                | LV <sub>DD</sub> | 6,10, 38 |  |  |  |

| TSEC2_TXD[5:7]/<br>GPOUT[13:15] | AH21, AG22, AG21                                  | 0                | LV <sub>DD</sub> | 6, 10    |  |  |  |

| TSEC2_TX_EN                     | AB21                                              | 0                | LV <sub>DD</sub> | 36       |  |  |  |

| TSEC2_TX_ER                     | AB19                                              | 0                | LV <sub>DD</sub> | 6, 38    |  |  |  |

| TSEC2_TX_CLK                    | AC21                                              | I                | LV <sub>DD</sub> | 40       |  |  |  |

| TSEC2_GTX_CLK                   | AD20                                              | 0                | LV <sub>DD</sub> | 41       |  |  |  |

| TSEC2_CRS                       | AE20                                              | I/O              | LV <sub>DD</sub> | 37       |  |  |  |

| TSEC2_COL                       | AE21                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC2_RXD[0:7]/<br>GPIN[8:15]   | AL22, AK22, AM21, AH20, AG20, AF20,<br>AF23, AF22 | ı                | LV <sub>DD</sub> | 10       |  |  |  |

| TSEC2_RX_DV                     | AC19                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC2_RX_ER                     | AD21                                              | I                | LV <sub>DD</sub> | _        |  |  |  |

| TSEC2_RX_CLK                    | AM22                                              | I                | LV <sub>DD</sub> | 40       |  |  |  |

|                                 | eTSEC Port 3 Signals <sup>5</sup>                 |                  |                  |          |  |  |  |

| TSEC3_TXD[0:3]                  | AL21, AJ21, AM20, AJ20                            | 0                | TV <sub>DD</sub> | 6        |  |  |  |

| TSEC3_TXD[4]/                   | AM19                                              | 0                | TV <sub>DD</sub> | _        |  |  |  |

| TSEC3_TXD[5:7]                  | AK21, AL20, AL19                                  | 0                | TV <sub>DD</sub> | 6        |  |  |  |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

### **Signal Listings**

## Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup>              | Package Pin Number                                | Pin Type                           | Power Supply     | Notes            |

|--------------------------------|---------------------------------------------------|------------------------------------|------------------|------------------|

| D1_MDVAL/LB_DVAL               | J16                                               | 0                                  | OV <sub>DD</sub> | 10               |

| D2_MDVAL                       | D19                                               | 0                                  | OV <sub>DD</sub> | _                |

|                                | Power Management S                                | ignals <sup>5</sup>                |                  |                  |

| ASLEEP                         | C19                                               | 0                                  | OV <sub>DD</sub> | _                |

|                                | System Clocking Sig                               | ınals <sup>5</sup>                 |                  |                  |

| SYSCLK                         | G16                                               | ı                                  | OV <sub>DD</sub> | _                |

| RTC                            | K17                                               | ı                                  | OV <sub>DD</sub> | 32               |

| CLK_OUT                        | B16                                               | 0                                  | OV <sub>DD</sub> | 23               |

|                                | Test Signals <sup>5</sup>                         | 1                                  | 1                |                  |

| LSSD_MODE                      | C18                                               | ı                                  | OV <sub>DD</sub> | 26               |

| TEST_MODE[0:3]                 | C16, E17, D18, D16                                | ı                                  | OV <sub>DD</sub> | 26               |

|                                | JTAG Signals <sup>5</sup>                         | 1                                  | 1                |                  |

| TCK                            | H18                                               | I                                  | OV <sub>DD</sub> | _                |

| TDI                            | J18                                               | I                                  | OV <sub>DD</sub> | 24               |

| TDO                            | G18                                               | 0                                  | OV <sub>DD</sub> | 23               |

| TMS                            | F18                                               | I                                  | OV <sub>DD</sub> | 24               |

| TRST                           | A17                                               | ı                                  | OV <sub>DD</sub> | 24               |

|                                | Miscellaneous <sup>5</sup>                        | ;                                  | 1                |                  |

| Spare                          | J17                                               | _                                  | _                | 13               |

| GPOUT[0:7]/<br>TSEC1_TXD[0:7]  | AF25, AC23, AG24, AG23, AE24, AE23, AE22, AD22    | 0                                  | OV <sub>DD</sub> | 6, 10            |

| GPIN[0:7]/<br>TSEC1_RXD[0:7]   | AL25, AL24, AK26, AK25, AM26, AF26,<br>AH24, AG25 | I                                  | OV <sub>DD</sub> | 10               |

| GPOUT[8:15]/<br>TSEC2_TXD[0:7] | AB20, AJ23, AJ22, AD19, AH23, AH21,<br>AG22, AG21 | 0                                  | OV <sub>DD</sub> | 10               |

| GPIN[8:15]/<br>TSEC2_RXD[0:7]  | AL22, AK22, AM21, AH20, AG20, AF20,<br>AF23, AF22 | ı                                  | OV <sub>DD</sub> | 10               |

|                                | Additional Analog Si                              | gnals                              |                  |                  |

| TEMP_ANODE                     | AA11                                              | Thermal                            | _                | _                |

| TEMP_CATHODE                   | Y11                                               | Thermal                            | _                | _                |

|                                | Sense, Power and GND                              | Signals                            | · '              |                  |

| SENSEV <sub>DD</sub> Core0     | M14                                               | V <sub>DD</sub> _Core0 sensing pin | _                | 31               |

| SENSEV <sub>DD</sub> Core1     | U20                                               | V <sub>DD</sub> _Core1 sensing pin | _                | 12,31, <i>S1</i> |

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

#### Table 63. MPC8641 Signal Reference by Functional Block (continued)

| Name <sup>1</sup> | Package Pin Number | Pin Type | Power Supply | Notes |

|-------------------|--------------------|----------|--------------|-------|

|-------------------|--------------------|----------|--------------|-------|

#### Note:

- Multi-pin signals such as D1\_MDQ[0:63] and D2\_MDQ[0:63] have their physical package pin numbers listed in order corresponding to the signal names.

- 2. Stub Series Terminated Logic (SSTL-18 and SSTL-25) type pins.

- 3. If a DDR port is not used, it is possible to leave the related power supply (Dn\_GVDD, Dn\_MVREF) turned off at reset. Note that these power supplies can only be powered up again at reset for functionality to occur on the DDR port.

- 4. Low Voltage Differential Signaling (LVDS) type pins.

- 5. Low Voltage Transistor-Transistor Logic (LVTTL) type pins.

- 6. This pin is a reset configuration pin and appears again in the Reset Configuration Signals section of this table. See the Reset Configuration Signals section of this table for config name and connection details.

- 7. Recommend a weak pull-up resistor (1–10  $k\Omega$ ) be placed from this pin to its power supply.

- 8. Recommend a weak pull-down resistor (2–10  $k\Omega)$  be placed from this pin to ground.

- 9. This multiplexed pin has input status in one mode and output in another

- 10. This pin is a multiplexed signal for different functional blocks and appears more than once in this table.

- 11. This pin is open drain signal.

- 12. Functional only on the MPC8641D.

- 13. These pins should be left floating.

- 14. These pins should be connected to SV<sub>DD</sub>.

- 15. These pins should be pulled to ground with a strong resistor (270- $\Omega$  to 330- $\Omega$ ).

- 16. These pins should be connected to OVDD.

- 17. This is a SerDes PLL/DLL digital test signal and is only for factory use.

- 18. This is a SerDes PLL/DLL analog test signal and is only for factory use.

- 19. This pin should be pulled to ground with a 100- $\Omega$  resistor.

- 20. The pins in this section are reset configuration pins. Each pin has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-k $\Omega$  pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 21. Should be pulled down at reset if platform frequency is at 400 MHz.

- 22. These pins require 4.7-k $\Omega$  pull-up or pull-down resistors and must be driven as they are used to determine PLL configuration ratios at reset.

- 23. This output is actively driven during reset rather than being tri-stated during reset.

- 24 These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 25. This pin should NOT be pulled down (or driven low) during reset.

- 26. These are test signals for factory use only and must be pulled up (100- $\Omega$  to 1-  $k\Omega$ ) to OVDD for normal machine operation.

- 27. Dn\_MDIC[0] should be connected to ground with an  $18-\Omega$  resistor  $+/-1-\Omega$  and Dn\_MDIC[1] should be connected Dn\_GVDD with an  $18-\Omega$  resistor  $+/-1-\Omega$ . These pins are used for automatic calibration of the DDR IOs.

- 28. Pin N18 is recommended as a reference point for determining the voltage of  $V_{DD}$ -PLAT and is hence considered as the  $V_{DD}$ -PLAT sensing voltage and is called SENSEVDD\_PLAT.

- 29. Pin P18 is recommended as the ground reference point for SENSEVDD\_PLAT and is called SENSEVSS\_PLAT.

- 30. This pin should be pulled to ground with a 200- $\Omega$  resistor.

- 31. These pins are connected to the power/ground planes internally and may be used by the core power supply to improve tracking and regulation.

- 32. Must be tied low if unused

- 33. These pins may be used as defined functional reset configuration pins in the future. Please include a resistor pull up/down option to allow flexibility of future designs.

- 34. Used as serial data output for SRIO 1x/4x link.

- 35. Used as serial data input for SRIO 1x/4x link.

- 36. This pin requires an external 4.7-kΩ pull-down resistor to pevent PHY from seeing a valid Transmit Enable before it is actively driven.

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

#### **Thermal**

The Bergquist Company 800-347-4572

18930 West 78<sup>th</sup> St.

Chanhassen, MN 55317

Internet: www.bergquistcompany.com

Chomerics, Inc. 781-935-4850

77 Dragon Ct.

Woburn, MA 01801

Internet: www.chomerics.com

Dow-Corning Corporation 800-248-2481

Corporate Center

PO Box 994

Midland, MI 48686-0994

Internet: www.dowcorning.com

Shin-Etsu MicroSi, Inc. 888-642-7674

10028 S. 51st St. Phoenix, AZ 85044

Internet: www.microsi.com

Thermagon Inc. 888-246-9050

4707 Detroit Ave. Cleveland, OH 44102

Internet: www.thermagon.com

The following section provides a heat sink selection example using one of the commercially available heat sinks.

# 19.2.3 Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_j = T_i + T_r + (R_{\theta JC} + R_{\theta int} + R_{\theta sa}) \times P_d$$

where:

T<sub>j</sub> is the die-junction temperature

T<sub>i</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$R_{\theta JC}$  is the junction-to-case thermal resistance

$R_{\theta int} \, is \, the \, adhesive \, or \, interface \, material \, thermal \, resistance \,$

$R_{\theta sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation, the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_i)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material  $(R_{\theta int})$  is typically about 0.2°C/W. For

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

#### **System Design Information**

The following pins must be connected to GND:

- SDn RX[7:0]

- $\overline{SDn} \overline{RX}[7:0]$

- SDn REF CLK

- SDn REF CLK

### **NOTE**

It is recommended to power down the unused lane through SRDS1CR1[0:7] register (offset = 0xE\_0F08) and SRDS2CR1[0:7] register (offset = 0xE\_0F44.) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

For other directions on reserved or no-connects pins see Section 17, "Signal Listings."

# 20.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8641 requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on all open drain type pins.

The following pins must NOT be pulled down during power-on reset: TSEC4\_TXD[4], LGPL0/LSDA10, LGPL1/LSDWE, TRIG\_OUT/READY, and D1\_MSRCID[2].

The following are factory test pins and require strong pull up resistors (100  $\Omega$  –1 k $\Omega$ ) to OVDD

LSSD\_MODE, TEST\_MODE[0:3]. The following pins require weak pull up resistors (2–10 k $\Omega$ ) to their specific power supplies: LCS[0:4], LCS[5]/DMA\_DREQ2, LCS[6]/DMA\_DACK[2], LCS[7]/DMA\_DDONE[2], IRQ\_OUT, IIC1\_SDA, IIC1\_SCL, IIC2\_SDA, IIC2\_SCL, and CKSTP\_OUT.

The following pins should be pulled to ground with a 100- $\Omega$  resistor: SD1\_IMP\_CAL\_TX, SD2\_IMP\_CAL\_TX. The following pins should be pulled to ground with a 200- $\Omega$  resistor: SD1\_IMP\_CAL\_RX, SD2\_IMP\_CAL\_RX.

TSECn\_TX\_EN signals require an external 4.7-k $\Omega$  pull down resistor to prevent PHY from seeing a valid Transmit Enable before it is actively driven.

When the platform frequency is 400 MHz, TSEC1\_TXD[1] must be pulled down at reset.

TSEC2\_TXD[4] and TSEC2\_TX\_ER pins function as cfg\_dram\_type[0 or 1] at reset and MUST BE VALID BEFORE HRESET ASSERTION when coming out of device sleep mode.

# 20.6.1 Special instructions for Single Core device

The mechanical drawing for the single core device does not have all the solder balls that exist on the single core device. This includes all the balls for VDD\_Core1 and SENSEV<sub>DD</sub>\_Core1 which exist on the package for the dual core device, but not on the single core package. A solder ball is present for SENSEV<sub>SS</sub>\_Core1 and needs to be connected to ground with a weak (2-10 k $\Omega$ ) pull down resistor. Likewise, AV<sub>DD</sub>\_Core1 needs to be pulled to ground as shown in Figure 64.

The mechanical drawing for the single core device is located in Section 16.2, "Mechanical Dimensions of the MPC8641 FC-CBGA."

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 3

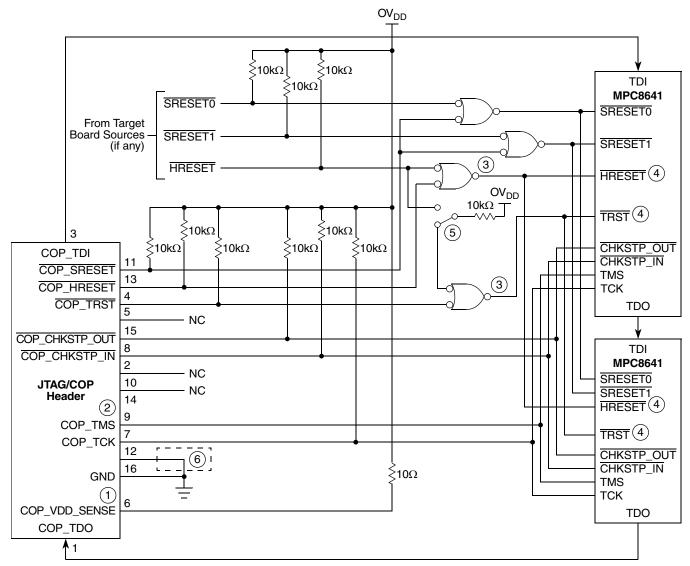

#### Notes:

- 1. Populate this with a  $10\Omega$  resistor for short circuit/current-limiting protection.

- 2. KEY location; pin 14 is not physically present on the COP header.

- 3. Use a AND gate with sufficient drive strength to drive two inputs.

- 4. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown above.

- 5. This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 6. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

Figure 69. JTAG/COP Interface Connection for Multiple MPC8641 Devices in Daisy Chain Configuration