#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z4d, e200z0h                                                        |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Speed                      | 80MHz/120MHz                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SCI, SPI                    |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 177                                                                     |

| Program Memory Size        | 3MB (3M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 256K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 33x10b, 10x12b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 208-LQFP                                                                |

| Supplier Device Package    | 208-TQFP (28x28)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5646ccf0mlt1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block                                                                 | Function                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LinFlexD (Local Interconnect<br>Network Flexible with DMA<br>support) | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                                                                 |

| Memory protection unit (MPU)                                          | Provides hardware access control for all memory references generated in a device                                                                                                                                                                                                                                                                                   |

| Clock generation module<br>(MC_CGM)                                   | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                                                                             |

| Power control unit (MC_PCU)                                           | Reduces the overall power consumption by disconnecting parts of the device from the power supply via a power switching device; device components are grouped into sections called "power domains" which are controlled by the PCU                                                                                                                                  |

| Reset generation module<br>(MC_RGM)                                   | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                                                                      |

| Mode entry module (MC_ME)                                             | Provides a mechanism for controlling the device operational mode and<br>modetransition sequences in all functional states; also manages the power<br>control unit, reset generation module and clock generation module, and holds the<br>configuration, control and status registers accessible for applications                                                   |

| Non-Maskable Interrupt (NMI)                                          | Handles external events that must produce an immediate response, such as power down detection                                                                                                                                                                                                                                                                      |

| Nexus Development Interface<br>(NDI)                                  | Provides real-time development capabilities for e200z0h and e200z4d core processor                                                                                                                                                                                                                                                                                 |

| Periodic interrupt timer/ Real Time<br>Interrupt Timer (PIT_RTI)      | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                                                                          |

| Real-time counter (RTC/API)                                           | A free running counter used for time keeping applications, the RTC can be<br>configured to generate an interrupt at a predefined interval independent of the<br>mode of operation (run mode or low-power mode). Supports autonomous<br>periodic interrupt (API) function to generate a periodic wakeup request to exit a<br>low power mode or an interrupt request |

| Static random-access memory (SRAM)                                    | Provides storage for program code, constants, and variables                                                                                                                                                                                                                                                                                                        |

| System integration unit lite (SIUL)                                   | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration                                                                                                                                           |

| System status and configuration module (SSCM)                         | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable                                                                                                                                   |

| System timer module (STM)                                             | Provides a set of output compare events to support AutoSAR and operating system tasks                                                                                                                                                                                                                                                                              |

| Semaphores                                                            | Provides the hardware support needed in multi-core systems for sharing resources and provides a simple mechanism to achieve lock/unlock operations via a single write access.                                                                                                                                                                                      |

| Wake Unit (WKPU)                                                      | Supports external sources that can generate interrupts or wakeup events, of which can cause non-maskable interrupt requests or wakeup events.                                                                                                                                                                                                                      |

#### Package pinouts and signal descriptions

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

|---|--------|--------------|--------|--------|--------|--------------|--------|--------|--------------|--------|--------|--------|--------------|--------|-----------------|-----------------|---|

| А | PC[15] | PB[2]        | PC[13] | PI[1]  | PE[7]  | PH[8]        | PE[2]  | PE[4]  | PC[4]        | PE[3]  | PH[9]  | PI[4]  | PH[11]       | PE[14] | PA[10]          | PG[11]          | A |

| в | PH[13] | PC[14]       | PC[8]  | PC[12] | PI[3]  | PE[6]        | PH[5]  | PE[5]  | PC[5]        | PC[0]  | PC[2]  | PH[12] | PG[10]       | PA[11] | PA[9]           | PA[8]           | В |

| с | PH[14] | VDD_HV_<br>A | PC[9]  | PL[0]  | PI[0]  | PH[7]        | PH[6]  | VSS_LV | VDD_HV_<br>A | PA[5]  | PC[3]  | PE[15] | PG[14]       | PE[12] | PA[7]           | PE[13]          | с |

| D | PG[5]  | PI[6]        | PJ[4]  | PB[3]  | PK[15] | PI[2]        | PH[4]  | VDD_LV | PC[1]        | PH[10] | PA[6]  | PI[5]  | PG[15]       | PF[14] | PF[15]          | PH[2]           | D |

| Е | PG[3]  | PI[7]        | PH[15] | PG[2]  | VDD_LV | VSS_LV       | PK[10] | PK[9]  | PM[1]        | PM[0]  | PL[15] | PL[14] | PG[0]        | PG[1]  | PH[0]           | VDD_HV_<br>A    | E |

| F | PA[2]  | PG[4]        | PA[1]  | PE[1]  | PL[2]  | PM[6]        | PL[1]  | PK[11] | PM[5]        | PL[13] | PL[12] | PM[2]  | PH[1]        | PH[3]  | PG[12]          | PG[13]          | F |

| G | PE[8]  | PE[0]        | PE[10] | PA[0]  | PL[3]  | VSS_HV       | VSS_HV | VSS_HV | VSS_HV       | VSS_HV | VSS_HV | PK[12] | VDD_HV_<br>B | PI[13] | PI[12]          | PA[3]           | G |

| н | PE[9]  | VDD_HV_<br>A | PE[11] | PK[1]  | PL[4]  | VSS_LV       | VSS_LV | VSS_HV | VSS_HV       | VSS_HV | VSS_HV | PK[13] | VDD_HV_<br>A | VDD_LV | VSS_LV          | PI[11]          | н |

| J | VSS_HV | VRC_CTR<br>L | VDD_LV | PG[9]  | PL[5]  | VSS_LV       | VSS_LV | VSS_LV | VSS_HV       | VSS_HV | VSS_HV | PK[14] | PD[15]       | PI[8]  | PI[9]           | PI[10]          | J |

| к | RESET  | VSS_LV       | PG[8]  | PC[11] | PL[6]  | VSS_LV       | VSS_LV | VSS_LV | VSS_LV       | VDD_LV | VDD_LV | PM[3]  | PD[14]       | PD[13] | PB[14]          | PB[15]          | к |

| L | PC[10] | PG[7]        | PB[0]  | PK[2]  | PL[7]  | VSS_LV       | VSS_LV | VSS_LV | VSS_LV       | VDD_LV | VDD_LV | PM[4]  | PD[12]       | PB[12] | PB[13]          | VDD_HV_<br>ADC1 | L |

| м | PG[6]  | PB[1]        | PK[4]  | PF[9]  | PK[5]  | PK[6]        | PK[7]  | PK[8]  | PL[8]        | PL[9]  | PL[10] | PL[11] | PB[11]       | PD[10] | PD[11]          | VSS_HV_<br>ADC1 | М |

| N | PK[3]  | PF[8]        | PC[6]  | PC[7]  | PJ[13] | VDD_HV_<br>A | PB[10] | PF[6]  | VDD_HV_<br>A | PJ[1]  | PD[2]  | PJ[5]  | PB[5]        | PB[6]  | PJ[6]           | PD[9]           | N |

| Ρ | PF[12] | PF[10]       | PF[13] | PA[14] | PJ[9]  | PA[12]       | PF[0]  | PF[5]  | PF[7]        | PJ[3]  | PI[15] | PD[4]  | PD[7]        | PD[8]  | PJ[8]           | PJ[7]           | Р |

| R | PF[11] | PA[15]       | PJ[11] | PJ[15] | PA[13] | PF[2]        | PF[3]  | PF[4]  | VDD_LV       | PJ[2]  | PJ[0]  | PD[0]  | PD[3]        | PD[6]  | VDD_HV_<br>ADC0 | PB[7]           | R |

| т | PJ[12] | PA[4]        | PK[0]  | PJ[14] | PJ[10] | PF[1]        | XTAL   | EXTAL  | VSS_LV       | PB[9]  | PB[8]  | PI[14] | PD[1]        | PD[5]  | VSS_HV_<br>ADC0 | PB[4]           | т |

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

Notes:

1) VDD\_HV\_B supplies the IO voltage domain for the pins PE[12], PA[11], PA[10], PA[9], PA[8], PA[7], PE[13], PF[14], PF[15], PG[0], PG[1], PH[3], PH[2], PH[1], PH[0], PG[12], PG[13], PA[3], PA[3], and PM[4]. 2)Availability of port pin alternate functions depends on product selection.

#### Figure 4. 256-pin BGA configuration

# 3.1 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^1$

$M = Medium^{1, 2}$

1. See the I/O pad electrical characteristics in the device data sheet for details.

MPC5646C Data Sheet, Rev.6

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium. For example, Fast/Medium pad will be Medium by default at reset. Similarly, Slow/Medium pad will be Slow by default. Only exception is PC[1] which is in medium configuration by default (refer to PCR.SRC in the reference manual, Pad Configuration Registers (PCR0—PCR198)).

|             |        |                                         |                                                                            |                                                                 |                                  |          |                  | Piı      | n numbe  | ər         |

|-------------|--------|-----------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR    | Alternate<br>function <sup>1</sup>      | Function                                                                   | Peripheral                                                      | I/O<br>direction <sup>2</sup>    | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PA[0]       | PCR[0] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>E0UC[13]<br>WKPU[19]<br>CAN1RX             | SIUL<br>eMIOS_0<br>MC_CGM<br>eMIOS_0<br>WKPU<br>FlexCAN_1       | I/O<br>I/O<br>I/O<br>I           | M/S      | Tristate         | 24       | 24       | G4         |

| PA[1]       | PCR[1] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[1]<br>E0UC[1]<br>—<br>WKPU[2]<br>CAN3RX<br>NMI[0] <sup>3</sup>        | SIUL<br>eMIOS_0<br>—<br>WKPU<br>FlexCAN_3<br>WKPU               | /O<br> /O<br><br> <br> <br> <br> | S        | Tristate         | 19       | 19       | F3         |

| PA[2]       | PCR[2] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[2]<br>E0UC[2]<br>—<br>MA[2]<br>WKPU[3]<br>NMI[1] <sup>3</sup>         | SIUL<br>eMIOS_0<br>—<br>ADC_0<br>WKPU<br>WKPU                   | /O<br> /O<br>—<br>0<br> <br>     | S        | Tristate         | 17       | 17       | F1         |

| PA[3]       | PCR[3] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[3]<br>E0UC[3]<br>LIN5TX<br>CS4_1<br>RX_ER_CLK<br>EIRQ[0]<br>ADC1_S[0] | SIUL<br>eMIOS_0<br>LINFlexD_5<br>DSPI_1<br>FEC<br>SIUL<br>ADC_1 | I/O<br>I/O<br>O<br>I<br>I<br>I   | M/S      | Tristate         | 114      | 138      | G16        |

| PA[4]       | PCR[4] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[4]<br>E0UC[4]<br>—<br>CS0_1<br>LIN5RX<br>WKPU[9]                      | SIUL<br>eMIOS_0<br><br>DSPI_1<br>LINFlexD_5<br>WKPU             | /O<br> /O<br> /O<br> <br>        | S        | Tristate         | 51       | 61       | T2         |

| PA[5]       | PCR[5] | AF0<br>AF1<br>AF2                       | GPIO[5]<br>E0UC[5]<br>LIN4TX                                               | SIUL<br>eMIOS_0<br>LINFlexD_4                                   | I/O<br>I/O<br>O                  | M/S      | Tristate         | 146      | 170      | C10        |

| PA[6]       | PCR[6] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[6]<br>E0UC[6]<br><br>CS1_1<br>LIN4RX<br>EIRQ[1]                       | SIUL<br>eMIOS_0<br><br>DSPI_1<br>LINFlexD_4<br>SIUL             | /O<br> /O<br>—<br>0<br> <br>     | S        | Tristate         | 147      | 171      | D11        |

| Table 4. Functional | port pi      | n descriptions |

|---------------------|--------------|----------------|

|                     | P • • • P ·· |                |

## Package pinouts and signal descriptions

|                    |         |                                              |                                                                                      |                                                           |                               |          |                  | Pir      | n numbe  | er         |

|--------------------|---------|----------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin        | PCR     | Alternate<br>function <sup>1</sup>           | Function                                                                             | Peripheral                                                | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PB[5]              | PCR[21] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[21]<br>—<br>—<br>ADC0_P[1]<br>ADC1_P[1]                                          | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          | -                             | I        | Tristate         | 91       | 107      | N13        |

| PB[6]              | PCR[22] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[22]<br>—<br>—<br>—<br>ADC0_P[2]<br>ADC1_P[2]                                     | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          | -<br>-<br>-<br>-              | I        | Tristate         | 92       | 108      | N14        |

| PB[7]              | PCR[23] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[23]<br>—<br>—<br>—<br>ADC0_P[3]<br>ADC1_P[3]                                     | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          |                               | I        | Tristate         | 93       | 109      | R16        |

| PB[8]              | PCR[24] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—<br>— | GPI[24]<br>—<br>—<br>ADC0_S[0]<br>ADC1_S[4]<br>WKPU[25]<br>OSC32k_XTAL <sup>4</sup>  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1<br>WKPU<br>SXOSC         | -                             | I        | _                | 61       | 77       | T11        |

| PB[9] <sup>5</sup> | PCR[25] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—<br>— | GPI[25]<br>—<br>—<br>ADC0_S[1]<br>ADC1_S[5]<br>WKPU[26]<br>OSC32k_EXTAL <sup>4</sup> | SIUL<br>—<br>ADC_0<br>ADC_1<br>WKPU<br>SXOSC              | <br> <br> <br> <br>           | I        |                  | 60       | 76       | T10        |

| PB[10]             | PCR[26] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—      | GPIO[26]<br>SOUT_1<br>CAN3TX<br>—<br>ADC0_S[2]<br>ADC1_S[6]<br>WKPU[8]               | SIUL<br>DSPI_1<br>FlexCAN_3<br><br>ADC_0<br>ADC_1<br>WKPU | I/O<br>O<br><br>I<br>I<br>I   | S        | Tristate         | 62       | 78       | N7         |

### Package pinouts and signal descriptions

|             |          |                                    |                                                  |                                               |                                 |          |                  | Pir      | n numbe  | ər         |

|-------------|----------|------------------------------------|--------------------------------------------------|-----------------------------------------------|---------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                                         | Peripheral                                    | I/O<br>direction <sup>2</sup>   | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PH[14]      | PCR[126] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[126]<br>SCK_4<br>CS1_3<br>E1UC[27]          | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1           | I/O<br>I/O<br>O<br>I/O          | M/S      | Tristate         | 10       | 10       | C1         |

| PH[15]      | PCR[127] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[127]<br>SOUT_5<br>—<br>E1UC[17]             | SIUL<br>DSPI_5<br>—<br>eMIOS_1                | I/O<br>O<br><br>I/O             | M/S      | Tristate         | 8        | 8        | E3         |

| PI[0]       | PCR[128] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[128]<br>E0UC[28]<br>LIN8TX<br>—             | SIUL<br>eMIOS_0<br>LINFlexD_8<br>—            | I/O<br>I/O<br>O                 | S        | Tristate         | 172      | 196      | C5         |

| PI[1]       | PCR[129] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[129]<br>E0UC[29]<br>—<br>WKPU[24]<br>LIN8RX | SIUL<br>eMIOS_0<br>—<br>WKPU<br>LINFlexD_8    | /O<br> /O<br><br> <br> <br>     | S        | Tristate         | 171      | 195      | A4         |

| PI[2]       | PCR[130] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[130]<br>E0UC[30]<br>LIN9TX<br>—             | SIUL<br>eMIOS_0<br>LINFlexD_9<br>—            | I/O<br>I/O<br>O                 | S        | Tristate         | 170      | 194      | D6         |

| PI[3]       | PCR[131] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[131]<br>E0UC[31]<br>—<br>WKPU[23]<br>LIN9RX | SIUL<br>eMIOS_0<br><br>WKPU<br>LINFlexD_9     | /O<br> /O<br><br> <br> <br>     | S        | Tristate         | 169      | 193      | B5         |

| PI[4]       | PCR[132] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[132]<br>E1UC[28]<br>SOUT_4<br>—             | SIUL<br>eMIOS_1<br>DSPI_4<br>—                | I/O<br>I/O<br>O                 | M/S      | Tristate         | 143      | 167      | A12        |

| PI[5]       | PCR[133] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[133]<br>E1UC[29]<br>SCK_4<br>CS2_5<br>CS2_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>I/O<br>O          | M/S      | Tristate         | 142      | 166      | D12        |

| PI[6]       | PCR[134] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[134]<br>E1UC[30]<br>CS0_4<br>CS0_5<br>CS0_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>I/O<br>I/O<br>I/O | S        | Tristate         | 11       | 11       | D2         |

| Table 4. Functional port pin descriptions (continue |

|-----------------------------------------------------|

|-----------------------------------------------------|

|             |          |                                    |                          |                     |                               |          |                  | Pir      | n numbe  | ər         |

|-------------|----------|------------------------------------|--------------------------|---------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                 | Peripheral          | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PM[4]       | PCR[196] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[196]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>                       | M/S      | Tristate         |          | _        | L12        |

| PM[5]       | PCR[197] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[197]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>                       | M/S      | Tristate         | _        | _        | F9         |

| PM[6]       | PCR[198] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[198]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>—<br>—<br>—            | M/S      | Tristate         |          | _        | F6         |

Table 4. Functional port pin descriptions (continued)

NOTES:

- <sup>1</sup> Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 000 → AF0; PCR.PA = 001 → AF1; PCR.PA = 010 → AF2; PCR.PA = 011 → AF3; PCR.PA = 100 → ALT4. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

- <sup>2</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- <sup>3</sup> NMI[0] and NMI[1] have a higher priority than alternate functions. When NMI is selected, the PCR.PA field is ignored.

- <sup>4</sup> SXOSC's OSC32k\_XTAL and OSC32k\_EXTAL pins are shared with GPIO functionality. When used as crystal pins, other functionality of the pin cannot be used and it should be ensured that application never programs OBE and PUE bit of the corresponding PCR to "1".

- <sup>5</sup> If you want to use OSC32K functionality through PB[8] and PB[9], you must ensure that PB[10] is static in nature as PB[10] can induce coupling on PB[9] and disturb oscillator frequency.

- <sup>6</sup> Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO.

PC[0:1] are available as JTAG pins (TDI and TDO respectively).

PH[9:10] are available as JTAG pins (TCK and TMS respectively).

It is up to the user to configure these pins as GPIO when needed.

- <sup>7</sup> When MBIST is enabled to run (STCU Enable = 1), the application must not drive or tie PAD[178) (MDO[0]) to 0 V before the device exits reset (external reset is removed) as the pad is internally driven to 1 to indicate MBIST operation. When MBIST is not enabled (STCU Enable = 0), there are no restriction as the device does not internally drive the pad.

- <sup>8</sup> These pins can be configured as Nexus pins during reset by the debugger writing to the Nexus Development Interface "Port Control Register" rather than the SIUL. Specifically, the debugger can enable the MDO[7:0], MSEO, and MCKO ports by programming NDI (PCR[MCKO\_EN] or PCR[PSTAT\_EN]). MDO[8:11] ports can be enabled by programming NDI ((PCR[MCKO\_EN] and PCR[FPM]) or PCR[PSTAT\_EN]).

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS_HV}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

# 4.1 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 5 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

Table 5. Parameter classifications

# NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 4.2 NVUSRO register

Portions of the device configuration, such as high voltage supply is controlled via bit values in the Non-Volatile User Options Register (NVUSRO). For a detailed description of the NVUSRO register, see MPC5646C Reference Manual.

| Symbol              |    | Parameter                                                                   | Conditions                             | Va  | lue | Unit  |

|---------------------|----|-----------------------------------------------------------------------------|----------------------------------------|-----|-----|-------|

| Symbol              |    | Falameter                                                                   | Conditions                             | Min | Max | Onit  |

| I <sub>INJPAD</sub> | SR | Injected input current on any<br>pin during overload condition              |                                        | -5  | 5   | mA    |

| I <sub>INJSUM</sub> |    | Absolute sum of all injected<br>input currents during overload<br>condition | _                                      | -50 | 50  |       |

| TV <sub>DD</sub>    | SR | V <sub>DD_HV_A</sub> slope to ensure<br>correct power up <sup>8</sup>       | —                                      | _   | 0.5 | V/µs  |

|                     |    | correct power up <sup>o</sup>                                               | —                                      | 0.5 | —   | V/min |

| T <sub>A</sub>      | SR | Ambient temperature under bias                                              | f <sub>CPU</sub> up to<br>120 MHz + 2% | -40 | 125 | °C    |

| Тј                  | SR | Junction temperature under bias                                             | —                                      | -40 | 150 |       |

| Table 9. Recommended operating | conditions (3.3 V) | (continued) |

|--------------------------------|--------------------|-------------|

|--------------------------------|--------------------|-------------|

NOTES:

- <sup>1</sup> 100 nF EMI capacitance need to be provided between each VDD/VSS\_HV pair.

- <sup>2</sup> 100 nF EMI capacitance needs to be provided between each VDD\_LV/VSS\_LV supply pair. 10 µF bulk capacitance needs to be provided as CREG on each VDD\_LV pin. For details refer to the Power Management chapter of the MPC5646C Reference Manual.

- <sup>3</sup> This voltage is internally generated by the device and no external voltage should be supplied.

- $^4~$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

- <sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

- <sup>6</sup> Both the relative and the fixed conditions must be met. For instance: If  $V_{DD_HV_A}$  is 5.9 V,  $V_{DD_HV_ADC0}$  maximum value is 6.0 V then, despite the relative condition, the max value is  $V_{DD_HV_A} + 0.3 = 6.2$  V.

- <sup>7</sup> PA3, PA7, PA10, PA11 and PE12 ADC\_1 channels are coming from V<sub>DD\_HV\_B</sub> domain hence V<sub>DD\_HV\_ADC1</sub> should be within ±100 mV of V<sub>DD\_HV\_B</sub> when these channels are used for ADC\_1.

- <sup>8</sup> Guaranteed by the device validation.

| Symbol                 |    | Parameter                                                                                                                                                                                            | Conditions                | Valu | Value   |   |  |

|------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------|---|--|

| Symbol                 |    | Falanielei                                                                                                                                                                                           | Conditions                | Min  | Min Max |   |  |

| V <sub>SS_HV</sub>     | SR | Digital ground on VSS_HV pins                                                                                                                                                                        | —                         | 0    | 0       | V |  |

| V <sub>DD_HV_A</sub> 1 | SR | Voltage on VDD_HV_A pins with                                                                                                                                                                        | —                         | 4.5  | 5.5     | V |  |

|                        |    | respect to ground ( $V_{SS_HV}$ )                                                                                                                                                                    | Voltage drop <sup>2</sup> | 3.0  | 5.5     |   |  |

| V <sub>DD_HV_B</sub>   | SR | Generic GPIO functionality                                                                                                                                                                           | —                         | 3.0  | 5.5     | V |  |

|                        |    | Ethernet/3.3 V functionality<br>(See the notes in all figures in<br>Section 3, "Package pinouts and<br>signal descriptions" for the list of<br>channels operating in V <sub>DD_HV_B</sub><br>domain) | _                         | 3.0  | 3.6     | V |  |

Table 10. Recommended operating conditions (5.0 V)

- <sup>4</sup> This voltage is internally generated by the device and no external voltage should be supplied.

- <sup>5</sup> 100 nF capacitance needs to be provided between  $V_{DD_HV_(ADC0/ADC1)}/V_{SS_HV_(ADC0/ADC1)}$  pair.

- <sup>6</sup> Both the relative and the fixed conditions must be met. For instance: If  $V_{DD_{HV_A}}$  is 5.9 V,  $V_{DD_{HV_A}DC0}$  maximum value is 6.0 V then, despite the relative condition, the max value is  $V_{DD_{HV_A}} + 0.3 = 6.2$  V.

- <sup>7</sup> PA3, PA7, PA10, PA11 and PE12 ADC\_1 channels are coming from V<sub>DD-HV\_B</sub> domain hence VDD\_HV\_ADC1 should be within ±100 mV of V<sub>DD HV B</sub> when these channels are used for ADC\_1.

- <sup>8</sup> Guaranteed by device validation.

### NOTE

### SRAM retention guaranteed to LVD levels.

# 4.5 Thermal characteristics

# 4.5.1 Package thermal characteristics

| Symbol         |    | с                                                            | Parameter                                           | Conditions <sup>2</sup> | Pin count |     | Unit            |                 |      |

|----------------|----|--------------------------------------------------------------|-----------------------------------------------------|-------------------------|-----------|-----|-----------------|-----------------|------|

|                |    | Ŭ                                                            | i di di neter                                       | Conditions              |           | Min | Тур             | Max             | onne |

| $R_{\thetaJA}$ | CC | D                                                            | Thermal resistance,                                 | Single-layer            | 176       |     | _               | 38 <sup>5</sup> | °C/W |

|                |    | junction-to-ambient board—1s natural convection <sup>4</sup> | board—1s                                            | 208                     |           | —   | 41 <sup>6</sup> | °C/W            |      |

| $R_{\thetaJA}$ | CC |                                                              |                                                     | 176                     | _         | _   | 31              | °C/W            |      |

|                |    |                                                              | junction-to-ambient natural convection <sup>7</sup> | board—2s2p <sup>7</sup> | 208       | —   | _               | 34              | °C/W |

### Table 11. LQFP thermal characteristics<sup>1</sup>

NOTES:

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C.

<sup>3</sup> All values need to be confirmed during device validation.

<sup>4</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>5</sup> Junction-to-Ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6.

<sup>6</sup> Junction-to-Ambient thermal resistance determined per JEDEC JESD51-2 and JESD51-6

<sup>7</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8.

| Table 12. 256 MAPBGA thermal characteri | stics <sup>1</sup> |

|-----------------------------------------|--------------------|

|-----------------------------------------|--------------------|

| S              | Symbol C |    | С | Parameter          | Conditions            | Value           | Unit |

|----------------|----------|----|---|--------------------|-----------------------|-----------------|------|

| R <sub>θ</sub> | JA       | СС |   |                    | Single-layer board—1s | 43 <sup>2</sup> | °C/W |

|                |          |    |   | natural convection | Four-layer board—2s2p | 26 <sup>3</sup> |      |

NOTES:

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

<sup>3</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-6 with the board horizontal.

| Symbol                 |    | с | Parameter                                                                                     | Conditions <sup>1</sup>                               |     | Value <sup>2</sup> |                  | Unit |

|------------------------|----|---|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|--------------------|------------------|------|

| Symbol                 |    |   | Falameter                                                                                     | Conditions                                            | Min | Тур                | Max              | Unit |

| I <sub>LPREGINT</sub>  | СС | D | Low power regulator module current consumption                                                | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | -   | —                  | 600              | μΑ   |

|                        |    |   |                                                                                               | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _   | 20                 |                  |      |

| I <sub>VREGREF</sub>   | СС | D | Main LVDs and reference current<br>consumption (low power and main<br>regulator switched off) | T <sub>A</sub> = 55 °C                                | _   | 2                  | _                | μA   |

| I <sub>VREDLVD12</sub> | СС | D | Main LVD current consumption (switch-off during standby)                                      | T <sub>A</sub> = 55 °C                                | -   | 1                  |                  | μA   |

| I <sub>DD_HV_A</sub>   | СС | D | In-rush current on V <sub>DD_BV</sub> during power-up                                         | _                                                     | -   |                    | 600 <sup>3</sup> | mA   |

NOTES:

$^1$  V<sub>DD HV A</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> Inrush current is seen more like steps of 600 mA peak. The startup of the regulator happens in steps of 50 mV in ~25 steps to reach ~1.2 V V<sub>DD LV</sub>. Each step peak current is within 600 mA

# 4.8.3 Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as four low voltage detectors to monitor the  $V_{DD\ HV\ A}$  and the  $V_{DD\ LV}$  voltage while device is supplied:

- POR monitors V<sub>DD\_HV\_A</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors  $V_{DD HV_A}$  to ensure device is reset below minimum functional supply

- LVDHV5 monitors  $V_{DD HV A}$  when application uses device in the 5.0 V±10% range

- LVDLVCOR monitors power domain No. 1 (PD1)

- LVDLVBKP monitors power domain No. 0 (PD0). VDD\_LV is same as PD0 supply.

### NOTE

When enabled, PD2 (RAM retention) is monitored through LVD\_DIGBKP.

### Table 26 shows the data flash memory program and erase characteristics.

### Table 26. Data flash memory—Program and erase specifications

|                         |    |    |                                          | Value |                  |                             |                            |      |    |    |    |

|-------------------------|----|----|------------------------------------------|-------|------------------|-----------------------------|----------------------------|------|----|----|----|

| Symbol                  |    | С  | C Parameter                              | Min   | Typ <sup>1</sup> | Initial<br>max <sup>2</sup> | Max <sup>3</sup>           | Unit |    |    |    |

| T <sub>wprogram</sub>   |    |    | Word (32 bits) program time <sup>4</sup> | _     | 30               | 70                          | 500                        | μs   |    |    |    |

| T <sub>16Kpperase</sub> |    | С  | 16 KB block pre-program and erase time   | _     | 700              | 800                         | 5000                       | ms   |    |    |    |

| T <sub>eslat</sub>      | сс | сс | сс                                       | сс    | D                | Erase Suspend Latency       | _                          | —    | 30 | 30 | μs |

| t <sub>ESRT</sub> 5     |    |    |                                          |       | CC               | С                           | Erase Suspend Request Rate | 10   | —  | —  | _  |

| t <sub>PABT</sub>       |    | D  | Program Abort Latency                    | _     | —                | 12                          | 12                         | μs   |    |    |    |

| t <sub>EAPT</sub>       |    | D  | Erase Abort Latency                      | _     | —                | 30                          | 30                         | μs   |    |    |    |

### NOTES:

Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

<sup>5</sup> It is time between erase suspend resume and next erase suspend.

| Symbol    |    | с | Parameter                                                                                                                  | Conditions                     | Va      | lue     | Unit   |

|-----------|----|---|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------|---------|--------|

|           |    | Ŭ | i di dificici                                                                                                              | Conditions                     | Min     | Тур     |        |

| P/E       | CC | С | Number of program/erase cycles per<br>block for 16 Kbyte blocks over the<br>operating temperature range (T <sub>J</sub> )  | _                              | 100,000 | 100,000 | cycles |

|           |    |   | Number of program/erase cycles per<br>block for 32 Kbyte blocks over the<br>operating temperature range (T <sub>J</sub> )  | _                              | 10,000  | 100,000 | cycles |

|           |    |   | Number of program/erase cycles per<br>block for 128 Kbyte blocks over the<br>operating temperature range (T <sub>J</sub> ) | _                              | 1,000   | 100,000 | cycles |

| Retention | СС | С | Minimum data retention at 85 °C average ambient temperature <sup>1</sup>                                                   | Blocks with 0–1,000 P/E cycles | 20      |         | years  |

|           |    |   |                                                                                                                            | Blocks with 10,000 P/E cycles  | 10      | _       | years  |

|           |    |   |                                                                                                                            | Blocks with 100,000 P/E cycles | 5       | —       | years  |

#### Table 27. Flash memory module life

NOTES:

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

| Symbol               |    | C Parameter | Conditions <sup>1</sup>                                                                                  | Value <sup>2</sup>                                     |     |     | Unit |          |

|----------------------|----|-------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-----|------|----------|

| Symbol               |    | Ŭ           | ruruneter                                                                                                | Conditions                                             | Min | Тур | Max  | <b>U</b> |

| T <sub>SIRCSU</sub>  | СС | Ρ           | Slow internal RC oscillator start-up time                                                                | $T_A = 25 \text{ °C}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | _   | 8   | 12   | μs       |

| $\Delta_{SIRCPRE}$   | СС | С           | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub>                       | T <sub>A</sub> = 25 °C                                 | -2  |     | +2   | %        |

|                      | СС | С           | Slow internal RC oscillator trimming step                                                                | _                                                      | _   | 2.7 | —    |          |

| <sup>∆</sup> sircvar | СС | С           | Variation in f <sub>SIRC</sub> across<br>temperature and fluctuation in<br>supply voltage, post trimming | _                                                      | -10 |     | +10  | %        |

### Table 40. Slow internal RC oscillator (128 kHz) electrical characteristics (continued)

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

#### 4.17 **ADC** electrical characteristics

#### 4.17.1 Introduction

The device provides two Successive Approximation Register (SAR) analog-to-digital converters (10-bit and 12-bit).

## NOTE

Due to ADC limitations, the two ADCs cannot sample a shared channel at the same time i.e., their sampling windows cannot overlap if a shared channel is selected. If this is done, neither of the ADCs can guarantee their conversion accuracies.

This relation can again be simplified considering  $C_S$  as an additional worst condition. In reality, transient is faster, but the A/D converter circuitry has been designed to be robust also in very worst case: the sampling time  $T_s$  is always much longer than the internal time constant.

Eqn. 6

$$\tau_1 < (R_{SW} + R_{AD}) \bullet C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to the following equation

$$Eqn. 7$$

$$V_{A1} \bullet (C_{S} + C_{P1} + C_{P2}) = V_{A} \bullet (C_{P1} + C_{P2})$$

• A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance RL: again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_L$  sizing is obtained:

Eqn. 9

8.5 •

$$\tau_2 = 8.5 • R_I • (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . The following equation must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

#### Eqn. 10

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing

# 4.17.1.2 ADC electrical characteristics

| Table 41. ADC input leakage current |  |

|-------------------------------------|--|

|-------------------------------------|--|

| Sum              | Symbol |   | Parameter             |                         | Conditions                           |   | Value |     | Unit |

|------------------|--------|---|-----------------------|-------------------------|--------------------------------------|---|-------|-----|------|

| Symbol           |        | C | Falameter             | Conditions              |                                      |   | Тур   | Max | Unit |

| I <sub>LKG</sub> | СС     | С | Input leakage current | $T_A = -40 \ ^\circ C$  | No current injection on adjacent pin | _ | 1     | _   | nA   |

|                  |        | С |                       | T <sub>A</sub> = 25 °C  |                                      | _ | 1     | _   |      |

|                  |        | С |                       | T <sub>A</sub> = 105 °C |                                      | _ | 8     | 200 |      |

|                  |        | Ρ |                       | T <sub>A</sub> = 125 °C |                                      | — | 45    | 400 | 1    |

## Table 42. ADC conversion characteristics (10-bit ADC\_0)

| Symbol               |        | с | Devenueter                                                                                                         | Conditions <sup>1</sup>   |                            | Value | •                          | 11   |

|----------------------|--------|---|--------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|-------|----------------------------|------|

| Symbo                | Gymbol |   | Parameter                                                                                                          | Conditions                | Min                        | Тур   | Max                        | Unit |

| V <sub>SS_ADC0</sub> | SR     |   | Voltage on<br>VSS_HV_ADC0<br>(ADC_0 reference)<br>pin with respect to<br>ground (V <sub>SS_HV</sub> ) <sup>2</sup> | _                         | -0.1                       | _     | 0.1                        | V    |

| V <sub>DD_ADC0</sub> | SR     |   | Voltage on<br>VDD_HV_ADC0 pin<br>(ADC_0 reference)<br>with respect to<br>ground (V <sub>SS_HV</sub> )              | _                         | V <sub>DD_HV_A</sub> – 0.1 |       | V <sub>DD_HV_A</sub> + 0.1 | V    |

| V <sub>AINx</sub>    | SR     |   | Analog input voltage <sup>3</sup>                                                                                  | _                         | $V_{SS\_ADC0} - 0.1$       |       | V <sub>DD_ADC0</sub> + 0.1 | V    |

| f <sub>ADC0</sub>    | SR     |   | ADC_0 analog<br>frequency                                                                                          | _                         | 6                          | _     | 32 + 2%                    | MHz  |

| t <sub>ADC0_PU</sub> | SR     | _ | ADC_0 power up<br>delay                                                                                            | _                         | —                          | _     | 1.5                        | μs   |

| t <sub>ADC0_S</sub>  | СС     | Т | Sample time <sup>4</sup>                                                                                           | f <sub>ADC</sub> = 32 MHz | 500                        | —     |                            | ns   |

| t <sub>ADC0_C</sub>  | СС     | Ρ | Conversion time <sup>5,6</sup>                                                                                     | f <sub>ADC</sub> = 32 MHz | 0.625                      | _     |                            | μs   |

|                      |        |   |                                                                                                                    | f <sub>ADC</sub> = 30 MHz | 0.700                      | _     |                            |      |

| C <sub>S</sub>       | СС     | D | ADC_0 input<br>sampling<br>capacitance                                                                             | _                         | _                          |       | 3                          | pF   |

| C <sub>P1</sub>      | СС     | D | ADC_0 input pin<br>capacitance 1                                                                                   | _                         | —                          | _     | 3                          | pF   |

| C <sub>P2</sub>      | сс     | D | ADC_0 input pin<br>capacitance 2                                                                                   | _                         | —                          |       | 1                          | pF   |

| C <sub>P3</sub>      | сс     | D | ADC_0 input pin 1 capacitance 3                                                                                    |                           | 1                          | pF    |                            |      |

| R <sub>SW1</sub>     | сс     | D | Internal resistance of analog source                                                                               | _                         | —                          | —     | 3                          | kΩ   |

| Symbol                            |    |   |                                                                                                                    | o 1                         | Value                      |     |                            |      |

|-----------------------------------|----|---|--------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|-----|----------------------------|------|

| Symb                              | ol | С | Parameter                                                                                                          | Conditions <sup>1</sup>     | Min Typ                    |     | Max                        | Unit |

| V <sub>SS_ADC1</sub>              | SR | — | Voltage on<br>VSS_HV_ADC1<br>(ADC_1 reference)<br>pin with respect to<br>ground (V <sub>SS_HV</sub> ) <sup>2</sup> | _                           | -0.1                       |     | 0.1                        | V    |

| V <sub>DD_ADC1</sub> <sup>3</sup> | SR | _ | Voltage on<br>VDD_HV_ADC1<br>pin (ADC_1<br>reference) with<br>respect to ground<br>(V <sub>SS_HV</sub> )           | _                           | V <sub>DD_HV_A</sub> – 0.1 |     | V <sub>DD_HV_A</sub> + 0.1 | V    |

| V <sub>AINx</sub> <sup>3,4</sup>  | SR | — | Analog input<br>voltage <sup>5</sup>                                                                               | _                           | V <sub>SS_ADC1</sub> - 0.1 |     | V <sub>DD_ADC1</sub> + 0.1 | V    |

| f <sub>ADC1</sub>                 | SR |   | ADC_1 analog<br>frequency                                                                                          | _                           | 8 + 2%                     |     | 32 + 2%                    | MHz  |

| t <sub>ADC1_PU</sub>              | SR |   | ADC_1 power up<br>delay                                                                                            | _                           |                            | 1.5 |                            | μs   |

| t <sub>ADC1_S</sub>               | CC | Т | Sample time <sup>6</sup><br>VDD=5.0 V                                                                              | _                           | 440                        |     |                            | ns   |

|                                   |    |   | Sample time <sup>(6)</sup><br>VDD=3.3 V                                                                            | _                           | 530                        |     |                            |      |

| t <sub>ADC1_C</sub>               | CC | Р | Conversion time <sup>7, 8</sup><br>VDD=5.0 V                                                                       | $f_{ADC1} = 32 \text{ MHz}$ | 2                          |     |                            |      |

|                                   |    |   | Conversion time <sup>(7),</sup><br><sup>(6)</sup><br>VDD =5.0 V                                                    | f <sub>ADC 1</sub> = 30 MHz | 2.1                        |     |                            | μs   |

|                                   |    |   | Conversion time <sup>(7),</sup><br><sup>(6)</sup><br>VDD=3.3 V                                                     | f <sub>ADC 1</sub> = 20 MHz | 3                          |     |                            |      |

|                                   |    |   | Conversion time <sup>(7),</sup><br>(6)<br>VDD =3.3 V                                                               | f <sub>ADC1</sub> = 15 MHz  | 3.01                       |     |                            |      |

| C <sub>S</sub>                    | СС | D | ADC_1 input<br>sampling<br>capacitance                                                                             | _                           |                            | 5   |                            | pF   |

| C <sub>P1</sub>                   | СС | D | ADC_1 input pin capacitance 1                                                                                      | —                           |                            | 3   |                            | pF   |

| C <sub>P2</sub>                   | СС | D | ADC_1 input pin capacitance 2                                                                                      | _                           |                            | 1   |                            | pF   |

| C <sub>P3</sub>                   | СС | D | ADC_1 input pin capacitance 3                                                                                      | _                           |                            | 1.5 |                            | pF   |

| R <sub>SW1</sub>                  | СС | D | Internal resistance<br>of analog source                                                                            |                             |                            |     | 1                          | kΩ   |

- <sup>7</sup> Conversion time = Bit evaluation time + Sampling time + 1 Clock cycle delay.

- <sup>8</sup> Refer to ADC conversion table for detailed calculations.

- <sup>9</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

# 4.18 Fast Ethernet Controller

MII signals use CMOS signal levels compatible with devices operating at 3.3 V. Signals are not TTL compatible. They follow the CMOS electrical characteristics.

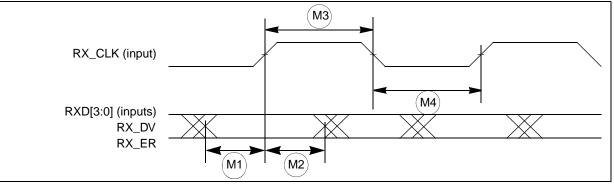

# 4.18.1 MII Receive Signal Timing (RXD[3:0], RX\_DV, RX\_ER, and RX\_CLK)

The receiver functions correctly up to a RX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the system clock frequency must exceed four times the RX\_CLK frequency in 2:1 mode and two times the RX\_CLK frequency in 1:1 mode.

| Spec | Characteristic                               | Min | Max | Unit          |

|------|----------------------------------------------|-----|-----|---------------|

| M1   | RXD[3:0], RX_DV,<br>RX_ER to RX_CLK<br>setup | 5   | _   | ns            |

| M2   | RX_CLK to<br>RXD[3:0], RX_DV,<br>RX_ER hold  | 5   | _   | ns            |

| M3   | RX_CLK pulse width<br>high                   | 35% | 65% | RX_CLK period |

| M4   | RX_CLK pulse width low                       | 35% | 65% | RX_CLK period |

Table 44. MII Receive Signal Timing

Figure 21. MII receive signal timing diagram

# 4.18.2 MII Transmit Signal Timing (TXD[3:0], TX\_EN, TX\_ER, TX\_CLK)

The transmitter functions correctly up to a TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the system clock frequency must exceed four times the TX\_CLK frequency in 2:1 mode and two times the TX\_CLK frequency in 1:1 mode.

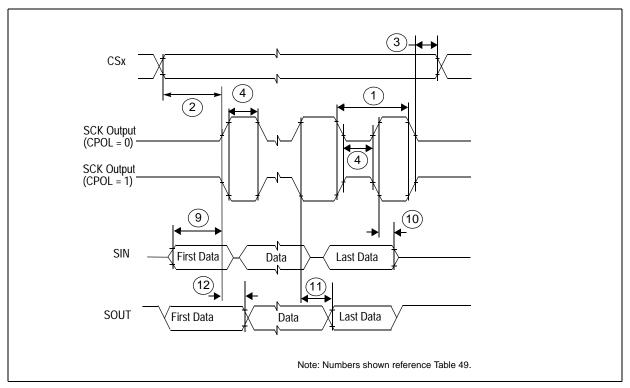

Figure 29. DSPI modified transfer format timing-master, CPHA = 0

| No. | Symbol               |    | с | Parameter               |     | Unit |     |      |

|-----|----------------------|----|---|-------------------------|-----|------|-----|------|

| NO. |                      |    |   | r ai ainetei            | Min | Тур  | Мах | onit |

| 6   | t <sub>TDOV</sub>    | CC | D | TCK low to TDO valid    |     |      | 33  | ns   |

| 7   | t <sub>TDOI</sub>    | СС | D | TCK low to TDO invalid  | 6   | —    | —   | ns   |

| —   | t <sub>TDC</sub>     | CC | D | TCK Duty Cycle          | 40  | —    | 60  | %    |

| —   | t <sub>TCKRISE</sub> | СС | D | TCK Rise and Fall Times | —   | —    | 3   | ns   |

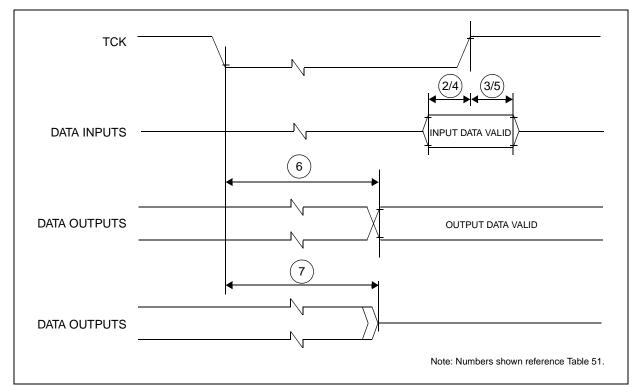

Figure 36. Timing diagram - JTAG boundary scan

Package characteristics

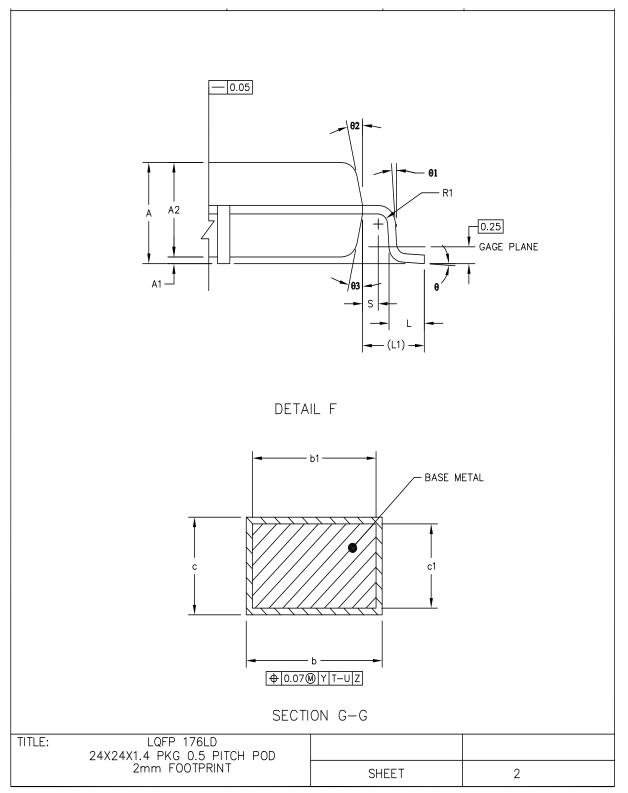

Figure 38. 176 LQFP mechanical drawing (Part 2 of 3)

MPC5646C Data Sheet, Rev.6

## **Revision history**

| Revision | Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 12 Feb 2014 | <ul> <li>Removed occurrences of 208BGA from Table 3 System pin descriptions.</li> <li>Added PM[3] and PM[4] in the figure note 1 of Figure 4, 256-pin BGA configuration.</li> <li>Added a table note in Table 19 I/O supplies.</li> <li>Updated Figure 8, Voltage regulator capacitance connection and added a note in this figure.</li> <li>Removed max values of V<sub>LPREG</sub> and V<sub>MREG</sub>, changed min value of V<sub>LPREG</sub> to 1.21 V, and updated V<sub>MREG</sub> and V<sub>LPREG</sub> after trimming values in Table 22 Voltage regulator electrical characteristics.</li> <li>Updated 1st footnote and updated max values for I<sub>DDRUN</sub>, I<sub>DDHALT</sub>, I<sub>DDSTOP</sub> I<sub>DDSTDBY3</sub>, I<sub>DDSTDBY2</sub>, I<sub>DDSTDBY1</sub> and removed values at 85°C and 105°C in Table 24 Low voltage power domain electrical characteristics.</li> <li>Added a footnote below Table 28 Flash memory read access timing.</li> <li>Updated the formula in Eq. 11 in Section 4.17.1.1, "Input impedance and ADC accuracy.</li> <li>Added Figure 17, Input equivalent circuit (extended channels).</li> <li>Updated t<sub>ADCO_PU</sub> value to 1.5 as max and added footnote for I<sub>INJ</sub> in Table 42 ADC conversion characteristics (10-bit ADC_0).</li> <li>Added Category column in Table 43 Conversion characteristics (12-bit ADC_1).</li> <li>Added a note in Figure 45, Orderable parts.</li> </ul> |

## Table 52. Revision history (continued)

## NOTE

This revision history uses clickable cross-references for ease of navigation. The numbers and titles in each cross-reference are relative to the latest published release.