Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z4d, e200z0h                                                        |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Speed                      | 80MHz/120MHz                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SCI, SPI                    |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 199                                                                     |

| Program Memory Size        | 3MB (3M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 256K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 33x10b, 10x12b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 256-LBGA                                                                |

| Supplier Device Package    | 256-MAPBGA (17x17)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5646ccf0mmj1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document Overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the MPC5646C device. To ensure a complete understanding of the device functionality, refer also to the MPC5646C Reference Manual.

# 1.2 Description

The MPC5646C is a new family of next generation microcontrollers built on the Power Architecture embedded category. This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

The MPC5646C family expands the range of the MPC560xB microcontroller family. It provides the scalability needed to implement platform approaches and delivers the performance required by increasingly sophisticated software architectures. The advanced and cost-efficient host processor core of the MPC5646C automotive controller family complies with the Power Architecture embedded category, which is 100 percent user-mode compatible with the original Power Architecture user instruction set architecture (UISA). It operates at speeds of up to 120 MHz and offers high performance processing optimized for low power consumption. It also capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# Table 2 summarizes the functions of the blocks present on the MPC5646C. Table 2. MPC5646C series block summary

| Block                                                         | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Converts analog voltages to digital values                                                                                                                                                                                                                                                                        |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Cryptographic Security Engine<br>(CSE)                        | Supports the encoding and decoding of any kind of data                                                                                                                                                                                                                                                            |

| Crossbar (XBAR) switch                                        | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width                                                                                                                                                    |

| DMA Channel Multiplexer<br>(DMAMUX)                           | Allows to route DMA sources (called slots) to DMA channels                                                                                                                                                                                                                                                        |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels.                                                                                                                                                                                                    |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| FMPLL (frequency-modulated phase-locked loop)                 | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| FlexRay (FlexRay communication controller)                    | Provides high-speed distributed control for advanced automotive applications                                                                                                                                                                                                                                      |

| Fast Ethernet Controller (FEC)                                | Ethernet Media Access Controller (MAC) designed to support both 10 and 100<br>Mbps Ethernet/IEEE 802.3 networks                                                                                                                                                                                                   |

| Internal multiplexer (IMUX) SIUL subblock                     | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests for both e200z0h and e200z4d cores                                                                                                                                                                                                            |

| JTAG controller                                               | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

## Package pinouts and signal descriptions

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

|---|--------|--------------|--------|--------|--------|--------------|--------|--------|--------------|--------|--------|--------|--------------|--------|-----------------|-----------------|---|

| А | PC[15] | PB[2]        | PC[13] | PI[1]  | PE[7]  | PH[8]        | PE[2]  | PE[4]  | PC[4]        | PE[3]  | PH[9]  | PI[4]  | PH[11]       | PE[14] | PA[10]          | PG[11]          | ļ |

| в | PH[13] | PC[14]       | PC[8]  | PC[12] | PI[3]  | PE[6]        | PH[5]  | PE[5]  | PC[5]        | PC[0]  | PC[2]  | PH[12] | PG[10]       | PA[11] | PA[9]           | PA[8]           | E |

| С | PH[14] | VDD_HV<br>_A | PC[9]  | PL[0]  | PI[0]  | PH[7]        | PH[6]  | VSS_LV | VDD_HV<br>_A | PA[5]  | PC[3]  | PE[15] | PG[14]       | PE[12] | PA[7]           | PE[13]          | C |

| D | PG[5]  | PI[6]        | PJ[4]  | PB[3]  | PK[15] | PI[2]        | PH[4]  | VDD_LV | PC[1]        | PH[10] | PA[6]  | PI[5]  | PG[15]       | PF[14] | PF[15]          | PH[2]           | I |

| Е | PG[3]  | PI[7]        | PH[15] | PG[2]  |        |              |        | I      |              | I      |        | I      | PG[0]        | PG[1]  | PH[0]           | VDD_HV<br>_A    | E |

| F | PA[2]  | PG[4]        | PA[1]  | PE[1]  |        |              |        |        |              |        |        |        | PH[1]        | PH[3]  | PG[12]          | PG[13]          |   |

| G | PE[8]  | PE[0]        | PE[10] | PA[0]  |        |              | VSS_HV | VSS_HV | VSS_HV       | VSS_HV |        |        | VDD_HV<br>_B | PI[13] | PI[12]          | PA[3]           | ( |

| н | PE[9]  | VDD_HV<br>_A | PE[11] | PK[1]  |        |              | VSS_LV | VSS_HV | VSS_HV       | VSS_HV |        |        | VDD_HV<br>_A | VDD_LV | VSS_LV          | PI[11]          | ł |

| J | VSS_HV | VRC_CT<br>RL | VDD_LV | PG[9]  |        |              | VSS_LV | VSS_LV | VSS_HV       | VSS_HV |        |        | PD[15]       | PI[8]  | PI[9]           | PI[10]          |   |

| к | RESET  | VSS_LV       | PG[8]  | PC[11] |        |              | VSS_LV | VSS_LV | VSS_LV       | VDD_LV |        |        | PD[14]       | PD[13] | PB[14]          | PB[15]          | ł |

| L | PC[10] | PG[7]        | PB[0]  | PK[2]  |        |              |        |        |              |        | l      |        | PD[12]       | PB[12] | PB[13]          | VDD_HV<br>_ADC1 | I |

| Μ | PG[6]  | PB[1]        | PK[4]  | PF[9]  |        |              |        |        |              |        |        |        | PB[11]       | PD[10] | PD[11]          | VSS_HV<br>_ADC1 | N |

| N | PK[3]  | PF[8]        | PC[6]  | PC[7]  | PJ[13] | VDD_HV<br>_A | PB[10] | PF[6]  | VDD_HV<br>_A | PJ[1]  | PD[2]  | PJ[5]  | PB[5]        | PB[6]  | PJ[6]           | PD[9]           | 1 |

| Ρ | PF[12] | PF[10]       | PF[13] | PA[14] | PJ[9]  | PA[12]       | PF[0]  | PF[5]  | PF[7]        | PJ[3]  | PI[15] | PD[4]  | PD[7]        | PD[8]  | PJ[8]           | PJ[7]           | F |

| R | PF[11] | PA[15]       | PJ[11] | PJ[15] | PA[13] | PF[2]        | PF[3]  | PF[4]  | VDD_LV       | PJ[2]  | PJ[0]  | PD[0]  | PD[3]        | PD[6]  | VDD_HV<br>_ADC0 | PB[7]           | I |

| т | PJ[12] | PA[4]        | PK[0]  | PJ[14] | PJ[10] | PF[1]        | XTAL   | EXTAL  | VSS_LV       | PB[9]  | PB[8]  | PI[14] | PD[1]        | PD[5]  | VSS_HV<br>_ADC0 | PB[4]           | T |

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

#### Notes:

VDD\_HV\_B supplies the IO voltage domain for the pins PE[12], PA[11], PA[10], PA[9], PA[8], PA[7], PE[13], PF[14], PF[15], PG[0], PG[1], PH[3], PH[2], PH[1], PH[0], PG[12], PG[13], and PA[3].

Availability of port pin alternate functions depends on product selection.

# Package pinouts and signal descriptions

|                    |         |                                              |                                                                                      |                                                           |                               |          |                  | Pir      | n numbe  | er         |

|--------------------|---------|----------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin        | PCR     | Alternate<br>function <sup>1</sup>           | Function                                                                             | Peripheral                                                | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PB[5]              | PCR[21] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[21]<br>—<br>—<br>ADC0_P[1]<br>ADC1_P[1]                                          | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          | -                             | I        | Tristate         | 91       | 107      | N13        |

| PB[6]              | PCR[22] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[22]<br>—<br>—<br>—<br>ADC0_P[2]<br>ADC1_P[2]                                     | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          | -<br>-<br>-<br>-              | I        | Tristate         | 92       | 108      | N14        |

| PB[7]              | PCR[23] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPI[23]<br>—<br>—<br>—<br>ADC0_P[3]<br>ADC1_P[3]                                     | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          |                               | I        | Tristate         | 93       | 109      | R16        |

| PB[8]              | PCR[24] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—<br>— | GPI[24]<br>—<br>—<br>ADC0_S[0]<br>ADC1_S[4]<br>WKPU[25]<br>OSC32k_XTAL <sup>4</sup>  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1<br>WKPU<br>SXOSC         | -                             | I        | _                | 61       | 77       | T11        |

| PB[9] <sup>5</sup> | PCR[25] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—<br>— | GPI[25]<br>—<br>—<br>ADC0_S[1]<br>ADC1_S[5]<br>WKPU[26]<br>OSC32k_EXTAL <sup>4</sup> | SIUL<br>—<br>ADC_0<br>ADC_1<br>WKPU<br>SXOSC              | <br> <br> <br> <br>           | I        |                  | 60       | 76       | T10        |

| PB[10]             | PCR[26] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—      | GPIO[26]<br>SOUT_1<br>CAN3TX<br>—<br>ADC0_S[2]<br>ADC1_S[6]<br>WKPU[8]               | SIUL<br>DSPI_1<br>FlexCAN_3<br><br>ADC_0<br>ADC_1<br>WKPU | I/O<br>O<br><br>I<br>I<br>I   | S        | Tristate         | 62       | 78       | N7         |

|                    |         |                                    |                                                |                                         |                               |          |                           | Pir      | n numbe  | er         |

|--------------------|---------|------------------------------------|------------------------------------------------|-----------------------------------------|-------------------------------|----------|---------------------------|----------|----------|------------|

| Port<br>pin        | PCR     | Alternate<br>function <sup>1</sup> | Function                                       | Peripheral                              | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config.          | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PB[11]             | PCR[27] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[27]<br>E0UC[3]<br>—<br>CS0_0<br>ADC0_S[3] | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>I/O<br>I        | S        | Tristate                  | 97       | 117      | M13        |

| PB[12]             | PCR[28] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[28]<br>E0UC[4]<br>—<br>CS1_0<br>ADC0_X[0] | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>0<br>I     | S        | Tristate                  | 101      | 123      | L14        |

| PB[13]             | PCR[29] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[29]<br>E0UC[5]<br>—<br>CS2_0<br>ADC0_X[1] | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>0<br>I     | S        | Tristate                  | 103      | 125      | L15        |

| PB[14]             | PCR[30] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[30]<br>E0UC[6]<br>—<br>CS3_0<br>ADC0_X[2] | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>0<br>I     | S        | Tristate                  | 105      | 127      | K15        |

| PB[15]             | PCR[31] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[31]<br>E0UC[7]<br>—<br>CS4_0<br>ADC0_X[3] | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0 | I/O<br>I/O<br>—<br>0<br>I     | S        | Tristate                  | 107      | 129      | K16        |

| PC[0] <sup>6</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                      | SIUL<br>—<br>JTAGC<br>—                 | I/O<br><br>I<br>              | M/S      | Input,<br>weak<br>pull-up | 154      | 178      | B10        |

| PC[1] <sup>6</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[33]<br>—<br>TDO<br>—                      | SIUL<br>—<br>JTAGC<br>—                 | I/O<br><br>                   | F/M      | Tristate                  | 149      | 173      | D9         |

| PC[2]              | PCR[34] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[34]<br>SCK_1<br>CAN4TX<br>—<br>EIRQ[5]    | SIUL<br>DSPI_1<br>FlexCAN_4<br><br>SIUL | I/O<br>I/O<br>O<br>I          | M/S      | Tristate                  | 145      | 169      | B11        |

| Table 4. Functional port pin descriptions (continued) |

|-------------------------------------------------------|

|-------------------------------------------------------|

## Package pinouts and signal descriptions

|             |         |                                            |                                                                        |                                                                |                                   |          |                  | Pir      | n numbe  | ər         |

|-------------|---------|--------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR     | Alternate<br>function <sup>1</sup>         | Function                                                               | Peripheral                                                     | I/O<br>direction <sup>2</sup>     | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PC[3]       | PCR[35] | AF0<br>AF1<br>AF2<br>AF3                   | GPIO[35]<br>CS0_1<br>MA[0]<br>—                                        | SIUL<br>DSPI_1<br>ADC_0<br>—                                   | I/O<br>I/O<br>O                   | S        | Tristate         | 144      | 168      | C11        |

|             |         | <br><br>                                   | CAN1RX<br>CAN4RX<br>EIRQ[6]                                            | FlexCAN_1<br>FlexCAN_4<br>SIUL                                 | <br> <br>                         |          |                  |          |          |            |

| PC[4]       | PCR[36] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4<br>—<br>— | GPIO[36]<br>E1UC[31]<br>—<br>FR_B_TX_EN<br>SIN_1<br>CAN3RX<br>EIRQ[18] | SIUL<br>eMIOS_1<br>—<br>Flexray<br>DSPI_1<br>FlexCAN_3<br>SIUL | /O<br> /O<br> <br> <br> <br> <br> | M/S      | Tristate         | 159      | 183      | A9         |

| PC[5]       | PCR[37] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4<br>—      | GPIO[37]<br>SOUT_1<br>CAN3TX<br>—<br>FR_A_TX<br>EIRQ[7]                | SIUL<br>DSPI_1<br>FlexCAN_3<br>—<br>Flexray<br>SIUL            | I/O<br>O<br>O<br>I                | M/S      | Tristate         | 158      | 182      | B9         |

| PC[6]       | PCR[38] | AF0<br>AF1<br>AF2<br>AF3                   | GPIO[38]<br>LIN1TX<br>E1UC[28]<br>—                                    | SIUL<br>LINFlexD_1<br>eMIOS_1<br>—                             | I/O<br>O<br>I/O<br>—              | S        | Tristate         | 44       | 52       | N3         |

| PC[7]       | PCR[39] | AF0<br>AF1<br>AF2<br>AF3<br>               | GPIO[39]<br>—<br>E1UC[29]<br>—<br>LIN1RX<br>WKPU[12]                   | SIUL<br>—<br>eMIOS_1<br>—<br>LINFlexD_1<br>WKPU                | /O<br><br> /O<br><br> <br>        | S        | Tristate         | 45       | 53       | N4         |

| PC[8]       | PCR[40] | AF0<br>AF1<br>AF2<br>AF3                   | GPIO[40]<br>LIN2TX<br>E0UC[3]<br>—                                     | SIUL<br>LINFlexD_2<br>eMIOS_0<br>—                             | I/O<br>O<br>I/O<br>—              | S        | Tristate         | 175      | 207      | В3         |

| PC[9]       | PCR[41] | AF0<br>AF1<br>AF2<br>AF3                   | GPIO[41]<br>—<br>E0UC[7]<br>—<br>LIN2RX                                | SIUL<br>—<br>eMIOS_0<br>—<br>LINFlexD_2                        | I/O<br>—<br>I/O<br>—<br>I         | S        | Tristate         | 2        | 2        | C3         |

|             |         | _                                          | WKPU[13]                                                               | WKPU                                                           | I                                 |          |                  |          |          |            |

## Package pinouts and signal descriptions

|             |         |                                         |                                                               |                                                       |                                    |          |                  | Pir      | n numbe  | er         |

|-------------|---------|-----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|------------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR     | Alternate<br>function <sup>1</sup>      | Function                                                      | Peripheral                                            | I/O<br>direction <sup>2</sup>      | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PD[15]      | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4        | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>FR_DBG[1]               | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>Flexray             | 1/0 0/0<br>1/0   0                 | S        | Tristate         | 106      | 128      | J13        |

| PE[0]       | PCR[64] | —<br>AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | ADC0_S[7]<br>GPIO[64]<br>E0UC[16]<br><br>CAN5RX<br>WKPU[6]    | ADC_0<br>SIUL<br>eMIOS_0<br>—<br>FlexCAN_5<br>WKPU    | <br> /O<br> /O<br> -<br> <br> <br> | S        | Tristate         | 18       | 18       | G2         |

| PE[1]       | PCR[65] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[65]<br>E0UC[17]<br>CAN5TX<br>—                           | SIUL<br>eMIOS_0<br>FlexCAN_5<br>—                     | I/O<br>I/O<br>O<br>—               | M/S      | Tristate         | 20       | 20       | F4         |

| PE[2]       | PCR[66] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4<br>—   | GPIO[66]<br>E0UC[18]<br>—<br>FR_A_TX_EN<br>SIN_1<br>EIRQ[21]  | SIUL<br>eMIOS_0<br>—<br>Flexray<br>DSPI_1<br>SIUL     | /O<br> /O<br> -<br> <br> <br> <br> | M/S      | Tristate         | 156      | 180      | A7         |

| PE[3]       | PCR[67] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[67]<br>E0UC[19]<br>SOUT_1<br>—<br>FR_A_RX<br>WKPU[29]    | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>Flexray<br>WKPU     | /O<br> /O<br><br> <br>             | M/S      | Tristate         | 157      | 181      | A10        |

| PE[4]       | PCR[68] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4<br>—   | GPIO[68]<br>E0UC[20]<br>SCK_1<br>—<br>FR_B_TX<br>EIRQ[9]      | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>Flexray<br>SIUL     | /O<br> /O<br> /O<br><br>0<br>      | M/S      | Tristate         | 160      | 184      | A8         |

| PE[5]       | PCR[69] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[69]<br>E0UC[21]<br>CS0_1<br>MA[2]<br>FR_B_RX<br>WKPU[30] | SIUL<br>eMIOS_0<br>DSPI_1<br>ADC_0<br>Flexray<br>WKPU | /O<br> /O<br> /O<br>0<br> <br>     | M/S      | Tristate         | 161      | 185      | B8         |

|             |          |                                    |                          |                     |                               |          |                  | Pir      | n numbe  | ər         |

|-------------|----------|------------------------------------|--------------------------|---------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                 | Peripheral          | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PM[4]       | PCR[196] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[196]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>                       | M/S      | Tristate         |          | _        | L12        |

| PM[5]       | PCR[197] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[197]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>                       | M/S      | Tristate         | _        | _        | F9         |

| PM[6]       | PCR[198] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[198]<br>—<br>—<br>— | SIUL<br>—<br>—<br>— | I/O<br>—<br>—<br>—            | M/S      | Tristate         |          | _        | F6         |

Table 4. Functional port pin descriptions (continued)

NOTES:

- <sup>1</sup> Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 000 → AF0; PCR.PA = 001 → AF1; PCR.PA = 010 → AF2; PCR.PA = 011 → AF3; PCR.PA = 100 → ALT4. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

- <sup>2</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- <sup>3</sup> NMI[0] and NMI[1] have a higher priority than alternate functions. When NMI is selected, the PCR.PA field is ignored.

- <sup>4</sup> SXOSC's OSC32k\_XTAL and OSC32k\_EXTAL pins are shared with GPIO functionality. When used as crystal pins, other functionality of the pin cannot be used and it should be ensured that application never programs OBE and PUE bit of the corresponding PCR to "1".

- <sup>5</sup> If you want to use OSC32K functionality through PB[8] and PB[9], you must ensure that PB[10] is static in nature as PB[10] can induce coupling on PB[9] and disturb oscillator frequency.

- <sup>6</sup> Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO.

PC[0:1] are available as JTAG pins (TDI and TDO respectively).

PH[9:10] are available as JTAG pins (TCK and TMS respectively).

It is up to the user to configure these pins as GPIO when needed.

- <sup>7</sup> When MBIST is enabled to run (STCU Enable = 1), the application must not drive or tie PAD[178) (MDO[0]) to 0 V before the device exits reset (external reset is removed) as the pad is internally driven to 1 to indicate MBIST operation. When MBIST is not enabled (STCU Enable = 0), there are no restriction as the device does not internally drive the pad.

- <sup>8</sup> These pins can be configured as Nexus pins during reset by the debugger writing to the Nexus Development Interface "Port Control Register" rather than the SIUL. Specifically, the debugger can enable the MDO[7:0], MSEO, and MCKO ports by programming NDI (PCR[MCKO\_EN] or PCR[PSTAT\_EN]). MDO[8:11] ports can be enabled by programming NDI ((PCR[MCKO\_EN] and PCR[FPM]) or PCR[PSTAT\_EN]).

Medium and fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

# 4.6.2 I/O input DC characteristics

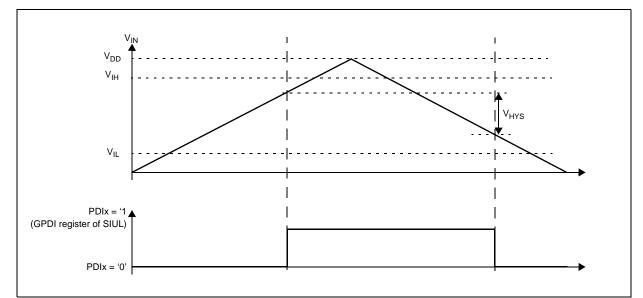

Table 13 provides input DC electrical characteristics as described in Figure 5.

Figure 5. I/O input DC electrical characteristics definition

| Symb             |    | с | Parameter                                                     | Condi                               | tions <sup>1</sup>      |                     | Value <sup>2</sup> |                       | Unit |

|------------------|----|---|---------------------------------------------------------------|-------------------------------------|-------------------------|---------------------|--------------------|-----------------------|------|

| - Oynic          |    | 0 | i arameter                                                    | Cond                                |                         | Min                 | Тур                | Мах                   | onne |

| V <sub>IH</sub>  | SR | Ρ | Input high level CMOS (Schmitt<br>Trigger)                    | _                                   | _                       | 0.65V <sub>DD</sub> | _                  | V <sub>DD</sub> + 0.4 | V    |

| V <sub>IL</sub>  | SR | Ρ | Input low level CMOS (Schmitt<br>Trigger)                     | -                                   | _                       | -0.3                | _                  | 0.35V <sub>DD</sub>   |      |

| V <sub>HYS</sub> | СС | С | Input hysteresis CMOS (Schmitt<br>Trigger)                    | -                                   | _                       | 0.1V <sub>DD</sub>  | —                  | _                     |      |

| I <sub>LKG</sub> | СС | Ρ | Digital input leakage                                         | No injection $T_A = -40 \text{ °C}$ |                         | —                   | 2                  | _                     | nA   |

|                  |    | Ρ |                                                               | on adjacent<br>pin                  | T <sub>A</sub> = 25 °C  | —                   | 2                  | _                     |      |

|                  |    | D |                                                               |                                     | T <sub>A</sub> = 105 °C | —                   | 12                 | 500                   |      |

|                  |    | Ρ |                                                               |                                     | T <sub>A</sub> = 125 °C | —                   | 70                 | 1000                  |      |

| W <sub>FI</sub>  | SR | Ρ | Width of input pulse rejected by analog filter <sup>3</sup>   | -                                   | _                       | —                   | _                  | 40 <sup>4</sup>       | ns   |

| W <sub>NFI</sub> | SR | Ρ | Width of input pulse accepted by analog filter <sup>(3)</sup> | -                                   | _                       | 1000 <sup>4</sup>   | —                  | —                     | ns   |

NOTES:

$V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

# NP

#### **Electrical Characteristics**

- $^{2}$  V<sub>DD</sub> as mentioned in the table is V<sub>DD\_HV\_A</sub>/V<sub>DD\_HV\_B</sub>. All values need to be confirmed during device validation.

- <sup>3</sup> Analog filters are available on all wakeup lines.

- <sup>4</sup> The width of input pulse in between 40 ns to 1000 ns is indeterminate. It may pass the noise or may not depending on silicon sample to sample variation.

# 4.6.3 I/O output DC characteristics

The following tables provide DC characteristics for bidirectional pads:

- Table 14 provides weak pull figures. Both pull-up and pull-down resistances are supported.

- Table 15 provides output driver characteristics for I/O pads when in SLOW configuration.

- Table 16 provides output driver characteristics for I/O pads when in MEDIUM configuration.

- Table 17 provides output driver characteristics for I/O pads when in FAST configuration.

| Svm              | Symbol |   | Parameter                                                            | Conditio                                                             | Value             |     |     |     |      |  |

|------------------|--------|---|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|-----|-----|-----|------|--|

| Cymbol           |        | С | i di difictei                                                        | Contaniono                                                           |                   | Min | Тур | Мах | Unit |  |

| I <sub>WPU</sub> | CC     | Р |                                                                      | $V_{IN} = V_{IL}, V_{DD} =$                                          | PAD3V5V = 0       | 10  | _   | 150 | μA   |  |

|                  |        | С | current absolute 5<br>value                                          | 5.0 V ± 10%                                                          | $PAD3V5V = 1^{3}$ | 10  | _   | 250 |      |  |

|                  |        | Ρ |                                                                      | V <sub>IN</sub> = V <sub>IL</sub> , V <sub>DD</sub> =<br>3.3 V ± 10% | PAD3V5V = 1       | 10  | _   | 150 |      |  |

| I <sub>WPD</sub> |        |   |                                                                      | PAD3V5V = 0                                                          | 10                |     | 150 | μA  |      |  |

|                  |        | С | current absolute value                                               | 5.0 V ± 10%                                                          | PAD3V5V = 1       | 10  |     | 250 |      |  |

|                  | P      |   | V <sub>IN</sub> = V <sub>IH</sub> , V <sub>DD</sub> =<br>3.3 V ± 10% | PAD3V5V = 1                                                          | 10                |     | 150 |     |      |  |

## Table 14. I/O pull-up/pull-down DC electrical characteristics

NOTES:

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified.

$^2~V_{DD}$  as mentioned in the table is  $V_{DD\_HV\_A}\!/V_{DD\_HV\_B}.$

<sup>3</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

| Table 15. SLOW configuration output buff | fer electrical characteristics |

|------------------------------------------|--------------------------------|

|------------------------------------------|--------------------------------|

| Sv              | Symbol C Parameter |   | C | Parameter     |           | Conditions <sup>1,2</sup>                                                             |                       | Value |   | Unit |

|-----------------|--------------------|---|---|---------------|-----------|---------------------------------------------------------------------------------------|-----------------------|-------|---|------|

| Uy,             |                    |   |   | Conditions    | Min       | Тур                                                                                   | Мах                   | Onic  |   |      |

| V <sub>Oł</sub> | H C                | C |   | SLOW          | Push Pull | I <sub>OH</sub> = -3 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                | 0.8V <sub>DD</sub>    | _     | _ | V    |

|                 |                    | ( | С | configuration |           | $I_{OH} = -3 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^3$ | 0.8V <sub>DD</sub>    |       | _ |      |

|                 |                    |   | Ρ |               |           | I <sub>OH</sub> = −1.5 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1              | V <sub>DD</sub> - 0.8 | _     | _ |      |

| Sum             | nbol | с | Parameter                                  |           | onditions <sup>1,2</sup>                                                                     |                       | Value |                    | Unit |

|-----------------|------|---|--------------------------------------------|-----------|----------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|------|

| J               |      | C | Farameter                                  |           |                                                                                              |                       | Тур   | Мах                | Onit |

| V <sub>OH</sub> | CC   | Р | Output high level<br>FAST<br>configuration | Push Pull | $I_{OH} = -14 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0              | 0.8V <sub>DD</sub>    |       | _                  | V    |

|                 |      | С |                                            |           | $I_{OH} = -7 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 <sup>3</sup>  | 0.8V <sub>DD</sub>    | _     | _                  |      |

|                 |      | С |                                            |           | $I_{OH} = -11 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1              | V <sub>DD</sub> – 0.8 |       | —                  |      |

| V <sub>OL</sub> | CC   | Р | Output low level<br>FAST<br>configuration  | Push Pull | I <sub>OL</sub> = 14 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0                    | —                     | _     | 0.1V <sub>DD</sub> | V    |

|                 |      | С |                                            |           | $I_{OL} = 7 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 <sup>(3)</sup> | —                     | _     | 0.1V <sub>DD</sub> |      |

|                 |      | С |                                            |           | I <sub>OL</sub> = 11 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                    | —                     | _     | 0.5                |      |

Table 17. FAST configuration output buffer electrical characteristics

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

$^2~V_{DD}$  as mentioned in the table is  $V_{DD\_HV\_A}/V_{DD\_HV\_B}.$

<sup>3</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus outputs (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

#### **Output pin transition times** 4.6.4

Table 18. Output pin transition times

| 6, | Symbol ( |    | с | Parameter                                     | Cor                     | nditions <sup>1,2</sup>     |     | Unit |     |    |

|----|----------|----|---|-----------------------------------------------|-------------------------|-----------------------------|-----|------|-----|----|

| 3  |          |    | C | Farameter                                     | Conditions              |                             | Min | Тур  | Max |    |

| Tt | tr       | CC | D | Output transition time                        | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 V \pm 10\%$ , |     | —    | 50  | ns |

|    |          |    | Т | output pin <sup>4</sup><br>SLOW configuration | C <sub>L</sub> = 50 pF  | PAD3V5V = 0                 |     | _    | 100 |    |

|    |          |    | D | -                                             | C <sub>L</sub> = 100 pF |                             |     | —    | 125 |    |

|    |          |    | D | -                                             | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 V \pm 10\%,$  |     | —    | 40  |    |

|    |          |    | Т |                                               | C <sub>L</sub> = 50 pF  | PAD3V5V = 1                 |     | _    | 50  |    |

|    |          |    | D |                                               | C <sub>L</sub> = 100 pF |                             |     | —    | 75  |    |

| Package  |                         |                       |                         | I/O Su                | pplies                  |                         |   |   |

|----------|-------------------------|-----------------------|-------------------------|-----------------------|-------------------------|-------------------------|---|---|

| 176 LQFP | pin6                    | pin27                 | pin57                   | pin85                 | pin123                  | pin150                  | — | _ |

|          | (V <sub>DD_HV_A</sub> ) | $(V_{DD_HV_A})$       | (V <sub>SS_HV</sub> )   | $(V_{DD_HV_A})$       | (V <sub>SS_HV</sub> )   | (V <sub>SS_HV</sub> )   |   |   |

|          | pin7                    | pin28                 | pin59                   | pin86                 | pin124                  | pin151                  |   |   |

|          | (V <sub>SS_HV</sub> )   | (V <sub>SS_HV</sub> ) | (V <sub>DD_HV_A</sub> ) | (V <sub>SS_HV</sub> ) | (V <sub>DD_HV_B</sub> ) | (V <sub>DD_HV_A</sub> ) |   |   |

# Table 19. I/O supplies (continued)

# Table 20. I/O consumption

| Symbol                             |    | с | Parameter                                  | Conditi                         | ions <sup>1,2</sup>                           |     | Value <sup>3</sup> |       | Unit |

|------------------------------------|----|---|--------------------------------------------|---------------------------------|-----------------------------------------------|-----|--------------------|-------|------|

| Symbol                             |    | C | Farameter                                  | Conditi                         |                                               | Min | Тур                | Мах   | Unit |

| I <sub>SWTSLW</sub> ,4             | СС | D | Peak I/O current for<br>SLOW configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   | _                  | 19.9  |      |

|                                    |    |   |                                            |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _                  | 15.5  | mA   |

| I <sub>SWTMED</sub> <sup>(4)</sup> | СС | D | Peak I/O current for<br>MEDIUM             | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | —                  | 28.8  |      |

|                                    |    |   | configuration                              |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _                  | 16.3  | mA   |

| I <sub>SWTFST</sub> <sup>(4)</sup> | СС | D | Peak I/O current for<br>FAST configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   | _                  | 113.5 |      |

|                                    |    |   |                                            |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _                  | 52.1  | mA   |

| I <sub>RMSSLW</sub>                | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 5.0 V \pm 10\%$                     |     | —                  | 2.22  |      |

|                                    |    |   | I/O current for SLOW configuration         | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 0                                   | _   | —                  | 3.13  | mA   |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 2 MHz  |                                               | _   | _                  | 6.54  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     |                    | 1.51  | mA   |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 1                                   | _   | _                  | 2.14  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 2 MHz  |                                               | _   | _                  | 4.33  |      |

| IRMSMED                            | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   |     |                    | 6.5   | mA   |

|                                    |    |   | I/O current for<br>MEDIUM                  | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 0                                   |     |                    | 13.32 | 1    |

|                                    |    |   | configuration                              | C <sub>L</sub> = 100 pF, 13 MHz |                                               |     |                    | 18.26 |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     |                    | 4.91  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 1                                   |     |                    | 8.47  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 13 MHz |                                               |     |                    | 10.94 |      |

| I <sub>RMSFST</sub>                | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   |     |                    | 21.05 | mA   |

|                                    |    |   | I/O current for FAST configuration         | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 0                                   |     |                    | 33    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 40 MHz |                                               |     |                    | 55.77 |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   | _   | —                  | 14    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 1                                   |     |                    | 20    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 40 MHz |                                               | _   | _                  | 34.89 |      |

MPC5646C Data Sheet, Rev.6

| Ok. al                |    | ( | Descention                          | Condi            |                         |     | 1                | Unit               |      |

|-----------------------|----|---|-------------------------------------|------------------|-------------------------|-----|------------------|--------------------|------|

| Symbol                |    | С | Parameter                           | Condi            | tions                   | Min | Typ <sup>3</sup> | Max <sup>4</sup>   | Unit |

| I <sub>DDMAX</sub> 5  | СС | D | RUN mode maximum<br>average current | _                | _                       | —   | 210              | 300 <sup>6,7</sup> | mA   |

| IDDRUN                | СС | Ρ | RUN mode typical average            | at 120 MHz       | T <sub>A</sub> = 25 °C  | _   | 150              | 200 <sup>9</sup>   | mA   |

|                       |    | D | current <sup>8</sup>                | at 80 MHz        | T <sub>A</sub> = 25 °C  | —   | 110 <sup>8</sup> | 150 <sup>10</sup>  | mA   |

|                       |    | С |                                     | at 120 MHz       | T <sub>A</sub> = 125 °C | _   | 180              | 270                | mA   |

| IDDHALT               | СС | Ρ | HALT mode current <sup>11</sup>     | at 120 MHz       | T <sub>A</sub> = 25 °C  | —   | 20               | 27                 | mA   |

|                       |    | С |                                     | at 120 MHz       | T <sub>A</sub> = 125 °C | —   | 35               | 113                | mA   |

| IDDSTOP               | СС | Ρ | STOP mode current <sup>12</sup>     | No clocks active | T <sub>A</sub> = 25 °C  | _   | 0.4              | 3                  | mA   |

|                       |    | С |                                     |                  | T <sub>A</sub> = 125 °C | _   | 16               | 95                 | mA   |

| I <sub>DDSTDBY3</sub> | СС | Ρ | STANDBY3 mode                       | No clocks active | T <sub>A</sub> = 25 °C  | —   | 50               | 99                 | μA   |

| (96 KB RAM retained)  |    | С | current <sup>13</sup>               |                  | T <sub>A</sub> = 125 °C | -   | 630              | 3200               | μA   |

| IDDSTDBY2             | СС | С | STANDBY2 mode                       | No clocks active | T <sub>A</sub> = 25 °C  | —   | 40               | 94                 | μΑ   |

| (64 KB RAM retained)  |    | С | current <sup>14</sup>               |                  | T <sub>A</sub> = 125 °C | -   | 500              | 2500               | μA   |

| IDDSTDBY1             | СС | С |                                     | No clocks active | T <sub>A</sub> = 25 °C  | —   | 25               | 87                 | μΑ   |

| (8 KB RAM retained)   |    | С | current <sup>15</sup>               |                  | T <sub>A</sub> = 125 °C | -   | 230              | 1250               | μA   |

| Adders in LP          | СС | Т | 32 KHz OSC                          |                  | T <sub>A</sub> = 25 °C  | —   | _                | 5                  | μΑ   |

| mode                  |    |   | 4–40 MHz OSC                        | —                | T <sub>A</sub> = 25 °C  | —   | _                | 3                  | mA   |

|                       |    |   | 16 MHz IRC                          |                  | T <sub>A</sub> = 25 °C  |     |                  | 500                | μA   |

|                       |    |   | 128 KHz IRC                         |                  | T <sub>A</sub> = 25 °C  | —   | —                | 5                  | μA   |

| Table 24. Low voltage power domain electrical characteristics <sup>1</sup> |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

NOTES:

<sup>1</sup> Except for  $I_{DDMAX}$ , all the current values are total current drawn from  $V_{DD_{-HV_{-}A}}$ .

- $^2$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified All temperatures are based on an ambient temperature.

- <sup>3</sup> Target typical current consumption for the following typical operating conditions and configuration. Process = typical, Voltage = 1.2 V.

- <sup>4</sup> Target maximum current consumption for mode observed under typical operating conditions. Process = Fast, Voltage = 1.32 V.

- <sup>5</sup> Running consumption is given on voltage regulator supply (V<sub>DDREG</sub>). It does not include consumption linked to I/Os toggling. This value is highly dependent on the application. The given value is thought to be a worst case value with all cores and peripherals running, and code fetched from code flash while modify operation on-going on data flash. It is to be noticed that this value can be significantly reduced by application: switch-off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- <sup>6</sup> Higher current may sunk by device during power-up and standby exit. Please refer to in rush current in Table 22.

- <sup>7</sup> Maximum "allowed" current is package dependent.

- <sup>8</sup> Only for the "P" classification: Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled. RUN current measured with typical application with accesses on both code flash and RAM.

ECC circuitry provides correction of single bit faults and is used to improve further automotive reliability results. Some units will experience single bit corrections throughout the life of the product with no impact to product reliability.

|                   | Symbol |   |                                     | Cond                 | itions <sup>2</sup>  | Frequency |      |

|-------------------|--------|---|-------------------------------------|----------------------|----------------------|-----------|------|

| Sym               |        |   | Parameter                           | Code flash<br>memory | Data flash<br>memory | range     | Unit |

| f <sub>READ</sub> | CC     | Ρ | Maximum frequency for Flash reading | 5 wait states        | 13 wait states       | 120 —100  |      |

|                   |        | С |                                     | 4 wait states        | 11 wait states       | 100—80    | MHz  |

|                   |        | D |                                     | 3 wait states        | 9 wait states        | 80—64     |      |

|                   |        | С |                                     | 2 wait states        | 7 wait states        | 64—40     |      |

|                   |        | С |                                     | 1 wait states        | 4 wait states        | 40—20     |      |

|                   |        | С |                                     | 0 wait states        | 2 wait states        | 20—0      |      |

| Table 28 | Flash | memory | read | access | timing <sup>1</sup> |

|----------|-------|--------|------|--------|---------------------|

|----------|-------|--------|------|--------|---------------------|

NOTES:

<sup>1</sup> Max speed is the maximum speed allowed including PLL frequency modulation (FM).

$^2~$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

#### 4.10.2 Flash memory power supply DC characteristics

Table 29 shows the flash memory power supply DC characteristics on external supply.

| S                 | Symbol             |    | Parameter                                                                          | Conditions <sup>1</sup>                                      |                      | Unit |     |     |    |

|-------------------|--------------------|----|------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------|------|-----|-----|----|

|                   |                    |    | i alameter                                                                         | Conditions                                                   | Min                  | Тур  | Max |     |    |

| I <sub>CFR</sub>  | EAD <sup>3</sup>   | CC | Sum of the current consumption on $V_{DD\_HV\_A}$ on read access                   | Flash memory module read $f_{CPU} = 120 \text{ MHz} + 2\%^4$ | Code flash<br>memory |      |     | 33  | mA |

| I <sub>DFRE</sub> | EAD <sup>(3)</sup> |    |                                                                                    |                                                              | Data flash<br>memory |      |     | 13  |    |

| I <sub>CFM</sub>  | OD <sup>(3)</sup>  | CC | Sum of the current consumption on $V_{DD_HV_A}$ (program/erase)                    | Program/Erase on-going while reading flash memory            | Code flash<br>memory |      |     | 52  | mA |

| I <sub>DFM</sub>  | OD <sup>(3)</sup>  |    |                                                                                    | registers<br>f <sub>CPU</sub> = 120 MHz + 2% <sup>(4)</sup>  | Data flash<br>memory |      |     | 13  |    |

| I <sub>CFLF</sub> | PW <sup>(3)</sup>  | CC | Sum of the current consumption on $V_{DD_HV_A}$ during flash memory low power mode |                                                              | Code flash<br>memory |      |     | 1.1 | mA |

| I <sub>CFP\</sub> | WD <sup>(3)</sup>  |    | Sum of the current consumption on $V_{DD\_HV\_A}$ during flash                     |                                                              | Code flash<br>memory |      |     | 150 | μA |

| I <sub>DFP\</sub> | WD <sup>(3)</sup>  |    | memory power down mode                                                             |                                                              | Data flash<br>memory |      |     | 150 |    |

NOTES: <sup>1</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% \text{ / } 5.0 \text{ V} \pm 10\%, \text{ T}_{\text{A}} = -40 \text{ to } 125 \text{ °C}, \text{ unless otherwise specified.}$ <sup>2</sup> All values need to be confirmed during device validation.

NOTES:

- All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

- <sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

- <sup>3</sup> Data based on characterization results, not tested in production.

# 4.11.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply over-voltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

## Table 33. Latch-up results

| Symbol | Parameter | Conditions                                       | Class      |

|--------|-----------|--------------------------------------------------|------------|

| LU     | -         | $T_A = 125 \ ^{\circ}C$<br>conforming to JESD 78 | II level A |

# 4.12 Fast external crystal oscillator (4–40 MHz) electrical characteristics

The device provides an oscillator/resonator driver. Figure 10 describes a simple model of the internal oscillator driver and provides an example of a connection for an oscillator or a resonator.

Table 34 provides the parameter description of 4 MHz to 40 MHz crystals used for the design simulations.

| Symbol          | Symbol |   | Parameter                                     | Conditions <sup>1</sup>   |                          | Value <sup>2</sup> |                            | Unit |

|-----------------|--------|---|-----------------------------------------------|---------------------------|--------------------------|--------------------|----------------------------|------|

| Gymbol          |        | С | i arameter                                    | Conditions                | Min 1                    |                    | Мах                        | Onic |

| V <sub>IH</sub> | SR     | Ρ | Input high level<br>CMOS<br>(Schmitt Trigger) | Oscillator bypass<br>mode | 0.65V <sub>DD_HV_A</sub> | —                  | V <sub>DD_HV_A</sub> + 0.4 | V    |

| V <sub>IL</sub> | SR     | Ρ | Input low level<br>CMOS<br>(Schmitt Trigger)  | Oscillator bypass<br>mode | -0.3                     | _                  | 0.35V <sub>DD_HV_</sub> A  | V    |

Table 35. Fast external crystal oscillator (4 to 40 MHz) electrical characteristics

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> Based on ATE Cz

<sup>4</sup> Stated values take into account only analog module consumption but not the digital contributor (clock tree and enabled peripherals).

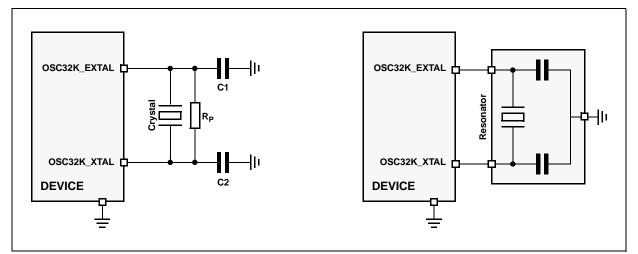

#### 4.13 Slow external crystal oscillator (32 kHz) electrical characteristics

The device provides a low power oscillator/resonator driver.

Figure 12. Crystal oscillator and resonator connection scheme

# NOTE

OSC32K\_XTAL/OSC32K\_EXTAL must not be directly used to drive external circuits.

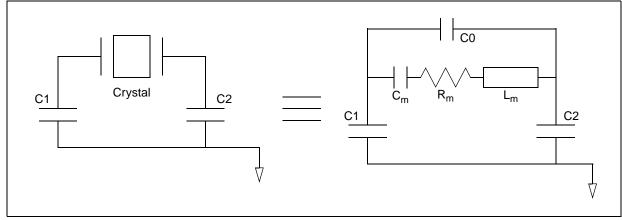

Figure 13. Equivalent circuit of a quartz crystal

| Table 36 | Crystal | motional | characteristics <sup>1</sup> |

|----------|---------|----------|------------------------------|

|----------|---------|----------|------------------------------|

| Symbol                      | Parameter                                                                            | Conditions                               |     | Unit   |     |      |

|-----------------------------|--------------------------------------------------------------------------------------|------------------------------------------|-----|--------|-----|------|

| Symbol                      | raiametei                                                                            | Conditions                               | Min | Тур    | Max | Onic |

| L <sub>m</sub>              | Motional inductance                                                                  | —                                        | _   | 11.796 |     | КН   |

| C <sub>m</sub>              | Motional capacitance                                                                 | —                                        | _   | 2      |     | fF   |

| C1/C2                       | Load capacitance at OSC32K_XTAL and OSC32K_EXTAL with respect to ground <sup>2</sup> | _                                        | 18  | —      | 28  | pF   |

| R <sub>m</sub> <sup>3</sup> | Motional resistance                                                                  | AC coupled @ $C0 = 2.85 \text{ pF}^4$    | _   | —      | 65  | kΩ   |

|                             |                                                                                      | AC coupled @ $C0 = 4.9 \text{ pF}^{(4)}$ |     | —      | 50  |      |

|                             |                                                                                      | AC coupled @ $C0 = 7.0 \text{ pF}^{(4)}$ | _   | —      | 35  |      |

|                             |                                                                                      | AC coupled @ $C0 = 9.0 \text{ pF}^{(4)}$ |     | —      | 30  |      |

NOTES: <sup>1</sup> The crystal used is Epson Toyocom MC306.

$^2\,$  This is the recommended range of load capacitance at OSC32K\_XTAL and OSC32K\_EXTAL with respect to ground. It includes all the parasitics due to board traces, crystal and package.

$^3$  Maximum ESR (R<sub>m</sub>) of the crystal is 50 k\Omega.

<sup>4</sup> C0 Includes a parasitic capacitance of 2.0 pF between OSC32K\_XTAL and OSC32K\_EXTAL pins.

| Symbol                |    | с | Parameter                                                                                                                                                 | C                       | onditions <sup>1</sup>            |    | Value <sup>2</sup> |     | Unit |

|-----------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|----|--------------------|-----|------|

| Cymbol                |    | Ŭ | i alameter                                                                                                                                                |                         |                                   |    |                    | Мах | Unit |

| I <sub>FIRCSTOP</sub> | CC | Т | Fast internal RC oscillator high                                                                                                                          | T <sub>A</sub> = 25 °C  | sysclk = off                      | _  | 500                |     | μΑ   |

|                       |    |   | frequency and system clock<br>current in stop mode                                                                                                        |                         | sysclk = 2 MHz                    | —  | 600                |     |      |

|                       |    |   | ,                                                                                                                                                         |                         | sysclk = 4 MHz                    | —  | 700                |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 8 MHz                    | —  | 900                |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 16 MHz                   | _  | 1250               | —   |      |

| T <sub>FIRCSU</sub>   | СС | С | Fast internal RC oscillator                                                                                                                               | T <sub>A</sub> = 55 °C  | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | _  |                    | 2.0 | μs   |

|                       |    | _ | start-up time                                                                                                                                             |                         | $V_{DD} = 3.3 \text{ V} \pm 10\%$ | _  |                    | 5   |      |

|                       |    | — |                                                                                                                                                           | T <sub>A</sub> = 125 °C | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | —  |                    | 2.0 |      |

|                       |    | _ |                                                                                                                                                           |                         | $V_{DD} = 3.3 \text{ V} \pm 10\%$ | _  |                    | 5   |      |

| <sup>Δ</sup> fircpre  | СС | С | Fast internal RC oscillator<br>precision after software<br>trimming of f <sub>FIRC</sub>                                                                  | Т                       | <sub>A</sub> = 25 °C              | -1 |                    | +1  | %    |

|                       | СС | С | Fast internal RC oscillator<br>trimming step                                                                                                              | Т                       | <sub>A</sub> = 25 °C              | _  | 1.6                |     | %    |

|                       | CC | С | Fast internal RC oscillator<br>variation over temperature and<br>supply with respect to $f_{FIRC}$ at<br>$T_A = 25$ °C in high-frequency<br>configuration |                         | -5                                |    | +5                 | %   |      |

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

#### 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz low power internal RC oscillator. This can be used as the reference clock for the RTC module.

| Symbol C                        |    | с | Parameter                                            | Conditions <sup>1</sup>           |     | Value <sup>2</sup> |     | Unit |

|---------------------------------|----|---|------------------------------------------------------|-----------------------------------|-----|--------------------|-----|------|

|                                 |    | Ŭ | i di di lictori                                      | Conditions                        | Min | Тур                | Max | •    |

| f <sub>SIRC</sub>               | СС | Ρ | Slow internal RC oscillator low                      | T <sub>A</sub> = 25 °C, trimmed   | _   | 128                | _   | kHz  |

|                                 | SR |   | frequency                                            | untrimmed, across<br>temperatures | 84  | _                  | 205 |      |

| I <sub>SIRC</sub> <sup>3,</sup> | СС |   | Slow internal RC oscillator low<br>frequency current | T <sub>A</sub> = 25 °C, trimmed   | —   | _                  | 5   | μA   |

Table 40. Slow internal RC oscillator (128 kHz) electrical characteristics

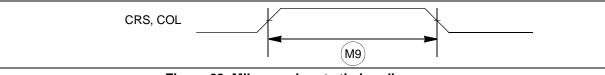

Figure 23. MII async inputs timing diagram

#### 4.18.4 **MII Serial Management Channel Timing (MDIO and MDC)**

The FEC functions correctly with a maximum MDC frequency of 2.5 MHz.

| Spec | Characteristic                                                               | Min | Max | Unit       |

|------|------------------------------------------------------------------------------|-----|-----|------------|

| M10  | MDC falling edge to<br>MDIO output invalid<br>(minimum<br>propagation delay) | 0   | _   | ns         |

| M11  | MDC falling edge to<br>MDIO output valid<br>(max prop delay)                 | _   | 25  | ns         |

| M12  | MDIO (input) to MDC<br>rising edge setup                                     | 28  | -   | ns         |

| M13  | MDIO (input) to MDC<br>rising edge hold                                      | 0   | _   | ns         |

| M14  | MDC pulse width high                                                         | 40% | 60% | MDC period |

| M15  | MDC pulse width low                                                          | 40% | 60% | MDC period |

# Table 47. MII serial management channel timing<sup>1</sup>

NOTES: <sup>1</sup> Output pads configured with SRE = 0b11.

| NOTES:                                                                                                                                                                                                                                                                                                                                                          |                            |          |             |             |             |     |      |         |        |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|-------------|-------------|-------------|-----|------|---------|--------|--|--|--|

| 1. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE<br>PROTRUSION IS 0.25MM PER SIDE. DIMENSIONS D1 AND E1 DO INCLUDE<br>MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE DATUM H.                                                                                                                                                                 |                            |          |             |             |             |     |      |         |        |  |  |  |