Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5646ccf0vlu1 |

|----------------------------|-------------------------------------------------------------------------|

| Supplier Device Package    | 176-LQFP (24x24)                                                        |

| Package / Case             | 176-LQFP                                                                |

| Mounting Type              | Surface Mount                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Oscillator Type            | Internal                                                                |

| Data Converters            | A/D 27x10b, 5x12b                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| RAM Size                   | 256К х 8                                                                |

| EEPROM Size                | 64K x 8                                                                 |

| Program Memory Type        | FLASH                                                                   |

| Program Memory Size        | 3MB (3M x 8)                                                            |

| Number of I/O              | 147                                                                     |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SCI, SPI                    |

| Speed                      | 80MHz/120MHz                                                            |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Core Processor             | e200z4d, e200z0h                                                        |

| Product Status             | Active                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |         |                                    |                                                          |                                                           |                                  |          |                  | Pir      | n numbe  | ər         |

|-------------|---------|------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                 | Peripheral                                                | I/O<br>direction <sup>2</sup>    | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PA[13]      | PCR[13] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[13]<br>SOUT_0<br>E0UC[29]<br>—                      | SIUL<br>DSPI_0<br>eMIOS_0<br>—                            | I/O<br>O<br>I/O<br>—             | M/S      | Tristate         | 52       | 66       | R5         |

| PA[14]      | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[14]<br>SCK_0<br>CS0_0<br>E0UC[0]<br>EIRQ[4]         | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>SIUL               | I/O<br>I/O<br>I/O<br>I/O<br>I    | M/S      | Tristate         | 50       | 58       | P4         |

| PA[15]      | PCR[15] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[15]<br>CS0_0<br>SCK_0<br>E0UC[1]<br>WKPU[10]        | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>WKPU               | I/O<br>I/O<br>I/O<br>I/O<br>I    | M/S      | Tristate         | 48       | 56       | R2         |

| PB[0]       | PCR[16] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[16]<br>CAN0TX<br>E0UC[30]<br>LIN0TX                 | SIUL<br>FlexCAN_0<br>eMIOS_0<br>LINFlexD_0                | I/O<br>O<br>I/O<br>I             | M/S      | Tristate         | 39       | 39       | L3         |

| PB[1]       | PCR[17] | AF0<br>AF1<br>AF2<br>—<br>—        | GPIO[17]<br>—<br>E0UC[31]<br>LIN0RX<br>WKPU[4]<br>CAN0RX | SIUL<br>—<br>eMIOS_0<br>LINFlexD_0<br>WKPU<br>FlexCAN_0   | /O<br><br> /O<br> <br> <br> <br> | S        | Tristate         | 40       | 40       | M2         |

| PB[2]       | PCR[18] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[18]<br>LIN0TX<br>SDA<br>E0UC[30]                    | SIUL<br>LINFlexD_0<br>I <sup>2</sup> C<br>eMIOS_0         | I/O<br>O<br>I/O<br>I/O           | M/S      | Tristate         | 176      | 208      | A2         |

| PB[3]       | PCR[19] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[19]<br>E0UC[31]<br>SCL<br><br>WKPU[11]<br>LIN0RX    | SIUL<br>eMIOS_0<br>I <sup>2</sup> C<br>WKPU<br>LINFlexD_0 | /O<br> /O<br> /O<br> <br> <br>   | S        | Tristate         | 1        | 1        | D4         |

| PB[4]       | PCR[20] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPI[20]<br>—<br>—<br>—<br>ADC0_P[0]<br>ADC1_P[0]         | SIUL<br>—<br>—<br>ADC_0<br>ADC_1                          | -                                | I        | Tristate         | 88       | 104      | T16        |

| Table 4. Functional | port pir | description   | s (continued) |

|---------------------|----------|---------------|---------------|

|                     | portpii  | i accomption. |               |

### Package pinouts and signal descriptions

|             |          |                                      |                                                                   |                                                              |                                      |          |                  | Piı      | n numbe  | ər         |

|-------------|----------|--------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup>   | Function                                                          | Peripheral                                                   | I/O<br>direction <sup>2</sup>        | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PF[13]      | PCR[93]  | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[93]<br>E1UC[26]<br>—<br>LIN5RX<br>WKPU[16]                   | SIUL<br>eMIOS_1<br><br>LINFlexD_5<br>WKPU                    | /O<br> /O<br><br> <br>               | S        | Tristate         | 49       | 57       | P3         |

| PF[14]      | PCR[94]  | AF0<br>AF1<br>AF2<br>AF3<br>ALT4     | GPIO[94]<br>CAN4TX<br>E1UC[27]<br>CAN1TX<br>MDIO                  | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_1<br>FEC             | I/O<br>O<br>I/O<br>O<br>I/O          | M/S      | Tristate         | 126      | 150      | D14        |

| PF[15]      | PCR[95]  | AF0<br>AF1<br>AF2<br>AF3<br><br><br> | GPIO[95]<br>E1UC[4]<br>—<br>RX_DV<br>CAN1RX<br>CAN4RX<br>EIRQ[13] | SIUL<br>eMIOS_1<br><br>FEC<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | /0<br> /0<br>                        | M/S      | Tristate         | 125      | 149      | D15        |

| PG[0]       | PCR[96]  | AF0<br>AF1<br>AF2<br>AF3<br>ALT4     | GPIO[96]<br>CAN5TX<br>E1UC[23]<br>—<br>MDC                        | SIUL<br>FlexCAN_5<br>eMIOS_1<br><br>FEC                      | I/O<br>O<br>I/O<br>—<br>O            | F        | Tristate         | 122      | 146      | E13        |

| PG[1]       | PCR[97]  | AF0<br>AF1<br>AF2<br>AF3<br><br>     | GPIO[97]<br>—<br>E1UC[24]<br>—<br>TX_CLK<br>CAN5RX<br>EIRQ[14]    | SIUL<br>—<br>eMIOS_1<br>—<br>FEC<br>FlexCAN_5<br>SIUL        | /O<br><br> /O<br><br> <br> <br> <br> | Μ        | Tristate         | 121      | 145      | E14        |

| PG[2]       | PCR[98]  | AF0<br>AF1<br>AF2<br>AF3             | GPIO[98]<br>E1UC[11]<br>SOUT_3<br>—                               | SIUL<br>eMIOS_1<br>DSPI_3<br>—                               | I/O<br>I/O<br>O                      | M/S      | Tristate         | 16       | 16       | E4         |

| PG[3]       | PCR[99]  | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[99]<br>E1UC[12]<br>CS0_3<br>—<br>WKPU[17]                    | SIUL<br>eMIOS_1<br>DSPI_3<br>—<br>WKPU                       | I/O<br>I/O<br>I/O<br>I               | S        | Tristate         | 15       | 15       | E1         |

| PG[4]       | PCR[100] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[100]<br>E1UC[13]<br>SCK_3<br>—                               | SIUL<br>eMIOS_1<br>DSPI_3<br>—                               | I/O<br>I/O<br>I/O<br>—               | M/S      | Tristate         | 14       | 14       | F2         |

### Package pinouts and signal descriptions

|             |          |                                    |                                                  |                                               |                                 |          |                  | Pir      | n numbe  | ər         |

|-------------|----------|------------------------------------|--------------------------------------------------|-----------------------------------------------|---------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                                         | Peripheral                                    | I/O<br>direction <sup>2</sup>   | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PH[14]      | PCR[126] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[126]<br>SCK_4<br>CS1_3<br>E1UC[27]          | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1           | I/O<br>I/O<br>O<br>I/O          | M/S      | Tristate         | 10       | 10       | C1         |

| PH[15]      | PCR[127] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[127]<br>SOUT_5<br>—<br>E1UC[17]             | SIUL<br>DSPI_5<br>—<br>eMIOS_1                | I/O<br>O<br><br>I/O             | M/S      | Tristate         | 8        | 8        | E3         |

| PI[0]       | PCR[128] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[128]<br>E0UC[28]<br>LIN8TX<br>—             | SIUL<br>eMIOS_0<br>LINFlexD_8<br>—            | I/O<br>I/O<br>O                 | S        | Tristate         | 172      | 196      | C5         |

| PI[1]       | PCR[129] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[129]<br>E0UC[29]<br>—<br>WKPU[24]<br>LIN8RX | SIUL<br>eMIOS_0<br>—<br>WKPU<br>LINFlexD_8    | /O<br> /O<br><br> <br> <br>     | S        | Tristate         | 171      | 195      | A4         |

| PI[2]       | PCR[130] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[130]<br>E0UC[30]<br>LIN9TX<br>—             | SIUL<br>eMIOS_0<br>LINFlexD_9<br>—            | I/O<br>I/O<br>O                 | S        | Tristate         | 170      | 194      | D6         |

| PI[3]       | PCR[131] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[131]<br>E0UC[31]<br>—<br>WKPU[23]<br>LIN9RX | SIUL<br>eMIOS_0<br><br>WKPU<br>LINFlexD_9     | /O<br> /O<br><br> <br> <br>     | S        | Tristate         | 169      | 193      | B5         |

| PI[4]       | PCR[132] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[132]<br>E1UC[28]<br>SOUT_4<br>—             | SIUL<br>eMIOS_1<br>DSPI_4<br>—                | I/O<br>I/O<br>O                 | M/S      | Tristate         | 143      | 167      | A12        |

| PI[5]       | PCR[133] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[133]<br>E1UC[29]<br>SCK_4<br>CS2_5<br>CS2_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>I/O<br>O          | M/S      | Tristate         | 142      | 166      | D12        |

| PI[6]       | PCR[134] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[134]<br>E1UC[30]<br>CS0_4<br>CS0_5<br>CS0_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>I/O<br>I/O<br>I/O | S        | Tristate         | 11       | 11       | D2         |

| Table 4. Functional port pin descriptions (continue |

|-----------------------------------------------------|

|-----------------------------------------------------|

|             |          |                                    |                                                  |                                               |                               |          |                  | Pir      | n numbe  | er         |

|-------------|----------|------------------------------------|--------------------------------------------------|-----------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                                         | Peripheral                                    | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PI[7]       | PCR[135] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[135]<br>E1UC[31]<br>CS1_4<br>CS1_5<br>CS1_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>O<br>O          | S        | Tristate         | 12       | 12       | E2         |

| PI[8]       | PCR[136] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[136]<br>—<br>—<br>—<br>ADC0_S[16]           | SIUL<br> -<br> <br>ADC_0                      | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         | 108      | 130      | J14        |

| PI[9]       | PCR[137] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[137]<br>—<br>—<br>—<br>ADC0_S[17]           | SIUL<br>—<br>—<br>ADC_0                       | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         | _        | 131      | J15        |

| PI[10]      | PCR[138] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[138]<br>—<br>—<br>—<br>ADC0_S[18]           | SIUL<br>—<br>—<br>ADC_0                       | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 134      | J16        |

| PI[11]      | PCR[139] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[139]<br>—<br>—<br>—<br>ADC0_S[19]<br>SIN_3  | SIUL<br>—<br>—<br>ADC_0<br>DSPI_3             | /O<br><br><br> <br> <br>      | S        | Tristate         | 111      | 135      | H16        |

| PI[12]      | PCR[140] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[140]<br>CS0_3<br>CS0_2<br>—<br>ADC0_S[20]   | SIUL<br>DSPI_3<br>DSPI_2<br>—<br>ADC_0        | I/O<br>I/O<br>I/O<br>I        | S        | Tristate         | 112      | 136      | G15        |

| PI[13]      | PCR[141] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[141]<br>CS1_3<br>CS1_2<br>—<br>ADC0_S[21]   | SIUL<br>DSPI_3<br>DSPI_2<br>—<br>ADC_0        | I/O<br>O<br>—<br>I            | S        | Tristate         | 113      | 137      | G14        |

| PI[14]      | PCR[142] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[142]<br>—<br>—<br>—<br>ADC0_S[22]<br>SIN_4  | SIUL<br>—<br>—<br>ADC_0<br>DSPI_4             | /O<br>                        | S        | Tristate         | 76       | 92       | T12        |

| Table 4. Functional | port pin        | descriptions   | (continued) |

|---------------------|-----------------|----------------|-------------|

|                     | P • • • P · · · | acceriptione , |             |

| O much a l                                  |                                                       | <b>D</b>                                                                                                      |                                                  | Value                      |                                    |       |  |  |

|---------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|------------------------------------|-------|--|--|

| Symbol                                      |                                                       | Parameter                                                                                                     | Conditions                                       | Min                        | Max                                | Unit  |  |  |

| V <sub>SS_LV</sub> <sup>3</sup>             | SR                                                    | Voltage on VSS_LV (Low voltage digital supply) pins with respect to ground (V <sub>SS_HV</sub> )              |                                                  | V <sub>SS_HV</sub> -0.1    | V <sub>SS_HV</sub> + 0.1           | V     |  |  |

| V <sub>RC_CTRL</sub> <sup>4</sup>           | Base control voltage for external<br>BCP68 NPN device |                                                                                                               | Relative to<br>V <sub>DD_LV</sub>                | 0                          | V <sub>DD_LV</sub> + 1             | V     |  |  |

| V <sub>SS_ADC</sub>                         | SR                                                    | Voltage on VSS_HV_ADC0,<br>VSS_HV_ADC1 (ADC reference)<br>pin with respect to ground<br>(V <sub>SS_HV</sub> ) | _                                                | V <sub>SS_HV</sub> – 0.1   | V <sub>SS_HV</sub> + 0.1           | V     |  |  |

| $V_{\text{DD}\_\text{HV}\_\text{ADC0}}{}^5$ | SR                                                    | Voltage on VDD_HV_ADC0 with                                                                                   | —                                                | 4.5                        | 5.5                                | V     |  |  |

|                                             |                                                       | respect to ground (V <sub>SS_HV</sub> )                                                                       | Voltage drop <sup>(2)</sup>                      | 3.0                        | 5.5                                |       |  |  |

|                                             |                                                       |                                                                                                               | Relative to<br>V <sub>DD_HV_A</sub> <sup>6</sup> | V <sub>DD_HV_A</sub> - 0.1 | V <sub>DD_HV_A</sub> + 0.1         |       |  |  |

| V <sub>DD_HV_ADC1</sub> <sup>7</sup>        | SR                                                    | Voltage on VDD_HV_ADC1 with                                                                                   | —                                                | 4.5                        | 5.5                                | V     |  |  |

|                                             |                                                       | respect to ground (V <sub>SS_HV</sub> )                                                                       | Voltage drop <sup>(2)</sup>                      | 3.0                        | 5.5                                |       |  |  |

|                                             |                                                       |                                                                                                               | Relative to<br>V <sub>DD_HV_A</sub> <sup>6</sup> | $V_{DD_HV_A} - 0.1$        | $V_{DD_HV_A} + 0.1$                |       |  |  |

| V <sub>IN</sub>                             | SR                                                    | Voltage on any GPIO pin with                                                                                  | —                                                | V <sub>SS_HV</sub> –0.1    |                                    | V     |  |  |

|                                             |                                                       | respect to ground (V <sub>SS_HV</sub> )                                                                       | Relative to<br>V <sub>DD_HV_A/HV_B</sub>         | _                          | V <sub>DD_HV_A/HV_B</sub><br>+ 0.1 |       |  |  |

| I <sub>INJPAD</sub>                         | SR                                                    | Injected input current on any pin during overload condition                                                   | —                                                | -5                         | 5                                  | mA    |  |  |

| I <sub>INJSUM</sub>                         | SR                                                    | Absolute sum of all injected input currents during overload condition                                         | _                                                | -50                        | 50                                 |       |  |  |

| $TV_{DD}$                                   | SR                                                    | V <sub>DD_HV_A</sub> slope to ensure correct                                                                  | —                                                | _                          | 0.5                                | V/µs  |  |  |

|                                             |                                                       | power up <sup>8</sup>                                                                                         | —                                                | 0.5                        | _                                  | V/min |  |  |

| TA C-Grade Part                             | SR                                                    | Ambient temperature under bias                                                                                | —                                                | -40                        | 85                                 |       |  |  |

| T <sub>J C-Grade Part</sub>                 | SR                                                    | Junction temperature under bias                                                                               | —                                                | -40                        | 110                                |       |  |  |

| T <sub>A V-Grade Part</sub>                 | SR                                                    | Ambient temperature under bias                                                                                | —                                                | -40                        | 105                                | °C    |  |  |

| T <sub>J V-Grade Part</sub>                 | SR                                                    | Junction temperature under bias                                                                               | —                                                | -40                        | 130                                |       |  |  |

| TA M-Grade Part                             | SR                                                    | Ambient temperature under bias                                                                                | —                                                | -40                        | 125                                |       |  |  |

| T <sub>J M-Grade Part</sub>                 | SR                                                    | Junction temperature under bias                                                                               | —                                                | -40                        | 150                                |       |  |  |

NOTES:

<sup>1</sup> 100 nF EMI capacitance need to be provided between each VDD/VSS\_HV pair.

<sup>2</sup> Full device operation is guaranteed by design from 3.0 V–5.5 V. OSC functionality is guaranteed from the entire range 3.0V–5.5 V, the parametrics measured are at 3.0V and 5.5V (extreme voltage ranges to cover the range of operation). The parametrics might have some variation in the intermediate voltage range, but there is no impact to functionality.

<sup>3</sup> 100 nF EMI capacitance needs to be provided between each VDD\_LV/VSS\_LV supply pair. 10 µF bulk capacitance needs to be provided as CREG on each VDD\_LV pin.

- <sup>4</sup> This voltage is internally generated by the device and no external voltage should be supplied.

- <sup>5</sup> 100 nF capacitance needs to be provided between  $V_{DD_HV_(ADC0/ADC1)}/V_{SS_HV_(ADC0/ADC1)}$  pair.

- <sup>6</sup> Both the relative and the fixed conditions must be met. For instance: If  $V_{DD_{HV_A}}$  is 5.9 V,  $V_{DD_{HV_A}DC0}$  maximum value is 6.0 V then, despite the relative condition, the max value is  $V_{DD_{HV_A}} + 0.3 = 6.2$  V.

- <sup>7</sup> PA3, PA7, PA10, PA11 and PE12 ADC\_1 channels are coming from V<sub>DD-HV\_B</sub> domain hence VDD\_HV\_ADC1 should be within ±100 mV of V<sub>DD HV B</sub> when these channels are used for ADC\_1.

- <sup>8</sup> Guaranteed by device validation.

## NOTE

### SRAM retention guaranteed to LVD levels.

## 4.5 Thermal characteristics

## 4.5.1 Package thermal characteristics

| Symbol C F     |    | Parameter Conditions <sup>2</sup> F |                                                     | Pin count -              |     | Unit |     |                 |      |

|----------------|----|-------------------------------------|-----------------------------------------------------|--------------------------|-----|------|-----|-----------------|------|

|                |    | i di di neter                       | Conditions                                          |                          | Min | Тур  | Max | onne            |      |

| $R_{\thetaJA}$ | CC | D                                   | Thermal resistance,                                 | Single-layer<br>board—1s | 176 |      | _   | 38 <sup>5</sup> | °C/W |

|                |    |                                     | junction-to-ambient natural convection <sup>4</sup> |                          | 208 |      | —   | 41 <sup>6</sup> | °C/W |

| $R_{\thetaJA}$ | CC | D                                   | Thermal resistance,                                 | Four-layer               | 176 | _    | _   | 31              | °C/W |

|                |    |                                     | junction-to-ambient natural convection <sup>7</sup> | board—2s2p <sup>7</sup>  | 208 | —    | _   | 34              | °C/W |

### Table 11. LQFP thermal characteristics<sup>1</sup>

NOTES:

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C.

<sup>3</sup> All values need to be confirmed during device validation.

<sup>4</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>5</sup> Junction-to-Ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6.

<sup>6</sup> Junction-to-Ambient thermal resistance determined per JEDEC JESD51-2 and JESD51-6

<sup>7</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8.

| Table 12. 256 MAPBGA thermal characteri | stics <sup>1</sup> |

|-----------------------------------------|--------------------|

|-----------------------------------------|--------------------|

| S              | ymb | ool | С | Parameter          | Conditions            | Value           | Unit |

|----------------|-----|-----|---|--------------------|-----------------------|-----------------|------|

| R <sub>θ</sub> | JA  | СС  |   |                    | Single-layer board—1s | 43 <sup>2</sup> | °C/W |

|                |     |     |   | natural convection | Four-layer board—2s2p | 26 <sup>3</sup> |      |

NOTES:

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

<sup>2</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

<sup>3</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-6 with the board horizontal.

| Sum             | nbol | с | Parameter                                  |           | onditions <sup>1,2</sup>                                                                     |                       | Value |                    | Unit |

|-----------------|------|---|--------------------------------------------|-----------|----------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|------|

| J               |      | C | Farameter                                  |           | onutions                                                                                     | Min                   | Тур   | Мах                | Onit |

| V <sub>OH</sub> | CC   | Р | Output high level<br>FAST<br>configuration | Push Pull | $I_{OH} = -14 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0              | 0.8V <sub>DD</sub>    |       | _                  | V    |

|                 |      | С |                                            |           | $I_{OH} = -7 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 <sup>3</sup>  | 0.8V <sub>DD</sub>    | _     | _                  |      |

|                 |      | С |                                            |           | $I_{OH} = -11 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1              | V <sub>DD</sub> – 0.8 |       | —                  |      |

| V <sub>OL</sub> | CC   | Р | Output low level<br>FAST<br>configuration  | Push Pull | I <sub>OL</sub> = 14 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0                    | —                     | _     | 0.1V <sub>DD</sub> | V    |

|                 |      | С |                                            |           | $I_{OL} = 7 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 <sup>(3)</sup> | —                     | _     | 0.1V <sub>DD</sub> |      |

|                 |      | С |                                            |           | I <sub>OL</sub> = 11 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                    | —                     | _     | 0.5                |      |

Table 17. FAST configuration output buffer electrical characteristics

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

$^2~V_{DD}$  as mentioned in the table is  $V_{DD\_HV\_A}/V_{DD\_HV\_B}.$

<sup>3</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus outputs (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

#### **Output pin transition times** 4.6.4

Table 18. Output pin transition times

| 6, | vm  | bol  | с | Parameter                                     | Cor                     | nditions <sup>1,2</sup>     |     | Value <sup>3</sup> |     | Unit |

|----|-----|------|---|-----------------------------------------------|-------------------------|-----------------------------|-----|--------------------|-----|------|

| 3  | yın | IDUI | C | Farameter                                     | CO                      |                             | Min | Тур                | Max |      |

| Tt | tr  | CC   | D | Output transition time                        | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 V \pm 10\%$ , |     | —                  | 50  | ns   |

|    |     |      | Т | output pin <sup>4</sup><br>SLOW configuration | C <sub>L</sub> = 50 pF  | PAD3V5V = 0                 |     | _                  | 100 |      |

|    |     |      | D | -                                             | C <sub>L</sub> = 100 pF |                             |     | —                  | 125 |      |

|    |     |      | D |                                               | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 V \pm 10\%$ , |     | —                  | 40  |      |

|    |     |      | Т |                                               | C <sub>L</sub> = 50 pF  | PAD3V5V = 1                 |     | _                  | 50  |      |

|    |     |      | D |                                               | C <sub>L</sub> = 100 pF |                             |     | —                  | 75  |      |

| Package  |                       |                       |                 | I/O Su                | pplies                  |                         |   |   |

|----------|-----------------------|-----------------------|-----------------|-----------------------|-------------------------|-------------------------|---|---|

| 176 LQFP | pin6                  | pin27                 | pin57           | pin85                 | pin123                  | pin150                  | _ | _ |

|          |                       | $(V_{DD_HV_A})$       |                 | $(V_{DD_HV_A})$       |                         | (V <sub>SS_HV</sub> )   |   |   |

|          | pin7                  | pin28                 | pin59           | pin86                 | pin124                  | pin151                  |   |   |

|          | (V <sub>SS_HV</sub> ) | (V <sub>SS_HV</sub> ) | $(V_{DD_HV_A})$ | (V <sub>SS_HV</sub> ) | (V <sub>DD_HV_B</sub> ) | (V <sub>DD_HV_A</sub> ) |   |   |

## Table 19. I/O supplies (continued)

## Table 20. I/O consumption

| Symbol                             |    | с | Parameter                                  | Conditi                         | ions <sup>1,2</sup>                           |     | Value <sup>3</sup> |       | Unit |

|------------------------------------|----|---|--------------------------------------------|---------------------------------|-----------------------------------------------|-----|--------------------|-------|------|

| Symbol                             |    | C | Farameter                                  | Conditi                         |                                               | Min | Тур                | Max   | Onit |

| I <sub>SWTSLW</sub> ,4             | СС | D | Peak I/O current for<br>SLOW configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | _                  | 19.9  |      |

|                                    |    |   |                                            |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _                  | 15.5  | mA   |

| I <sub>SWTMED</sub> <sup>(4)</sup> | СС | D | Peak I/O current for<br>MEDIUM             | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | —                  | 28.8  |      |

|                                    |    |   | configuration                              |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _                  | 16.3  | mA   |

| I <sub>SWTFST</sub> <sup>(4)</sup> | СС | D | Peak I/O current for<br>FAST configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   | —                  | 113.5 |      |

|                                    |    |   |                                            |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | —                  | 52.1  | mA   |

| I <sub>RMSSLW</sub>                | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 5.0 V \pm 10\%$ ,                   |     | —                  | 2.22  |      |

|                                    |    |   | I/O current for SLOW configuration         | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 0                                   |     | _                  | 3.13  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 2 MHz  |                                               |     | —                  | 6.54  | mA   |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 3.3 V \pm 10\%$ ,                   | —   | —                  | 1.51  | mA   |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 1                                   | _   | —                  | 2.14  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 2 MHz  |                                               | _   | —                  | 4.33  |      |

| IRMSMED                            | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   | _   | —                  | 6.5   | mA   |

|                                    |    |   | I/O current for<br>MEDIUM                  | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 0                                   | _   | _                  | 13.32 |      |

|                                    |    |   | configuration                              | C <sub>L</sub> = 100 pF, 13 MHz |                                               | _   | _                  | 18.26 |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     |                    | 4.91  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 1                                   | _   | _                  | 8.47  |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 13 MHz |                                               | _   | _                  | 10.94 |      |

| I <sub>RMSFST</sub>                | СС | D | Root mean square                           | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   | _   | —                  | 21.05 | mA   |

|                                    |    |   | I/O current for FAST configuration         | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 0                                   | _   | _                  | 33    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 40 MHz |                                               | _   | _                  | 55.77 |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 3.3 V \pm 10\%,$                    | _   | —                  | 14    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 1                                   |     |                    | 20    |      |

|                                    |    |   |                                            | C <sub>L</sub> = 100 pF, 40 MHz |                                               | _   |                    | 34.89 |      |

- LV\_CFLA0/CFLA1: Low voltage supply for the two code Flash modules. It is shorted with LV\_COR through double bonding.

- LV\_DFLA: Low voltage supply for data Flash module. It is shorted with LV\_COR through double bonding.

- LV\_PLL: Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

1) All VSS\_LV pins must be grounded, as shown for VSS\_HV pin.

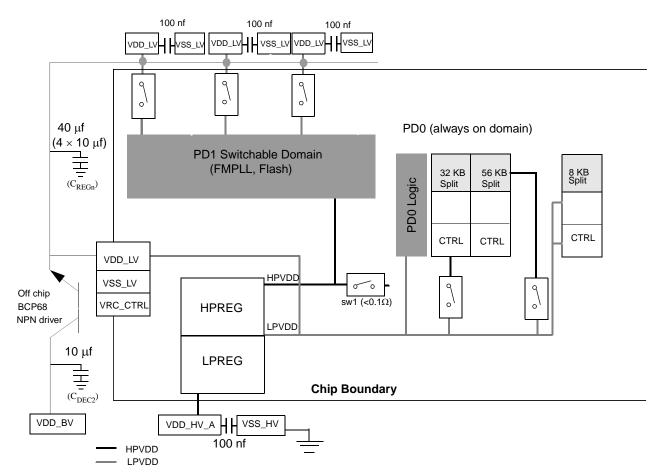

## Figure 8. Voltage regulator capacitance connection

The internal voltage regulator requires external bulk capacitance ( $C_{REGn}$ ) to be connected to the device to provide a stable low voltage digital supply to the device. Also required for stability is the  $C_{DEC2}$  capacitor at ballast collector. This is needed to minimize sharp injection current when ballast is turning ON. Apart from the bulk capacitance, user should connect EMI/decoupling cap ( $C_{REGP}$ ) at each  $V_{DD_LV}/V_{SS_LV}$  pin pair.

## 4.8.1.1 Recommendations

- The external NPN driver must be BCP68 type.

- V<sub>DD LV</sub> should be implemented as a power plane from the emitter of the ballast transistor.

- <sup>3</sup> Data based on characterization results, not tested in production.

- <sup>4</sup> f<sub>CPU</sub> 120 MHz + 2% can be achieved over full temperature 125 °C ambient, 150 °C junction temperature.

## 4.10.3 Flash memory start-up/switch-off timings

### Table 30. Start-up time/Switch-off time

| Symbol                  |    | с | Parameter                                                |                      | Conditions <sup>1</sup> |     | Value |     | Unit |

|-------------------------|----|---|----------------------------------------------------------|----------------------|-------------------------|-----|-------|-----|------|

| - Cymbol                |    | Ŭ | r drumotor                                               |                      | Conditions              | Min | Тур   | Max | Onic |

| T <sub>FLARSTEXIT</sub> | СС | D | Delay for flash memory module to exit reset mode         | Code flash<br>memory | _                       |     |       | 125 |      |

|                         |    |   |                                                          | Data flash<br>memory |                         |     | _     |     |      |

| T <sub>FLALPEXIT</sub>  | СС | Т | Delay for flash memory module to exit low-power mode     | Code flash<br>memory | _                       |     | _     | 0.5 | μs   |

| T <sub>FLAPDEXIT</sub>  | СС | Т | Delay for flash memory module to exit<br>power-down mode | Code flash<br>memory | —                       | _   | _     | 30  |      |

|                         |    |   |                                                          | Data flash<br>memory |                         |     | _     |     |      |

| T <sub>FLALPENTRY</sub> | СС | Т | Delay for flash memory module to enter low-power mode    | Code flash<br>memory | —                       |     | _     | 0.5 |      |

NOTES:

$V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

# 4.11 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## 4.11.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and pre-qualification tests in relation with the EMC level requested for the application.

- Software recommendations The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers)

- Pre-qualification trials Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring.

# 4.11.2 Electromagnetic interference (EMI)

The product is monitored in terms of emission based on a typical application. This emission test conforms to the IEC61967-1 standard, which specifies the general conditions for EMI measurements.

Table 31. EMI radiated emission measurement<sup>1,2</sup>

| Symb               |    | С | Parameter             | Conditions                                                                              |                               |       | Value |                 | Unit |

|--------------------|----|---|-----------------------|-----------------------------------------------------------------------------------------|-------------------------------|-------|-------|-----------------|------|

| C y III.           |    | Ŭ | i ulullotoi           | Contanione                                                                              |                               | Min   | Тур   | Max             | onic |

| —                  | SR |   | Scan range            | —                                                                                       |                               | 0.150 |       | 1000            | MHz  |

| f <sub>CPU</sub>   | SR |   | Operating frequency   | _                                                                                       |                               | —     | 120   | _               | MHz  |

| V <sub>DD_LV</sub> | SR |   | LV operating voltages | _                                                                                       |                               | —     | 1.28  | _               | V    |

| S <sub>EMI</sub>   | СС | Т |                       | $V_{DD} = 5 V$ , $T_A = 25 °C$ ,<br>LQFP176 package                                     | No PLL frequency modulation   | —     | _     | 18              | dBµV |

|                    |    |   |                       | Test conforming to IEC 61967-2,<br>f <sub>OSC</sub> = 40 MHz/f <sub>CPU</sub> = 120 MHz | ± 2% PLL frequency modulation | —     |       | 14 <sup>3</sup> | dBµV |

NOTES:

EMI testing and I/O port waveforms per IEC 61967-1, -2, -4.

<sup>2</sup> For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

<sup>3</sup> All values need to be confirmed during device validation.

# 4.11.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

## 4.11.3.1 Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

| Symbol                | Ratings                                                   | Conditions                                           | Class | Max value <sup>3</sup> | Unit |

|-----------------------|-----------------------------------------------------------|------------------------------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human Body Model)     | $T_A = 25 \text{ °C}$<br>conforming to AEC-Q100-002  | H1C   | 2000                   | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage<br>(Machine Model)        | $T_A = 25 \text{ °C}$<br>conforming to AEC-Q100-003  | M2    | 200                    |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage<br>(Charged Device Model) | $T_A = 25 \ ^{\circ}C$<br>conforming to AEC-Q100-011 | C3A   | 500<br>750 (corners)   |      |

Table 32. ESD absolute maximum ratings<sup>1,2</sup>

| Symbol          |    | с | Parameter                                     | Conditions <sup>1</sup>   |                          | Value <sup>2</sup> |                            | Unit |

|-----------------|----|---|-----------------------------------------------|---------------------------|--------------------------|--------------------|----------------------------|------|

| Gymbol          |    | Ŭ | i arameter                                    | Conditions                | Min                      | Тур                | Мах                        |      |

| V <sub>IH</sub> | SR | Ρ | Input high level<br>CMOS<br>(Schmitt Trigger) | Oscillator bypass<br>mode | 0.65V <sub>DD_HV_A</sub> | —                  | V <sub>DD_HV_A</sub> + 0.4 | V    |

| V <sub>IL</sub> | SR | Ρ | Input low level<br>CMOS<br>(Schmitt Trigger)  | Oscillator bypass<br>mode | -0.3                     | _                  | 0.35V <sub>DD_HV_</sub> A  | V    |

Table 35. Fast external crystal oscillator (4 to 40 MHz) electrical characteristics

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> Based on ATE Cz

<sup>4</sup> Stated values take into account only analog module consumption but not the digital contributor (clock tree and enabled peripherals).

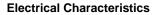

#### 4.13 Slow external crystal oscillator (32 kHz) electrical characteristics

The device provides a low power oscillator/resonator driver.

Figure 12. Crystal oscillator and resonator connection scheme

## NOTE

OSC32K\_XTAL/OSC32K\_EXTAL must not be directly used to drive external circuits.

| Symbol               |    | с | Parameter                                                                                                | Conditions <sup>1</sup>                                |     | Value <sup>2</sup> |     | Unit |

|----------------------|----|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|--------------------|-----|------|

| Cymbol               |    | Ŭ | rurumeter                                                                                                | Conditions                                             | Min | Тур                | Max | onn  |

| T <sub>SIRCSU</sub>  | СС | Ρ | Slow internal RC oscillator start-up time                                                                | $T_A = 25 \text{ °C}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | _   | 8                  | 12  | μs   |

| $\Delta_{SIRCPRE}$   | СС | С | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub>                       | T <sub>A</sub> = 25 °C                                 | -2  |                    | +2  | %    |

|                      | СС | С | Slow internal RC oscillator trimming step                                                                | _                                                      | _   | 2.7                | —   |      |

| <sup>∆</sup> sircvar | СС | С | Variation in f <sub>SIRC</sub> across<br>temperature and fluctuation in<br>supply voltage, post trimming | _                                                      | -10 |                    | +10 | %    |

### Table 40. Slow internal RC oscillator (128 kHz) electrical characteristics (continued)

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

#### 4.17 **ADC** electrical characteristics

#### 4.17.1 Introduction

The device provides two Successive Approximation Register (SAR) analog-to-digital converters (10-bit and 12-bit).

## NOTE

Due to ADC limitations, the two ADCs cannot sample a shared channel at the same time i.e., their sampling windows cannot overlap if a shared channel is selected. If this is done, neither of the ADCs can guarantee their conversion accuracies.

This relation can again be simplified considering  $C_S$  as an additional worst condition. In reality, transient is faster, but the A/D converter circuitry has been designed to be robust also in very worst case: the sampling time  $T_s$  is always much longer than the internal time constant.

Eqn. 6

$$\tau_1 < (R_{SW} + R_{AD}) \bullet C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to the following equation

$$Eqn. 7$$

$$V_{A1} \bullet (C_{S} + C_{P1} + C_{P2}) = V_{A} \bullet (C_{P1} + C_{P2})$$

• A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance RL: again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_L$  sizing is obtained:

Eqn. 9

8.5 •

$$\tau_2 = 8.5 • R_I • (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . The following equation must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

#### Eqn. 10

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing

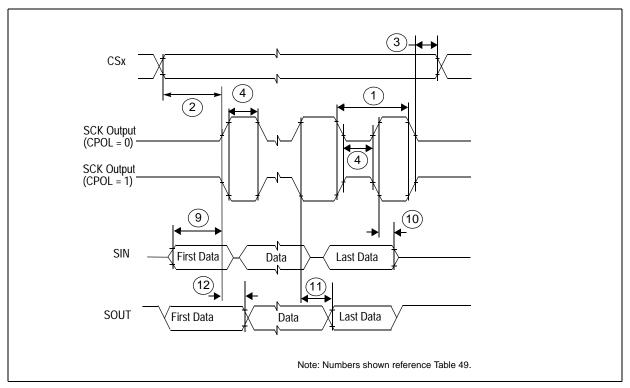

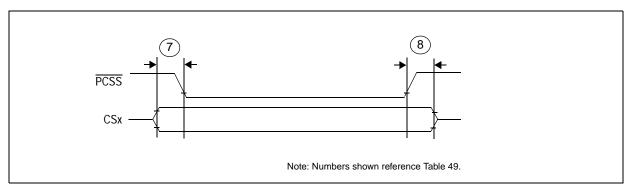

Figure 29. DSPI modified transfer format timing-master, CPHA = 0

Figure 33. DSPI PCS strobe (PCSS) timing

## 4.19.3 Nexus characteristics

| Spec | Characteristic                                            | Symbol                                  | Min  | Max  | Unit              |

|------|-----------------------------------------------------------|-----------------------------------------|------|------|-------------------|

| 1    | MCKO Cycle<br>Time <sup>2</sup>                           | t <sub>MCYC</sub>                       | 16.3 | -    | ns                |

| 2    | MCKO Duty Cycle                                           | t <sub>MDC</sub>                        | 40   | 60   | %                 |

| 3    | MCKO Low to<br>MDO, MSEO,<br>EVTO Data Valid <sup>3</sup> | t <sub>MDOV</sub>                       | -0.1 | 0.25 | t <sub>MCYC</sub> |

| 4    | EVTI Pulse Width                                          | t <sub>EVTIPW</sub>                     | 4.0  | —    | t <sub>TCYC</sub> |

| 5    | EVTO Pulse<br>Width                                       | t <sub>EVTOPW</sub>                     | 1    |      | t <sub>MCYC</sub> |

| 6    | TCK Cycle Time <sup>4</sup>                               | t <sub>TCYC</sub>                       | 40   | —    | ns                |

| 7    | TCK Duty Cycle                                            | t <sub>TDC</sub>                        | 40   | 60   | %                 |

| 8    | TDI, TMS Data<br>Setup Time                               | t <sub>NTDIS</sub> , t <sub>NTMSS</sub> | 8    | -    | ns                |

| 9    | TDI, TMS Data<br>Hold Time                                | t <sub>NTDIH</sub> , t <sub>NTMSH</sub> | 5    | _    | ns                |

| 10   | TCK Low to TDO<br>Data Valid                              | t <sub>JOV</sub>                        | 0    | 25   | ns                |

NOTES:

JTAG specifications in this table apply when used for debug functionality. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DDE} = 4.0 - 5.5$  V,  $T_A = T_L$  to  $T_H$ , and  $C_L = 30$  pF with SRC = 0b11.

<sup>2</sup> MCKO can run up to 1/2 of full system frequency. It can also run at system frequency when it is <60 MHz.

$^{3}$  MDO,  $\overline{\text{MSEO}}$ , and  $\overline{\text{EVTO}}$  data is held valid until next MCKO low cycle.

<sup>4</sup> The system clock frequency needs to be three times faster than the TCK frequency.

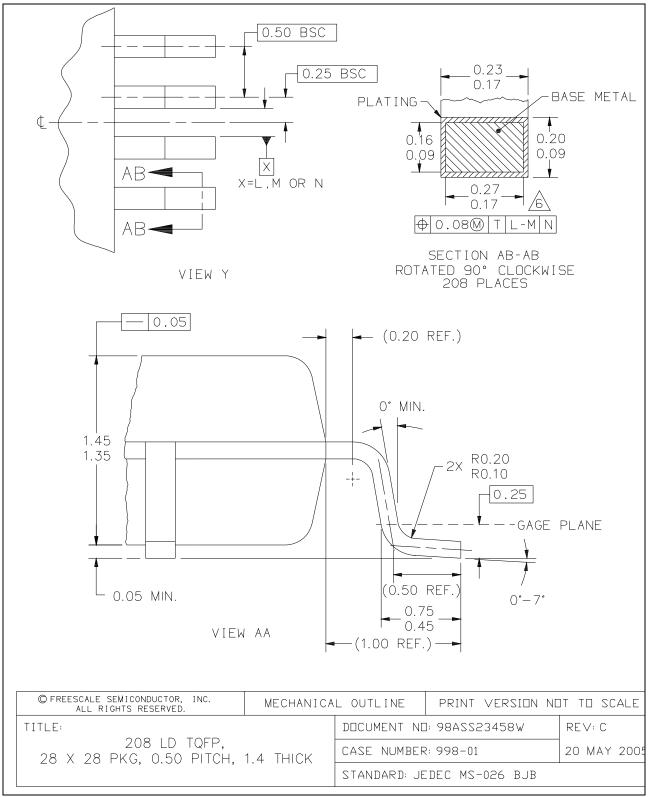

### Package characteristics

Figure 41. 208 LQFP mechanical drawing (Part 2 of 3)

Package characteristics

# 5.1.3 256 MAPBGA package mechanical drawing

Figure 43. 256 MAPBGA mechanical drawing (Part 1 of 2)

Package characteristics

Figure 44. 256 MAPBGA mechanical drawing (Part 2 of 2)

| Table 52. | Revision | history | (continued) |

|-----------|----------|---------|-------------|

|-----------|----------|---------|-------------|

| <ul> <li>5 21 June 2012</li> <li>Updated the pins 23 and 24 of Figure 2.176-pin LQFP configurat</li> <li>Updated unit of measure in Table 43 Conversion characteristics (</li> <li>Modified the value to typical value in Table 48 On-chip peripheral consumption</li> <li>Added footnote to t<sub>ESRT</sub> parameter in Table 25 Code flash memor erase specifications</li> <li>Added footnote to t<sub>ESRT</sub> parameter in Table 26 Data flash memor erase specifications</li> <li>Updated Table 28 Flash memory read access timing.</li> <li>Updated Notes 2 and Notes 3 of Table 9 Recommended operatin (3.3 V) and Table 10 Recommended operating conditions (5.0 V)</li> <li>Updated the footnote1 of Table 9 Recommended operating conditions (5.0 V)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (12-bit ADC_1)<br>Is current<br>ry—Program and<br>ry—Program and<br>ng conditions<br>) respectively.                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Updated V<sub>DD_HV_A</sub> to V<sub>DD_BV</sub> for C<sub>DEC2</sub> and I<sub>DD_HV_A</sub> in Table 22, regulator electrical characteristics and deleted footnote3</li> <li>Updated the dedicated number of channels for 12-bit ADC in fair tables</li> <li>Updated the values of f<sub>SIRC</sub>, parameters and conditions of Δ<sub>SIRC</sub>. Slow internal RC oscillator (128 kHz) electrical characteristics</li> <li>Updated the value of f<sub>ADC0_PU</sub> in Table 42, ADC conversion chara ADC_0)</li> <li>Updated the value of t<sub>ADC0_PU</sub> in Table 42, ADC conversion chara ADC_0)</li> <li>Updated the IDD values in Table 24, Low voltage power domain electrical related to current drawn from V<sub>DD_HV_A</sub> and V<sub>DD_HV_B</sub></li> <li>Updated the values of V<sub>LPREG</sub> in Table 22, Voltage regulator electrical characteristics.</li> <li>Added footnote to V<sub>LPREG</sub> in Table 22, Voltage regulator electrical characteristics.</li> <li>Added T<sub>A</sub> = 25 °C, min and max values of V<sub>LPREG</sub> in Table 22, Vo electrical characteristics</li> <li>Updated the min, max and typical values of V<sub>LDLVCORL</sub> and V<sub>LV</sub> Table 23, Low voltage of gmFXOSC in Table 35, Fast external crystal oscillator (32 kHz) electrical characteristics</li> <li>Updated the footnote 5 for T<sub>ADC0_C</sub> in Table 42, ADC conversion (10-bit ADC_0)</li> </ul> | nily comparison<br><sub>VAR</sub> in Table 40<br>conditions (5.0 V)<br>acteristics (10-bit<br>electrical<br>I characteristics<br>curacy"- Updated<br>haracteristics.<br>ctrical<br>oltage regulator<br>oltage regulator<br>rDLVBKPL in<br>oscillator (4 to 40<br>Table 37, Slow<br>characteristics |

| 5.1 15 Aug 2012 • Removed Footer: Preliminary tag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                    |