Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | e200z4d, e200z0h                                            |

| Core Size                  | 32-Bit Dual-Core                                            |

| Speed                      | 80MHz/120MHz                                                |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SCI, SPI        |

| Peripherals                | DMA, POR, PWM, WDT                                          |

| Number of I/O              | 147                                                         |

| Program Memory Size        | 3MB (3M x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 64K x 8                                                     |

| RAM Size                   | 256K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 27x10b, 5x12b                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 176-LQFP                                                    |

| Supplier Device Package    | 176-LQFP (24x24)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5646cf0mlu1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   | Introd | luction                                               |

|---|--------|-------------------------------------------------------|

|   | 1.1    | Document Overview                                     |

|   | 1.2    | Description                                           |

| 2 | Block  | diagram                                               |

| 3 | Packa  | age pinouts and signal descriptions                   |

|   | 3.1    | Pad types                                             |

|   | 3.2    | System pins14                                         |

|   | 3.3    | Functional ports14                                    |

| 4 | Elect  | rical Characteristics41                               |

|   | 4.1    | Parameter classification                              |

|   | 4.2    | NVUSRO register                                       |

|   |        | 4.2.1 NVUSRO [PAD3V5V(0)] field description42         |

|   |        | 4.2.2 NVUSRO [PAD3V5V(1)] field description42         |

|   | 4.3    | Absolute maximum ratings                              |

|   | 4.4    | Recommended operating conditions                      |

|   | 4.5    | Thermal characteristics                               |

|   |        | 4.5.1 Package thermal characteristics                 |

|   |        | 4.5.2 Power considerations                            |

|   | 4.6    | I/O pad electrical characteristics                    |

|   |        | 4.6.1 I/O pad types                                   |

|   |        | 4.6.2 I/O input DC characteristics                    |

|   |        | 4.6.3 I/O output DC characteristics                   |

|   |        | 4.6.4 Output pin transition times                     |

|   |        | 4.6.5 I/O pad current specification                   |

|   | 4.7    | RESET electrical characteristics                      |

|   | 4.8    | Power management electrical characteristics           |

|   |        | 4.8.1 Voltage regulator electrical characteristics57  |

|   |        | 4.8.2 VDD_BV options                                  |

|   |        | 4.8.3 Voltage monitor electrical characteristics 60   |

|   | 4.9    | Low voltage domain power consumption61                |

|   | 4.10   | Flash memory electrical characteristics               |

|   |        | 4.10.1 Program/Erase characteristics                  |

|   |        | 4.10.2 Flash memory power supply DC characteristics65 |

|   |        | 4.10.3 Flash memory start-up/switch-off timings66     |

|   | 4.11   | Electromagnetic compatibility (EMC) characteristics66 |

|   |        | 4.11.1 Designing hardened software to avoid noise     |

|   |       | problems                                                   |

|---|-------|------------------------------------------------------------|

|   |       | 4.11.2 Electromagnetic interference (EMI) 67               |

|   |       | 4.11.3 Absolute maximum ratings (electrical sensitivity)67 |

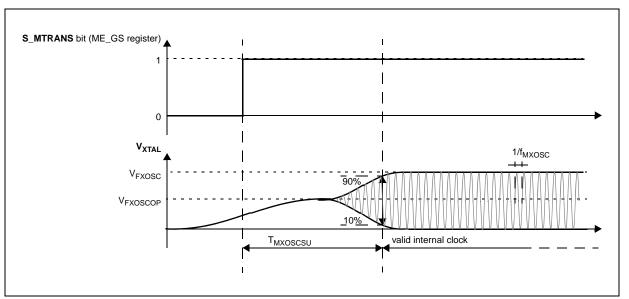

|   | 4.12  | Fast external crystal oscillator (4-40 MHz) electrical     |

|   |       | characteristics                                            |

|   | 4.13  | Slow external crystal oscillator (32 kHz) electrical       |

|   |       | characteristics                                            |

|   | 4.14  | FMPLL electrical characteristics                           |

|   | 4.15  | Fast internal RC oscillator (16 MHz) electrical            |

|   |       | characteristics                                            |

|   | 4.16  | Slow internal RC oscillator (128 kHz) electrical           |

|   |       | characteristics                                            |

|   | 4.17  | ADC electrical characteristics                             |

|   |       | 4.17.1 Introduction                                        |

|   | 4.18  | Fast Ethernet Controller 87                                |

|   |       | 4.18.1 MII Receive Signal Timing (RXD[3:0], RX_DV,         |

|   |       | RX_ER, and RX_CLK)                                         |

|   |       | 4.18.2 MII Transmit Signal Timing (TXD[3:0], TX_EN,        |

|   |       | TX_ER, TX_CLK)                                             |

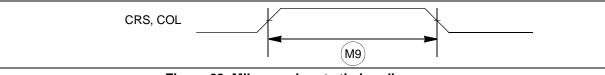

|   |       | 4.18.3 MII Async Inputs Signal Timing (CRS and COL)88      |

|   |       | 4.18.4 MII Serial Management Channel Timing (MDIO and      |

|   |       | MDC)89                                                     |

|   | 4.19  |                                                            |

|   |       | 4.19.1 Current consumption                                 |

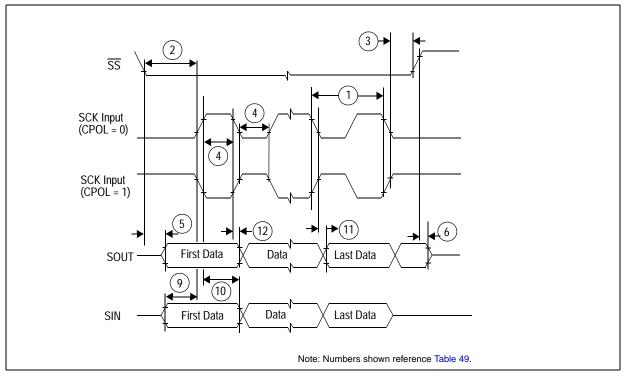

|   |       | 4.19.2 DSPI characteristics                                |

|   |       | 4.19.3 Nexus characteristics 101                           |

|   |       | 4.19.4 JTAG characteristics                                |

| 5 |       | age characteristics                                        |

|   | 5.1   | Package mechanical data 105                                |

|   |       | 5.1.1 176 LQFP package mechanical drawing 105              |

|   |       | 5.1.2 208 LQFP package mechanical drawing 108              |

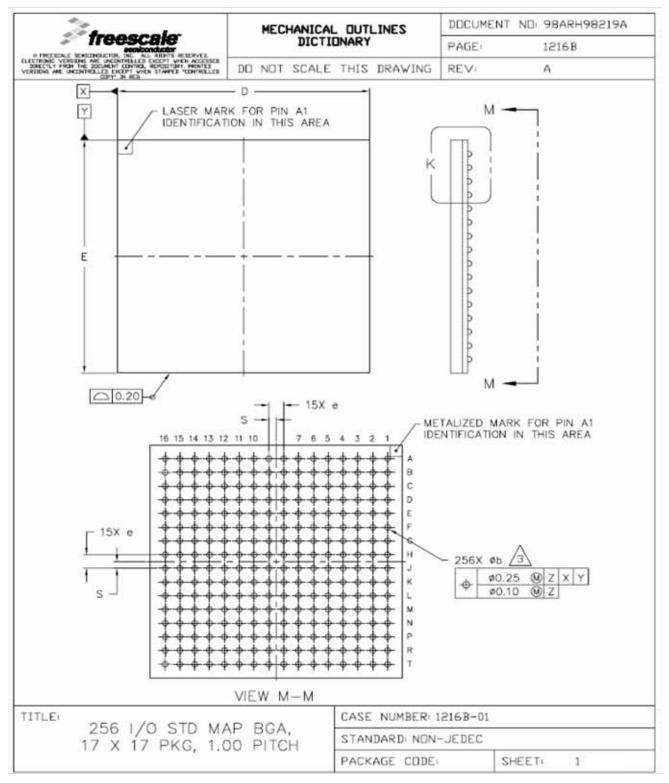

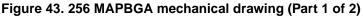

|   |       | 5.1.3 256 MAPBGA package mechanical drawing . 113          |

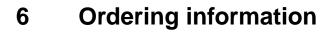

| 6 |       | ring information                                           |

| 7 | Revis | sion history                                               |

NP

\_\_\_\_\_

# 1 Introduction

## 1.1 Document Overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the MPC5646C device. To ensure a complete understanding of the device functionality, refer also to the MPC5646C Reference Manual.

## 1.2 Description

The MPC5646C is a new family of next generation microcontrollers built on the Power Architecture embedded category. This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

The MPC5646C family expands the range of the MPC560xB microcontroller family. It provides the scalability needed to implement platform approaches and delivers the performance required by increasingly sophisticated software architectures. The advanced and cost-efficient host processor core of the MPC5646C automotive controller family complies with the Power Architecture embedded category, which is 100 percent user-mode compatible with the original Power Architecture user instruction set architecture (UISA). It operates at speeds of up to 120 MHz and offers high performance processing optimized for low power consumption. It also capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

## Table 1. MPC5646C family comparison<sup>1</sup> (continued)

| Feature                                | MPC         | MPC5644B      |             | MPC5644C    |             | MPC5645B    |             | MPC5645C    |             | 5C          | MPC5646B    |             | MPC5646C    |             | 6C          |

|----------------------------------------|-------------|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Package                                | 176<br>LQFP | 208<br>LQFP   | 176<br>LQFP | 208<br>LQFP | 256<br>BGA  | 176<br>LQFP | 208<br>LQFP | 176<br>LQFP | 208<br>LQFP | 256<br>BGA  | 176<br>LQFP | 208<br>LQFP | 176<br>LQFP | 208<br>LQFP | 256<br>BGA  |

| Ethernet                               | N           | No Yes No Yes |             |             |             |             | N           | lo          | Yes         |             |             |             |             |             |             |

| l <sup>2</sup> C                       |             | 1             |             |             |             |             |             |             |             |             |             |             |             |             |             |

| 32 kHz oscillator (SXOSC)              |             |               |             |             |             |             |             | Yes         |             |             |             |             |             |             |             |

| GPIO <sup>12</sup>                     | 147         | 177           | 147         | 177         | 199         | 147         | 177         | 147         | 177         | 199         | 147         | 177         | 147         | 177         | 199         |

| Debug                                  |             | JT            | AG          |             | Nexus<br>3+ |             | JT          | AG          | 1           | Nexus<br>3+ |             | JT          | AG          | 1           | Nexus<br>3+ |

| Cryptographic Services<br>Engine (CSE) |             |               |             |             | 1           |             |             | Optiona     | I           |             | l.          |             |             |             | •           |

### NOTES:

<sup>1</sup> Feature set dependent on selected peripheral multiplexing; table shows example.

<sup>2</sup> Based on 125 °C ambient operating temperature and subject to full device characterisation.

<sup>3</sup> The e200z0h can run at speeds up to 80 MHz. However, if system frequency is >80 MHz (e.g., e200z4d running at 120 MHz) the e200z0h needs to run at 1/2 system frequency. There is a configurable e200z0 system clock divider for this purpose.

<sup>4</sup> DMAMUX also included that allows for software selection of 32 out of a possible 57 sources.

<sup>5</sup> Not shared with 12-bit ADC, but possibly shared with other alternate functions.

<sup>6</sup> There are 23 dedicated ANS plus 4 dedicated ANX channels on LQPF176. For higher pin count packages, there are 29 dedicated ANS plus 4 dedicated ANX channels.

<sup>7</sup> 16x precision channels (ANP) and 3x standard (ANS).

<sup>8</sup> Not shared with 10-bit ADC, but possibly shared with other alternate functions.

<sup>9</sup> As a minimum, all timer channels can function as PWM or Input Capture and Output Control. Refer to the eMIOS section of the device reference manual for information on the channel configuration and functions.

<sup>10</sup> CAN Sampler also included that allows ID of CAN message to be captured when in low power mode.

<sup>11</sup> STCU controls MBIST activation and reporting.

<sup>12</sup> Estimated I/O count for proposed packages based on multiplexing with peripherals.

1

MPC5646C Data Sheet, Rev.6

റ

Package pinouts and signal descriptions

- $F = Fast^{1, 2}$

- I = Input only with analog feature<sup>1</sup>

- A = Analog

## 3.2 System pins

The system pins are listed in Table 3.

## Table 3. System pin descriptions

|          |                                                                                                                                                                                       |                  |                |                                                |          | er       |            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------------------------------------|----------|----------|------------|

| Port pin | Function                                                                                                                                                                              | I/O<br>direction | Pad<br>type    | RESET<br>config.                               | 176 LQFP | 208 LQFP | 256 MAPBGA |

| RESET    | Bidirectional reset with Schmitt-Trigger characteristics and noise filter.                                                                                                            | I/O              | Μ              | Input, weak<br>pull-up only<br>after<br>PHASE2 | 29       | 29       | K1         |

| EXTAL    | Analog input of the oscillator amplifier<br>circuit. Needs to be grounded if oscillator<br>bypass mode is used.                                                                       | I                | A <sup>1</sup> | _                                              | 58       | 74       | Т8         |

| XTAL     | Analog output of the oscillator amplifier<br>circuit, when the oscillator is not in bypass<br>mode.<br>Analog input for the clock generator when<br>the oscillator is in bypass mode. | I/O              | A <sup>1</sup> | _                                              | 56       | 72       | Τ7         |

NOTES:

For analog pads, it is not recommended to enable IBE if APC is enabled to avoid extra current in middle range voltage.

## 3.3 Functional ports

The functional port pins are listed in Table 4.

|             |          |                                    |                                                  |                                               |                               |          |                  | Pir      | n numbe  | er         |

|-------------|----------|------------------------------------|--------------------------------------------------|-----------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup> | Function                                         | Peripheral                                    | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PI[7]       | PCR[135] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4   | GPIO[135]<br>E1UC[31]<br>CS1_4<br>CS1_5<br>CS1_6 | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6 | I/O<br>I/O<br>O<br>O          | S        | Tristate         | 12       | 12       | E2         |

| PI[8]       | PCR[136] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[136]<br>—<br>—<br>—<br>ADC0_S[16]           | SIUL<br> -<br> <br>ADC_0                      | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         | 108      | 130      | J14        |

| PI[9]       | PCR[137] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[137]<br>—<br>—<br>—<br>ADC0_S[17]           | SIUL<br>—<br>—<br>ADC_0                       | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         | _        | 131      | J15        |

| PI[10]      | PCR[138] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[138]<br>—<br>—<br>—<br>ADC0_S[18]           | SIUL<br>—<br>—<br>ADC_0                       | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 134      | J16        |

| PI[11]      | PCR[139] | AF0<br>AF1<br>AF2<br>AF3<br>       | GPIO[139]<br>—<br>—<br>—<br>ADC0_S[19]<br>SIN_3  | SIUL<br>—<br>—<br>ADC_0<br>DSPI_3             | /O<br><br><br> <br> <br>      | S        | Tristate         | 111      | 135      | H16        |

| PI[12]      | PCR[140] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[140]<br>CS0_3<br>CS0_2<br>—<br>ADC0_S[20]   | SIUL<br>DSPI_3<br>DSPI_2<br>—<br>ADC_0        | I/O<br>I/O<br>I/O<br>I        | S        | Tristate         | 112      | 136      | G15        |

| PI[13]      | PCR[141] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[141]<br>CS1_3<br>CS1_2<br>—<br>ADC0_S[21]   | SIUL<br>DSPI_3<br>DSPI_2<br>—<br>ADC_0        | I/O<br>O<br>—<br>I            | S        | Tristate         | 113      | 137      | G14        |

| PI[14]      | PCR[142] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[142]<br>—<br>—<br>—<br>ADC0_S[22]<br>SIN_4  | SIUL<br>—<br>—<br>ADC_0<br>DSPI_4             | /O<br>                        | S        | Tristate         | 76       | 92       | T12        |

| Table 4. Functional | port pin        | descriptions   | (continued) |

|---------------------|-----------------|----------------|-------------|

|                     | P • • • P · · · | acceriptione , |             |

|             |          |                                              |                                                                            |                                                                   |                               |          |                  | Pir      | n numbe  | ər         |

|-------------|----------|----------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR      | Alternate<br>function <sup>1</sup>           | Function                                                                   | Peripheral                                                        | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PJ[7]       | PCR[151] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[151]<br>—<br>—<br>—<br>ADC0_S[30]                                     | SIUL<br>—<br>—<br>ADC_0                                           | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 111      | P16        |

| PJ[8]       | PCR[152] | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[152]<br>—<br>—<br>—<br>ADC0_S[31]                                     | SIUL<br>—<br>—<br>ADC_0                                           | I/O<br>—<br>—<br>I            | S        | Tristate         | _        | 110      | P15        |

| PJ[9]       | PCR[153] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[153]<br>—<br>—<br>—<br>ADC1_S[8]                                      | SIUL<br>—<br>—<br>—<br>ADC_1                                      | I/O<br>—<br>—<br>—<br>—       | S        | Tristate         | _        | 68       | P5         |

| PJ[10]      | PCR[154] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[154]<br>—<br>—<br>—<br>ADC1_S[9]                                      | SIUL<br>—<br>—<br>—<br>ADC_1                                      | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 67       | Τ5         |

| PJ[11]      | PCR[155] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[155]<br>—<br>—<br>—<br>ADC1_S[10]                                     | SIUL<br>—<br>—<br>—<br>ADC_1                                      | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 60       | R3         |

| PJ[12]      | PCR[156] | AF0<br>AF1<br>AF2<br>AF3<br>—                | GPIO[156]<br>—<br>—<br>—<br>ADC1_S[11]                                     | SIUL<br>—<br>—<br>—<br>ADC_1                                      | I/O<br>—<br>—<br>—<br>I       | S        | Tristate         |          | 59       | T1         |

| PJ[13]      | PCR[157] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—<br>— | GPIO[157]<br>—<br>CS1_7<br>—<br>CAN4RX<br>ADC1_S[12]<br>CAN1RX<br>WKPU[31] | SIUL<br><br>DSPI_7<br><br>FlexCAN_4<br>ADC_1<br>FlexCAN_1<br>WKPU | /O<br>                        | S        | Tristate         |          | 65       | N5         |

| PJ[14]      | PCR[158] | AF0<br>AF1<br>AF2<br>AF3                     | GPIO[158]<br>CAN1TX<br>CAN4TX<br>CS2_7                                     | SIUL<br>FlexCAN_1<br>FlexCAN_4<br>DSPI_7                          | I/O<br>O<br>O<br>O            | M/S      | Tristate         |          | 64       | T4         |

| Table 4. Functional port pir | descriptions (continued) |

|------------------------------|--------------------------|

| Table III anotienai peri pi  |                          |

## NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions  $(V_{IN} > V_{DD\_HV\_A/HV\_B} \text{ or } V_{IN} < V_{SS\_HV})$ , the voltage on pins with respect to ground  $(V_{SS\_HV})$  must not exceed the recommended values.

#### **Recommended operating conditions** 4.4

| Symbol                               |    | Parameter                                                                                                     | Conditions                                    | Va                       | lue                                                                                                                                                                                                                                                                   | Unit |

|--------------------------------------|----|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbol                               |    | Faiametei                                                                                                     | Conditions                                    | Min                      | Min         Max           0         0           3.0         3.6           3.0         3.6           3.0         3.6 $3.0$ 3.6 $-HV - 0.1$ $V_{SS_HV} + 0.1$ $0$ $V_{DD_LV} + 1$ $-HV - 0.1$ $V_{SS_HV} + 0.1$ $3.0^5$ $3.6$ $+VA - 0.1$ $V_{DDHVA} + 0.1$ $3.0$ $3.6$ | Onit |

| V <sub>SS_HV</sub>                   | SR | Digital ground on VSS_HV pins                                                                                 |                                               | 0                        | 0                                                                                                                                                                                                                                                                     | V    |

| V <sub>DD_HV_A</sub> 1               | SR | Voltage on V <sub>DD_HV_A</sub> pins<br>with respect to ground<br>(V <sub>SS_HV</sub> )                       | _                                             | 3.0                      | 3.6                                                                                                                                                                                                                                                                   | V    |

| V <sub>DD_HV_B</sub> 1               | SR | Voltage on V <sub>DD_HV_B</sub> pins<br>with respect to ground<br>(V <sub>SS_HV</sub> )                       | _                                             | 3.0                      | 3.6                                                                                                                                                                                                                                                                   | V    |

| V <sub>SS_LV</sub> <sup>2</sup>      | SR | Voltage on VSS_LV (low<br>voltage digital supply) pins<br>with respect to ground<br>(V <sub>SS_HV</sub> )     | _                                             | V <sub>SS_HV</sub> – 0.1 | V <sub>SS_HV</sub> + 0.1                                                                                                                                                                                                                                              | V    |

| V <sub>RC_CTRL</sub> <sup>3</sup>    |    | Base control voltage for<br>external BCP68 NPN device                                                         | Relative to V <sub>DD_LV</sub>                | 0                        | V <sub>DD_LV</sub> + 1                                                                                                                                                                                                                                                | V    |

| V <sub>SS_ADC</sub>                  | SR | Voltage on VSS_HV_ADC0,<br>VSS_HV_ADC1 (ADC<br>reference) pin with respect to<br>ground (V <sub>SS_HV</sub> ) | _                                             | V <sub>SS_HV</sub> - 0.1 | V <sub>SS_HV</sub> + 0.1                                                                                                                                                                                                                                              | V    |

| V <sub>DD_HV_ADC0</sub> <sup>4</sup> | SR |                                                                                                               | _                                             | 3.0 <sup>5</sup>         | 3.6                                                                                                                                                                                                                                                                   | V    |

|                                      |    | with respect to ground<br>(V <sub>SS_HV</sub> )                                                               | Relative to V <sub>DD_HV_A</sub> <sup>6</sup> | $V_{DD_HV_A} - 0.1$      | V <sub>DD_HV_A</sub> + 0.1                                                                                                                                                                                                                                            |      |

| V <sub>DD_HV_ADC1</sub> <sup>7</sup> | SR |                                                                                                               | —                                             | 3.0                      | 3.6                                                                                                                                                                                                                                                                   | V    |

|                                      |    | with respect to ground<br>(V <sub>SS_HV</sub> )                                                               | Relative to V <sub>DD_HV_A</sub> <sup>6</sup> | $V_{DD_HV_A} - 0.1$      | V <sub>DD_HV_A</sub> + 0.1                                                                                                                                                                                                                                            |      |

| V <sub>IN</sub>                      | SR | Voltage on any GPIO pin with                                                                                  | —                                             | V <sub>SS_HV</sub> - 0.1 | —                                                                                                                                                                                                                                                                     | V    |

|                                      |    | respect to ground ( $V_{SS_HV}$ )                                                                             | Relative to<br>V <sub>DD_HV_</sub> A/HV_B     |                          | V <sub>DD_HV_A/HV_B</sub><br>+ 0.1                                                                                                                                                                                                                                    |      |

| Symbol              |    | с | Parameter                              | Conditions <sup>1,2</sup>                  |     | Value <sup>3</sup> |                 | Unit |

|---------------------|----|---|----------------------------------------|--------------------------------------------|-----|--------------------|-----------------|------|

| Gymbol              |    | Ŭ | randicter                              | Conditions                                 | Min | Тур                | Max             | onne |

| I <sub>AVGSEG</sub> | SR |   |                                        | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 |     | _                  | 70              | mA   |

|                     |    |   | I/O current within a<br>supply segment | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |     |                    | 65 <sup>4</sup> |      |

### Table 20. I/O consumption (continued)

NOTES:  $^{1}$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

$^{2}$  V<sub>DD</sub> as mentioned in the table is V<sub>DD\_HV\_A</sub>/V<sub>DD\_HV\_B</sub>.

<sup>3</sup> All values need to be confirmed during device validation.

<sup>4</sup> Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

#### **RESET** electrical characteristics 4.7

The device implements a dedicated bidirectional RESET pin.

Figure 6. Start-up reset requirements

| Symbol                 |    | с | Parameter                                                                                     | Conditions <sup>1</sup>                               |     | Value <sup>2</sup> |                  | Unit |

|------------------------|----|---|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|--------------------|------------------|------|

| Symbol                 |    | C | Falameter                                                                                     | Conditions                                            | Min | Тур Мах            |                  | Unit |

| I <sub>LPREGINT</sub>  | СС | D | Low power regulator module current consumption                                                | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | -   | —                  | 600              | μΑ   |

|                        |    |   |                                                                                               | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _   | 20                 |                  |      |

| I <sub>VREGREF</sub>   | СС | D | Main LVDs and reference current<br>consumption (low power and main<br>regulator switched off) | T <sub>A</sub> = 55 °C                                | _   | 2                  | _                | μA   |

| I <sub>VREDLVD12</sub> | СС | D | Main LVD current consumption (switch-off during standby)                                      | T <sub>A</sub> = 55 °C                                | -   | 1                  |                  | μA   |

| I <sub>DD_HV_A</sub>   | СС | D | In-rush current on V <sub>DD_BV</sub> during power-up                                         | _                                                     | -   |                    | 600 <sup>3</sup> | mA   |

NOTES:

$^1$  V<sub>DD HV A</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> Inrush current is seen more like steps of 600 mA peak. The startup of the regulator happens in steps of 50 mV in ~25 steps to reach ~1.2 V V<sub>DD LV</sub>. Each step peak current is within 600 mA

## 4.8.3 Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as four low voltage detectors to monitor the  $V_{DD\ HV\ A}$  and the  $V_{DD\ LV}$  voltage while device is supplied:

- POR monitors V<sub>DD\_HV\_A</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors  $V_{DD HV_A}$  to ensure device is reset below minimum functional supply

- LVDHV5 monitors  $V_{DD HV A}$  when application uses device in the 5.0 V±10% range

- LVDLVCOR monitors power domain No. 1 (PD1)

- LVDLVBKP monitors power domain No. 0 (PD0). VDD\_LV is same as PD0 supply.

## NOTE

When enabled, PD2 (RAM retention) is monitored through LVD\_DIGBKP.

| Symbol                | I  | с | Parameter                                            | Conditions <sup>1</sup>                                                                             |                | Value <sup>2</sup> |                 | Unit |

|-----------------------|----|---|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|--------------------|-----------------|------|

| Symbol                | I  |   | Farameter                                            | Conditions                                                                                          | Min            | Тур                | Max             | Unit |

| f <sub>FXOSC</sub>    | SR | — | Fast external crystal<br>oscillator frequency        | _                                                                                                   | 4.0            | -                  | 40.0            | MHz  |

| g <sub>mFXOSC</sub>   | CC | С | Fast external crystal                                | $V_{DD} = 3.3 \text{ V} \pm 10\%$                                                                   | 4 <sup>3</sup> | —                  | 20 <sup>3</sup> | mA/V |

|                       |    |   | oscillator<br>transconductance                       | $V_{DD} = 5.0 V \pm 10\%$                                                                           | 4 <sup>3</sup> | -                  | 20 <sup>3</sup> |      |

| V <sub>FXOSC</sub>    | CC | Т | Oscillation<br>amplitude at EXTAL                    | $f_{OSC} = 40 \text{ MHz}$<br>For both V <sub>DD</sub> = 3.3 V ± 10%, V <sub>DD</sub> = 5.0 V ± 10% | _              | 0.95               | —               | V    |

| V <sub>FXOSCOP</sub>  | СС | Ρ | Oscillation<br>operating point                       | _                                                                                                   | —              | 1.8                |                 | V    |

| I <sub>FXOSC</sub> ,4 | СС | Т | Fast external crystal oscillator                     | $V_{DD} = 3.3 V \pm 10\%,$<br>$f_{OSC} = 40 \text{ MHz}$                                            | _              | 2                  | 2.2             |      |

|                       |    |   | consumption                                          | $V_{DD} = 5.0 V \pm 10\%,$<br>$f_{OSC} = 40 MHz$                                                    | _              | 2.3                | 2.5             | mA   |

|                       |    |   |                                                      | $V_{DD} = 3.3 V \pm 10\%,$<br>$f_{OSC} = 16 MHz$                                                    | _              | 1.3                | 1.5             |      |

|                       |    |   |                                                      | $V_{DD} = 5.0 V \pm 10\%,$<br>$f_{OSC} = 16 MHz$                                                    | —              | 1.6                | 1.8             |      |

| T <sub>FXOSCSU</sub>  | CC | Т | Fast external crystal<br>oscillator start-up<br>time | $f_{OSC} = 40 \text{ MHz}$<br>For both V <sub>DD</sub> = 3.3 V ± 10%, V <sub>DD</sub> = 5.0 V ± 10% | _              | —                  | 5               | ms   |

| Symbol                |    | с | Parameter                                                                                                                                                 | Co                      | onditions <sup>1</sup>            |     | Value <sup>2</sup> |     | Unit |

|-----------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|-----|--------------------|-----|------|

| Cymbol                |    | Ŭ | i alameter                                                                                                                                                |                         |                                   | Min | Тур                | Мах | Unit |

| I <sub>FIRCSTOP</sub> | СС | Т | Fast internal RC oscillator high                                                                                                                          | T <sub>A</sub> = 25 °C  | sysclk = off                      | _   | 500                | _   | μA   |

|                       |    |   | frequency and system clock<br>current in stop mode                                                                                                        |                         | sysclk = 2 MHz                    | —   | 600                |     |      |

|                       |    |   | '                                                                                                                                                         |                         | sysclk = 4 MHz                    | —   | 700                |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 8 MHz                    | —   | 900                |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 16 MHz                   | —   | 1250               |     |      |

| T <sub>FIRCSU</sub>   | СС | С | Fast internal RC oscillator                                                                                                                               | T <sub>A</sub> = 55 °C  | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | _   |                    | 2.0 | μs   |

|                       |    |   | start-up time                                                                                                                                             |                         | $V_{DD} = 3.3 \text{ V} \pm 10\%$ | _   |                    | 5   |      |

|                       |    | _ |                                                                                                                                                           | T <sub>A</sub> = 125 °C | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | —   |                    | 2.0 |      |

|                       |    |   |                                                                                                                                                           |                         | $V_{DD} = 3.3 \text{ V} \pm 10\%$ | _   |                    | 5   |      |

| <sup>∆</sup> fircpre  | СС | С | Fast internal RC oscillator<br>precision after software<br>trimming of f <sub>FIRC</sub>                                                                  | Т                       | <sub>A</sub> = 25 °C              | -1  |                    | +1  | %    |

|                       | СС | С | Fast internal RC oscillator<br>trimming step                                                                                                              | Т                       | <sub>A</sub> = 25 °C              | _   | 1.6                |     | %    |

|                       | СС | С | Fast internal RC oscillator<br>variation over temperature and<br>supply with respect to $f_{FIRC}$ at<br>$T_A = 25$ °C in high-frequency<br>configuration | _                       |                                   | -5  |                    | +5  | %    |

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

#### 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz low power internal RC oscillator. This can be used as the reference clock for the RTC module.

| Symbol                          | Symbol C |   | Parameter                                            | Conditions <sup>1</sup>           |     | Value <sup>2</sup> |     | Unit |

|---------------------------------|----------|---|------------------------------------------------------|-----------------------------------|-----|--------------------|-----|------|

| Cymbol                          |          | Ŭ | i di di lictori                                      | Conditions                        | Min | Тур                | Max | onn  |

| f <sub>SIRC</sub>               | СС       | Ρ | Slow internal RC oscillator low                      | T <sub>A</sub> = 25 °C, trimmed   | _   | 128                | _   | kHz  |

|                                 | SR       |   | frequency                                            | untrimmed, across<br>temperatures | 84  | _                  | 205 |      |

| I <sub>SIRC</sub> <sup>3,</sup> | СС       |   | Slow internal RC oscillator low<br>frequency current | T <sub>A</sub> = 25 °C, trimmed   | —   | _                  | 5   | μA   |

Table 40. Slow internal RC oscillator (128 kHz) electrical characteristics

| Symbol               |    | с | Parameter                                                                                                | Conditions <sup>1</sup>                                |     | Value <sup>2</sup> |     | Unit |

|----------------------|----|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|--------------------|-----|------|

| Cymbol               |    |   | Conditions                                                                                               | Min                                                    | Тур | Max                |     |      |

| T <sub>SIRCSU</sub>  | СС | Ρ | Slow internal RC oscillator start-up time                                                                | $T_A = 25 \text{ °C}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | _   | 8                  | 12  | μs   |

| $\Delta_{SIRCPRE}$   | СС | С | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub>                       | T <sub>A</sub> = 25 °C                                 | -2  |                    | +2  | %    |

|                      | СС | С | Slow internal RC oscillator trimming step                                                                | _                                                      | _   | 2.7                | —   |      |

| <sup>∆</sup> sircvar | СС | С | Variation in f <sub>SIRC</sub> across<br>temperature and fluctuation in<br>supply voltage, post trimming | _                                                      | -10 |                    | +10 | %    |

### Table 40. Slow internal RC oscillator (128 kHz) electrical characteristics (continued)

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

<sup>2</sup> All values need to be confirmed during device validation.

<sup>3</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

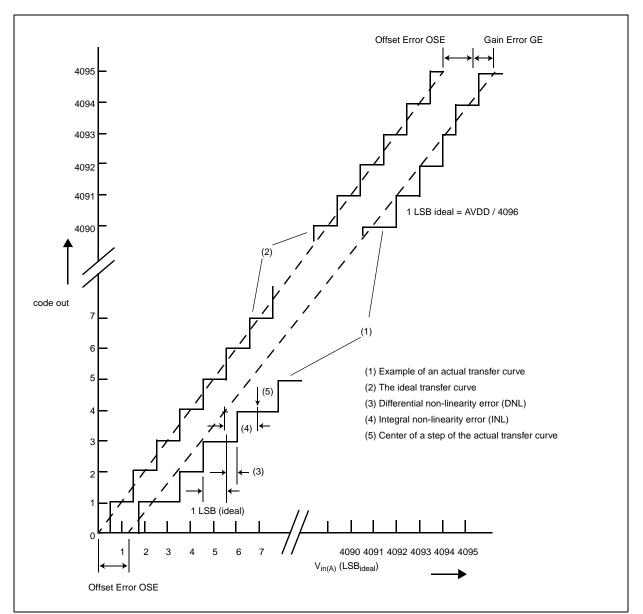

#### 4.17 **ADC** electrical characteristics

#### 4.17.1 Introduction

The device provides two Successive Approximation Register (SAR) analog-to-digital converters (10-bit and 12-bit).

## NOTE

Due to ADC limitations, the two ADCs cannot sample a shared channel at the same time i.e., their sampling windows cannot overlap if a shared channel is selected. If this is done, neither of the ADCs can guarantee their conversion accuracies.

Figure 20. ADC\_1 characteristic and error definitions

Figure 23. MII async inputs timing diagram

#### 4.18.4 **MII Serial Management Channel Timing (MDIO and MDC)**

The FEC functions correctly with a maximum MDC frequency of 2.5 MHz.

| Spec | Characteristic                                                               | Min | Max | Unit       |

|------|------------------------------------------------------------------------------|-----|-----|------------|

| M10  | MDC falling edge to<br>MDIO output invalid<br>(minimum<br>propagation delay) | 0   | _   | ns         |

| M11  | MDC falling edge to<br>MDIO output valid<br>(max prop delay)                 | _   | 25  | ns         |

| M12  | MDIO (input) to MDC<br>rising edge setup                                     | 28  | -   | ns         |

| M13  | MDIO (input) to MDC<br>rising edge hold                                      | 0   | —   | ns         |

| M14  | MDC pulse width high                                                         | 40% | 60% | MDC period |

| M15  | MDC pulse width low                                                          | 40% | 60% | MDC period |

## Table 47. MII serial management channel timing<sup>1</sup>

NOTES: <sup>1</sup> Output pads configured with SRE = 0b11.

Figure 27. DSPI classic SPI timing–slave, CPHA = 0

## 5.1.3 256 MAPBGA package mechanical drawing

MPC5646C Data Sheet, Rev.6

Figure 45. Orderable parts

**Revision history**

# 7 Revision history

Table 52 summarizes revisions to this document.

## Table 52. Revision history

| Revision | Date           | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | 15 April 2010  | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2        | 17 August 2010 | <ul> <li>Editing and formatting updates throughout the document.</li> <li>Updated Voltage regulator capacitance connection figure.</li> <li>Added a new sub-section "V<sub>DD_BV</sub> Options"</li> <li>Program and erase specifications:         <ul> <li>Updated Tdwprogram TYP to 22 us</li> <li>Updated T128Kpperase Max to 5000 ms</li> <li>Added 128UB parameter</li> </ul> </li> <li>Added recommendation in the Voltage regulator electrical characteristics section</li> <li>Added Crystal description table in Fast external crystal oscillator (4 to 140 MHz) electrical characteristics section and corrected the cross-reference to the same.</li> <li>Added a new sections - Pad types, System pins and functional ports</li> <li>Updated TYP numbers in the Flash program and erase specifications table</li> <li>Added a new table: Program and erase specifications (Data Flash)</li> <li>Flash read access timing table: Added Data flash memory numbers</li> <li>Flash power supply DC electrical characteristics table: Updated IDFREAD and IDFMOD values for Data flash, Removed IDFLPW parameter</li> <li>Updated feature list.</li> <li>MPC5646C 3M family comparison table: Updated ADC channels and added ADC footnotes.</li> <li>Functional Port Pin Descriptions table: Added OSC32k_XTAL and OSC32k_EXTAL function at PB8 and PB9 port pins.</li> <li>Electrical Characteristics: Replaced VSS with VSS_HV throughout the section.</li> <li>Absolute maximum ratings, Recommended operating conditions (3.3 V) and Recommended operating conditions (3.3 V) and Recommended operating conditions (5.0 V) tables: Clarified footnote 2 in both tables.</li> <li>LQFP thermal characteristics section: Updated numbers for LQFP packages.</li> <li>Low voltage power domain electrical characteristics table: Clarified footnotes based upon review comments.</li> <li>Code flash memory—Program and erase specifications: Updated tESRT to 20 ms</li> <li>ADC electrical ch</li></ul> |  |  |  |

## **Revision history**

| Revision | Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 12 Feb 2014 | <ul> <li>Removed occurrences of 208BGA from Table 3 System pin descriptions.</li> <li>Added PM[3] and PM[4] in the figure note 1 of Figure 4, 256-pin BGA configuration.</li> <li>Added a table note in Table 19 I/O supplies.</li> <li>Updated Figure 8, Voltage regulator capacitance connection and added a note in this figure.</li> <li>Removed max values of V<sub>LPREG</sub> and V<sub>MREG</sub>, changed min value of V<sub>LPREG</sub> to 1.21 V, and updated V<sub>MREG</sub> and V<sub>LPREG</sub> after trimming values in Table 22 Voltage regulator electrical characteristics.</li> <li>Updated 1st footnote and updated max values for I<sub>DDRUN</sub>, I<sub>DDHALT</sub>, I<sub>DDSTOP</sub> I<sub>DDSTDBY3</sub>, I<sub>DDSTDBY2</sub>, I<sub>DDSTDBY1</sub> and removed values at 85°C and 105°C in Table 24 Low voltage power domain electrical characteristics.</li> <li>Added a footnote below Table 28 Flash memory read access timing.</li> <li>Updated the formula in Eq. 11 in Section 4.17.1.1, "Input impedance and ADC accuracy.</li> <li>Added Figure 17, Input equivalent circuit (extended channels).</li> <li>Updated t<sub>ADC0_PU</sub> value to 1.5 as max and added footnote for I<sub>INJ</sub> in Table 42 ADC conversion characteristics (10-bit ADC_0).</li> <li>Added Category column in Table 43 Conversion characteristics (12-bit ADC_1).</li> <li>Added the IDD_HV_ADC0 values in Table 48 On-chip peripherals current consumption.</li> <li>Added a note in Figure 45, Orderable parts.</li> </ul> |

## Table 52. Revision history (continued)

## NOTE

This revision history uses clickable cross-references for ease of navigation. The numbers and titles in each cross-reference are relative to the latest published release.

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandCo nditions.html.

Freescale, the Freescale logo, is trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2009-2014 Freescale Semiconductor, Inc.

MPC5646C Rev.6 02/2014