#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z7                                                                   |

| Core Size                  | 32-Bit Tri-Core                                                          |

| Speed                      | 264MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                  |

| Peripherals                | DMA, LVD, POR, Zipwire                                                   |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 8MB (8M × 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 516-BGA                                                                  |

| Supplier Device Package    | 516-MAPBGA (27x27)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777clk3mmo3r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 1       | 2            | 3               | 4             | 5             | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13      | 14       | 15      | 16          | 17             | 18             | 19            | 20            | 21     | 22     | 23      | 24      | 25      | 26      | _ |

|--------|---------|--------------|-----------------|---------------|---------------|---------------|-------|-------|----------------|----------------|----------------|----------------|---------|----------|---------|-------------|----------------|----------------|---------------|---------------|--------|--------|---------|---------|---------|---------|---|

| A      | VSS     | VDD          | RSTOUT          | ANAO_SDA<br>O | ANA4          | ANAS          | ANA11 | ANA15 | VDDA_SD        | REFBYPCA<br>25 | VRL_SD         | VRH_SD         | AN28    | AN32     | AN36    | VDDA_E<br>Q | REFBYPCB<br>25 | VRL_EQ         | VRH_EQ        | ANB7_SDD<br>7 | ANB11  | ANB14  | ANB17   | ANB21   | ANB23   | VSS     | , |

| в      | VDDEH1  | VSS          | VDD             | TEST          | ANA1_SDA<br>1 | ANA5          | ANA10 | ANA14 | VDDA_MISC      | VSSA_SD        | REFBYPCA<br>75 | AN24           | AN27    | AN29     | AN33    | VDDA_E<br>Q | VSSA_EQ        | REFBYPCB<br>75 | ANB6_SDD<br>6 | ANB8          | ANB10  | ANB15  | ANB18   | ANB22   | VSS     | TCRCLKC |   |

| с      | ETPUA30 | ETPUA31      | VSS             | VDD           | ANA2_SDA<br>2 | ANA6          | ANA9  | ANA13 | ANA17_SDB<br>1 | B3             | C1             | C3             | AN26    | AN30     | AN34    | AN37        | AN38           | ANBO_SDD<br>0  | ANB4_SDD<br>4 | ANB5_SDD<br>5 | ANB12  | ANB16  | ANB19   | VSS     | ETPUCO  | ETPUC1  |   |

| D      | ETPUA27 | ETPUA28      | ETPUA29         | VSS           | VDD           | ANA3_SDA<br>3 | ANA7  | ANA12 | ANA16_SDB<br>0 | ANA18_SD<br>B2 | ANA20_SD<br>CO | ANA22_SD<br>C2 | AN25    | AN31     | AN35    | AN39        | ANB1_SDD<br>1  | ANB2_SDD<br>2  | ANB3_SDD<br>3 | ANB9          | ANB13  | ANB20  | VSS     | SENT2_A | ETPUC2  | ETPUC3  |   |

| E      | ETPUA23 | ETPUA24      | ETPUA25         | ETPUA26       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDDEH7  | ETPUC4  | ETPUCS  | ETPUC6  |   |

|        | ETPUA19 | ETPUA20      | ETPUA21         | ETPUA22       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 |   |

|        | ETPUA15 | ETPUA16      | ETPUA17         | ETPUA18       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 |   |

| •      | ETPUA11 | ETPUA12      | ETPUA14         | ETPUA13       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC15 | ETPUC16 | ETPUC17 | ETPUC18 |   |

|        | ETPUA7  | ETPUA8       | ETPUA9          | ETPUA10       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC19 | ETPUC20 | ETPUC21 | ETPUC22 |   |

|        | ETPUA3  | ETPUA4       | ETPUAS          | ETPUA6        |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC23 | ETPUC24 | ETPUC25 | ETPUC26 |   |

|        | TCRCLKA | ETPUAO       | ETPUA1          | ETPUA2        |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC27 | ETPUC28 | ETPUC29 | ETPUC30 |   |

| ۱.     | NC      | TXDA         | RXDA            | VSTBY         |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC31 | ETPUB15 | ETPUB14 | VDDEH7  |   |

| •      | RXDB    | BOOTCFG<br>1 | WKPCFG          | VDD           |               |               |       |       |                | VDDE2          | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | VDDEH6  | ETPUB11 | ETPUB12 | ETPUB13 |   |

| ,<br>- | TXDB    | PLLCFG1      | PLLCFG2         | VDDEH1        |               |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB7  | ETPUB8  | ETPUB9  | ETPUB10 |   |

| ۲      | JCOMP   | RESET        | PLLCFG0         | RDY           |               |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB3  | ETPUB4  | ETPUB5  | ETPUB6  |   |

|        | VDDE2   | мско         | MSEO1           | EVTI          |               |               |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | TCRCLKB | ETPUBO  | ETPUB1  | ETPUB2  |   |

| '      | EVTO    | MSEOO        | MD00            | MDO1          |               |               |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB19 | ETPUB18 | ETPUB17 |         |   |

| 1      | MDO2    | MDO3         | MDO4            | MDO5          |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUB26 | ETPUB22 | ETPUB21 | ETPUB20 |   |

| ۷      | MDO6    | MDO7         | MD08            | VDDE2         |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | REGSEL  | ETPUB25 | ETPUB24 | ETPUB23 |   |

| -      | MDO9    | MDO10        | MDO11           | MDO15         |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUB29 | ETPUB28 | ETPUB27 | REGCTL  |   |

| ^      | MDO12   | MDO13        | MDO14           | NC            |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDDPMC  | ETPUB30 | VDDPWR  | VSSSYN  |   |

| в      | TDO     | тск          | TMS             | VDD           | FEC_TXCLK     |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDD     | ETPUB31 | VSSPWR  | EXTAL   |   |

| с      | VDDE2   | TDI          | VDD             | VSS           | REFCLK        | PCSA1         | PCSA2 | PCSB4 | PCSB1          | VDDEH3         | VDDEH4         |                |         | <u> </u> |         |             |                | EMIOS31        | CNRXB         | CNRXD         | VDDEH5 | PCSC1  | VSSPMC  | VDD     | VDDEH6  | XTAL    |   |

| D      | ENGCLK  | VDD          | VSS<br>FEC_RX_D | -             | FEC_TXD1      | PCSA5         | SOUTA | SCKA  | PCSBO          | PCSB3          | EMIOS2         |                |         | <u> </u> |         |             |                | EMIOS30        | CNTXB         | CNTXD         | SCKC   | RXDC   | PCSC3   | VSS     | VDD     | VDDFLA  |   |

| E      | VDD     | VSS          | v               | FEC_TX_EN     |               | PCSAD         | PCSA3 | SCKB  | SINB           | EMIOSO         | EMIOS3         |                |         | <u> </u> |         |             | EMIOS25        | EMIOS29        | CNRXA         | CNRXC         | PCSCO  | SINC   | PCSC2   | PCSC5   | VSS     | VDD     |   |

| F      | VSS     | VDDE2A       | FEC_RXD0        | FEC_RXD1      | VDDEH3A       | PCSB5         | SINA  | PCSB2 | SOUTB          | EMIOS1         | EMIOS4         | EMIOS7         | EMIOS11 | EMIOS12  | EMIÖS16 | EMIOS20     | EMIOS24        | EMIOS28        | CNTXA         | CNTXC         | SOUTC  | VDDEH4 | TXDC    | PCSC4   | VDDEH5  | VSS     | I |

|        | 1       | 2            | 3               | 4             | 5             | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13      | 14       | 15      | 16          | 17             | 18             | 19            | 20            | 21     | 22     | 23      | 24      | 25      | 26      |   |

Figure 2. MPC5777C 416-ball MAPBGA (full diagram)

# 2.2 516-ball MAPBGA pin assignments

Figure 3 shows the 516-ball MAPBGA pin assignments.

#### **Electrical characteristics**

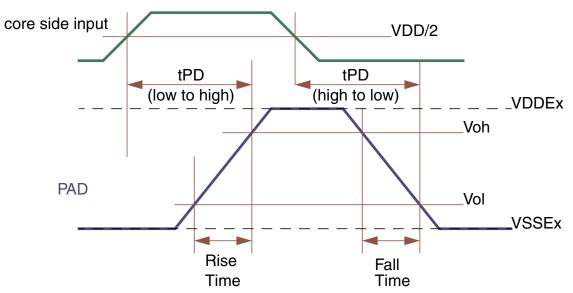

Figure 5. I/O output DC electrical characteristics definition

The following tables specify output DC electrical characteristics.

| Table 9. | GPIO and EBI data pad output buffer electrical characteristics (SR |

|----------|--------------------------------------------------------------------|

|          | pads) <sup>1</sup>                                                 |

| Symbol          | Parameter            | Conditions <sup>2</sup>                   | Conditions <sup>2</sup> |      |   | Value <sup>3</sup> |      |  |  |  |

|-----------------|----------------------|-------------------------------------------|-------------------------|------|---|--------------------|------|--|--|--|

| Symbol          | Falameter            | Conditions                                |                         |      |   | Max                | Unit |  |  |  |

|                 | GPIO pad output high | $V_{OH} = 0.8 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b   | 25   | — | _                  | mA   |  |  |  |

|                 | current              | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b   | 15   | — | _                  |      |  |  |  |

|                 |                      | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b   | 13   |   | _                  |      |  |  |  |

|                 |                      | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b   | 8    | — | _                  |      |  |  |  |

| I <sub>OL</sub> | GPIO pad output low  | $V_{OL} = 0.2 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b   | 48   | — | _                  | mA   |  |  |  |

|                 | current              | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b   | 22   | — | _                  |      |  |  |  |

|                 |                      | V <sub>OL</sub> = 0.2 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b   | 17   | _ | _                  |      |  |  |  |

|                 |                      | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b   | 10.5 | — |                    |      |  |  |  |

Table continues on the next page ...

1. PCR[DSC] values refer to the setting of that register field in the SIU.

## 3.6.3 I/O pad current specifications

The I/O pads are distributed across the I/O supply segments. Each I/O supply segment is associated with a  $V_{DDEx}$  supply segment.

Table 11 provides I/O consumption figures.

To ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 1.

To ensure device functionality, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 3.

#### NOTE

The MPC5777C I/O Signal Description and Input Multiplexing Tables are contained in a Microsoft Excel® file attached to the Reference Manual. In the spreadsheet, select the I/O Signal Table tab.

| Symbol                | Parameter                 | Conditions                                                  |     | Unit |      |    |

|-----------------------|---------------------------|-------------------------------------------------------------|-----|------|------|----|

| Symbol                |                           | Conditions                                                  | Min | Тур  | Мах  |    |

| I <sub>AVG_GPIO</sub> |                           | C <sub>L</sub> = 25 pF, 2 MHz                               | —   | —    | 0.42 | mA |

|                       |                           | $V_{DDEx} = 5.0 V \pm 10\%$                                 |     |      |      |    |

|                       |                           | C <sub>L</sub> = 50 pF, 1 MHz                               | —   | —    | 0.35 |    |

|                       |                           | $V_{DDEx} = 5.0 V \pm 10\%$                                 |     |      |      |    |

| I <sub>AVG_EBI</sub>  |                           | $C_{DRV} = 10 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |     |      | 9    | mA |

|                       | bus output pins (per pad) | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

|                       |                           | $C_{DRV} = 20 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |     | _    | 18   |    |

|                       |                           | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

|                       |                           | $C_{DRV} = 30 \text{ pF}, \text{ f}_{EBI} = 66 \text{ MHz}$ |     | _    | 30   |    |

|                       |                           | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

Table 11. I/O consumption

# 3.7 Oscillator and PLL electrical specifications

The on-chip dual PLL—consisting of the peripheral clock and reference PLL (PLL0) and the frequency-modulated system PLL (PLL1)—generates the system and auxiliary clocks from the main oscillator driver.

| Symbol                  | Parameter                                      | Conditions                                  |       | Unit |                  |     |

|-------------------------|------------------------------------------------|---------------------------------------------|-------|------|------------------|-----|

| Symbol                  | Farameter                                      | Conditions                                  | Min   | Тур  | Max              |     |

| f <sub>PLL1IN</sub>     | PLL1 input clock <sup>1</sup>                  | —                                           | 38    | _    | 78               | MHz |

| Δ <sub>PLL1IN</sub>     | PLL1 input clock duty cycle <sup>1</sup>       | —                                           | 35    | —    | 65               | %   |

| f <sub>PLL1VCO</sub>    | PLL1 VCO frequency                             | —                                           | 600   | _    | 1250             | MHz |

| f <sub>PLL1PHI</sub>    | PLL1 output clock PHI                          | —                                           | 4.762 | —    | 264              | MHz |

| t <sub>PLL1LOCK</sub>   | PLL1 lock time                                 | —                                           | —     | —    | 100              | μs  |

| Δ <sub>PLL1PHISPJ</sub> | PLL1_PHI single period peak-to-<br>peak jitter | f <sub>PLL1PHI</sub> = 200 MHz, 6-<br>sigma |       | _    | 500 <sup>2</sup> | ps  |

| f <sub>PLL1MOD</sub>    | PLL1 modulation frequency                      | —                                           | —     | _    | 250              | kHz |

| δ <sub>PLL1MOD</sub>    | PLL1 modulation depth (when                    | Center spread                               | 0.25  | _    | 2                | %   |

|                         | enabled)                                       | Down spread                                 | 0.5   | —    | 4                | %   |

| I <sub>PLL1</sub>       | PLL1 consumption                               | FINE LOCK state                             | —     | —    | 6                | mA  |

Table 13. PLL1 electrical characteristics

1. PLL1IN clock retrieved directly from either internal PLL0 or external XOSC clock. Input characteristics are granted when using internal PLL0 or external oscillator in functional mode.

2. Noise on the V<sub>DD</sub> supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the V<sub>DD</sub> supply with frequency content in the range of 40 kHz – 50 MHz must be filtered externally to the device.

# 3.7.2 Oscillator electrical specifications

### NOTE

All oscillator specifications in Table 14 are valid for  $V_{DDEH6} = 3.0 \text{ V}$  to 5.5 V.

### Table 14. External oscillator (XOSC) electrical specifications

| Symbol               | Parameter                                                 | Conditions                                   | Va                     | alue                   | Unit |

|----------------------|-----------------------------------------------------------|----------------------------------------------|------------------------|------------------------|------|

| Symbol               | Farameter                                                 | Conditions                                   | Min                    | Мах                    |      |

| f <sub>XTAL</sub>    | Crystal frequency range                                   | —                                            | 8                      | 40                     | MHz  |

| t <sub>cst</sub>     | Crystal start-up time <sup>1, 2</sup>                     | T <sub>J</sub> = 150 °C                      | —                      | 5                      | ms   |

| t <sub>rec</sub>     | Crystal recovery time <sup>3</sup>                        | —                                            | —                      | 0.5                    | ms   |

| VIHEXT               | EXTAL input high voltage (external reference)             | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | V <sub>REF</sub> + 0.6 | _                      | V    |

| V <sub>ILEXT</sub>   | EXTAL input low voltage (external reference)              | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | —                      | V <sub>REF</sub> – 0.6 | V    |

| C <sub>S_EXTAL</sub> | Total on-chip stray capacitance on EXTAL pin <sup>4</sup> | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

|                      |                                                           | 516-ball MAPBGA                              | 2.1                    | 2.8                    |      |

| C <sub>S_XTAL</sub>  | Total on-chip stray capacitance on XTAL pin <sup>4</sup>  | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

|                      |                                                           | 516-ball MAPBGA                              | 2.2                    | 2.9                    |      |

| 9 <sub>m</sub>       | Oscillator transconductance <sup>5</sup>                  | Low                                          | 3                      | 10                     | mA/V |

|                      |                                                           | Medium                                       | 10                     | 27                     | 1    |

|                      |                                                           | High                                         | 12                     | 35                     |      |

Table continues on the next page ...

### 3.8.1 Enhanced Queued Analog-to-Digital Converter (eQADC) Table 17. eQADC conversion specifications (operating)

| Cumb al            | Devenueter                                                   | Va               | lue             | 11                   |  |

|--------------------|--------------------------------------------------------------|------------------|-----------------|----------------------|--|

| Symbol             | Parameter                                                    | Min              | Max             | - Unit               |  |

| f <sub>ADCLK</sub> | ADC Clock (ADCLK) Frequency                                  | 2                | 33              | MHz                  |  |

| CC                 | Conversion Cycles                                            | 2 + 13           | 128 + 15        | ADCLK cycles         |  |

| T <sub>SR</sub>    | Stop Mode Recovery Time <sup>1</sup>                         | 10               | _               | μs                   |  |

| _                  | Resolution <sup>2</sup>                                      | 1.25             | _               | mV                   |  |

| INL                | INL: 16.5 MHz eQADC clock <sup>3</sup>                       | -4               | 4               | LSB <sup>4</sup>     |  |

|                    | INL: 33 MHz eQADC clock <sup>3</sup>                         | -6               | 6               | LSB                  |  |

| DNL                | DNL: 16.5 MHz eQADC clock <sup>3</sup>                       | -3               | 3               | LSB                  |  |

|                    | DNL: 33 MHz eQADC clock <sup>3</sup>                         | -3               | 3               | LSB                  |  |

| OFFNC              | Offset Error without Calibration                             | 0                | 140             | LSB                  |  |

| OFFWC              | Offset Error with Calibration                                | -8               | 8               | LSB                  |  |

| GAINNC             | Full Scale Gain Error without Calibration                    | -150             | 0               | LSB                  |  |

| GAINWC             | Full Scale Gain Error with Calibration                       | -8               | 8               | LSB                  |  |

| I <sub>INJ</sub>   | Disruptive Input Injection Current <sup>5, 6, 7, 8</sup>     | -3               | 3               | mA                   |  |

| E <sub>INJ</sub>   | Incremental Error due to injection current <sup>9, 10</sup>  | —                | +4              | Counts               |  |

| TUE                | TUE value <sup>11, 12</sup> (with calibration)               | _                | ±8              | Counts               |  |

| GAINVGA1           | Variable gain amplifier accuracy (gain = 1) <sup>13</sup>    | -                | -               | Counts <sup>15</sup> |  |

|                    | INL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

| GAINVGA2           | Variable gain amplifier accuracy (gain = 2) <sup>13</sup>    | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -5               | 5               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3               | 3               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3               | 3               |                      |  |

| GAINVGA4           | Variable gain amplifier accuracy (gain = $4$ ) <sup>13</sup> | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -7               | 7               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -4               | 4               |                      |  |

|                    | Current consumption per ADC (two ADCs per EQADC)             |                  | 10              | mA                   |  |

|                    | Reference voltage current consumption per EQADC              |                  | 200             |                      |  |

| I <sub>ADR</sub>   |                                                              |                  | 200             | μΑ                   |  |

1. Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

At V<sub>RH\_EQ</sub> – V<sub>RL\_EQ</sub> = 5.12 V, one count = 1.25 mV without using pregain. Based on 12-bit conversion result; does not account for AC and DC errors

- 3. INL and DNL are tested from V<sub>RL</sub> + 50 LSB to V<sub>RH</sub> 50 LSB.

- 4. At  $V_{RH_{EQ}} V_{RL_{EQ}} = 5.12 \text{ V}$ , one LSB = 1.25 mV.

| Cumbal                   | Devenueter                                    | Canditiana                          |     | Value |     | Unit |

|--------------------------|-----------------------------------------------|-------------------------------------|-----|-------|-----|------|

| Symbol                   | Parameter                                     | Conditions                          | Min | Тур   | Max |      |

| SINAD <sub>DIFF333</sub> | Signal to noise and                           | Gain = 1                            | 66  | _     |     | dBFS |

|                          | distortion ratio in<br>differential mode, 333 | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          | Ksps output rate                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                          |                                               | Gain = 2                            | 66  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                          |                                               | Gain = 4                            | 63  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                          |                                               | Gain = 8                            | 62  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_SD} = V_{DDA_SD}$            |     |       |     |      |

|                          |                                               | Gain = 16                           | 59  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

| SINAD <sub>SE150</sub>   | Signal to noise and                           | Gain = 1                            | 66  | _     | _   | dBFS |

|                          | distortion ratio in single-ended mode,        | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          | 150 Ksps output rate                          | $V_{RH\_SD} = V_{DDA\_SD}$          |     |       |     |      |

|                          |                                               | Gain = 2                            | 66  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_SD} = V_{DDA_SD}$            |     |       |     |      |

|                          |                                               | Gain = 4                            | 63  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_SD} = V_{DDA_SD}$            |     |       |     |      |

|                          |                                               | Gain = 8                            | 62  | -     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                          |                                               | Gain = 16                           | 54  | _     | _   |      |

|                          |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                          |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

### Table 18. SDADC electrical specifications (continued)

Table continues on the next page...

**Electrical characteristics**

# 3.10.1 LFAST interface timing diagrams

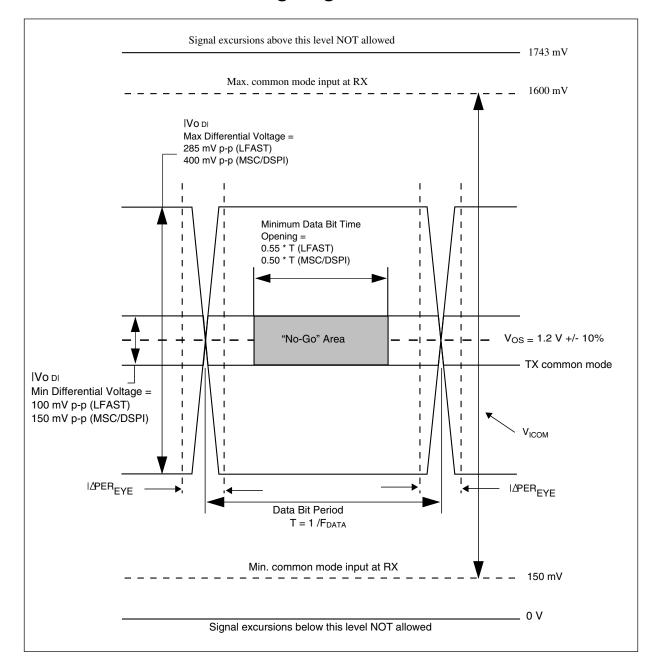

Figure 8. LFAST and MSC/DSPI LVDS timing definition

#### Table 20. LVDS pad startup and receiver electrical characteristics<sup>1</sup> (continued)

| Symbol                                                                                                          | Parameter                                                         | Conditions                                 |                   | Value |                   | Unit |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------|-------------------|-------|-------------------|------|

| Symbol                                                                                                          | Falameter                                                         | Conditions                                 | Min               | Тур   | Max               |      |

| t <sub>PD2NM_TX</sub>                                                                                           | Transmitter startup time (power down to Normal mode) <sup>5</sup> | —                                          | -                 | 0.4   | 2.75              | μs   |

| t <sub>SM2NM_TX</sub>                                                                                           | Transmitter startup time (Sleep mode to Normal mode) <sup>6</sup> | Not applicable to the MSC/DSPI<br>LVDS pad | -                 | 0.2   | 0.5               | μs   |

| t <sub>PD2NM_RX</sub>                                                                                           | Receiver startup time (power down to Normal mode) <sup>7</sup>    | —                                          | -                 | 20    | 40                | ns   |

| t <sub>PD2SM_RX</sub> Receiver startup time (power down to Sleep mode) <sup>8</sup> Not applicable to the MSC/E |                                                                   | Not applicable to the MSC/DSPI<br>LVDS pad | -                 | 20    | 50                | ns   |

| I <sub>LVDS_BIAS</sub>                                                                                          | LVDS bias current consumption                                     | Tx or Rx enabled                           | _                 | _     | 0.95              | mA   |

|                                                                                                                 | TRANSMISSION LINE                                                 | CHARACTERISTICS (PCB Track)                |                   |       |                   |      |

| Z <sub>0</sub>                                                                                                  | Transmission line characteristic impedance                        | —                                          | 47.5              | 50    | 52.5              | Ω    |

| Z <sub>DIFF</sub>                                                                                               | Transmission line differential impedance                          | —                                          | 95                | 100   | 105               | Ω    |

|                                                                                                                 |                                                                   | RECEIVER                                   | •                 |       | •                 |      |

| V <sub>ICOM</sub>                                                                                               | Common mode voltage                                               | —                                          | 0.15 <sup>9</sup> | _     | 1.6 <sup>10</sup> | V    |

| ΔVII                                                                                                            | Differential input voltage                                        | —                                          | 100               | —     | _                 | mV   |

| V <sub>HYS</sub>                                                                                                | Input hysteresis                                                  | —                                          | 25                | —     | _                 | mV   |

| R <sub>IN</sub>                                                                                                 | Terminating resistance                                            | V <sub>DDEH</sub> = 3.0 V to 5.5 V         | 80                | 125   | 150               | Ω    |

| C <sub>IN</sub>                                                                                                 | Differential input capacitance <sup>11</sup>                      | —                                          | _                 | 3.5   | 6.0               | pF   |

| I <sub>LVDS_RX</sub>                                                                                            | Receiver DC current consumption                                   | Enabled                                    | _                 | _     | 0.5               | mA   |

1. The LVDS pad startup and receiver electrical characteristics in this table apply to both the LFAST and the MSC/DSPI LVDS pad except where noted in the conditions.

- 2. All startup times are defined after a 2 peripheral bridge clock delay from writing to the corresponding enable bit in the LVDS control registers (LCR) of the LFAST and High-Speed Debug modules.

- 3. Startup times are valid for the maximum external loads CL defined in both the LFAST/HSD and MSC/DSPI transmitter electrical characteristic tables.

- 4. Bias startup time is defined as the time taken by the current reference block to reach the settling bias current after being enabled.

- 5. Total transmitter startup time from power down to normal mode is t<sub>STRT\_BIAS</sub> + t<sub>PD2NM\_TX</sub> + 2 peripheral bridge clock periods.

- Total transmitter startup time from sleep mode to normal mode is t<sub>SM2NM\_TX</sub> + 2 peripheral bridge clock periods. Bias block remains enabled in sleep mode.

- Total receiver startup time from power down to normal mode is t<sub>STRT\_BIAS</sub> + t<sub>PD2NM\_RX</sub> + 2 peripheral bridge clock periods.

Total receiver startup time from power down to sleep mode is t<sub>PD2SM\_RX</sub> + 2 peripheral bridge clock periods. Bias block

- remains enabled in sleep mode.

- 9. Absolute min = 0.15 V (285 mV/2) = 0 V

- 10. Absolute max = 1.6 V + (285 mV/2) = 1.743 V

- 11. Total internal capacitance including receiver and termination, co-bonded GPIO pads, and package contributions. For bare die devices, subtract the package value given in Figure 11.

#### Table 21. LFAST transmitter electrical characteristics<sup>1</sup>

| Symbol            | Parameter  | Conditions |     | Unit |     |      |

|-------------------|------------|------------|-----|------|-----|------|

| Symbol            | Falaniciel | Conditions | Min | Тур  | Max |      |

| f <sub>DATA</sub> | Data rate  | —          |     | —    | 240 | Mbps |

Table continues on the next page...

### Table 21. LFAST transmitter electrical characteristics<sup>1</sup> (continued)

| Symphol              | Parameter                                                       | Conditions               | Value |     |      | Unit |

|----------------------|-----------------------------------------------------------------|--------------------------|-------|-----|------|------|

| Symbol Parameter     | Conditions                                                      | Min                      | Тур   | Мах |      |      |

| V <sub>OS</sub>      | Common mode voltage                                             | —                        | 1.08  |     | 1.32 | V    |

| IV <sub>OD</sub> I   | Differential output voltage swing (terminated) <sup>2,3</sup>   | —                        | 110   | 200 | 285  | mV   |

| t <sub>TR</sub>      | Rise/fall time (10% – 90% of swing) <sup>2</sup> , <sup>3</sup> | —                        | 0.26  |     | 1.5  | ns   |

| CL                   | External lumped differential load capacitance <sup>2</sup>      | V <sub>DDE</sub> = 4.5 V | —     | —   | 12.0 | pF   |

|                      |                                                                 | V <sub>DDE</sub> = 3.0 V | _     |     | 8.5  |      |

| I <sub>LVDS_TX</sub> | Transmitter DC current consumption                              | Enabled                  |       | _   | 3.2  | mA   |

1. The LFAST pad electrical characteristics are based on worst-case internal capacitance values shown in Figure 11.

Valid for maximum data rate f<sub>DATA</sub>. Value given is the capacitance on each terminal of the differential pair, as shown in Figure 11.

3. Valid for maximum external load CL.

### Table 22. MSC/DSPI LVDS transmitter electrical characteristics<sup>1</sup>

| Symbol               | Parameter                                                     | Conditions               | Value |     |      | Unit |  |

|----------------------|---------------------------------------------------------------|--------------------------|-------|-----|------|------|--|

| Symbol               | Farameter                                                     | Conditions               | Min   | Тур | Мах  |      |  |

| f <sub>DATA</sub>    | Data rate                                                     | —                        | —     | —   | 80   | Mbps |  |

| V <sub>OS</sub>      | Common mode voltage                                           | —                        | 1.08  | —   | 1.32 | V    |  |

| IV <sub>OD</sub> I   | Differential output voltage swing (terminated) <sup>2,3</sup> | —                        | 150   | 200 | 400  | mV   |  |

| t <sub>TR</sub>      | Rise/Fall time (10%–90% of swing) <sup>2</sup> , <sup>3</sup> | —                        | 0.8   | —   | 4.0  | ns   |  |

| CL                   | External lumped differential load capacitance <sup>2</sup>    | V <sub>DDE</sub> = 4.5 V | _     | —   | 50   | pF   |  |

|                      |                                                               | V <sub>DDE</sub> = 3.0 V | —     | —   | 39   |      |  |

| I <sub>LVDS_TX</sub> | Transmitter DC current consumption                            | Enabled                  | _     | _   | 4.0  | mA   |  |

1. The MSC and DSPI LVDS pad electrical characteristics are based on the application circuit and typical worst-case internal capacitance values given in Figure 11.

Valid for maximum data rate f<sub>DATA</sub>. Value given is the capacitance on each terminal of the differential pair, as shown in Figure 11.

3. Valid for maximum external load C<sub>L</sub>.

### 3.12.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                 | Characteristic                                                | Min    | Typical | Max <sup>1</sup>             | Units<br>2 |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|------------|

| t <sub>ai16kseq</sub>  | Array Integrity time for sequential sequence on 16 KB block.  | -      | _       | 512 x<br>Tperiod x<br>Nread  |            |

| t <sub>ai32kseq</sub>  | Array Integrity time for sequential sequence on 32 KB block.  | _      | _       | 1024 x<br>Tperiod x<br>Nread | _          |

| t <sub>ai64kseq</sub>  | Array Integrity time for sequential sequence on 64 KB block.  | —      | _       | 2048 x<br>Tperiod x<br>Nread | _          |

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | _      | _       | 8192 x<br>Tperiod x<br>Nread | _          |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | _       | 110.7                        | μs         |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | —       | 192.6                        | μs         |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 | —       | 356.5                        | μs         |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 | —       | 1,339.5                      | μs         |

- Array Integrity times need to be calculated and is dependent on system frequency and number of clocks per read. The

equation presented require Tperiod (which is the unit accurate period, thus for 200 MHz, Tperiod would equal 5e-9) and

Nread (which is the number of clocks required for read, including pipeline contribution. Thus for a read setup that requires

6 clocks to read with no pipeline, Nread would equal 6. For a read setup that requires 6 clocks to read, and has the

address pipeline set to 2, Nread would equal 4 (or 6 2).)

- 2. The units for Array Integrity are determined by the period of the system clock. If unit accurate period is used in the equation, the results of the equation are also unit accurate.

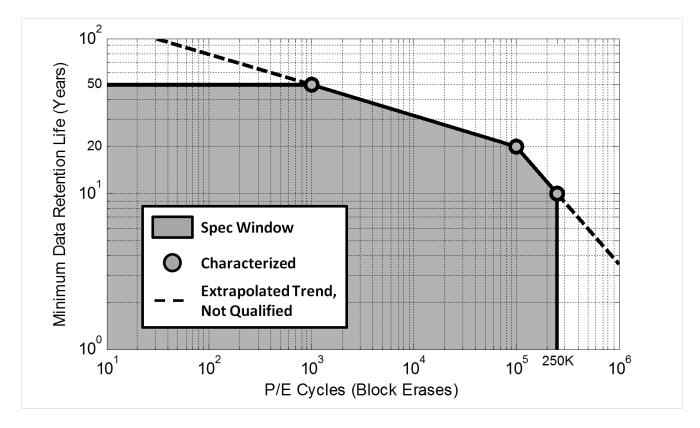

# 3.12.3 Flash memory module life specifications

| Symbol              | Characteristic                                                                              | Conditions                        | Min     | Typical | Units         |

|---------------------|---------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|---------------|

| Array P/E<br>cycles | Number of program/erase cycles per block<br>for 16 KB, 32 KB and 64 KB blocks. <sup>1</sup> | —                                 | 250,000 | -       | P/E<br>cycles |

|                     | Number of program/erase cycles per block for 256 KB blocks. <sup>2</sup>                    | —                                 | 1,000   | 250,000 | P/E<br>cycles |

| Data retention      | Minimum data retention.                                                                     | Blocks with 0 - 1,000 P/E cycles. | 50      | -       | Years         |

|                     |                                                                                             | Blocks with 100,000 P/E cycles.   | 20      | -       | Years         |

|                     |                                                                                             | Blocks with 250,000 P/E cycles.   | 10      | -       | Years         |

Table 32.

Flash memory module life specifications

- 1. Program and erase supported across standard temperature specs.

- 2. Program and erase supported across standard temperature specs.

# 3.12.4 Data retention vs program/erase cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits.

### 3.12.5 Flash memory AC timing specifications Table 33. Flash memory AC timing specifications

| Symbol            | Characteristic                                                                | Min | Typical                                        | Max                                             | Units |

|-------------------|-------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub> | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.          |     | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>esus</sub> | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.          |     | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>res</sub>  | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low. | _   | _                                              | 100                                             | ns    |

Table continues on the next page...

**Electrical characteristics**

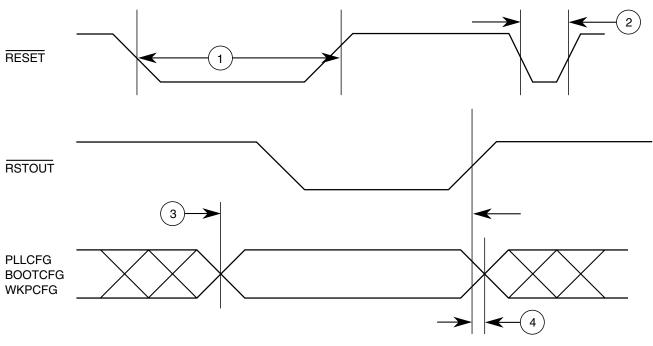

Figure 18. Reset and configuration pin timing

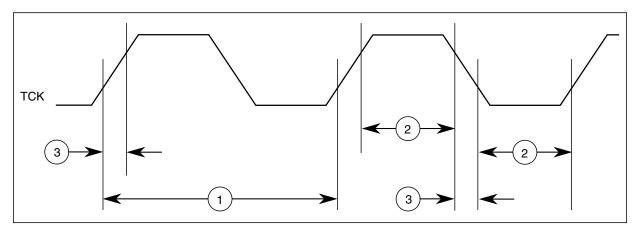

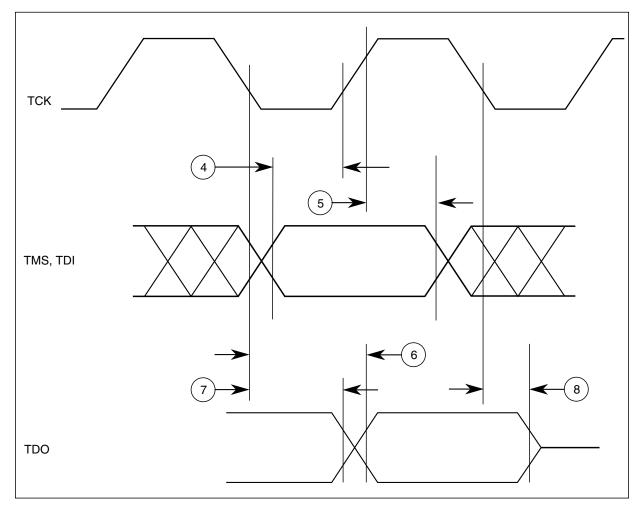

### 3.13.3 IEEE 1149.1 interface timing Table 36. JTAG pin AC electrical characteristics<sup>1</sup>

| #  | Symbol                                | mbol Characteristic                                    | Va  | lue              | Unit |

|----|---------------------------------------|--------------------------------------------------------|-----|------------------|------|

| #  | Symbol                                | Characteristic                                         | Min | Max              | Unit |

| 1  | t <sub>JCYC</sub>                     | TCK cycle time                                         | 100 | —                | ns   |

| 2  | t <sub>JDC</sub>                      | TCK clock pulse width                                  | 40  | 60               | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK rise and fall times (40%–70%)                      | _   | 3                | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI data setup time                               | 5   | —                | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI data hold time                                | 5   | —                | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK low to TDO data valid                              | _   | 16 <sup>2</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK low to TDO data invalid                            | 0   | —                | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK low to TDO high impedance                          | _   | 15               | ns   |

| 9  | t <sub>JCMPPW</sub>                   | JCOMP assertion time                                   | 100 |                  | ns   |

| 10 | t <sub>JCMPS</sub>                    | JCOMP setup time to TCK low                            | 40  | —                | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK falling edge to output valid                       | _   | 600 <sup>3</sup> | ns   |

| 12 | t <sub>BSDVZ</sub>                    | TCK falling edge to output valid out of high impedance | _   | 600              | ns   |

| 13 | t <sub>BSDHZ</sub>                    | TCK falling edge to output high impedance              |     | 600              | ns   |

| 14 | t <sub>BSDST</sub>                    | Boundary scan input valid to TCK rising edge           | 15  | —                | ns   |

| 15 | t <sub>BSDHT</sub>                    | TCK rising edge to boundary scan input invalid         | 15  |                  | ns   |

1. These specifications apply to JTAG boundary scan only. See Table 37 for functional specifications.

- 2. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 3. Applies to all pins, limited by pad slew rate. Refer to I/O delay and transition specification and add 20 ns for JTAG delay.

Figure 19. JTAG test clock input timing

Figure 20. JTAG test access port timing

#### **Electrical characteristics**

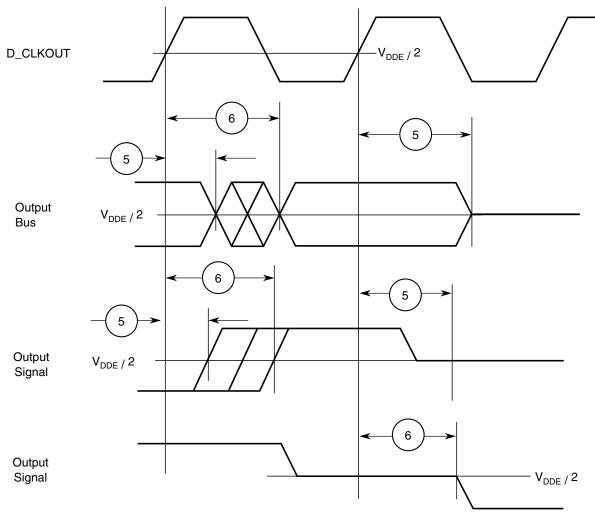

Figure 26. Synchronous output timing

**Electrical characteristics**

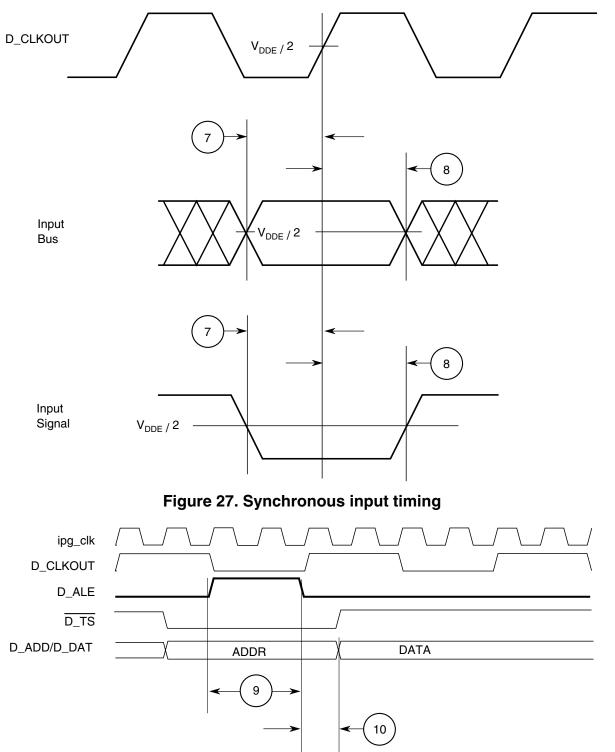

Figure 28. ALE signal timing

# 3.13.9 DSPI timing with CMOS and LVDS pads

### NOTE

The DSPI in TSB mode with LVDS pads can be used to implement the Micro Second Channel (MSC) bus protocol.

DSPI channel frequency support is shown in Table 42. Timing specifications are shown in Table 43, Table 44, Table 45, Table 46, and Table 47.

|                    | DSPI use mode                                           |    |  |

|--------------------|---------------------------------------------------------|----|--|

| CMOS (Master mode) | Full duplex – Classic timing (Table 43)                 | 17 |  |

|                    | Full duplex – Modified timing (Table 44)                | 30 |  |

|                    | Output only mode (SCK/SOUT/PCS) (Table 43 and Table 44) | 30 |  |

|                    | Output only mode TSB mode (SCK/SOUT/PCS) (Table 47)     | 30 |  |

| LVDS (Master mode) | Full duplex – Modified timing (Table 45)                | 30 |  |

|                    | Output only mode TSB mode (SCK/SOUT/PCS) (Table 46)     | 40 |  |

#### Table 42. DSPI channel frequency support

1. Maximum usable frequency can be achieved if used with fastest configuration of the highest drive pads.

2. Maximum usable frequency does not take into account external device propagation delay.

### 3.13.9.1 DSPI master mode full duplex timing with CMOS and LVDS pads

### 3.13.9.1.1 DSPI CMOS Master Mode — Classic Timing

Table 43. DSPI CMOS master classic timing (full duplex and output only) – MTFE = 0, CPHA = 0 or  $1^1$

| # | Symbol           | Characteristic   | Condition              | 2                      | Value                             | alue <sup>3</sup> |      |

|---|------------------|------------------|------------------------|------------------------|-----------------------------------|-------------------|------|

| # | Symbol           | Characteristic   | Pad drive <sup>4</sup> | Load (C <sub>L</sub> ) | Min                               | Max               | Unit |

| 1 | t <sub>SCK</sub> | SCK cycle time   | PCR[SRC]=11b           | 25 pF                  | 33.0                              | —                 | ns   |

|   |                  |                  | PCR[SRC]=10b           | 50 pF                  | 80.0                              |                   |      |

|   |                  |                  | PCR[SRC]=01b           | 50 pF                  | 200.0                             | _                 |      |

| 2 | t <sub>CSC</sub> | PCS to SCK delay | PCR[SRC]=11b           | 25 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 16$ | _                 | ns   |

|   |                  |                  | PCR[SRC]=10b           | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 16$ | _                 |      |

|   |                  |                  | PCR[SRC]=01b           | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 18$ | _                 |      |

|   |                  |                  | PCS: PCR[SRC]=01b      | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 45$ | _                 |      |

|   |                  |                  | SCK: PCR[SRC]=10b      |                        |                                   |                   |      |

Table continues on the next page...

# Table 47. DSPI CMOS master timing – output only – timed serial bus mode TSB = 1 or ITSB = 1, CPOL = 0 or 1, continuous SCK clock 1, 2 (continued)

| #  | Symbol           | Characteristic                  | Condition                | 3                      | Val                     | ue <sup>4</sup>         | Unit |

|----|------------------|---------------------------------|--------------------------|------------------------|-------------------------|-------------------------|------|

| #  | Symbol           | Characteristic                  | Pad drive <sup>5</sup>   | Load (C <sub>L</sub> ) | Min                     | Max                     |      |

| 3  | t <sub>CSH</sub> | PCS hold after SCK <sup>6</sup> | PCR[SRC]=11b             | PCS: 0 pF              | -14                     |                         | ns   |

|    |                  |                                 |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                 | PCR[SRC]=10b             | PCS: 0 pF              | -14                     |                         | ns   |

|    |                  |                                 |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                 | PCR[SRC]=01b             | PCS: 0 pF              | -33                     |                         | ns   |

|    |                  |                                 |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                 | PCS: PCR[SRC]=01b        | PCS: 0 pF              | -35                     |                         | ns   |

|    |                  |                                 | SCK: PCR[SRC]=10b        | SCK: 50 pF             |                         |                         |      |

| 4  | t <sub>SDC</sub> | SCK duty cycle <sup>7</sup>     | PCR[SRC]=11b             | 0 pF                   | 1/2t <sub>SCK</sub> – 2 | 1/2t <sub>SCK</sub> + 2 | ns   |

|    |                  |                                 | PCR[SRC]=10b             | 0 pF                   | 1/2t <sub>SCK</sub> – 2 | 1/2t <sub>SCK</sub> + 2 | ns   |

|    |                  |                                 | PCR[SRC]=01b             | 0 pF                   | 1/2t <sub>SCK</sub> – 5 | 1/2t <sub>SCK</sub> + 5 | ns   |

|    |                  |                                 | SOUT data valid time (af | ter SCK edge)          |                         |                         |      |

| 9  | t <sub>SUO</sub> | SOUT data valid time            | PCR[SRC]=11b             | 25 pF                  |                         | 7.0                     | ns   |

|    |                  | from SCK                        | PCR[SRC]=10b             | 50 pF                  | _                       | 8.0                     | ns   |

|    |                  | CPHA = 1 <sup>8</sup>           | PCR[SRC]=01b             | 50 pF                  |                         | 18.0                    | ns   |

|    |                  |                                 | SOUT data hold time (aft | er SCK edge)           |                         |                         |      |

| 10 | t <sub>HO</sub>  | SOUT data hold time             | PCR[SRC]=11b             | 25 pF                  | -9.0                    |                         | ns   |

|    |                  | after SCK                       | PCR[SRC]=10b             | 50 pF                  | -10.0                   | —                       | ns   |

|    |                  | CPHA = 1 <sup>8</sup>           | PCR[SRC]=01b             | 50 pF                  | -21.0                   |                         | ns   |

1. TSB = 1 or ITSB = 1 automatically selects MTFE = 1 and CPHA = 1.

2. All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

3. When a characteristic involves two signals, the pad drive and load conditions apply to each signal's pad, unless specified otherwise.

- 4. All timing values for output signals in this table are measured to 50% of the output voltage.

- 5. Pad drive is defined as the PCR[SRC] field setting in the SIU. Timing is guaranteed to same drive capabilities for all signals; mixing of pad drives may reduce operating speeds and may cause incorrect operation.

6. With TSB mode or Continuous SCK clock mode selected, PCS and SCK are driven by the same edge of DSPI\_CLKn. This timing value is due to pad delays and signal propagation delays.

- 7. t<sub>SDC</sub> is only valid for even divide ratios. For odd divide ratios the fundamental duty cycle is not 50:50. For these odd divide ratios cases, the absolute spec number is applied as jitter/uncertainty to the nominal high time and low time.

- 8. SOUT Data Valid and Data hold are independent of load capacitance if SCK and SOUT load capacitances are the same value.

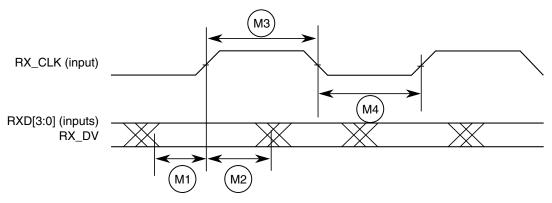

Figure 41. MII receive signal timing diagram

## 3.13.10.2 MII transmit signal timing (TXD[3:0], TX\_EN, and TX\_CLK)

The transmitter functions correctly up to a TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. The system clock frequency must be at least equal to or greater than the TX\_CLK frequency.

The transmit outputs (TXD[3:0], TX\_EN) can be programmed to transition from either the rising or falling edge of TX\_CLK, and the timing is the same in either case. This options allows the use of noncompliant MII PHYs.

Refer to the *MPC5777C Microcontroller Reference Manual's* Fast Ethernet Controller (FEC) chapter for details of this option and how to enable it.

| Symbol | Characteristic                    | Value <sup>2</sup> |     | Unit          |  |

|--------|-----------------------------------|--------------------|-----|---------------|--|

| Symbol |                                   | Min                | Max | Unit          |  |

| M5     | TX_CLK to TXD[3:0], TX_EN invalid | 4.5                | _   | ns            |  |

| M6     | TX_CLK to TXD[3:0], TX_EN valid   | —                  | 25  | ns            |  |

| M7     | TX_CLK pulse width high           | 35%                | 65% | TX_CLK period |  |

| M8     | TX_CLK pulse width low            | 35%                | 65% | TX_CLK period |  |

Table 49. MII transmit signal timing<sup>1</sup>

1. All timing specifications valid to the pad input levels defined in I/O pad specifications.

2. Output parameters are valid for  $C_L = 25 \text{ pF}$ , where  $C_L$  is the external load to the device. The internal package capacitance is accounted for, and does not need to be subtracted from the 25 pF value.

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

As a general rule, the value obtained on a single-layer board is within the normal range for the tightly packed printed circuit board. The value obtained on a board with the internal planes is usually within the normal range if the application board has:

- One oz. (35 micron nominal thickness) internal planes

- Components are well separated

- Overall power dissipation on the board is less than  $0.02 \text{ W/cm}^2$

The thermal performance of any component depends on the power dissipation of the surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_J = T_B + \left( R_{\theta JB} * P_D \right)$$

where:

$T_B$  = board temperature for the package perimeter (°C)

$R_{\Theta JB}$  = junction-to-board thermal resistance (°C/W) per JESD51-8

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air does not factor into the calculation, the junction temperature is predictable if the application board is similar to the thermal test condition, with the component soldered to a board with internal planes.

The thermal resistance is expressed as the sum of a junction-to-case thermal resistance plus a case-to-ambient thermal resistance:

#### **Document revision history**

| Part number <sup>1</sup> | Paakaga description  |                          | Operating temperature <sup>3</sup> |                       |

|--------------------------|----------------------|--------------------------|------------------------------------|-----------------------|

|                          | Package description  | Speed (MHz) <sup>2</sup> | Min (T <sub>L</sub> )              | Max (T <sub>H</sub> ) |

| SPC5777CCK3MME3          | MPC5777C 416 package | 264                      | –40 °C                             | 125 °C                |

|                          | Lead-free (Pb-free)  |                          |                                    |                       |

| SPC5777CK3MME3           | MPC5777C 416 package | 264                      | –40 °C                             | 125 °C                |

|                          | Lead-free (Pb-free)  |                          |                                    |                       |

| SPC5777CCK3MMO3          | MPC5777C 516 package | 264                      | –40 °C                             | 125 °C                |

|                          | Lead-free (Pb-free)  |                          |                                    |                       |

| SPC5777CK3MMO3           | MPC5777C 516 package | 264                      | –40 °C                             | 125 °C                |

|                          | Lead-free (Pb-free)  |                          |                                    |                       |

Table 56.

Example orderable part numbers

1. All packaged devices are PPC5777C, rather than MPC5777C or SPC5777C, until product qualifications are complete. The unpackaged device prefix is PCC, rather than SCC, until product qualification is complete.

Not all configurations are available in the PPC parts.

- 2. For the operating mode frequency of various blocks on the device, see Table 3.

- The lowest ambient operating temperature is referenced by T<sub>L</sub>; the highest ambient operating temperature is referenced by T<sub>H</sub>.

# 6 Document revision history

The following table summarizes revisions to this document since the previous release.

### Table 57. Revision history

| Revision | Date    | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11       | 04/2017 | <ul> <li>In Figure 47 of Ordering information, added codes and firmware version information in definition of "Optional features field"</li> <li>At end of line for (<i>blank</i>), added "version 2.07"</li> <li>Added line for A</li> <li>At end of line for R, added "version 2.08"</li> <li>At end of line for C, added "version 2.07"</li> <li>Added line for D</li> <li>At end of line for L, added "version 2.08"</li> </ul> |