# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z7                                                                  |

| Core Size                  | 32-Bit Tri-Core                                                         |

| Speed                      | 264MHz                                                                  |

| Connectivity               | EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                         |

| Peripherals                | DMA, LVD, POR, Zipwire                                                  |

| Number of I/O              | -                                                                       |

| Program Memory Size        | 8MB (8M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 416-BGA                                                                 |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777crk3mme3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Introd | luction     |                                             |

|---|--------|-------------|---------------------------------------------|

|   | 1.1    | Features    | summary3                                    |

|   | 1.2    | Block dia   | gram4                                       |

| 2 | Pinou  | ıts         | 5                                           |

|   | 2.1    | 416-ball N  | APBGA pin assignments5                      |

|   | 2.2    | 516-ball N  | APBGA pin assignments6                      |

| 3 | Electi | rical chara | cteristics7                                 |

|   | 3.1    | Absolute    | maximum ratings7                            |

|   | 3.2    | Electroma   | agnetic interference (EMI) characteristics9 |

|   | 3.3    | Electrosta  | atic discharge (ESD) characteristics9       |

|   | 3.4    | Operating   | conditions9                                 |

|   | 3.5    | DC electr   | ical specifications12                       |

|   | 3.6    | I/O pad s   | pecifications13                             |

|   |        | 3.6.1       | Input pad specifications13                  |

|   |        | 3.6.2       | Output pad specifications15                 |

|   |        | 3.6.3       | I/O pad current specifications19            |

|   | 3.7    | Oscillator  | and PLL electrical specifications19         |

|   |        | 3.7.1       | PLL electrical specifications20             |

|   |        | 3.7.2       | Oscillator electrical specifications21      |

|   | 3.8    | Analog-to   | -Digital Converter (ADC) electrical         |

|   |        | specificat  | ions23                                      |

|   |        | 3.8.1       | Enhanced Queued Analog-to-Digital           |

|   |        |             | Converter (eQADC)23                         |

|   |        | 3.8.2       | Sigma-Delta ADC (SDADC)25                   |

|   | 3.9    | Temperat    | ure Sensor34                                |

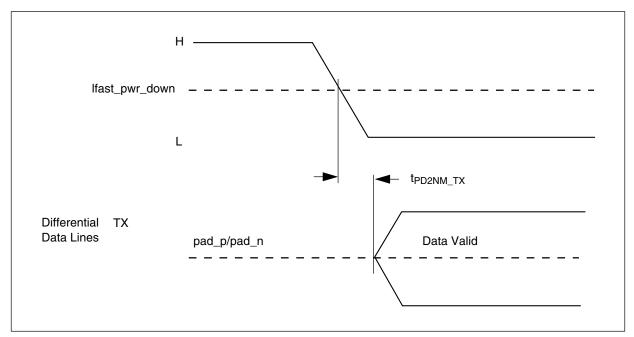

|   | 3.10   | LVDS Fa     | st Asynchronous Serial Transmission (LFAST) |

|   |        | pad elect   | rical characteristics34                     |

|   |        | 3.10.1      | LFAST interface timing diagrams34           |

|   |        | 3.10.2      | LFAST and MSC/DSPI LVDS interface           |

|   |        |             | electrical characteristics                  |

|   |        | 3.10.3      | LFAST PLL electrical characteristics39      |

|   | 3.11   | Power ma    | anagement: PMC, POR/LVD, power              |

|   |        | sequenci    | ng40                                        |

|        | 3.11.1      | Power management electrical characteristics 40 |

|--------|-------------|------------------------------------------------|

|        | 3.11.2      | Power management integration43                 |

|        | 3.11.3      | Device voltage monitoring44                    |

|        | 3.11.4      | Power sequencing requirements46                |

| 3.12   | Flash me    | mory specifications47                          |

|        | 3.12.1      | Flash memory program and erase                 |

|        |             | specifications48                               |

|        | 3.12.2      | Flash memory Array Integrity and Margin        |

|        |             | Read specifications48                          |

|        | 3.12.3      | Flash memory module life specifications49      |

|        | 3.12.4      | Data retention vs program/erase cycles50       |

|        | 3.12.5      | Flash memory AC timing specifications50        |

|        | 3.12.6      | Flash memory read wait-state and address-      |

|        |             | pipeline control settings51                    |

| 3.13   | AC timing   | j52                                            |

|        | 3.13.1      | Generic timing diagrams52                      |

|        | 3.13.2      | Reset and configuration pin timing53           |

|        | 3.13.3      | IEEE 1149.1 interface timing54                 |

|        | 3.13.4      | Nexus timing57                                 |

|        | 3.13.5      | External Bus Interface (EBI) timing59          |

|        | 3.13.6      | External interrupt timing (IRQ/NMI pin)63      |

|        | 3.13.7      | eTPU timing64                                  |

|        | 3.13.8      | eMIOS timing65                                 |

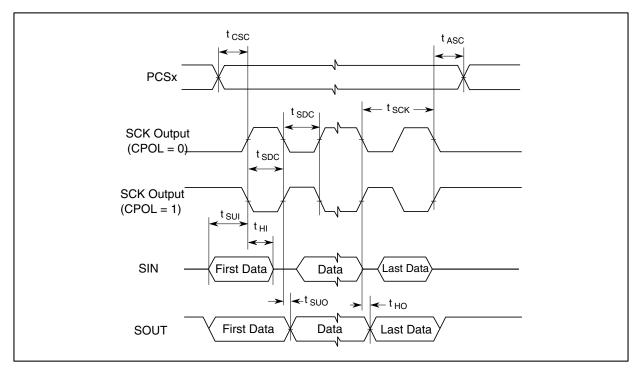

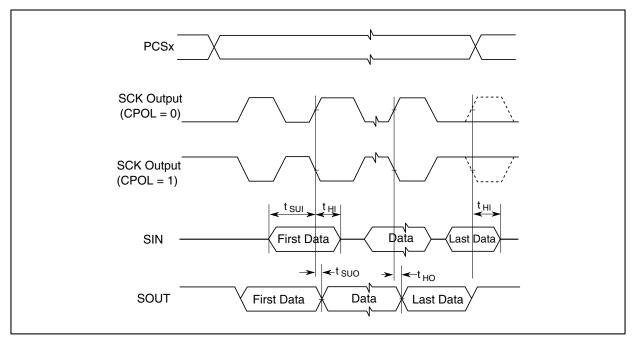

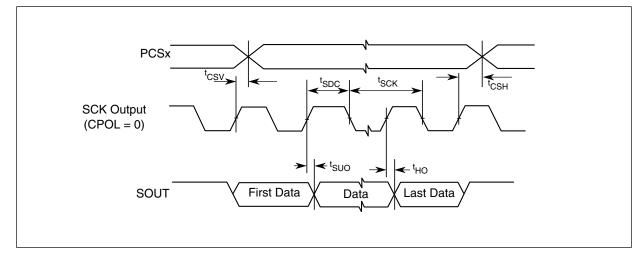

|        | 3.13.9      | DSPI timing with CMOS and LVDS pads66          |

|        | 3.13.10     | FEC timing78                                   |

| 4 Pack | age inform  | nation83                                       |

| 4.1    | Thermal     | characteristics83                              |

|        | 4.1.1       | General notes for thermal characteristics84    |

| 5 Orde | ring inform | nation87                                       |

| 6 Docu | iment revis | sion history88                                 |

#### Introduction

- Enhanced Modular Input/Output System (eMIOS) supporting 32 unified channels with each channel capable of single action, double action, pulse width modulation (PWM) and modulus counter operation

- Two Enhanced Queued Analog-to-Digital Converter (eQADC) modules with:

- Two separate analog converters per eQADC module

- Support for a total of 70 analog input pins, expandable to 182 inputs with offchip multiplexers

- Interface to twelve hardware Decimation Filters

- Enhanced "Tap" command to route any conversion to two separate Decimation Filters

- Four independent 16-bit Sigma-Delta ADCs (SDADCs)

- 10-channel Reaction Module

- Ethernet (FEC)

- Two PSI5 modules

- Two SENT Receiver (SRX) modules supporting 12 channels

- Zipwire: SIPI and LFAST modules

- Five Deserial Serial Peripheral Interface (DSPI) modules

- Five Enhanced Serial Communication Interface (eSCI) modules

- Four Controller Area Network (FlexCAN) modules

- Two M\_CAN modules that support FD

- Fault Collection and Control Unit (FCCU)

- Clock Monitor Units (CMUs)

- Tamper Detection Module (TDM)

- Cryptographic Services Engine (CSE)

- Complies with Secure Hardware Extension (SHE) Functional Specification Version 1.1 security functions

- Includes software selectable enhancement to key usage flag for MAC verification and increase in number of memory slots for security keys

- PASS module to support security features

- Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Device and board test support per Joint Test Action Group (JTAG) IEEE 1149.1 and 1149.7

- On-chip voltage regulator controller (VRC) that derives the core logic supply voltage from the high-voltage supply

- On-chip voltage regulator for flash memory

- Self Test capability

|   | 1       | 2       | 3             | 4             | 5                    | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13     | 14      | 15      | 16          | 17             | 18             | 19            | 20            | 21      | 22      | 23      | 24      | 25      | 26      |

|---|---------|---------|---------------|---------------|----------------------|---------------|-------|-------|----------------|----------------|----------------|----------------|--------|---------|---------|-------------|----------------|----------------|---------------|---------------|---------|---------|---------|---------|---------|---------|

| _ |         | VDD     | RSTOUT        | ANAO_SDA<br>O | ANA4                 | ANA9          | ANA11 | ANA15 | VDDA_SD        | REFBYPCA<br>25 | VRL_SD         | VRH_SD         | AN28   | AN29    | AN36    | VDDA_E<br>Q | REFBYPCB<br>25 | VRL_EQ         | VRH_EQ        | ANB5_SDD<br>5 | ANB9    | ANB12   | ANB18   | ANB21   | VSS     |         |

|   | VDDEH1  | VSS     | VDD           | TEST          | ANA1_SDA<br>1        | ANA5          | ANA10 | ANA14 | VDDA_MISC      | VSSA_SD        | REFBYPCA<br>75 | AN24           | AN27   | AN30    | AN32    | VDDA_E<br>Q | VSSA_EQ        | REFBYPCB<br>75 | ANB4_SDD<br>4 | ANB8          | ANB10   | ANB13   | ANB19   | ANB22   | VSS     | VSS     |

| 1 | ETPUA30 | ETPUA31 | VSS           | VDD           | ANA2_SDA<br>2        | ANA6          | ANA7  | ANA13 | ANA17_SDB<br>1 | ANA19_SD<br>B3 | ANA21_SD<br>C1 | ANA22_SD<br>C2 | AN25   | AN31    | AN34    | AN39        | AN37           | ANBO_SDD<br>O  | ANB7_SDD<br>7 | ANB6_SDD<br>6 | ANB11   | ANB15   | ANB20   | VSS     | ETPUCO  | ETPUC1  |

| 1 | ETPUA27 | ETPUA28 | ETPUA29       | VSS           | VDD                  | ANA3_SDA<br>3 | ANAS  | ANA12 | ANA16_SDB<br>0 | ANA18_SD<br>B2 | ANA20_SD<br>CO | ANA23_SD<br>C3 | AN26   | AN33    | AN35    | AN38        | ANB1_SDD<br>1  | ANB2_SDD<br>2  | ANB3_SDD<br>3 | ANB14         | ANB16   | ANB17   | VSS     | SENT2_A | ETPUC2  | ETPUC3  |

|   | ETPUA23 | ETPUA24 | ETPUA25       | ETPUA26       | VSS                  | VDD           | VSS   | VSS   | VSS            | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            | VSS            | VSS           | ANB23         | VSS     | VSS     | VDDEH7  | ETPUC4  | ETPUC5  | ETPUC6  |

| 1 | ETPUA19 | ETPUA20 | ETPUA21       | ETPUA22       | VSS                  | VDDE8         |       | VDDE8 |                | VDDE8          | VDDE8          |                | VSS    | VSS     |         | VDDE10      | VDDE10         |                | VDDE10        |               | VDDE10  | TCRCLKC | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 |

| 1 | ETPUA11 | ETPUA13 | ETPUA15       | ETPUA17       | ETPUA18              |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | ETPUC15 |

|   | ETPUAS  | ETPUA7  | ETPUA8        | ETPUA3        | ETPUA14              | ETPUA16       |       |       |                |                |                |                |        |         |         |             |                |                |               |               | ETPUC19 | ETPUC16 | ETPUC17 | ETPUC18 | ETPUC20 | ETPUC21 |

|   | ETPUA1  | ETPUA2  | ETPUA9        | ETPUA4        | ETPUA12              |               |       |       |                |                | -              |                | -      | -       |         | -           |                | _              |               |               |         | ETPUC22 | ETPUC23 | ETPUC24 | ETPUC26 | ETPUC27 |

|   | TXDB    | TXDA    | RXDA          | TCRCLKA       | ETPUA6               | ETPUA10       |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | vss         | VSS            |                |               |               | ETPUC25 | ETPUC28 | ETPUC29 | ETPUC30 | ETPUC31 | D_DAT15 |

|   | PLLCFG1 | PLLCFG2 | BOOTCFG1      | BOOTCFGO      | RXDB                 | ETPUAD        |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | vss         | VSS            |                |               |               | NC      | D_DAT14 | D_DAT13 | D_DAT12 | D_DAT11 | D_DAT10 |

| l | NC      | D_BDIP  | PLLCFG0       | VSTBY         | WKPCFG               |               |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               |         | D_DAT9  | D_DAT8  | D_DAT7  | D_DAT5  | VDDEH7  |

|   | D_WEO   | D_WE2   | D_WE3         | VDD           | RESET                | VDDE8         |       |       |                | VDDE2          | VSS            | VSS            | VSS    | vss     | VSS     | vss         | VSS            |                |               |               | VDDE10  | D_DAT6  | VDDEH6  | D_DAT2  | D_DAT3  | D_DAT4  |

|   | D_ADD9  | D_ADD10 | D_ADD11       | VDDEH1        | D_WE1                | NC            |       |       |                | VDDE2          | VDDE2          | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | VDDE10  | ETPUB13 | D_OE    | D_ALE   | D_DATO  | D_DAT1  |

| 1 | D_ADD12 | D_ADD13 | D_ADD14       | D_ADD15       | D_ADD16              |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               |         | ETPUB9  | ETPUB12 | ETPUB14 | ETPUB15 | D_RD_WR |

|   | VDDE2   | D_ADD18 | D_ADD19       | D_ADD20       | D_ADD17              | D_CS3         |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | ETPUB17 | ETPUB3  | ETPUB7  | ETPUB8  | ETPUB10 | ETPUB11 |

|   | D_CS2   | JCOMP   | RDY           | мско          | MSEO1                | MSEO0         |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | ETPUB23 | ETPUB1  | ETPUB2  | ETPUB4  | ETPUB5  | ETPUB6  |

|   | EVTI    | EVTO    | MD00          | MDO2          | MDO3                 |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUB21 | ETPUB22 | ETPUB16 | TCRCLKB | ETPUB0  |

|   | MDO4    | MDO5    | MDO6          | VDDE2         | MDO8                 | MDO1          |       |       |                |                |                |                |        |         |         |             |                |                |               |               | ETPUB25 | ETPUB29 | REGSEL  | ETPUB20 | ETPUB19 | ETPUB18 |

|   | MDO7    | MDO9    | MDO10         | MDO11         | MDO12                |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUB31 | ETPUB26 | ETPUB27 | ETPUB24 | REGCTL  |

|   | MDO13   | MDO14   | MDO15         | NC            | VDDE8                | VSS           |       | PCSA5 |                | SOUTB          | NC             |                | VDDE9  | NC      |         | EMIOS23     | EMIOS31        |                | CNRXB         |               | VSS     | VDDE10  | VDDPMC  | ETPUB28 | VDDPWR  | VSSSYN  |

|   | TDO     | тск     | TMS           | VDD           | VSS                  | VDDE9         | VDDE9 | SCKA  | SINB           | D_CS1          | D_ADD21        | D_ADD29        | EMIOS1 | EMIOS11 | EMIOS17 | EMIOS19     | EMIOS29        | VDDE9          | VDDE9         | VDDE9         | VDDE9   | VSS     | VDD     | ETPUB30 | VSSPWR  | EXTAL   |

|   | VDDE2   | TDI     | VDD           | VSS           | FEC_TXCLK<br>_REFCLK | PCSA1         | SOUTA | SCKB  | PCSB3          | VDDEH3         | VDDEH4         | VDD            | EMIOSO | EMIOS8  | EMIOS13 | EMIOS22     | EMIOS24        | EMIOS28        | CNTXB         | CNRXD         | VDDEH5  | PCSC1   | VSSPMC  | VDD     | VDDEH6  | XTAL    |

|   | ENGCLK  | VDD     | VSS           | FEC_TXD0      | FEC_TXD1             | PCSAD         | PCSA3 | PCSB2 | D_CSO          | D_ADD22        | D_ADD25        | D_ADD28        | EMIOS2 | EMIOS7  | EMIOS12 | EMIOS16     | EMIOS18        | EMIOS27        | CNRXA         | CNTXD         | SCKC    | RXDC    | PCSC3   | VSS     | VDD     | VDDFLA  |

|   | VDD     | VSS     | FEC_RX_D<br>V | FEC_TX_EN     | PCSA4                | PCSB5         | SINA  | PCSB1 | D_TS           | D_ADD23        | D_ADD26        | D_ADD30        | EMIOS3 | EMIOS6  | EMIOS10 | EMIOS15     | EMIOS21        | EMIOS26        | CNTXA         | CNRXC         | PCSCO   | SINC    | PCSC2   | PCSC5   | VSS     | VDD     |

|   |         | VDDE2A  | FEC_RXD0      | FEC_RXD1      | VDDEH3A              | PCSA2         | PCSB4 | PCSBO | D_TA           | D_ADD24        | D_ADD27        | D_CLKOUT       | EMIOS4 | EMIOS5  | EMIOS9  | EMIOS20     | EMIOS14        | EMIOS25        | EMIOS30       | CNTXC         | SOUTC   | VDDEH4  | TXDC    | PCSC4   | VDDEH5  |         |

|   | 1       | 2       | 3             | 4             | 5                    | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13     | 14      | 15      | 16          | 17             | 18             | 19            | 20            | 21      | 22      | 23      | 24      | 25      | 26      |

Figure 3. MPC5777C 516-ball MAPBGA (full diagram)

The following information includes details about power considerations, DC/AC electrical characteristics, and AC timing specifications.

# 3.1 Absolute maximum ratings

Absolute maximum specifications are stress ratings only. Functional operation at these maxima is not guaranteed.

# CAUTION

Stress beyond listed maxima may affect device reliability or cause permanent damage to the device.

See Operating conditions for functional operation specifications.

**Electrical characteristics**

- 1. I<sub>DD</sub> measured on an application-specific pattern with all cores enabled at full frequency, T<sub>J</sub> = 40°C to 150°C. Flash memory program/erase current on the V<sub>DD</sub> supply not included.

- 2. This value is considering the use of the internal core regulator with the simulation of an external transistor with the minimum value of  $h_{FE}$  of 60.

- 3. This bandgap reference is for EQADC calibration and Temperature Sensors.

# 3.6 I/O pad specifications

Input-only pads

The following table describes the different pad types on the chip.

| Pad type                 | Description                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| General-purpose I/O pads | General-purpose I/O and EBI data bus pads with four selectable output slew rate settings; also called SR pads                    |

| EBI pads                 | Provide necessary speed for fast external memory interfaces on the EBI CLKOUT, address, and control signals; also called FC pads |

| LVDS pads                | Low Voltage Differential Signal interface pads                                                                                   |

Low-input-leakage pads that are associated with the ADC channels

#### Table 5. I/O pad specification descriptions

## NOTE

Each I/O pin on the device supports specific drive configurations. See the signal description table in the device reference manual for the available drive configurations for each I/O pin.

## NOTE

Throughout the I/O pad specifications, the symbol  $V_{DDEx}$  represents all  $V_{DDEx}$  and  $V_{DDEHx}$  segments.

# 3.6.1 Input pad specifications

Table 6 provides input DC electrical characteristics as described in Figure 4.

# 3.8.1 Enhanced Queued Analog-to-Digital Converter (eQADC) Table 17. eQADC conversion specifications (operating)

| Cumb al            | Devenueter                                                   | Va               | lue             | 11                   |  |

|--------------------|--------------------------------------------------------------|------------------|-----------------|----------------------|--|

| Symbol             | Parameter                                                    | Min              | Max             | - Unit               |  |

| f <sub>ADCLK</sub> | ADC Clock (ADCLK) Frequency                                  | 2                | 33              | MHz                  |  |

| CC                 | Conversion Cycles                                            | 2 + 13           | 128 + 15        | ADCLK cycles         |  |

| T <sub>SR</sub>    | Stop Mode Recovery Time <sup>1</sup>                         | 10               | _               | μs                   |  |

| _                  | Resolution <sup>2</sup>                                      | 1.25             | _               | mV                   |  |

| INL                | INL: 16.5 MHz eQADC clock <sup>3</sup>                       | -4               | 4               | LSB <sup>4</sup>     |  |

|                    | INL: 33 MHz eQADC clock <sup>3</sup>                         | -6               | 6               | LSB                  |  |

| DNL                | DNL: 16.5 MHz eQADC clock <sup>3</sup>                       | -3               | 3               | LSB                  |  |

|                    | DNL: 33 MHz eQADC clock <sup>3</sup>                         | -3               | 3               | LSB                  |  |

| OFFNC              | Offset Error without Calibration                             | 0                | 140             | LSB                  |  |

| OFFWC              | Offset Error with Calibration                                | -8               | 8               | LSB                  |  |

| GAINNC             | Full Scale Gain Error without Calibration                    | -150             | 0               | LSB                  |  |

| GAINWC             | Full Scale Gain Error with Calibration                       | -8               | 8               | LSB                  |  |

| I <sub>INJ</sub>   | Disruptive Input Injection Current <sup>5, 6, 7, 8</sup>     | -3               | 3               | mA                   |  |

| E <sub>INJ</sub>   | Incremental Error due to injection current <sup>9, 10</sup>  | —                | +4              | Counts               |  |

| TUE                | TUE value <sup>11, 12</sup> (with calibration)               | _                | ±8              | Counts               |  |

| GAINVGA1           | Variable gain amplifier accuracy (gain = 1) <sup>13</sup>    | -                | -               | Counts <sup>15</sup> |  |

|                    | INL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

| GAINVGA2           | Variable gain amplifier accuracy (gain = 2) <sup>13</sup>    | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -5               | 5               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3               | 3               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3               | 3               |                      |  |

| GAINVGA4           | Variable gain amplifier accuracy (gain = $4$ ) <sup>13</sup> | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -7               | 7               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -4               | 4               |                      |  |

|                    | Current consumption per ADC (two ADCs per EQADC)             |                  | 10              | mA                   |  |

|                    | Reference voltage current consumption per EQADC              |                  | 200             |                      |  |

| I <sub>ADR</sub>   |                                                              |                  | 200             | μΑ                   |  |

1. Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

At V<sub>RH\_EQ</sub> – V<sub>RL\_EQ</sub> = 5.12 V, one count = 1.25 mV without using pregain. Based on 12-bit conversion result; does not account for AC and DC errors

- 3. INL and DNL are tested from V<sub>RL</sub> + 50 LSB to V<sub>RH</sub> 50 LSB.

- 4. At  $V_{RH_{EQ}} V_{RL_{EQ}} = 5.12 \text{ V}$ , one LSB = 1.25 mV.

| Cumhal                 | Devementer                                | Conditions                          |     | Value |     | L Insite |

|------------------------|-------------------------------------------|-------------------------------------|-----|-------|-----|----------|

| Symbol                 | Parameter                                 | Conditions                          | Min | Тур   | Мах | Unit     |

| THD <sub>DIFF150</sub> | Total harmonic                            | Gain = 1                            | 65  | _     | _   | dBFS     |

|                        | distortion in differential mode, 150 Ksps | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        | output rate                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 2                            | 68  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 4                            | 74  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 8                            | 80  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 16                           | 80  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

| THD <sub>DIFF333</sub> | Total harmonic                            | Gain = 1                            | 65  | _     | —   | dBFS     |

|                        | distortion in differential mode, 333 Ksps | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        | output rate                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 2                            | 68  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 4                            | 74  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 8                            | 80  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

|                        |                                           | Gain = 16                           | 80  | _     | _   |          |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Symbol                | Parameter                                         | Conditions                          |      | Value                 |                             |      |  |  |

|-----------------------|---------------------------------------------------|-------------------------------------|------|-----------------------|-----------------------------|------|--|--|

| Symbol                | Farameter                                         | Conditions                          | Min  | Тур                   | Max                         | Unit |  |  |

| THD <sub>SE150</sub>  | Total harmonic                                    | Gain = 1                            | 68   | _                     | —                           | dBFS |  |  |

|                       | distortion in single-<br>ended mode, 150          | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |                       |                             |      |  |  |

|                       | Ksps output rate                                  | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |                       |                             |      |  |  |

|                       |                                                   | Gain = 2                            | 68   |                       | _                           |      |  |  |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |                       |                             |      |  |  |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |                       |                             |      |  |  |

|                       |                                                   | Gain = 4                            | 66   |                       | _                           |      |  |  |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |                       |                             |      |  |  |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |                       |                             |      |  |  |

|                       |                                                   | Gain = 8                            | 68   | _                     |                             |      |  |  |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |                       |                             |      |  |  |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |                       |                             |      |  |  |

|                       |                                                   | Gain = 16                           | 68   | _                     | _                           |      |  |  |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |      |                       |                             |      |  |  |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |      |                       |                             |      |  |  |

| SFDR                  | Spurious free dynamic                             |                                     | 60   | _                     | _                           | dB   |  |  |

|                       | range                                             |                                     |      |                       |                             |      |  |  |

| Z <sub>DIFF</sub>     | Differential input impedance <sup>10, 11</sup>    | GAIN = 1                            | 1000 | 1250                  | 1500                        | kΩ   |  |  |

|                       | Impedance <sup>10</sup> , 11                      | GAIN = 2                            | 600  | 800                   | 1000                        | _    |  |  |

|                       |                                                   | GAIN = 4                            | 300  | 400                   | 500                         |      |  |  |

|                       |                                                   | GAIN = 8                            | 200  | 250                   | 300                         |      |  |  |

|                       |                                                   | GAIN = 16                           | 200  | 250                   | 300                         |      |  |  |

| Z <sub>CM</sub>       | Common Mode input impedance <sup>11, 12</sup>     | GAIN = 1                            | 1400 | 1800                  | 2200                        | kΩ   |  |  |

|                       |                                                   | GAIN = 2                            | 1000 | 1300                  | 1600                        |      |  |  |

|                       |                                                   | GAIN = 4                            | 700  | 950                   | 1150                        |      |  |  |

|                       |                                                   | GAIN = 8                            | 500  | 650                   | 800                         |      |  |  |

|                       |                                                   | GAIN = 16                           | 500  | 650                   | 800                         |      |  |  |

| R <sub>BIAS</sub>     | Bare bias resistance                              | —                                   | 110  | 144                   | 180                         | kΩ   |  |  |

| $\Delta V_{INTCM}$    | Common Mode input reference voltage <sup>13</sup> | _                                   | -12  | —                     | +12                         | %    |  |  |

| V <sub>BIAS</sub>     | Bias voltage                                      | —                                   | _    | V <sub>RH_SD</sub> /2 | _                           | V    |  |  |

| $\delta V_{BIAS}$     | Bias voltage accuracy                             | —                                   | -2.5 | _                     | +2.5                        | %    |  |  |

| CMRR                  | Common mode rejection ratio                       | _                                   | 20   | _                     | —                           | dB   |  |  |

| R <sub>Caaf</sub>     | Anti-aliasing filter                              | External series resistance          |      |                       | 20                          | kΩ   |  |  |

|                       |                                                   | Filter capacitances                 | 220  |                       | _                           | pF   |  |  |

| f <sub>PASSBAND</sub> | Pass band <sup>9</sup>                            | —                                   | 0.01 | _                     | 0.333 * f <sub>ADCD_S</sub> | kHz  |  |  |

| δ <sub>RIPPLE</sub>   | Pass band ripple <sup>14</sup>                    | 0.333 * f <sub>ADCD_S</sub>         | 1    |                       | 1                           | %    |  |  |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page...

| Cumb - I             | Boromotor                                         | Conditions                                               |                              | Value             |                                              |    |  |  |

|----------------------|---------------------------------------------------|----------------------------------------------------------|------------------------------|-------------------|----------------------------------------------|----|--|--|

| Symbol               | Parameter                                         | Conditions                                               | Min                          | Тур               | Max                                          | Un |  |  |

| F <sub>rolloff</sub> | Stop band attenuation                             | [0.5 * f <sub>ADCD_S</sub> , 1.0 * f <sub>ADCD_S</sub> ] | 40                           |                   |                                              | dE |  |  |

|                      |                                                   | [1.0 * f <sub>ADCD_S</sub> , 1.5 * f <sub>ADCD_S</sub> ] | 45                           | _                 | _                                            |    |  |  |

|                      |                                                   | [1.5 * f <sub>ADCD_S</sub> , 2.0 * f <sub>ADCD_S</sub> ] | 50                           |                   |                                              |    |  |  |

|                      |                                                   | [2.0 * f <sub>ADCD_S</sub> , 2.5 * f <sub>ADCD_S</sub> ] | 55                           |                   |                                              |    |  |  |

|                      |                                                   | [2.5 * f <sub>ADCD_S</sub> , f <sub>ADCD_M</sub> /2]     | 60                           |                   |                                              |    |  |  |

| δ <sub>GROUP</sub>   | Group delay                                       | Within pass band: Tclk is $f_{ADCD_M} / 2$               | —                            |                   |                                              | _  |  |  |

|                      |                                                   | OSR = 24                                                 | —                            |                   | 235.5                                        | Tc |  |  |

|                      |                                                   | OSR = 28                                                 | —                            | _                 | 275                                          |    |  |  |

|                      |                                                   | OSR = 32                                                 | —                            |                   | 314.5                                        | -  |  |  |

|                      |                                                   | OSR = 36                                                 | —                            |                   | 354                                          |    |  |  |

|                      |                                                   | OSR = 40                                                 | —                            | _                 | 393.5                                        |    |  |  |

|                      |                                                   | OSR = 44                                                 | —                            |                   | 433                                          |    |  |  |

|                      |                                                   | OSR = 48                                                 | —                            |                   | 472.5                                        |    |  |  |

|                      |                                                   | OSR = 56                                                 | —                            | _                 | 551.5                                        |    |  |  |

|                      |                                                   | OSR = 64                                                 | —                            |                   | 630.5                                        | -  |  |  |

|                      |                                                   | OSR = 72                                                 | —                            |                   | 709.5                                        |    |  |  |

|                      |                                                   | OSR = 75                                                 | —                            | _                 | 696                                          |    |  |  |

|                      |                                                   | OSR = 80                                                 | —                            |                   | 788.5                                        |    |  |  |

|                      |                                                   | OSR = 88                                                 | —                            | _                 | 867.5                                        |    |  |  |

|                      |                                                   | OSR = 96                                                 | —                            | _                 | 946.5                                        |    |  |  |

|                      |                                                   | OSR = 112                                                | —                            |                   | 1104.5                                       |    |  |  |

|                      |                                                   | OSR = 128                                                | —                            |                   | 1262.5                                       |    |  |  |

|                      |                                                   | OSR = 144                                                | —                            |                   | 1420.5                                       |    |  |  |

|                      |                                                   | OSR = 160                                                | —                            |                   | 1578.5                                       |    |  |  |

|                      |                                                   | OSR = 176                                                | —                            |                   | 1736.5                                       |    |  |  |

|                      |                                                   | OSR = 192                                                | —                            | _                 | 1894.5                                       |    |  |  |

|                      |                                                   | OSR = 224                                                | —                            | _                 | 2210.5                                       |    |  |  |

|                      |                                                   | OSR = 256                                                | —                            | _                 | 2526.5                                       |    |  |  |

|                      |                                                   | Distortion within pass band                              | -0.5/<br>f <sub>ADCD_S</sub> |                   | +0.5/ f <sub>ADCD_S</sub>                    | -  |  |  |

| f <sub>HIGH</sub>    | High pass filter 3 dB frequency                   | Enabled                                                  | -                            | 10e–5*<br>fADCD_S | _                                            | -  |  |  |

| t <sub>STARTUP</sub> | Startup time from power down state                | _                                                        | -                            | —                 | 100                                          | μ  |  |  |

| t <sub>LATENCY</sub> | Latency between input data and converted          | HPF = ON                                                 | -                            |                   | δ <sub>GROUP</sub> +<br>f <sub>ADCD_</sub> s | -  |  |  |

|                      | data when input mux does not change <sup>15</sup> | HPF = OFF                                                | —                            | —                 | δ <sub>GROUP</sub>                           | 1  |  |  |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page...

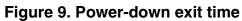

Figure 10. Rise/fall time

# 3.10.2 LFAST and MSC/DSPI LVDS interface electrical characteristics

The following table contains the electrical characteristics for the LFAST interface.

### Table 20. LVDS pad startup and receiver electrical characteristics<sup>1</sup>

| Symbol                              | Parameter                                        | Conditions |     | Unit |     |    |  |  |  |

|-------------------------------------|--------------------------------------------------|------------|-----|------|-----|----|--|--|--|

| Symbol                              | Farameter                                        | Conditions | Min | Тур  | Max |    |  |  |  |

| STARTUP <sup>2</sup> , <sup>3</sup> |                                                  |            |     |      |     |    |  |  |  |

| t <sub>STRT_BIAS</sub>              | Bias current reference startup time <sup>4</sup> | —          | —   | 0.5  | 4   | μs |  |  |  |

Table continues on the next page...

### Table 23. LFAST PLL electrical characteristics<sup>1</sup> (continued)

| Symbol             | Parameter                                     | Conditions                                  |      | Unit    |     |    |

|--------------------|-----------------------------------------------|---------------------------------------------|------|---------|-----|----|

| Symbol             | Falameter                                     | Conditions                                  | Min  | Nominal | Мах |    |

| $\Delta PER_{REF}$ | Input reference clock jitter (peak to peak)   | Single period, f <sub>RF_REF</sub> = 10 MHz | —    | —       | 300 | ps |

|                    |                                               | Long term, f <sub>RF_REF</sub> = 10 MHz     | -500 | —       | 500 |    |

| $\Delta PER_{EYE}$ | Output Eye Jitter (peak to peak) <sup>4</sup> | _                                           | _    | —       | 400 | ps |

1. The specifications in this table apply to both the interprocessor bus and debug LFAST interfaces.

- 2. The 480 MHz frequency is achieved with a 10 MHz or 20 MHz reference clock. With a 13 MHz or 26 MHz reference, the VCO frequency is 468 MHz.

- 3. The time from the PLL enable bit register write to the start of phase locks is maximum 2 clock cycles of the peripheral bridge clock that is connected to the PLL on the device.

- 4. Measured at the transmitter output across a 100 Ohm termination resistor on a device evaluation board. See Figure 11.

# 3.11 Power management: PMC, POR/LVD, power sequencing

# 3.11.1 Power management electrical characteristics

The power management module monitors the different power supplies. It also generates the internal supplies that are required for correct device functionality. The power management is supplied by the  $V_{DDPMC}$  supply.

# 3.11.1.1 LDO mode recommended power transistors

Only specific orderable part numbers of MPC5777C support LDO regulation mode. See Ordering information for MPC5777C parts that support this regulation mode.

The following NPN transistors are recommended for use with the on-chip LDO voltage regulator controller: ON Semiconductor<sup>TM</sup> NJD2873. The collector of the external transistor is preferably connected to the same voltage supply source as the output stage of the regulator.

The following table describes the characteristics of the power transistors.

| Symbol              | Parameter                               | Value  | Unit |

|---------------------|-----------------------------------------|--------|------|

| h <sub>FE</sub>     | DC current gain (Beta)                  | 60-550 | —    |

| PD                  | Absolute minimum power dissipation      | 1.60   | W    |

| I <sub>CMaxDC</sub> | Maximum DC collector current            | 2.0    | А    |

| VCE <sub>SAT</sub>  | Collector to emitter saturation voltage | 300    | mV   |

| V <sub>BE</sub>     | Base to emitter voltage                 | 0.95   | V    |

| V <sub>c</sub>      | Minimum voltage at transistor collector | 2.5    | V    |

Table 24.

Recommended operating characteristics

The following table describes the supply stability capacitances required on the device for proper operation.

| Symbol                    | Parameter                                                                       | Conditions |      |                  | Unit |    |

|---------------------------|---------------------------------------------------------------------------------|------------|------|------------------|------|----|

| Symbol                    | Farameter                                                                       | Conditions | Min  | Тур              | Max  |    |

| C <sub>LV</sub>           | Minimum V <sub>DD</sub> external bulk capacitance <sup>2, 3</sup>               | LDO mode   | 4.7  | _                | —    | μF |

|                           |                                                                                 | SMPS mode  | 22   | _                | _    | μF |

| C <sub>SMPSPWR</sub>      | Minimum SMPS driver supply capacitance                                          | —          | 22   | _                | _    | μF |

| C <sub>HV_PMC</sub>       | Minimum V <sub>DDPMC</sub> external bulk capacitance <sup>4, 5</sup>            | LDO mode   | 22   | _                | —    | μF |

|                           |                                                                                 | SMPS mode  | 22   | _                | —    | μF |

| C <sub>HV_IO</sub>        | Minimum V <sub>DDEx</sub> /V <sub>DDEHx</sub> external capacitance <sup>2</sup> | —          | —    | 4.7 <sup>6</sup> | _    | μF |

| C <sub>HV_FLA</sub>       | Minimum V <sub>DD_FLA</sub> external capacitance <sup>7</sup>                   | —          | 1.0  | 2.0              | _    | μF |

| C <sub>HV_ADC_EQA/B</sub> | Minimum V <sub>DDA_EQA/B</sub> external capacitance <sup>8</sup>                | —          | 0.01 | _                | _    | μF |

| C <sub>REFEQ</sub>        | Minimum REF <sub>BYPCA/B</sub> external capacitance <sup>9</sup>                | -          | 0.01 | _                | _    | μF |

| C <sub>HV_ADC_SD</sub>    | Minimum V <sub>DDA_SD</sub> external capacitance <sup>10</sup>                  | —          | 1.0  | 2.2              |      | μF |

Table 28. Device power supply integration

1. See Figure 14 for capacitor integration.

- 2. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 3. Each V<sub>DD</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 4. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 5. Each V<sub>DDPMC</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 6. The actual capacitance should be selected based on the I/O usage in order to keep the supply voltage within its operating range.

- 7. The recommended flash regulator composition capacitor is 2.0  $\mu$ F typical X7R or X5R, with -50% and +35% as min and max. This puts the min cap at 0.75  $\mu$ F.

- For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_EQA/B</sub> and V<sub>SSA\_EQ</sub>.

- 9. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 µF between REF<sub>BYPCA/B</sub> and V<sub>SS</sub>.

- 10. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_SD</sub> and V<sub>SSA\_SD</sub>.

# 3.11.3 Device voltage monitoring

The LVD/HVDs for the device and their levels are given in the following table. Voltage monitoring threshold definition is provided in the following figure.

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical                                       | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------|

| t <sub>done</sub>    | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.                                                                                                                          | —                                                | _                                             | 5                                                | ns    |

| t <sub>dones</sub>   | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1.                                                                                                                         |                                                  | 16<br>plus four<br>system<br>clock<br>periods | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>drov</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  | _                                             | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP |                                                  | _                                             | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       | _                                                |                                               | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods | -                                             | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

### Table 33. Flash memory AC timing specifications (continued)

# 3.12.6 Flash memory read wait-state and address-pipeline control settings

The following table describes the recommended settings of the Flash Memory Controller's PFCR1[RWSC] and PFCR1[APC] fields at various flash memory operating frequencies, based on specified intrinsic flash memory access times of the C55FMC array at 150°C.

Table 34.

Flash memory read wait-state and address-pipeline control combinations

| Flash memory frequency                           | RWSC | APC | Flash memory read latency on<br>mini-cache miss (# of f <sub>PLATF</sub><br>clock periods) | Flash memory read latency on<br>mini-cache hit (# of f <sub>PLATF</sub> clock<br>periods) |

|--------------------------------------------------|------|-----|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 0 MHz < f <sub>PLATF</sub> ≤ 33 MHz              | 0    | 0   | 3                                                                                          | 1                                                                                         |

| $33 \text{ MHz} < f_{PLATF} \le 100 \text{ MHz}$ | 2    | 1   | 5                                                                                          | 1                                                                                         |

Table continues on the next page...

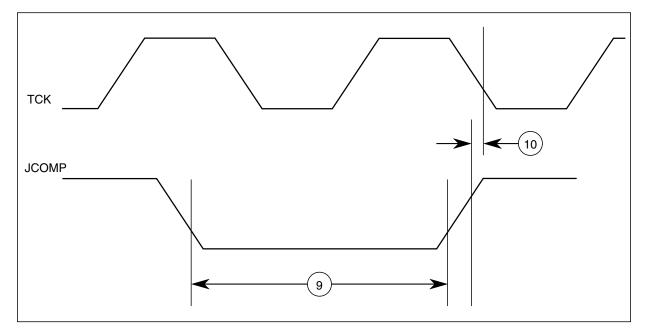

Figure 21. JTAG JCOMP timing

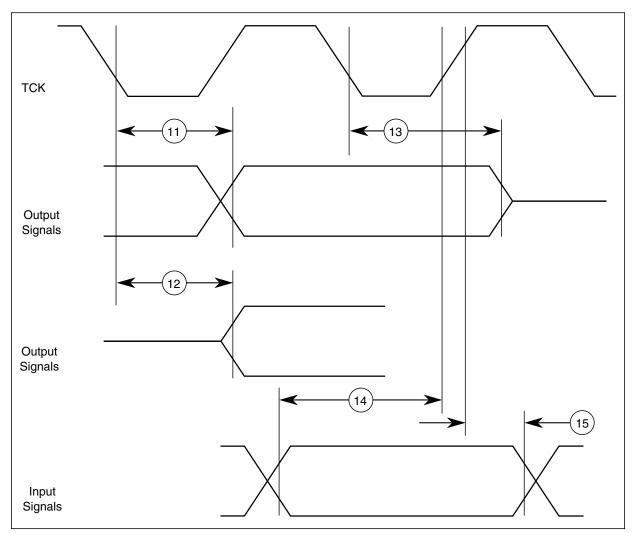

Figure 22. JTAG boundary scan timing

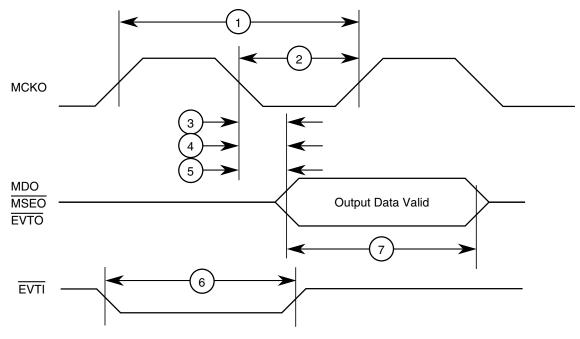

# 3.13.4 Nexus timing

## Table 37. Nexus debug port timing<sup>1</sup>

| Spec | Characteristic                           | Symbol              | Min            | Max | Unit              |

|------|------------------------------------------|---------------------|----------------|-----|-------------------|

| 1    | MCKO Cycle Time                          | t <sub>MCYC</sub>   | 2              | 8   | t <sub>CYC</sub>  |

| 2    | MCKO Duty Cycle                          | t <sub>MDC</sub>    | 40             | 60  | %                 |

| 3    | MCKO Low to MDO Data Valid <sup>2</sup>  | t <sub>MDOV</sub>   | -0.1           | 0.2 | t <sub>MCYC</sub> |

| 4    | MCKO Low to MSEO Data Valid <sup>2</sup> | t <sub>MSEOV</sub>  | -0.1           | 0.2 | t <sub>MCYC</sub> |

| 5    | MCKO Low to EVTO Data Valid <sup>2</sup> | t <sub>EVTOV</sub>  | -0.1           | 0.2 | t <sub>MCYC</sub> |

| 6    | EVTI Pulse Width                         | t <sub>EVTIPW</sub> | 4.0            | —   | t <sub>TCYC</sub> |

| 7    | EVTO Pulse Width                         | t <sub>EVTOPW</sub> | 1              | —   | t <sub>MCYC</sub> |

| 8    | TCK Cycle Time                           | t <sub>TCYC</sub>   | 2 <sup>3</sup> | _   | t <sub>CYC</sub>  |

Table continues on the next page...

### Table 37. Nexus debug port timing<sup>1</sup> (continued)

| Spec | Characteristic                                                               | Symbol                                  | Min             | Max | Unit |

|------|------------------------------------------------------------------------------|-----------------------------------------|-----------------|-----|------|

| 8    | Absolute minimum TCK cycle time <sup>4</sup> (TDO sampled on posedge of TCK) | t <sub>TCYC</sub>                       | 40 <sup>5</sup> | —   | ns   |

|      | Absolute minimum TCK cycle time <sup>4</sup> (TDO sampled on negedge of TCK) |                                         | 20 <sup>5</sup> | _   |      |

| 9    | TCK Duty Cycle                                                               | t <sub>TDC</sub>                        | 40              | 60  | %    |

| 10   | TDI, TMS Data Setup Time <sup>6</sup>                                        | t <sub>NTDIS</sub> , t <sub>NTMSS</sub> | 8               | —   | ns   |

| 11   | TDI, TMS Data Hold Time <sup>6</sup>                                         | T <sub>NTDIH</sub> , t <sub>NTMSH</sub> | 5               | _   | ns   |

| 12   | TCK Low to TDO Data Valid <sup>6</sup>                                       | t <sub>NTDOV</sub>                      | 0               | 18  | ns   |

| 13   | RDY Valid to MCKO <sup>7</sup>                                               | _                                       | —               | —   | —    |

| 14   | TDO hold time after TCLK low <sup>6</sup>                                    | t <sub>NTDOH</sub>                      | 1               | _   | ns   |

1. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDE}$  = 3.0 V to 3.6 V,  $V_{DD33}$  and  $V_{DDSYN}$  = 3.0 V to 3.6 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

- 2. MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. This is a functionally allowable feature. However, it may be limited by the maximum frequency specified by the absolute minimum TCK period specification.

- 4. This value is TDO propagation time plus 2 ns setup time to sampling edge.

- 5. This may require a maximum clock speed that is less than the maximum functional capability of the design depending on the actual system frequency being used.

- 6. Applies to TMS pin timing for the bit frame when using the 1149.7 advanced protocol.

- 7. The RDY pin timing is asynchronous to MCKO. The timing is guaranteed by design to function correctly.

Figure 23. Nexus timings

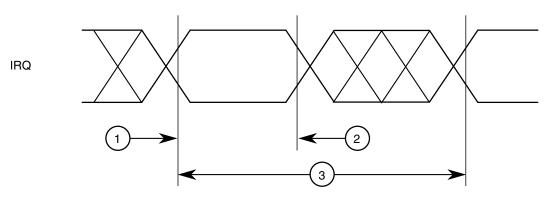

# 3.13.6 External interrupt timing (IRQ/NMI pin) Table 39. External Interrupt timing<sup>1</sup>

| Spec | Characteristic                         | Symbol            | Min | Max | Unit                          |

|------|----------------------------------------|-------------------|-----|-----|-------------------------------|

| 1    | IRQ/NMI Pulse Width Low                | t <sub>IPWL</sub> | 3   | —   | t <sub>cyc</sub> <sup>2</sup> |

| 2    | IRQ/NMI Pulse Width High               | t <sub>IPWH</sub> | 3   | _   | t <sub>cyc</sub> <sup>2</sup> |

| 3    | IRQ/NMI Edge to Edge Time <sup>3</sup> | t <sub>ICYC</sub> | 6   | _   | t <sub>cyc</sub> <sup>2</sup> |

- 1. IRQ/NMI timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ .

- 2. For further information on  $t_{cyc}$ , see Table 3.

- 3. Applies when IRQ/NMI pins are configured for rising edge or falling edge events, but not both.

Figure 29. External interrupt timing

## 3.13.7 eTPU timing Table 40. eTPU timing<sup>1</sup>

| Spec | Characteristic                  | Symbol            | Min            | Max | Unit                               |

|------|---------------------------------|-------------------|----------------|-----|------------------------------------|

| 1    | eTPU Input Channel Pulse Width  | t <sub>ICPW</sub> | 4              | _   | t <sub>CYC_ETPU</sub> <sup>2</sup> |

| 2    | eTPU Output Channel Pulse Width | t <sub>OCPW</sub> | 1 <sup>3</sup> | _   | t <sub>CYC_ETPU</sub> <sup>2</sup> |

1. eTPU timing specified at  $V_{DD}$  = 1.08 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 200 pF with SRC = 0b00.

2. For further information on tCYC ETPU, see Table 3.

3. This specification does not include the rise and fall times. When calculating the minimum eTPU pulse width, include the rise and fall times defined in the slew rate control fields (SRC) of the pad configuration registers (PCR).

# Table 44. DSPI CMOS master modified timing (full duplex and output only) – MTFE = 1, CPHA = 0 or $1^1$ (continued)

| # | Symbol             | Characteristic                 | Condition              | 2                      | Value                                | 3                                    | Unit |

|---|--------------------|--------------------------------|------------------------|------------------------|--------------------------------------|--------------------------------------|------|

| # | Symbol             | Characteristic                 | Pad drive <sup>4</sup> | Load (C <sub>L</sub> ) | Min                                  | Max                                  |      |

| 3 | t <sub>ASC</sub>   | After SCK delay                | PCR[SRC]=11b           | PCS: 0 pF              | $(M^7 \times t_{SYS}^{, 6}) - 35$    |                                      | ns   |

|   |                    |                                |                        | SCK: 50 pF             |                                      |                                      |      |

|   |                    |                                | PCR[SRC]=10b           | PCS: 0 pF              | $(M^7 \times t_{SYS}^{, 6}) - 35$    | _                                    |      |

|   |                    |                                |                        | SCK: 50 pF             |                                      |                                      |      |

|   |                    |                                | PCR[SRC]=01b           | PCS: 0 pF              | $(M^7 \times t_{SYS}^{, 6}) - 35$    |                                      |      |

|   |                    |                                |                        | SCK: 50 pF             |                                      |                                      |      |

|   |                    |                                | PCS: PCR[SRC]=01b      | PCS: 0 pF              | $(M^7 \times t_{SYS}^{, 6}) - 35$    | _                                    |      |

|   |                    |                                | SCK: PCR[SRC]=10b      | SCK: 50 pF             |                                      |                                      |      |

| 4 | t <sub>SDC</sub>   | SCK duty cycle <sup>8</sup>    | PCR[SRC]=11b           | 0 pF                   | 1/2t <sub>SCK</sub> – 2              | 1/2t <sub>SCK</sub> + 2              | ns   |

|   |                    |                                | PCR[SRC]=10b           | 0 pF                   | 1/2t <sub>SCK</sub> – 2              | 1/2t <sub>SCK</sub> + 2              | -    |

|   |                    |                                | PCR[SRC]=01b           | 0 pF                   | 1/2t <sub>SCK</sub> – 5              | 1/2t <sub>SCK</sub> + 5              | -    |

|   |                    |                                | PCS strob              | e timing               |                                      |                                      |      |

| 5 | t <sub>PCSC</sub>  | PCSx to PCSS time <sup>9</sup> | PCR[SRC]=10b           | 25 pF                  | 13.0                                 | —                                    | ns   |

| 6 | t <sub>PASC</sub>  | PCSS to PCSx time <sup>9</sup> | PCR[SRC]=10b           | 25 pF                  | 13.0                                 | _                                    | ns   |

|   |                    |                                | SIN setu               | ıp time                |                                      |                                      |      |

| 7 | t <sub>SUI</sub>   | SIN setup time to              | PCR[SRC]=11b           | 25 pF                  | $29 - (P^{11} \times t_{SYS}, 6)$    | _                                    | ns   |

|   |                    | SCK                            | PCR[SRC]=10b           | 50 pF                  | $31 - (P^{11} \times t_{SYS}, 6)$    | _                                    |      |

|   |                    | $CPHA = 0^{10}$                | PCR[SRC]=01b           | 50 pF                  | $62 - (P^{11} \times t_{SYS}^{, 6})$ | _                                    |      |

|   |                    | SIN setup time to              | PCR[SRC]=11b           | 25 pF                  | 29.0                                 | _                                    | ns   |

|   |                    | SCK                            | PCR[SRC]=10b           | 50 pF                  | 31.0                                 |                                      |      |

|   |                    | CPHA = 1 <sup>10</sup>         | PCR[SRC]=01b           | 50 pF                  | 62.0                                 | _                                    |      |

|   |                    | 4                              | SIN hol                | d time                 | 1                                    |                                      |      |

| 8 | t <sub>HI</sub> 12 | SIN hold time from             | PCR[SRC]=11b           | 0 pF                   | $-1 + (P^{11} \times t_{SYS}^{, 6})$ | —                                    | ns   |

|   |                    | SCK                            | PCR[SRC]=10b           | 0 pF                   | $-1 + (P^{11} \times t_{SYS}^{, 6})$ | _                                    |      |

|   |                    | $CPHA = 0^{10}$                | PCR[SRC]=01b           | 0 pF                   | $-1 + (P^{11} \times t_{SYS}^{, 6})$ |                                      |      |

|   |                    | SIN hold time from             | PCR[SRC]=11b           | 0 pF                   | -1.0                                 | _                                    | ns   |

|   |                    | SCK                            | PCR[SRC]=10b           | 0 pF                   | -1.0                                 | _                                    |      |

|   |                    | CPHA = 1 <sup>10</sup>         | PCR[SRC]=01b           | 0 pF                   | -1.0                                 | _                                    |      |

|   |                    |                                | SOUT data valid tim    | e (after SCK ed        | dge)                                 |                                      |      |

| 9 | t <sub>SUO</sub>   | SOUT data valid                | PCR[SRC]=11b           | 25 pF                  | —                                    | 7.0 + t <sub>SYS</sub> <sup>6</sup>  | ns   |

|   |                    | time from SCK                  | PCR[SRC]=10b           | 50 pF                  | —                                    | 8.0 + t <sub>SYS</sub> <sup>6</sup>  |      |

|   |                    | $CPHA = 0^{13}$                | PCR[SRC]=01b           | 50 pF                  | —                                    | 18.0 + t <sub>SYS</sub> <sup>6</sup> | 1    |

|   |                    | SOUT data valid                | PCR[SRC]=11b           | 25 pF                  | —                                    | 7.0                                  | ns   |

|   |                    | time from SCK                  | PCR[SRC]=10b           | 50 pF                  | —                                    | 8.0                                  | 1    |

|   |                    | CPHA = 1 <sup>13</sup>         | PCR[SRC]=01b           | 50 pF                  | —                                    | 18.0                                 | 1    |

| L |                    |                                | SOUT data hold tim     | e (after SCK ed        | lge)                                 |                                      |      |

Table continues on the next page ...

Figure 38. DSPI LVDS master mode – modified timing, CPHA = 0

Figure 39. DSPI LVDS master mode – modified timing, CPHA = 1

Figure 40. DSPI LVDS and CMOS master timing – output only – modified transfer format MTFE = 1, CHPA = 1

# 3.13.10 FEC timing

# 3.13.10.1 MII receive signal timing (RXD[3:0], RX\_DV, and RX\_CLK)

The receiver functions correctly up to a RX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. The system clock frequency must be at least equal to or greater than the RX\_CLK frequency.

| Symbol | Characteristic                  | Va  | lue | Unit          |

|--------|---------------------------------|-----|-----|---------------|

| Symbol | Characteristic                  | Min | Max | Unit          |

| M1     | RXD[3:0], RX_DV to RX_CLK setup | 5   | _   | ns            |

| M2     | RX_CLK to RXD[3:0], RX_DV hold  | 5   | _   | ns            |

| M3     | RX_CLK pulse width high         | 35% | 65% | RX_CLK period |

| M4     | RX_CLK pulse width low          | 35% | 65% | RX_CLK period |

Table 48. MII receive signal timing<sup>1</sup>

1. All timing specifications valid to the pad input levels defined in I/O pad current specifications.