# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z7                                                                  |

| Core Size                  | 32-Bit Tri-Core                                                         |

| Speed                      | 264MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                 |

| Peripherals                | DMA, LVD, POR, Zipwire                                                  |

| Number of I/O              | -                                                                       |

| Program Memory Size        | 8MB (8M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 416-BGA                                                                 |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777csk3mme3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 1       | 2            | 3               | 4             | 5             | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13      | 14       | 15      | 16          | 17             | 18             | 19            | 20            | 21     | 22     | 23      | 24      | 25      | 26      | _ |

|--------|---------|--------------|-----------------|---------------|---------------|---------------|-------|-------|----------------|----------------|----------------|----------------|---------|----------|---------|-------------|----------------|----------------|---------------|---------------|--------|--------|---------|---------|---------|---------|---|

| A      | VSS     | VDD          | RSTOUT          | ANAO_SDA<br>O | ANA4          | ANAS          | ANA11 | ANA15 | VDDA_SD        | REFBYPCA<br>25 | VRL_SD         | VRH_SD         | AN28    | AN32     | AN36    | VDDA_E<br>Q | REFBYPCB<br>25 | VRL_EQ         | VRH_EQ        | ANB7_SDD<br>7 | ANB11  | ANB14  | ANB17   | ANB21   | ANB23   | VSS     | , |

| в      | VDDEH1  | VSS          | VDD             | TEST          | ANA1_SDA<br>1 | ANA5          | ANA10 | ANA14 | VDDA_MISC      | VSSA_SD        | REFBYPCA<br>75 | AN24           | AN27    | AN29     | AN33    | VDDA_E<br>Q | VSSA_EQ        | REFBYPCB<br>75 | ANB6_SDD<br>6 | ANB8          | ANB10  | ANB15  | ANB18   | ANB22   | VSS     | TCRCLKC |   |

| с      | ETPUA30 | ETPUA31      | VSS             | VDD           | ANA2_SDA<br>2 | ANA6          | ANA9  | ANA13 | ANA17_SDB<br>1 | B3             | C1             | C3             | AN26    | AN30     | AN34    | AN37        | AN38           | ANBO_SDD<br>0  | ANB4_SDD<br>4 | ANB5_SDD<br>5 | ANB12  | ANB16  | ANB19   | VSS     | ETPUCO  | ETPUC1  |   |

| D      | ETPUA27 | ETPUA28      | ETPUA29         | VSS           | VDD           | ANA3_SDA<br>3 | ANA7  | ANA12 | ANA16_SDB<br>0 | ANA18_SD<br>B2 | ANA20_SD<br>CO | ANA22_SD<br>C2 | AN25    | AN31     | AN35    | AN39        | ANB1_SDD<br>1  | ANB2_SDD<br>2  | ANB3_SDD<br>3 | ANB9          | ANB13  | ANB20  | VSS     | SENT2_A | ETPUC2  | ETPUC3  |   |

| E      | ETPUA23 | ETPUA24      | ETPUA25         | ETPUA26       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDDEH7  | ETPUC4  | ETPUCS  | ETPUC6  |   |

|        | ETPUA19 | ETPUA20      | ETPUA21         | ETPUA22       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 |   |

|        | ETPUA15 | ETPUA16      | ETPUA17         | ETPUA18       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 |   |

| •      | ETPUA11 | ETPUA12      | ETPUA14         | ETPUA13       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC15 | ETPUC16 | ETPUC17 | ETPUC18 |   |

|        | ETPUA7  | ETPUA8       | ETPUA9          | ETPUA10       |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUC19 | ETPUC20 | ETPUC21 | ETPUC22 |   |

|        | ETPUA3  | ETPUA4       | ETPUAS          | ETPUA6        |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC23 | ETPUC24 | ETPUC25 | ETPUC26 |   |

|        | TCRCLKA | ETPUAO       | ETPUA1          | ETPUA2        |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC27 | ETPUC28 | ETPUC29 | ETPUC30 |   |

| ۱.     | NC      | TXDA         | RXDA            | VSTBY         |               |               |       |       |                | VSS            | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUC31 | ETPUB15 | ETPUB14 | VDDEH7  |   |

| •      | RXDB    | BOOTCFG<br>1 | WKPCFG          | VDD           |               |               |       |       |                | VDDE2          | VSS            | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | VDDEH6  | ETPUB11 | ETPUB12 | ETPUB13 |   |

| ,<br>- | TXDB    | PLLCFG1      | PLLCFG2         | VDDEH1        |               |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB7  | ETPUB8  | ETPUB9  | ETPUB10 |   |

| ۲      | JCOMP   | RESET        | PLLCFG0         | RDY           |               |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB3  | ETPUB4  | ETPUB5  | ETPUB6  |   |

|        | VDDE2   | мско         | MSEO1           | EVTI          |               |               |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | TCRCLKB | ETPUBO  | ETPUB1  | ETPUB2  |   |

| '      | EVTO    | MSEOO        | MD00            | MDO1          |               |               |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS     | VSS      | VSS     | VSS         | VSS            |                |               |               |        |        | ETPUB19 | ETPUB18 | ETPUB17 |         |   |

| 1      | MDO2    | MDO3         | MDO4            | MDO5          |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUB26 | ETPUB22 | ETPUB21 | ETPUB20 |   |

| ۷      | MDO6    | MDO7         | MD08            | VDDE2         |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | REGSEL  | ETPUB25 | ETPUB24 | ETPUB23 |   |

| -      | MDO9    | MDO10        | MDO11           | MDO15         |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | ETPUB29 | ETPUB28 | ETPUB27 | REGCTL  |   |

| ^      | MDO12   | MDO13        | MDO14           | NC            |               |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDDPMC  | ETPUB30 | VDDPWR  | VSSSYN  |   |

| в      | TDO     | тск          | TMS             | VDD           | FEC_TXCLK     |               |       |       |                |                |                |                |         |          |         |             |                |                |               |               |        |        | VDD     | ETPUB31 | VSSPWR  | EXTAL   |   |

| с      | VDDE2   | TDI          | VDD             | VSS           | REFCLK        | PCSA1         | PCSA2 | PCSB4 | PCSB1          | VDDEH3         | VDDEH4         |                |         | <u> </u> |         |             |                | EMIOS31        | CNRXB         | CNRXD         | VDDEH5 | PCSC1  | VSSPMC  | VDD     | VDDEH6  | XTAL    |   |

| D      | ENGCLK  | VDD          | VSS<br>FEC_RX_D | -             | FEC_TXD1      | PCSA5         | SOUTA | SCKA  | PCSBO          | PCSB3          | EMIOS2         |                |         | <u> </u> |         |             |                | EMIOS30        | CNTXB         | CNTXD         | SCKC   | RXDC   | PCSC3   | VSS     | VDD     | VDDFLA  |   |

| E      | VDD     | VSS          | v               | FEC_TX_EN     |               | PCSAD         | PCSA3 | SCKB  | SINB           | EMIOSO         | EMIOS3         |                |         | <u> </u> |         |             | EMIOS25        | EMIOS29        | CNRXA         | CNRXC         | PCSCO  | SINC   | PCSC2   | PCSC5   | VSS     | VDD     |   |

| F      | VSS     | VDDE2A       | FEC_RXD0        | FEC_RXD1      | VDDEH3A       | PCSB5         | SINA  | PCSB2 | SOUTB          | EMIOS1         | EMIOS4         | EMIOS7         | EMIOS11 | EMIOS12  | EMIÖS16 | EMIOS20     | EMIOS24        | EMIOS28        | CNTXA         | CNTXC         | SOUTC  | VDDEH4 | TXDC    | PCSC4   | VDDEH5  | VSS     | I |

|        | 1       | 2            | 3               | 4             | 5             | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13      | 14       | 15      | 16          | 17             | 18             | 19            | 20            | 21     | 22     | 23      | 24      | 25      | 26      |   |

Figure 2. MPC5777C 416-ball MAPBGA (full diagram)

# 2.2 516-ball MAPBGA pin assignments

Figure 3 shows the 516-ball MAPBGA pin assignments.

|   | 1       | 2       | 3             | 4             | 5                    | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13     | 14      | 15      | 16          | 17             | 18             | 19            | 20            | 21      | 22      | 23      | 24      | 25      | 26      |

|---|---------|---------|---------------|---------------|----------------------|---------------|-------|-------|----------------|----------------|----------------|----------------|--------|---------|---------|-------------|----------------|----------------|---------------|---------------|---------|---------|---------|---------|---------|---------|

| _ |         | VDD     | RSTOUT        | ANAO_SDA<br>O | ANA4                 | ANA9          | ANA11 | ANA15 | VDDA_SD        | REFBYPCA<br>25 | VRL_SD         | VRH_SD         | AN28   | AN29    | AN36    | VDDA_E<br>Q | REFBYPCB<br>25 | VRL_EQ         | VRH_EQ        | ANB5_SDD<br>5 | ANB9    | ANB12   | ANB18   | ANB21   | VSS     |         |

|   | VDDEH1  | VSS     | VDD           | TEST          | ANA1_SDA<br>1        | ANA5          | ANA10 | ANA14 | VDDA_MISC      | VSSA_SD        | REFBYPCA<br>75 | AN24           | AN27   | AN30    | AN32    | VDDA_E<br>Q | VSSA_EQ        | REFBYPCB<br>75 | ANB4_SDD<br>4 | ANB8          | ANB10   | ANB13   | ANB19   | ANB22   | VSS     | VSS     |

| 1 | ETPUA30 | ETPUA31 | VSS           | VDD           | ANA2_SDA<br>2        | ANA6          | ANA7  | ANA13 | ANA17_SDB<br>1 | ANA19_SD<br>B3 | ANA21_SD<br>C1 | ANA22_SD<br>C2 | AN25   | AN31    | AN34    | AN39        | AN37           | ANBO_SDD<br>O  | ANB7_SDD<br>7 | ANB6_SDD<br>6 | ANB11   | ANB15   | ANB20   | VSS     | ETPUCO  | ETPUC1  |

| 1 | ETPUA27 | ETPUA28 | ETPUA29       | VSS           | VDD                  | ANA3_SDA<br>3 | ANAS  | ANA12 | ANA16_SDB<br>0 | ANA18_SD<br>B2 | ANA20_SD<br>CO | ANA23_SD<br>C3 | AN26   | AN33    | AN35    | AN38        | ANB1_SDD<br>1  | ANB2_SDD<br>2  | ANB3_SDD<br>3 | ANB14         | ANB16   | ANB17   | VSS     | SENT2_A | ETPUC2  | ETPUC3  |

|   | ETPUA23 | ETPUA24 | ETPUA25       | ETPUA26       | VSS                  | VDD           | VSS   | VSS   | VSS            | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            | VSS            | VSS           | ANB23         | VSS     | VSS     | VDDEH7  | ETPUC4  | ETPUC5  | ETPUC6  |

| 1 | ETPUA19 | ETPUA20 | ETPUA21       | ETPUA22       | VSS                  | VDDE8         |       | VDDE8 |                | VDDE8          | VDDE8          |                | VSS    | VSS     |         | VDDE10      | VDDE10         |                | VDDE10        |               | VDDE10  | TCRCLKC | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 |

| 1 | ETPUA11 | ETPUA13 | ETPUA15       | ETPUA17       | ETPUA18              |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | ETPUC15 |

|   | ETPUAS  | ETPUA7  | ETPUA8        | ETPUA3        | ETPUA14              | ETPUA16       |       |       |                |                |                |                |        |         |         |             |                |                |               |               | ETPUC19 | ETPUC16 | ETPUC17 | ETPUC18 | ETPUC20 | ETPUC21 |

|   | ETPUA1  | ETPUA2  | ETPUA9        | ETPUA4        | ETPUA12              |               |       |       |                |                | -              |                | -      | -       |         | -           |                | _              |               |               |         | ETPUC22 | ETPUC23 | ETPUC24 | ETPUC26 | ETPUC27 |

|   | TXDB    | TXDA    | RXDA          | TCRCLKA       | ETPUA6               | ETPUA10       |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | vss         | VSS            |                |               |               | ETPUC25 | ETPUC28 | ETPUC29 | ETPUC30 | ETPUC31 | D_DAT15 |

|   | PLLCFG1 | PLLCFG2 | BOOTCFG1      | BOOTCFGO      | RXDB                 | ETPUAD        |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | vss         | VSS            |                |               |               | NC      | D_DAT14 | D_DAT13 | D_DAT12 | D_DAT11 | D_DAT10 |

| l | NC      | D_BDIP  | PLLCFG0       | VSTBY         | WKPCFG               |               |       |       |                | VSS            | VSS            | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               |         | D_DAT9  | D_DAT8  | D_DAT7  | D_DAT5  | VDDEH7  |

|   | D_WE0   | D_WE2   | D_WE3         | VDD           | RESET                | VDDE8         |       |       |                | VDDE2          | VSS            | VSS            | VSS    | vss     | VSS     | vss         | VSS            |                |               |               | VDDE10  | D_DAT6  | VDDEH6  | D_DAT2  | D_DAT3  | D_DAT4  |

|   | D_ADD9  | D_ADD10 | D_ADD11       | VDDEH1        | D_WE1                | NC            |       |       |                | VDDE2          | VDDE2          | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | VDDE10  | ETPUB13 | D_OE    | D_ALE   | D_DATO  | D_DAT1  |

| 1 | D_ADD12 | D_ADD13 | D_ADD14       | D_ADD15       | D_ADD16              |               |       |       |                | VDDE2          | VDDE2          | VSS            | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               |         | ETPUB9  | ETPUB12 | ETPUB14 | ETPUB15 | D_RD_WR |

|   | VDDE2   | D_ADD18 | D_ADD19       | D_ADD20       | D_ADD17              | D_CS3         |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | ETPUB17 | ETPUB3  | ETPUB7  | ETPUB8  | ETPUB10 | ETPUB11 |

|   | D_CS2   | JCOMP   | RDY           | мско          | MSEO1                | MSEO0         |       |       |                | VDDE2          | VDDE2          | VDDE2          | VSS    | VSS     | VSS     | VSS         | VSS            |                |               |               | ETPUB23 | ETPUB1  | ETPUB2  | ETPUB4  | ETPUB5  | ETPUB6  |

|   | EVTI    | EVTO    | MD00          | MDO2          | MDO3                 |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUB21 | ETPUB22 | ETPUB16 | TCRCLKB | ETPUB0  |

|   | MDO4    | MDO5    | MDO6          | VDDE2         | MDO8                 | MD01          |       |       |                |                |                |                |        |         |         |             |                |                |               |               | ETPUB25 | ETPUB29 | REGSEL  | ETPUB20 | ETPUB19 | ETPUB18 |

|   | MDO7    | MDO9    | MDO10         | MDO11         | MDO12                |               |       |       |                |                |                |                |        |         |         |             |                |                |               |               |         | ETPUB31 | ETPUB26 | ETPUB27 | ETPUB24 | REGCTL  |

|   | MDO13   | MDO14   | MDO15         | NC            | VDDE8                | VSS           |       | PCSA5 |                | SOUTB          | NC             |                | VDDE9  | NC      |         | EMIOS23     | EMIOS31        |                | CNRXB         |               | VSS     | VDDE10  | VDDPMC  | ETPUB28 | VDDPWR  | VSSSYN  |

|   | TDO     | тск     | TMS           | VDD           | VSS                  | VDDE9         | VDDE9 | SCKA  | SINB           | D_CS1          | D_ADD21        | D_ADD29        | EMIOS1 | EMIOS11 | EMIOS17 | EMIOS19     | EMIOS29        | VDDE9          | VDDE9         | VDDE9         | VDDE9   | VSS     | VDD     | ETPUB30 | VSSPWR  | EXTAL   |

|   | VDDE2   | TDI     | VDD           | VSS           | FEC_TXCLK<br>_REFCLK | PCSA1         | SOUTA | SCKB  | PCSB3          | VDDEH3         | VDDEH4         | VDD            | EMIOSO | EMIOS8  | EMIOS13 | EMIOS22     | EMIOS24        | EMIOS28        | CNTXB         | CNRXD         | VDDEH5  | PCSC1   | VSSPMC  | VDD     | VDDEH6  | XTAL    |

|   | ENGCLK  | VDD     | VSS           | FEC_TXD0      | FEC_TXD1             | PCSAD         | PCSA3 | PCSB2 | D_CSO          | D_ADD22        | D_ADD25        | D_ADD28        | EMIOS2 | EMIOS7  | EMIOS12 | EMIOS16     | EMIOS18        | EMIOS27        | CNRXA         | CNTXD         | SCKC    | RXDC    | PCSC3   | VSS     | VDD     | VDDFLA  |

|   | VDD     | VSS     | FEC_RX_D<br>V | FEC_TX_EN     | PCSA4                | PCSB5         | SINA  | PCSB1 | D_TS           | D_ADD23        | D_ADD26        | D_ADD30        | EMIOS3 | EMIOS6  | EMIOS10 | EMIOS15     | EMIOS21        | EMIOS26        | CNTXA         | CNRXC         | PCSCO   | SINC    | PCSC2   | PCSC5   | VSS     | VDD     |

|   |         | VDDE2A  | FEC_RXD0      | FEC_RXD1      | VDDEH3A              | PCSA2         | PCSB4 | PCSBO | D_TA           | D_ADD24        | D_ADD27        | D_CLKOUT       | EMIOS4 | EMIOS5  | EMIOS9  | EMIOS20     | EMIOS14        | EMIOS25        | EMIOS30       | CNTXC         | SOUTC   | VDDEH4  | TXDC    | PCSC4   | VDDEH5  |         |

|   | 1       | 2       | 3             | 4             | 5                    | 6             | 7     | 8     | 9              | 10             | 11             | 12             | 13     | 14      | 15      | 16          | 17             | 18             | 19            | 20            | 21      | 22      | 23      | 24      | 25      | 26      |

Figure 3. MPC5777C 516-ball MAPBGA (full diagram)

The following information includes details about power considerations, DC/AC electrical characteristics, and AC timing specifications.

# 3.1 Absolute maximum ratings

Absolute maximum specifications are stress ratings only. Functional operation at these maxima is not guaranteed.

# CAUTION

Stress beyond listed maxima may affect device reliability or cause permanent damage to the device.

See Operating conditions for functional operation specifications.

**Electrical characteristics**

# Table 9. GPIO and EBI data pad output buffer electrical characteristics (SR pads)<sup>1</sup> (continued)

| Symbol           | Parameter                                | Conditions <sup>2</sup>           |                                               |     | Value <sup>3</sup> |      | Unit |

|------------------|------------------------------------------|-----------------------------------|-----------------------------------------------|-----|--------------------|------|------|

| Symbol           |                                          |                                   |                                               | Min | Тур                | Max  |      |

| t <sub>R_F</sub> | GPIO pad output                          | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF                        |     |                    | 1.2  | ns   |

|                  | transition time (rise/fall)              | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 50 pF                        | _   |                    | 2.5  |      |

|                  |                                          |                                   | C <sub>L</sub> = 200 pF                       | _   | _                  | 8    |      |

|                  |                                          | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF                        | _   | —                  | 1.7  |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 50 pF                        | _   | —                  | 3.25 |      |

|                  |                                          |                                   | C <sub>L</sub> = 200 pF                       | _   | —                  | 12   |      |

|                  |                                          | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     | _                  | 5    |      |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   | —                  | 18   | ]    |

|                  |                                          | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     | —                  | 7    |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     | —                  | 25   |      |

|                  |                                          | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        | _   |                    | 13   |      |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   |                    | 24   | 1    |

|                  |                                          |                                   | C <sub>L</sub> = 50 pF                        | _   |                    | 25   |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 30   |      |

|                  |                                          | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        | _   |                    | 24   |      |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 50   |      |

|                  |                                          | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        |     |                    | 40   |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       | _   |                    | 51   |      |

| t <sub>PD</sub>  | GPIO pad output                          |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 6    | ns   |

|                  | propagation delay time                   | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   |                    | 13   |      |

|                  |                                          |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 8.25 |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 19.5 |      |

|                  |                                          | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     |                    | 9    |      |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     | _                  | 22   |      |

|                  |                                          |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 12.5 |      |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     | _                  | 35   |      |

|                  |                                          | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        |     |                    | 27   |      |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 40   |      |

|                  |                                          | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        |     |                    | 45   | 1    |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 65   | 1    |

|                  |                                          | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        |     |                    | 40   | 1    |

|                  |                                          | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 65   | 1    |

|                  |                                          |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 75   | 1    |

|                  |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V |                                               |     |                    | 100  | 1    |

| SKEW_W           | Difference between rise<br>and fall time |                                   | <u>  -                                   </u> | — — |                    | 25   | %    |

1. All GPIO pad output specifications are valid for 3.0 V <  $V_{DDEx}$  < 5.5 V, except where explicitly stated.

- 2. PCR[SRC] values refer to the setting of that register field in the SIU.

- 3. All values to be confirmed during device validation.

The following table shows the EBI CLKOUT, address, and control signal pad electrical characteristics. These pads can also be used for GPIO.

## Table 10. GPIO and EBI CLKOUT, address, and control signal pad output buffer electrical characteristics (FC pads)

| Symbol               | Parameter                                | Conditions <sup>1</sup>                   |                         |                           | Value |      | Un  |

|----------------------|------------------------------------------|-------------------------------------------|-------------------------|---------------------------|-------|------|-----|

| Symbol               | Parameter                                | Conditions                                |                         | Min                       | Тур   | Max  | 7 " |

|                      | EBI Mod                                  | e Output Specification                    | ns: valid for 3.0 V < \ | V <sub>DDEx</sub> < 3.6 V | 1     |      |     |

| C <sub>DRV</sub>     | External bus load                        | PCR[DSC] = 01b                            |                         | _                         |       | 10   | pF  |

|                      | capacitance                              | PCR[DSC] = 10b                            |                         | _                         |       | 20   |     |

|                      |                                          | PCR[DSC] = 11b                            |                         | _                         |       | 30   |     |

| f <sub>MAX_EBI</sub> | External bus maximum operating frequency | C <sub>DRV</sub> = 10/20/30 pF            |                         | -                         | _     | 66   | MH  |

|                      | 4                                        | GPIO and EBI Mode                         | Output Specificatio     | ns                        |       | 1    |     |

| I <sub>OH_EBI</sub>  | GPIO and external bus                    | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[DSC] = 11b          | 30                        |       | _    | m   |

|                      | pad output high current                  | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[DSC] = 10b          | 22                        |       | _    |     |

|                      |                                          |                                           | PCR[DSC] = 01b          | 13                        |       | —    | 1   |

|                      |                                          |                                           | PCR[DSC] = 00b          | 2                         | _     | —    | 1   |

|                      |                                          | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[DSC] = 11b          | 16                        | _     | —    | 1   |

|                      |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[DSC] = 10b          | 12                        |       | _    |     |

|                      |                                          |                                           | PCR[DSC] = 01b          | 7                         |       | _    |     |

|                      |                                          |                                           | PCR[DSC] = 00b          | 1                         |       | _    |     |

| I <sub>OL_EBI</sub>  | GPIO and external bus                    | V <sub>OL</sub> = 0.2 * V <sub>DDEx</sub> | PCR[DSC] = 11b          | 54                        |       | _    | m   |

|                      | pad output low current                   | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[DSC] = 10b          | 25                        |       | _    |     |

|                      |                                          |                                           | PCR[DSC] = 01b          | 16                        |       | _    | 1   |

|                      |                                          |                                           | PCR[DSC] = 00b          | 2                         |       | _    |     |

|                      |                                          | $V_{OL} = 0.2 * V_{DDEx}$                 | PCR[DSC] = 11b          | 17                        |       | _    |     |

|                      |                                          | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[DSC] = 10b          | 14                        | _     | _    |     |

|                      |                                          |                                           | PCR[DSC] = 01b          | 8                         |       | _    |     |

|                      |                                          |                                           | PCR[DSC] = 00b          | 1                         | _     | —    | 1   |

| t <sub>R_F_EBI</sub> | GPIO and external bus                    | PCR[DSC] = 11b                            | C <sub>L</sub> = 30 pF  | —                         | _     | 1.5  | n   |

|                      | pad output transition                    |                                           | C <sub>L</sub> = 50 pF  |                           |       | 2.4  | 1   |

|                      | time (rise/fall)                         | PCR[DSC] = 10b                            | C <sub>L</sub> = 20 pF  |                           | _     | 1.5  | 1   |

|                      |                                          | PCR[DSC] = 01b                            | C <sub>L</sub> = 10 pF  |                           | _     | 1.85 | 1   |

|                      |                                          | PCR[DSC] = 00b                            | C <sub>L</sub> = 50 pF  |                           |       | 45   | 1   |

| t <sub>PD_EBI</sub>  | GPIO and external bus                    | PCR[DSC] = 11b                            | C <sub>L</sub> = 30 pF  |                           |       | 4.2  | n   |

|                      | pad output propagation                   |                                           | C <sub>L</sub> = 50 pF  |                           |       | 5.5  | 1   |

|                      | delay time                               | PCR[DSC] = 10b                            | C <sub>L</sub> = 20 pF  |                           |       | 4.2  | 1   |

|                      |                                          | PCR[DSC] = 01b                            | C <sub>L</sub> = 10 pF  | —                         | _     | 4.4  | 1   |

|                      |                                          | PCR[DSC] = 00b                            | C <sub>L</sub> = 50 pF  |                           |       | 59   | 1   |

| load_cap_sel[4:0] from DCF record | Load capacitance <sup>1, 2</sup> (pF) |

|-----------------------------------|---------------------------------------|

| 01110                             | 14.9                                  |

| 01111                             | 15.8                                  |

Table 15. Selectable load capacitance (continued)

- 1. Values are determined from simulation across process corners and voltage and temperature variation. Capacitance values vary ±12% across process, 0.25% across voltage, and no variation across temperature.

- 2. Values in this table do not include the die and package capacitances given by C<sub>S\_XTAL</sub>/C<sub>S\_EXTAL</sub> in Table 14.

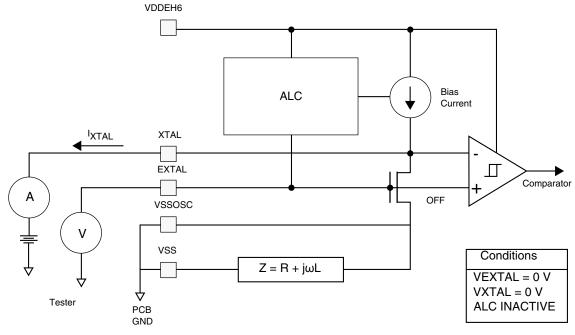

Figure 7. Test circuit

Table 16. Internal RC (IRC) oscillator electrical specifications

| Symbol              | Parameter               | Conditions |     | Value |     | Unit |

|---------------------|-------------------------|------------|-----|-------|-----|------|

| Symbol              | Falantelei              | Conditions | Min | Тур   | Max | Onne |

| f <sub>Target</sub> | IRC target frequency    | _          | _   | 16    |     | MHz  |

| δf <sub>var_T</sub> | IRC frequency variation | T < 150 °C | -8  | _     | 8   | %    |

# 3.8 Analog-to-Digital Converter (ADC) electrical specifications

- 5. Below disruptive current conditions, the channel being stressed has conversion values of \$3FF for analog inputs greater than V<sub>BH</sub> and \$000 for values less than V<sub>BL</sub>. Other channels are not affected by non-disruptive conditions.

- 6. Exceeding limit may cause conversion error on stressed channels and on unstressed channels. Transitions within the limit do not affect device reliability or cause permanent damage.

- Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values using V<sub>POSCLAMP</sub> = V<sub>DDA</sub> + 0.5 V and V<sub>NEGCLAMP</sub> = -0.3 V, then use the larger of the calculated values.

- 8. Condition applies to two adjacent pins at injection limits.

- 9. Performance expected with production silicon.

- 10. All channels have same 10 k $\Omega$  < Rs < 100 k $\Omega$  Channel under test has Rs = 10 k $\Omega$ ,  $I_{INJ}=I_{INJMAX}$ ,  $I_{INJMIN}$ .

- 11. The TUE specification is always less than the sum of the INL, DNL, offset, and gain errors due to cancelling errors.

- 12. TUE does not apply to differential conversions.

- Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed as indicated.

- 14. Guaranteed 10-bit monotonicity.

- 15. At  $V_{RH\_EQ} V_{RL\_EQ}$  = 5.12 V, one LSB = 1.25 mV.

# 3.8.2 Sigma-Delta ADC (SDADC)

The SDADC is a 16-bit Sigma-Delta analog-to-digital converter with a 333 Ksps maximum output conversion rate.

# NOTE

The voltage range is 4.5 V to 5.5 V for SDADC specifications, except where noted otherwise.

| Symbol                  | Parameter                                | Conditions                                                     |     | Value                     | 9                   | Unit |  |

|-------------------------|------------------------------------------|----------------------------------------------------------------|-----|---------------------------|---------------------|------|--|

| Symbol                  | Falameter                                | Conditions                                                     | Min | Тур                       | Мах                 |      |  |

| V <sub>IN</sub>         | ADC input signal                         | —                                                              | 0   | _                         | V <sub>DDA_SD</sub> | V    |  |

| V <sub>IN_PK2PK</sub> 1 | Input range peak to peak                 | Single ended<br>V <sub>INM</sub> = V <sub>RL_SD</sub>          |     | V <sub>RH_SD</sub> /G     | iAIN                | V    |  |

|                         | $V_{IN_{PK2PK}} = V_{INP}^2 - V_{INM}^3$ | Single ended<br>$V_{INM} = 0.5^*V_{RH_{SD}}$<br>GAIN = 1       |     | ±0.5*V <sub>RH</sub>      | I_SD                |      |  |

|                         |                                          | Single ended<br>$V_{INM} = 0.5^* V_{RH_SD}$<br>GAIN = 2,4,8,16 |     | ±V <sub>RH_SD</sub> /GAIN |                     |      |  |

|                         |                                          | Differential<br>0 < V <sub>IN</sub> < V <sub>DDEx</sub>        |     | ±V <sub>RH_SD</sub> /0    | GAIN                |      |  |

| f <sub>ADCD_M</sub>     | SD clock frequency <sup>4</sup>          | —                                                              | 4   | 14.4                      | 16                  | MHz  |  |

| f <sub>ADCD_S</sub>     | Conversion rate                          | —                                                              | —   | _                         | 333                 | Ksps |  |

| _                       | Oversampling ratio                       | Internal modulator                                             | 24  | —                         | 256                 | —    |  |

| RESOLUTION              | SD register resolution <sup>5</sup>      | 2's complement notation                                        |     | 16                        |                     | bit  |  |

## Table 18. SDADC electrical specifications

Table continues on the next page...

| Cumbal              | Devenuetor                                           | Canditions                                                                             |     | Value             |     | L Incia |

|---------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------------------|-----|---------|

| Symbol              | Parameter                                            | Conditions                                                                             | Min | Тур               | Max | Unit    |

| GAIN                | ADC gain                                             | Defined through<br>SDADC_MCR[PGAN]. Only integer<br>powers of 2 are valid gain values. | 1   | —                 | 16  | _       |

| δ <sub>GAIN</sub>   | Absolute value of the ADC gain error <sup>6, 7</sup> | Before calibration (applies to gain setting = 1)                                       | —   | —                 | 1.5 | %       |

|                     |                                                      | After calibration                                                                      | —   | _                 | 5   | mV      |

|                     |                                                      | $\Delta V_{RH\_SD} < 5\%, \Delta V_{DDA\_SD} < 10\%$                                   |     |                   |     |         |

|                     |                                                      | $\Delta T_{\rm J} < 50 \ ^{\circ}{\rm C}$                                              |     |                   |     |         |

|                     |                                                      | After calibration                                                                      | _   | _                 | 7.5 |         |

|                     |                                                      | $\Delta V_{RH_{SD}} < 5\%, \Delta V_{DDA_{SD}} < 10\%$                                 |     |                   |     |         |

|                     |                                                      | $\Delta T_{\rm J} < 100 \ ^{\circ}{\rm C}$                                             |     |                   |     |         |

|                     |                                                      | After calibration                                                                      | _   | _                 | 10  |         |

|                     |                                                      | $\Delta V_{RH_{SD}} < 5\%, \Delta V_{DDA_{SD}} < 10\%$                                 |     |                   |     |         |

|                     |                                                      | $\Delta T_{\rm J} < 150 \ ^{\circ}{\rm C}$                                             |     |                   |     |         |

| V <sub>OFFSET</sub> | Conversion offset <sup>6, 7</sup>                    | Before calibration (applies to all gain settings: 1, 2, 4, 8, 16)                      | —   | 10*(1+1/<br>gain) | 20  | mV      |

|                     |                                                      | After calibration                                                                      | —   | —                 | 5   |         |

|                     |                                                      | $\Delta V_{\text{DDA}\_\text{SD}} < 10\%$                                              |     |                   |     |         |

|                     |                                                      | $\Delta T_{\rm J} < 50 \ ^{\circ}{\rm C}$                                              |     |                   |     |         |

|                     |                                                      | After calibration                                                                      | _   | —                 | 7.5 |         |

|                     |                                                      | $\Delta V_{\text{DDA}\_\text{SD}} < 10\%$                                              |     |                   |     |         |

|                     |                                                      | ΔT <sub>J</sub> < 100 °C                                                               |     |                   |     |         |

|                     |                                                      | After calibration                                                                      | _   | _                 | 10  |         |

|                     |                                                      | $\Delta V_{\text{DDA}\_\text{SD}} < 10\%$                                              |     |                   |     |         |

|                     |                                                      | ΔT <sub>J</sub> < 150 °C                                                               |     |                   |     |         |

| Table 18. SDADC electrical specifications (continued |

|------------------------------------------------------|

|------------------------------------------------------|

Table continues on the next page ...

| Cumhal                   | Devenueter                                 | Conditions                                          |      | Value |     | 11   |

|--------------------------|--------------------------------------------|-----------------------------------------------------|------|-------|-----|------|

| Symbol                   | Parameter                                  | Conditions                                          | Min  | Тур   | Max | Unit |

| SNR <sub>SE150</sub>     | Signal to noise ratio in                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 72   | _     | _   | dB   |

|                          | single ended mode,<br>150 Ksps output rate | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | GAIN = 1                                            |      |       |     |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 69   | _     | _   |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | GAIN = 2                                            |      |       |     |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 66   | _     | _   |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | GAIN = 4                                            |      |       |     |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 62   | _     | _   |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | GAIN = 8                                            |      |       |     |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 54   | —     | _   |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | GAIN = 16                                           |      |       |     |      |

| SINAD <sub>DIFF150</sub> | Signal to noise and                        | Gain = 1                                            | 72   | -     | —   | dBFS |

|                          | distortion ratio in differential mode, 150 | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          | Ksps output rate                           | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | Gain = 2                                            | 72   | -     | —   |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | Gain = 4                                            | 69   | —     | —   |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | Gain = 8                                            | 68.8 | —     | _   |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                            | Gain = 16                                           | 64.8 | —     | _   |      |

|                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                            | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

# Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Cumhal                 | Parameter                                                                     | Conditions                          |     | Value |     |      |  |  |

|------------------------|-------------------------------------------------------------------------------|-------------------------------------|-----|-------|-----|------|--|--|

| Symbol                 |                                                                               | Conditions                          | Min | Тур   | Мах | Unit |  |  |

| THD <sub>DIFF150</sub> | Total harmonic                                                                | Gain = 1                            | 65  | _     | _   | dBFS |  |  |

|                        | distortion in differential mode, 150 Ksps                                     | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        | output rate                                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 2                            | 68  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 4                            | 74  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 8                            | 80  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 16                           | 80  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

| THD <sub>DIFF333</sub> | Total harmonic<br>distortion in differential<br>mode, 333 Ksps<br>output rate | Gain = 1                            | 65  | _     | _   | dBFS |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 2                            | 68  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 4                            | 74  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 8                            | 80  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

|                        |                                                                               | Gain = 16                           | 80  | _     | _   |      |  |  |

|                        |                                                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |  |  |

|                        |                                                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |  |  |

# Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Sympol                                                                                         | Parameter                                       | Conditions                          |   | Valu                                          | e                                                | Unit |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------|---|-----------------------------------------------|--------------------------------------------------|------|--|

| Symbol                                                                                         | Farameter                                       | Min T                               |   | Min Typ Max                                   |                                                  |      |  |

| t <sub>SETTLING</sub>                                                                          | Settling time after mux change                  | Analog inputs are muxed<br>HPF = ON | _ | _                                             | 2*δ <sub>GROUP</sub> +<br>3*f <sub>ADCD_</sub> s | —    |  |

|                                                                                                |                                                 | HPF = OFF                           | — | _                                             | 2∗δ <sub>GROUP</sub> +<br>2*f <sub>ADCD_S</sub>  |      |  |

| t <sub>ODRECOVERY</sub> Overdrive recovery time After input comes within range from saturation |                                                 | _                                   | _ | 2*δ <sub>GROUP</sub> +<br>f <sub>ADCD_S</sub> | —                                                |      |  |

|                                                                                                |                                                 | HPF = ON                            |   |                                               |                                                  |      |  |

| HPF                                                                                            |                                                 | HPF = OFF                           | — | _                                             | 2*δ <sub>GROUP</sub>                             |      |  |

| C <sub>S_D</sub>                                                                               | SDADC sampling                                  | GAIN = 1, 2, 4, 8                   | — | _                                             | 75*GAIN                                          | fF   |  |

|                                                                                                | capacitance after sampling switch <sup>16</sup> | GAIN = 16                           | — | _                                             | 600                                              | fF   |  |

| I <sub>BIAS</sub>                                                                              | Bias consumption                                | At least one SDADC enabled          |   | —                                             | 3.5                                              | mA   |  |

| I <sub>ADV_D</sub>                                                                             | SDADC supply Per SDADC enabled consumption      |                                     | — | —                                             | 4.325                                            | mA   |  |

| I <sub>ADR_D</sub>                                                                             | SDADC reference<br>current consumption          | Per SDADC enabled                   | — | _                                             | 20                                               | μA   |  |

## Table 18. SDADC electrical specifications (continued)

- 1. For input voltage above the maximum and below the clamp voltage of the input pad, there is no latch-up concern, and the signal will only be "clipped."

- 2. VINP is the input voltage applied to the positive terminal of the SDADC

- 3. VINM is the input voltage applied to the negative terminal of the SDADC

- 4. Sampling is generated internally  $f_{SAMPLING} = f_{ADCD_M/2}$

- 5. For Gain = 16, SDADC resolution is 15 bit.

- Calibration of gain is possible when gain = 1. Offset Calibration should be done with respect to 0.5<sup>\*</sup>V<sub>RH\_SD</sub> for differential mode and single ended mode with negative input = 0.5<sup>\*</sup>V<sub>RH\_SD</sub>. Offset Calibration should be done with respect to 0 for single ended mode with negative input = 0. Both Offset and Gain Calibration is guaranteed for +/-5% variation of V<sub>RH\_SD</sub>, +/-10% variation of V<sub>DDA SD</sub>, +/-50 C temperature variation.

- 7. Offset and gain error due to temperature drift can occur in either direction (+/-) for each of the SDADCs on the device.

- SDADC is functional in the range 3.6 V < V<sub>DDA\_SD</sub> < 4.0 V: SNR parameter degrades by 3 dB. SDADC is functional in the range 3.0 V < V<sub>RH\_SD</sub> < 4.0 V: SNR parameter degrades by 9 dB.</li>

- 9. SNR values guaranteed only if external noise on the ADC input pin is attenuated by the required SNR value in the frequency range of f<sub>ADCD\_M</sub> f<sub>ADCD\_S</sub> to f<sub>ADCD\_M</sub> + f<sub>ADCD\_S</sub>, where f<sub>ADCD\_M</sub> is the input sampling frequency and f<sub>ADCD\_S</sub> is the output sample frequency. A proper external input filter should be used to remove any interfering signals in this frequency range.

- 10. Input impedance in differential mode  $Z_{IN} = Z_{DIFF}$

- 11. Input impedance given at  $f_{ADCD_M} = 16$  MHz. Impedance is inversely proportional to SDADC clock frequency.  $Z_{DIFF}$  ( $f_{ADCD_M}$ ) = (16 MHz /  $f_{ADCD_M}$ ) \*  $Z_{DIFF}$ ,  $Z_{CM}$  ( $f_{ADCD_M}$ ) = (16 MHz /  $f_{ADCD_M}$ ) \*  $Z_{CM}$ .

- 12. Input impedance in single-ended mode  $Z_{IN} = (2 * Z_{DIFF} * Z_{CM}) / (Z_{DIFF} + Z_{CM})$

- 13.  $V_{INTCM}$  is the Common Mode input reference voltage for the SDADC. It has a nominal value of ( $V_{RH_SD}$   $V_{RL_SD}$ ) / 2.

- 14. The  $\pm 1\%$  passband ripple specification is equivalent to 20 \* log<sub>10</sub> (0.99) = 0.087 dB.

- 15. Propagation of the information from the pin to the register CDR[CDATA] and the flags SFR[DFEF] and SFR[DFFF] is given by the different modules that must be crossed: delta/sigma filters, high pass filter, FIFO module, and clock domain synchronizers. The time elapsed between data availability at the pin and internal SDADC module registers is given by the following formula, where f<sub>ADCD\_S</sub> is the frequency of the sampling clock, f<sub>ADCD\_M</sub> is the frequency of the modulator, and f<sub>FM\_PER\_CLK</sub> is the frequency of the peripheral bridge clock feeds to the SDADC module:

$REGISTER LATENCY = t_{LATENCY} + 0.5/f_{ADCD_S} + 2 (\sim+1)/f_{ADCD_M} + 2(\sim+1)f_{FM_PER_CLK}$

The (~+1) symbol refers to the number of clock cycles uncertainty (from 0 to 1 clock cycle) to be added due to resynchronization of the signal during clock domain crossing.

## Table 29. Voltage monitor electrical characteristics<sup>1, 2</sup> (continued)

|                         |                                                  |                              | Co       | nfigura            | tion       |      | Value |      |      |  |  |

|-------------------------|--------------------------------------------------|------------------------------|----------|--------------------|------------|------|-------|------|------|--|--|

| Symbol                  | Parameter                                        | Conditions                   |          |                    | Pow.<br>Up | Min  | Тур   | Max  | Unit |  |  |

| POR_HV                  | HV V <sub>DDPMC</sub> supply power               | Rising voltage (powerup)     | N/A      | No                 | Enab.      | 2444 | 2600  | 2756 | mV   |  |  |

|                         | on reset threshold                               | Falling voltage (power down) |          |                    |            | 2424 | 2580  | 2736 |      |  |  |

| LVD_HV                  | HV internal V <sub>DDPMC</sub> supply            | Rising voltage (untrimmed)   | 4bit     | No                 | Enab.      | 2935 | 3023  | 3112 | mV   |  |  |

|                         | low voltage monitoring                           | Falling voltage (untrimmed)  |          |                    |            | 2922 | 3010  | 3099 | 1    |  |  |

|                         |                                                  | Rising voltage (trimmed)     |          |                    |            | 2946 | 3010  | 3066 |      |  |  |

|                         |                                                  | Falling voltage (trimmed)    |          |                    |            | 2934 | 2998  | 3044 | ]    |  |  |

| HVD_HV                  | HV internal V <sub>DDPMC</sub> supply            | Rising voltage               | 4bit Yes | Yes                | Disab.     | 5696 | 5860  | 5968 | mV   |  |  |

| high voltage monitoring |                                                  | Falling voltage              |          |                    |            | 5666 | 5830  | 5938 | ]    |  |  |

| LVD_FLASH               | FLASH supply low voltage monitoring <sup>6</sup> | Rising voltage (untrimmed)   | 4bit     | No                 | Enab.      | 2935 | 3023  | 3112 | mV   |  |  |

|                         |                                                  | Falling voltage (untrimmed)  |          |                    |            | 2922 | 3010  | 3099 |      |  |  |

|                         |                                                  | Rising voltage (trimmed)     |          |                    |            | 2956 | 3010  | 3053 |      |  |  |

|                         |                                                  | Falling voltage (trimmed)    |          |                    |            | 2944 | 2998  | 3041 |      |  |  |

| HVD_FLASH               | FLASH supply high                                | Rising voltage               | 4bit     | Yes Disab. 3456 35 | 3530       | 3584 | mV    |      |      |  |  |

|                         | voltage monitoring <sup>6</sup>                  | Falling voltage              |          |                    |            | 3426 | 3500  | 3554 | 1    |  |  |

| LVD_IO                  | Main I/O V <sub>DDEH1</sub> supply               | Rising voltage (untrimmed)   | 4bit     | No                 | Enab.      | 3250 | 3350  | 3488 | mV   |  |  |

|                         | low voltage monitoring                           | Falling voltage (untrimmed)  |          |                    |            | 3220 | 3320  | 3458 |      |  |  |

|                         |                                                  | Rising voltage (trimmed)     |          |                    |            | 3347 | 3420  | 3468 |      |  |  |

|                         |                                                  | Falling voltage (trimmed)    |          |                    |            | 3317 | 3390  | 3438 | ]    |  |  |

| t <sub>VDASSERT</sub>   | Voltage detector threshold crossing assertion    | _                            | _        | -                  | _          | 0.1  | -     | 2.0  | μs   |  |  |

| t <sub>VDRELEASE</sub>  | Voltage detector threshold crossing de-assertion | _                            | _        | -                  | _          | 5    | -     | 20   | μs   |  |  |

- 1. LVD is released after t<sub>VDRELEASE</sub> temporization when upper threshold is crossed; LVD is asserted t<sub>VDASSERT</sub> after detection when lower threshold is crossed.

- 2. HVD is released after t<sub>VDRELEASE</sub> temporization when lower threshold is crossed; HVD is asserted t<sub>VDASSERT</sub> after detection when upper threshold is crossed.

- 3. POR098\_c threshold is an untrimmed value, before the completion of the power-up sequence. All other LVD/HVD thresholds are provided after trimming.

- 4. LV internal supply levels are measured on device internal supply grid after internal voltage drop.

- 5. LV external supply levels are measured on the die side of the package bond wire after package voltage drop.

- 6. V<sub>DDFLA</sub> range is guaranteed when internal flash memory regulator is used.

# 3.11.4 Power sequencing requirements

Requirements for power sequencing include the following.

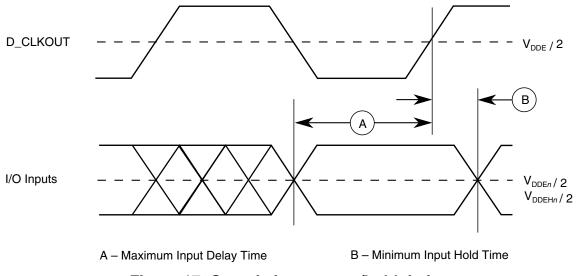

Figure 17. Generic input setup/hold timing

# 3.13.2 Reset and configuration pin timing

## Table 35. Reset and configuration pin timing<sup>1</sup>

| Spec | Characteristic                                     | Symbol            | Min | Max | Unit                          |

|------|----------------------------------------------------|-------------------|-----|-----|-------------------------------|

| 1    | RESET Pulse Width                                  | t <sub>RPW</sub>  | 10  | —   | t <sub>cyc</sub> <sup>2</sup> |

| 2    | RESET Glitch Detect Pulse Width                    | t <sub>GPW</sub>  | 2   | —   | t <sub>cyc</sub> <sup>2</sup> |

| 3    | PLLCFG, BOOTCFG, WKPCFG Setup Time to RSTOUT Valid | t <sub>RCSU</sub> | 10  | —   | t <sub>cyc</sub> <sup>2</sup> |

| 4    | PLLCFG, BOOTCFG, WKPCFG Hold Time to RSTOUT Valid  | t <sub>RCH</sub>  | 0   |     | t <sub>cyc</sub> <sup>2</sup> |

1. Reset timing specified at:  $V_{DDEH}$  = 3.0 V to 5.25 V,  $V_{DD}$  = 1.08 V to 1.32 V, TA = TL to TH.

2. For further information on  $t_{cyc}$ , see Table 3.

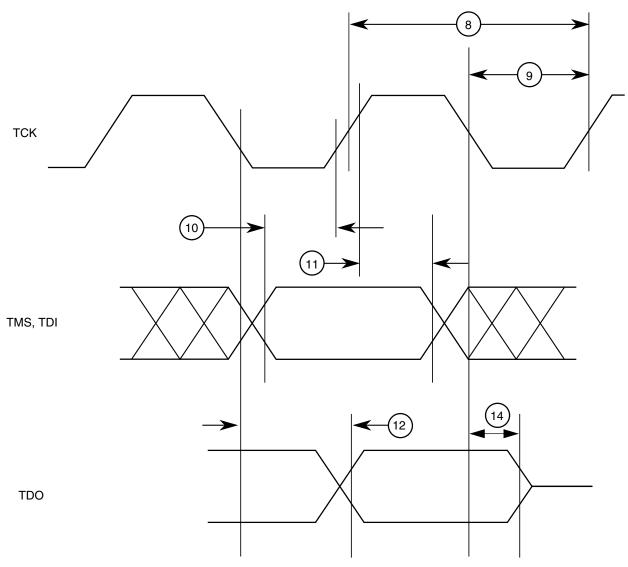

Figure 24. Nexus TCK, TDI, TMS, TDO Timing

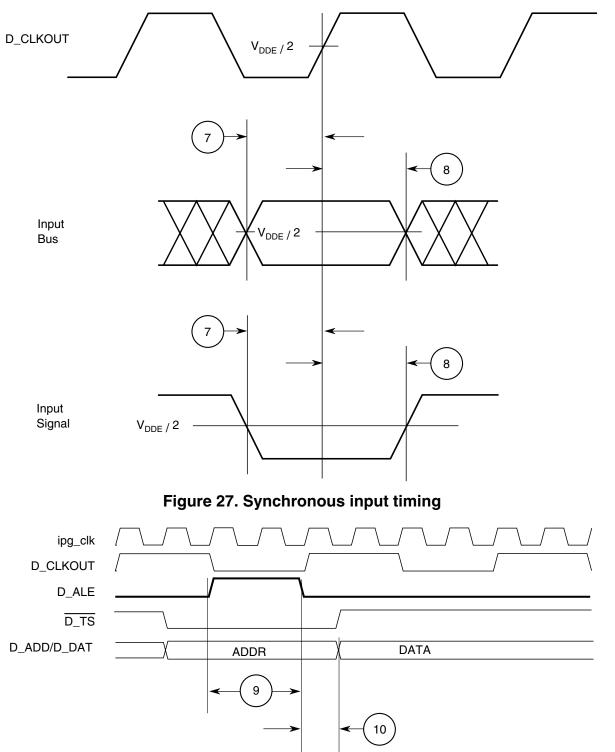

# 3.13.5 External Bus Interface (EBI) timing Table 38. Bus operation timing<sup>1</sup>

| Spec | Characteristic      | Symbol           | 66 MHz (Ext. | Iz (Ext. bus freq.) <sup>2, 3</sup> |                | Notes                                         |

|------|---------------------|------------------|--------------|-------------------------------------|----------------|-----------------------------------------------|

| Spec | Characteristic      | Symbol           | Min          | Мах                                 | Onit           | NOLES                                         |

| 1    | D_CLKOUT Period     | t <sub>C</sub>   | 15.2         | —                                   | ns             | Signals are measured at 50% $V_{\text{DDE}}.$ |

| 2    | D_CLKOUT Duty Cycle | t <sub>CDC</sub> | 45%          | 55%                                 | t <sub>C</sub> | —                                             |

| 3    | D_CLKOUT Rise Time  | t <sub>CRT</sub> | _            | 4                                   | ns             | —                                             |

| 4    | D_CLKOUT Fall Time  | t <sub>CFT</sub> |              | 4                                   | ns             | —                                             |

Table continues on the next page...

Table 38. Bus operation timing<sup>1</sup> (continued)

| ~    |                                                                                                                                                               |                  | 66 MHz (Ext | MHz (Ext. bus freq.) <sup>2, 3</sup> |      |                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|--------------------------------------|------|-------------------------------------------------------------------------------------------------|

| Spec | Characteristic                                                                                                                                                | Symbol           | Min         | Мах                                  | Unit | Notes                                                                                           |

| 5    | D_CLKOUT Posedge to Output<br>Signal Invalid or High Z (Hold<br>Time)<br>D_ADD[9:30]<br>D_BDIP<br>D_CS[0:3]<br>D_DAT[0:15]<br>D_OE<br>D_RD_WR<br>D_TA<br>D_TS | tсон             | 1.0/1.5     | _                                    | ns   | Hold time selectable via<br>SIU_ECCR[EBTS] bit:<br>EBTS = 0: 1.0 ns<br>EBTS = 1: 1.5 ns         |

| 6    | D_WE[0:3]/D_BE[0:3]<br>D_CLKOUT Posedge to Output<br>Signal Valid (Output Delay)<br>D_ADD[9:30]<br>D_BDIP<br>D_CS[0:3]                                        | t <sub>COV</sub> |             | 8.5/9.0                              | ns   | Output valid time selectable via<br>SIU_ECCR[EBTS] bit:<br>EBTS = 0: 8.5 ns<br>EBTS = 1: 9.0 ns |

|      | D_DAT[0:15]                                                                                                                                                   |                  |             | 11.5                                 |      |                                                                                                 |