Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z7                                                                   |

| Core Size                  | 32-Bit Tri-Core                                                          |

| Speed                      | 264MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                  |

| Peripherals                | DMA, LVD, POR, Zipwire                                                   |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 8MB (8M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 416-BGA                                                                  |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777csk3mme3r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Introd | luction     |                                             |

|---|--------|-------------|---------------------------------------------|

|   | 1.1    | Features    | summary3                                    |

|   | 1.2    | Block dia   | gram4                                       |

| 2 | Pinou  | ıts         | 5                                           |

|   | 2.1    | 416-ball N  | APBGA pin assignments5                      |

|   | 2.2    | 516-ball N  | APBGA pin assignments6                      |

| 3 | Electi | rical chara | cteristics7                                 |

|   | 3.1    | Absolute    | maximum ratings7                            |

|   | 3.2    | Electroma   | agnetic interference (EMI) characteristics9 |

|   | 3.3    | Electrosta  | atic discharge (ESD) characteristics9       |

|   | 3.4    | Operating   | conditions9                                 |

|   | 3.5    | DC electr   | ical specifications12                       |

|   | 3.6    | I/O pad s   | pecifications13                             |

|   |        | 3.6.1       | Input pad specifications13                  |

|   |        | 3.6.2       | Output pad specifications15                 |

|   |        | 3.6.3       | I/O pad current specifications19            |

|   | 3.7    | Oscillator  | and PLL electrical specifications19         |

|   |        | 3.7.1       | PLL electrical specifications20             |

|   |        | 3.7.2       | Oscillator electrical specifications21      |

|   | 3.8    | Analog-to   | -Digital Converter (ADC) electrical         |

|   |        | specificat  | ions23                                      |

|   |        | 3.8.1       | Enhanced Queued Analog-to-Digital           |

|   |        |             | Converter (eQADC)23                         |

|   |        | 3.8.2       | Sigma-Delta ADC (SDADC)25                   |

|   | 3.9    | Temperat    | ure Sensor34                                |

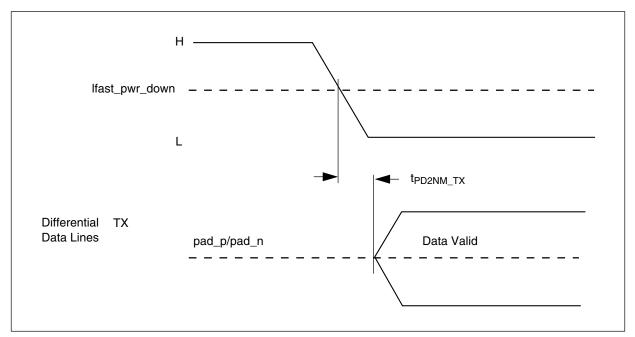

|   | 3.10   | LVDS Fa     | st Asynchronous Serial Transmission (LFAST) |

|   |        | pad elect   | rical characteristics34                     |

|   |        | 3.10.1      | LFAST interface timing diagrams34           |

|   |        | 3.10.2      | LFAST and MSC/DSPI LVDS interface           |

|   |        |             | electrical characteristics                  |

|   |        | 3.10.3      | LFAST PLL electrical characteristics39      |

|   | 3.11   | Power ma    | anagement: PMC, POR/LVD, power              |

|   |        | sequenci    | ng40                                        |

|        | 3.11.1      | Power management electrical characteristics 40 |

|--------|-------------|------------------------------------------------|

|        | 3.11.2      | Power management integration43                 |

|        | 3.11.3      | Device voltage monitoring44                    |

|        | 3.11.4      | Power sequencing requirements46                |

| 3.12   | Flash me    | mory specifications47                          |

|        | 3.12.1      | Flash memory program and erase                 |

|        |             | specifications48                               |

|        | 3.12.2      | Flash memory Array Integrity and Margin        |

|        |             | Read specifications48                          |

|        | 3.12.3      | Flash memory module life specifications49      |

|        | 3.12.4      | Data retention vs program/erase cycles50       |

|        | 3.12.5      | Flash memory AC timing specifications50        |

|        | 3.12.6      | Flash memory read wait-state and address-      |

|        |             | pipeline control settings51                    |

| 3.13   | AC timing   | j52                                            |

|        | 3.13.1      | Generic timing diagrams52                      |

|        | 3.13.2      | Reset and configuration pin timing53           |

|        | 3.13.3      | IEEE 1149.1 interface timing54                 |

|        | 3.13.4      | Nexus timing57                                 |

|        | 3.13.5      | External Bus Interface (EBI) timing59          |

|        | 3.13.6      | External interrupt timing (IRQ/NMI pin)63      |

|        | 3.13.7      | eTPU timing64                                  |

|        | 3.13.8      | eMIOS timing65                                 |

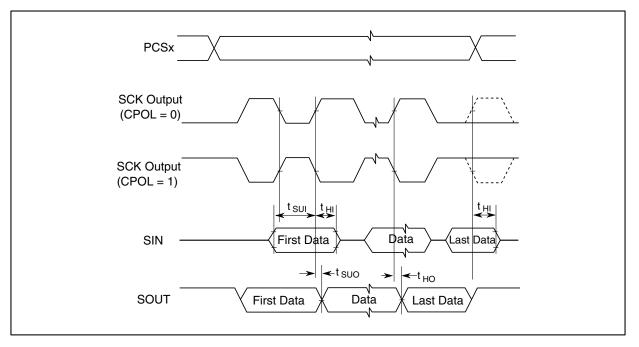

|        | 3.13.9      | DSPI timing with CMOS and LVDS pads66          |

|        | 3.13.10     | FEC timing78                                   |

| 4 Pack | age inform  | nation83                                       |

| 4.1    | Thermal     | characteristics83                              |

|        | 4.1.1       | General notes for thermal characteristics84    |

| 5 Orde | ring inform | nation87                                       |

| 6 Docu | iment revis | sion history88                                 |

#### Introduction

- Enhanced Modular Input/Output System (eMIOS) supporting 32 unified channels with each channel capable of single action, double action, pulse width modulation (PWM) and modulus counter operation

- Two Enhanced Queued Analog-to-Digital Converter (eQADC) modules with:

- Two separate analog converters per eQADC module

- Support for a total of 70 analog input pins, expandable to 182 inputs with offchip multiplexers

- Interface to twelve hardware Decimation Filters

- Enhanced "Tap" command to route any conversion to two separate Decimation Filters

- Four independent 16-bit Sigma-Delta ADCs (SDADCs)

- 10-channel Reaction Module

- Ethernet (FEC)

- Two PSI5 modules

- Two SENT Receiver (SRX) modules supporting 12 channels

- Zipwire: SIPI and LFAST modules

- Five Deserial Serial Peripheral Interface (DSPI) modules

- Five Enhanced Serial Communication Interface (eSCI) modules

- Four Controller Area Network (FlexCAN) modules

- Two M\_CAN modules that support FD

- Fault Collection and Control Unit (FCCU)

- Clock Monitor Units (CMUs)

- Tamper Detection Module (TDM)

- Cryptographic Services Engine (CSE)

- Complies with Secure Hardware Extension (SHE) Functional Specification Version 1.1 security functions

- Includes software selectable enhancement to key usage flag for MAC verification and increase in number of memory slots for security keys

- PASS module to support security features

- Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Device and board test support per Joint Test Action Group (JTAG) IEEE 1149.1 and 1149.7

- On-chip voltage regulator controller (VRC) that derives the core logic supply voltage from the high-voltage supply

- On-chip voltage regulator for flash memory

- Self Test capability

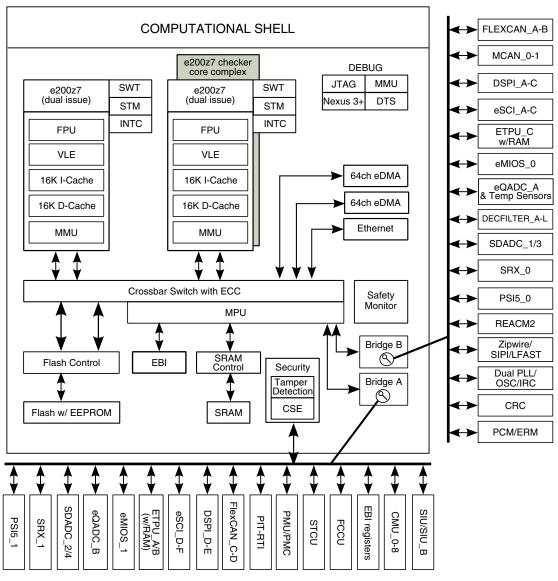

# 1.2 Block diagram

The following figure shows a top-level block diagram of the MPC5777C. The purpose of the block diagram is to show the general interconnection of functional modules through the crossbar switch.

Figure 1. MPC5777C block diagram

# 2 Pinouts

# 2.1 416-ball MAPBGA pin assignments

Figure 2 shows the 416-ball MAPBGA pin assignments.

| Cumhal                              | Deveneter                                                   | Conditional                                             | Va   | lue   | 11    |

|-------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|------|-------|-------|

| Symbol                              | Parameter                                                   | Conditions <sup>1</sup>                                 | Min  | Max   | Unit  |

| Cycle                               | Lifetime power cycles                                       | —                                                       | —    | 1000k | —     |

| V <sub>DD</sub>                     | 1.2 V core supply voltage <sup>2, 3, 4</sup>                | —                                                       | -0.3 | 1.5   | V     |

| V <sub>DDEHx</sub>                  | I/O supply voltage (medium I/O pads) <sup>5</sup>           | —                                                       | -0.3 | 6.0   | V     |

| V <sub>DDEx</sub>                   | I/O supply voltage (fast I/O pads) <sup>5</sup>             | —                                                       | -0.3 | 6.0   | V     |

| V <sub>DDPMC</sub>                  | Power Management Controller supply voltage <sup>5</sup>     | _                                                       | -0.3 | 6.0   | V     |

| V <sub>DDFLA</sub>                  | Decoupling pin for flash regulator <sup>6</sup>             | —                                                       | -0.3 | 4.5   | V     |

| V <sub>STBY</sub>                   | RAM standby supply voltage <sup>5</sup>                     | —                                                       | -0.3 | 6.0   | V     |

| V <sub>SSA_SD</sub>                 | SDADC ground voltage                                        | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>SSA_EQ</sub>                 | eQADC ground voltage                                        | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>DDA_EQA/B</sub>              | eQADC supply voltage                                        | Reference to V <sub>SSA_EQ</sub>                        | -0.3 | 6.0   | V     |

| V <sub>DDA_SD</sub>                 | SDADC supply voltage                                        | Reference to V <sub>SSA_SD</sub>                        | -0.3 | 6.0   | V     |

| V <sub>RL_SD</sub>                  | SDADC ground reference                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>RL_EQ</sub>                  | eQADC ground reference                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>RH_EQ</sub>                  | eQADC alternate reference                                   | Reference to V <sub>RL_EQ</sub>                         | -0.3 | 6.0   | V     |

| V <sub>RH_SD</sub>                  | SDADC alternate reference                                   | Reference to V <sub>RL_SD</sub>                         | -0.3 | 6.0   | V     |

| V <sub>REFBYPC</sub>                | eQADC reference decoupling capacitor pins                   | REFBYPCA25, REFBYPCA75,<br>REFBYPCB25, REFBYPC75        | -0.3 | 6.0   | V     |

| V <sub>DDA_MISC</sub>               | TRNG and IRC supply voltage                                 | —                                                       | -0.3 | 6.0   | V     |

| V <sub>DDPWR</sub>                  | SMPS driver supply pin                                      | —                                                       | -0.3 | 6.0   | V     |

| V <sub>SSPWR</sub>                  | SMPS driver supply pin                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| $V_{SS} - V_{SSA_EQ}$               | V <sub>SSA_EQ</sub> differential voltage                    | —                                                       | -0.3 | 0.3   | V     |

| $V_{SS} - V_{SSA\_SD}$              | V <sub>SSA_SD</sub> differential voltage                    | -                                                       | -0.3 | 0.3   | V     |

| $V_{SS} - V_{RL_{EQ}}$              | V <sub>RL_EQ</sub> differential voltage                     | -                                                       | -0.3 | 0.3   | V     |

| $V_{SS} - V_{RL_{SD}}$              | V <sub>RL_SD</sub> differential voltage                     | —                                                       | -0.3 | 0.3   | V     |

| V <sub>IN</sub>                     | I/O input voltage range <sup>7</sup>                        | —                                                       | -0.3 | 6.0   | V     |

|                                     |                                                             | Relative to V <sub>DDEx</sub> /V <sub>DDEHx</sub>       | —    | 0.3   | V     |

|                                     |                                                             | Relative to V <sub>SS</sub>                             | -0.3 | _     | V     |

| I <sub>INJD</sub>                   | Maximum DC injection current for digital pad                | Per pin, applies to all digital pins                    | -5   | 5     | mA    |

| I <sub>INJA</sub>                   | Maximum DC injection current for analog pad                 | Per pin, applies to all analog pins                     | -5   | 5     | mA    |

| I <sub>MAXSEG</sub> <sup>8, 9</sup> | Maximum current per I/O power segment                       | _                                                       | -120 | 120   | mA    |

| T <sub>STG</sub>                    | Storage temperature range and non-<br>operating times       | _                                                       | -55  | 175   | °C    |

| STORAGE                             | Maximum storage time, assembled part programmed in ECU      | No supply; storage temperature in range –40 °C to 60 °C | -    | 20    | years |

| T <sub>SDR</sub>                    | Maximum solder temperature <sup>10</sup><br>Pb-free package | _                                                       | -    | 260   | °C    |

## Table 1. Absolute maximum ratings

Table continues on the next page ...

| O-multiple                                     | Demonstern                                              |                              |      |                     |                   |      |

|------------------------------------------------|---------------------------------------------------------|------------------------------|------|---------------------|-------------------|------|

| Symbol                                         | Parameter                                               | Conditions                   | Min  | Тур                 | Max               | Unit |

| V <sub>STBY_BO</sub>                           | Standby RAM brownout flag trip point voltage            | —                            | -    | —                   | 0.9 <sup>12</sup> | V    |

| V <sub>RL_SD</sub>                             | SDADC ground reference voltage                          | —                            |      | V <sub>SSA_SD</sub> |                   | V    |

| V <sub>DDA_SD</sub>                            | SDADC supply voltage <sup>13</sup>                      | —                            | 4.5  | —                   | 5.5               | V    |

| V <sub>DDA_EQA/B</sub>                         | eQADC supply voltage                                    | —                            | 4.75 | _                   | 5.25              | V    |

| V <sub>RH_SD</sub>                             | SDADC reference                                         | -                            | 4.5  | V <sub>DDA_SD</sub> | 5.5               | V    |

| $V_{DDA\_SD} - V_{RH\_SD}$                     | SDADC reference differential voltage                    | —                            | —    | —                   | 25                | mV   |

| $V_{SSA\_SD} - V_{RL\_SD}$                     | V <sub>RL_SD</sub> differential voltage                 | -                            | -25  | —                   | 25                | mV   |

| V <sub>RH_EQ</sub>                             | eQADC reference                                         | —                            | 4.75 | —                   | 5.25              | V    |

| V <sub>DDA_EQA/B</sub> –<br>V <sub>RH_EQ</sub> | eQADC reference differential voltage                    | —                            | _    | —                   | 25                | mV   |

| $V_{SSA\_EQ} - V_{RL\_EQ}$                     | V <sub>RL_EQ</sub> differential voltage                 | -                            | -25  | —                   | 25                | mV   |

| $V_{SSA_{EQ}} - V_{SS}$                        | V <sub>SSA_EQ</sub> differential voltage                | —                            | -25  | —                   | 25                | mV   |

| $V_{SSA\_SD} - V_{SS}$                         | V <sub>SSA_SD</sub> differential voltage                | —                            | -25  | —                   | 25                | mV   |

| V <sub>RAMP</sub>                              | Slew rate on power supply pins                          | —                            | _    | —                   | 100               | V/ms |

|                                                |                                                         | Current                      |      |                     |                   | _    |

| I <sub>IC</sub>                                | DC injection current (per pin) <sup>14,</sup><br>15, 16 | Digital pins and analog pins | -3.0 | —                   | 3.0               | mA   |

| I <sub>MAXSEG</sub>                            | Maximum current per power segment <sup>17, 18</sup>     | —                            | -80  | —                   | 80                | mA   |

| Table 3. | <b>Device</b> o | perating | conditions ( | (continued) | ) |

|----------|-----------------|----------|--------------|-------------|---|

|----------|-----------------|----------|--------------|-------------|---|

- Maximum operating frequency is applicable to the computational cores and platform for the device. See the Clocking chapter in the MPC5777C Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 2. If frequency modulation (FM) is enabled, the maximum frequency still cannot exceed this value.

- 3. The maximum specification for operating junction temperature T<sub>J</sub> must be respected. Thermal characteristics provides details.

- 4. Core voltage as measured on device pin to guarantee published silicon performance

- 5. During power ramp, voltage measured on silicon might be lower. Maximum performance is not guaranteed, but correct silicon operation is guaranteed. See power management and reset management for description.

- 6. Maximum core voltage is not permitted for entire product life. See absolute maximum rating.

- 7. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device.

- 8. This LVD/HVD disabled supply voltage condition only applies after LVD/HVD are disabled by the application during the reset sequence, and the LVD/HVD are active until that point.

- 9. This spec does not apply to  $V_{DDEH1}$ .

- 10. When internal flash memory regulator is used:

- Flash memory read operation is supported for a minimum  $V_{DDPMC}$  value of 3.15 V.

- Flash memory read, program, and erase operations are supported for a minimum V<sub>DDPMC</sub> value of 3.5 V.

When flash memory power is supplied externally ( $V_{DDPMC}$  shorted to  $V_{DDFLA}$ ): The  $V_{DDPMC}$  range must be within the limits specified for LVD\_FLASH and HVD\_FLASH monitoring. Table 29 provides the monitored LVD\_FLASH and HVD\_FLASH limits.

- 11. If the standby RAM regulator is not used, the  $V_{STBY}$  supply input pin must be tied to ground.

- 12. V<sub>STBY\_BO</sub> is the maximum voltage that sets the standby RAM brownout flag in the device logic. The minimum voltage for RAM data retention is guaranteed always to be less than the V<sub>STBY\_BO</sub> maximum value.

- 13. For supply voltages between 3.0 V and 4.0 V there will be no guaranteed precision of ADC (accuracy/linearity). ADC will recover to a fully functional state when the voltage rises above 4.0 V.

- 14. Full device lifetime without performance degradation

- 15. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. See the absolute maximum ratings table for maximum input current for reliability requirements.

- 16. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pin is above the supply rail, current will be injected through the clamp diode to the supply rail. For external RC network calculation, assume a typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 17. The sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DDEx</sub>/V<sub>DDEHx</sub> power segment is defined as one or more GPIO pins located between two V<sub>DDEx</sub>/V<sub>DDEHx</sub> supply pins.

- 18. The average current values given in I/O pad current specifications should be used to calculate total I/O segment current.

## 3.5 DC electrical specifications

## NOTE

$I_{DDA\_MISC}$  is the sum of current consumption of IRC,  $I_{TRNG}$ , and  $I_{STBY}$  in the 5 V domain. IRC current is provided in the IRC specifications.

## NOTE

I/O, XOSC, EQADC, SDADC, and Temperature Sensor current specifications are in those components' dedicated sections.

| Symbol              | Parameter                                                                      | Conditions                                   |     | Value |      | Value | Unit |

|---------------------|--------------------------------------------------------------------------------|----------------------------------------------|-----|-------|------|-------|------|

| Symbol              | Farameter                                                                      | Conditions                                   | Min | Тур   | Max  |       |      |

| I <sub>DD</sub>     | Operating current on the $V_{DD}$ core logic supply <sup>1</sup>               | LVD/HVD enabled, $V_{DD}$ = 1.2 V to 1.32 V  | _   | 0.65  | 1.35 | A     |      |

|                     |                                                                                | LVD/HVD disabled, $V_{DD} = 1.2 V$ to 1.38 V | _   | 0.65  | 1.4  |       |      |

| I <sub>DD_PE</sub>  | Operating current on the V <sub>DD</sub> supply for flash memory program/erase | -                                            | _   | —     | 85   | mA    |      |

| I <sub>DDPMC</sub>  | Operating current on the V <sub>DDPMC</sub> supply <sup>2</sup>                | Flash memory read                            |     | —     | 40   | mA    |      |

|                     |                                                                                | Flash memory program/erase                   | _   | —     | 70   |       |      |

|                     |                                                                                | PMC only                                     |     | —     | 35   |       |      |

|                     | Operating current on the V <sub>DDPMC</sub> supply                             | Flash memory read                            | _   | —     | 10   | mA    |      |

|                     | (internal core regulator bypassed)                                             | Flash memory program/erase                   | _   | —     | 40   |       |      |

|                     |                                                                                | PMC only                                     | _   | —     | 5    | 1     |      |

| IREGCTL             | Core regulator DC current output on V <sub>REGCTL</sub> pin                    | -                                            | _   | -     | 25   | mA    |      |

| I <sub>STBY</sub>   | Standby RAM supply current ( $T_J = 150^{\circ}C$ )                            | 1.08 V                                       |     | —     | 1140 | μA    |      |

|                     |                                                                                | 1.25 V to 5.5 V                              | _   | —     | 1170 |       |      |

| I <sub>DD_PWR</sub> | Operating current on the V <sub>DDPWR</sub> supply                             | -                                            | —   | —     | 50   | mA    |      |

| I <sub>BG_REF</sub> | Bandgap reference current consumption <sup>3</sup>                             |                                              |     | —     | 600  | μA    |      |

| I <sub>TRNG</sub>   | True Random Number Generator current                                           | -                                            | _   | —     | 2.1  | mA    |      |

#### Table 4. DC electrical specifications

- 1. I<sub>DD</sub> measured on an application-specific pattern with all cores enabled at full frequency, T<sub>J</sub> = 40°C to 150°C. Flash memory program/erase current on the V<sub>DD</sub> supply not included.

- 2. This value is considering the use of the internal core regulator with the simulation of an external transistor with the minimum value of  $h_{FE}$  of 60.

- 3. This bandgap reference is for EQADC calibration and Temperature Sensors.

# 3.6 I/O pad specifications

Input-only pads

The following table describes the different pad types on the chip.

| Pad type                 | Description                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| General-purpose I/O pads | General-purpose I/O and EBI data bus pads with four selectable output slew rate settings; also called SR pads                    |

| EBI pads                 | Provide necessary speed for fast external memory interfaces on the EBI CLKOUT, address, and control signals; also called FC pads |

| LVDS pads                | Low Voltage Differential Signal interface pads                                                                                   |

Low-input-leakage pads that are associated with the ADC channels

#### Table 5. I/O pad specification descriptions

## NOTE

Each I/O pin on the device supports specific drive configurations. See the signal description table in the device reference manual for the available drive configurations for each I/O pin.

## NOTE

Throughout the I/O pad specifications, the symbol  $V_{DDEx}$  represents all  $V_{DDEx}$  and  $V_{DDEHx}$  segments.

## 3.6.1 Input pad specifications

Table 6 provides input DC electrical characteristics as described in Figure 4.

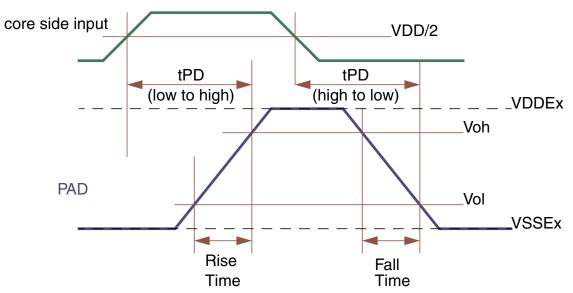

Figure 5. I/O output DC electrical characteristics definition

The following tables specify output DC electrical characteristics.

| Table 9. | GPIO and EBI data pad output buffer electrical characteristics (SR |

|----------|--------------------------------------------------------------------|

|          | pads) <sup>1</sup>                                                 |

| Symbol          | Parameter Conditions <sup>2</sup> |                                           | Value <sup>3</sup>    |      |     | Unit |    |

|-----------------|-----------------------------------|-------------------------------------------|-----------------------|------|-----|------|----|

| Symbol          | Falameter                         | Conditions                                |                       | Min  | Тур | Max  |    |

| I <sub>ОН</sub> | GPIO pad output high              | $V_{OH} = 0.8 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b | 25   | —   | _    | mA |

|                 | current                           | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b | 15   | —   | _    |    |

|                 |                                   | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b | 13   |     | _    |    |

|                 |                                   | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b | 8    | —   | _    |    |

| I <sub>OL</sub> | GPIO pad output low               | $V_{OL} = 0.2 * V_{DDEx}$                 | PCR[SRC] = 11b or 01b | 48   | —   | _    | mA |

|                 | current                           | 4.5 V < V <sub>DDEx</sub> < 5.5 V         | PCR[SRC] = 10b or 00b | 22   | —   | _    |    |

|                 |                                   | V <sub>OL</sub> = 0.2 * V <sub>DDEx</sub> | PCR[SRC] = 11b or 01b | 17   | _   | _    |    |

|                 |                                   | 3.0 V < V <sub>DDEx</sub> < 3.6 V         | PCR[SRC] = 10b or 00b | 10.5 | —   |      |    |

Table continues on the next page ...

1. PCR[DSC] values refer to the setting of that register field in the SIU.

## 3.6.3 I/O pad current specifications

The I/O pads are distributed across the I/O supply segments. Each I/O supply segment is associated with a  $V_{DDEx}$  supply segment.

Table 11 provides I/O consumption figures.

To ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 1.

To ensure device functionality, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 3.

### NOTE

The MPC5777C I/O Signal Description and Input Multiplexing Tables are contained in a Microsoft Excel® file attached to the Reference Manual. In the spreadsheet, select the I/O Signal Table tab.

| Symbol                | Parameter                         | Conditions                                                  |     | Unit |      |    |

|-----------------------|-----------------------------------|-------------------------------------------------------------|-----|------|------|----|

| Symbol                |                                   | Conditions                                                  | Min | Тур  | Мах  |    |

| I <sub>AVG_GPIO</sub> | Average I/O current for GPIO pads | C <sub>L</sub> = 25 pF, 2 MHz                               | —   | —    | 0.42 | mA |

|                       | (per pad)                         | $V_{DDEx} = 5.0 V \pm 10\%$                                 |     |      |      |    |

|                       |                                   | C <sub>L</sub> = 50 pF, 1 MHz                               | —   | _    | 0.35 |    |

|                       |                                   | $V_{DDEx} = 5.0 V \pm 10\%$                                 |     |      |      |    |

| I <sub>AVG_EBI</sub>  |                                   | $C_{DRV} = 10 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |     |      | 9    | mA |

|                       | bus output pins (per pad)         | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

|                       |                                   | $C_{DRV} = 20 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |     | _    | 18   |    |

|                       |                                   | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

|                       |                                   | $C_{DRV} = 30 \text{ pF}, \text{ f}_{EBI} = 66 \text{ MHz}$ | _   | _    | 30   |    |

|                       |                                   | $V_{DDEx} = 3.3 V \pm 10\%$                                 |     |      |      |    |

Table 11. I/O consumption

# 3.7 Oscillator and PLL electrical specifications

The on-chip dual PLL—consisting of the peripheral clock and reference PLL (PLL0) and the frequency-modulated system PLL (PLL1)—generates the system and auxiliary clocks from the main oscillator driver.

| Symbol                  | Parameter                                      | Conditions                                  |       | Unit |                                                                                                       |     |

|-------------------------|------------------------------------------------|---------------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------|-----|

| Symbol                  | Farameter                                      | Conditions                                  | Min   | Тур  | $ \begin{array}{c cccc} - & 78 \\ - & 65 \\ - & 1250 \\ - & 264 \\ - & 100 \\ - & 500^2 \end{array} $ |     |

| f <sub>PLL1IN</sub>     | PLL1 input clock <sup>1</sup>                  | —                                           | 38    | _    | 78                                                                                                    | MHz |

| Δ <sub>PLL1IN</sub>     | PLL1 input clock duty cycle <sup>1</sup>       | —                                           | 35    | —    | 65                                                                                                    | %   |

| f <sub>PLL1VCO</sub>    | PLL1 VCO frequency                             | —                                           | 600   | _    | 1250                                                                                                  | MHz |

| f <sub>PLL1PHI</sub>    | PLL1 output clock PHI                          | —                                           | 4.762 | —    | 264                                                                                                   | MHz |

| t <sub>PLL1LOCK</sub>   | PLL1 lock time                                 | —                                           | —     | —    | 100                                                                                                   | μs  |

| Δ <sub>PLL1PHISPJ</sub> | PLL1_PHI single period peak-to-<br>peak jitter | f <sub>PLL1PHI</sub> = 200 MHz, 6-<br>sigma |       | _    | 500 <sup>2</sup>                                                                                      | ps  |

| f <sub>PLL1MOD</sub>    | PLL1 modulation frequency                      | —                                           | _     | _    | 250                                                                                                   | kHz |

| δ <sub>PLL1MOD</sub>    | PLL1 modulation depth (when                    | Center spread                               | 0.25  | _    | 2                                                                                                     | %   |

| en                      | enabled)                                       | Down spread                                 | 0.5   | —    | 4                                                                                                     | %   |

| I <sub>PLL1</sub>       | PLL1 consumption                               | FINE LOCK state                             | —     | —    | 6                                                                                                     | mA  |

Table 13. PLL1 electrical characteristics

1. PLL1IN clock retrieved directly from either internal PLL0 or external XOSC clock. Input characteristics are granted when using internal PLL0 or external oscillator in functional mode.

2. Noise on the V<sub>DD</sub> supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the V<sub>DD</sub> supply with frequency content in the range of 40 kHz – 50 MHz must be filtered externally to the device.

# 3.7.2 Oscillator electrical specifications

## NOTE

All oscillator specifications in Table 14 are valid for  $V_{DDEH6} = 3.0 \text{ V}$  to 5.5 V.

### Table 14. External oscillator (XOSC) electrical specifications

| Symbol               | Parameter                                                 | Conditions                                   | Va                     | alue                   | Unit |

|----------------------|-----------------------------------------------------------|----------------------------------------------|------------------------|------------------------|------|

| Symbol               | Farameter                                                 | Conditions                                   | Min                    | Мах                    |      |

| f <sub>XTAL</sub>    | Crystal frequency range                                   | _                                            | 8                      | 40                     | MHz  |

| t <sub>cst</sub>     | Crystal start-up time <sup>1, 2</sup>                     | T <sub>J</sub> = 150 °C                      | —                      | 5                      | ms   |

| t <sub>rec</sub>     | Crystal recovery time <sup>3</sup>                        | _                                            | —                      | 0.5                    | ms   |

| VIHEXT               | EXTAL input high voltage (external reference)             | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | V <sub>REF</sub> + 0.6 | _                      | V    |

| V <sub>ILEXT</sub>   | EXTAL input low voltage (external reference)              | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | —                      | V <sub>REF</sub> – 0.6 | V    |

| C <sub>S_EXTAL</sub> | Total on-chip stray capacitance on EXTAL pin <sup>4</sup> | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

|                      |                                                           | 516-ball MAPBGA                              | 2.1                    | 2.8                    |      |

| C <sub>S_XTAL</sub>  | Total on-chip stray capacitance on XTAL pin <sup>4</sup>  | 416-ball MAPBGA                              | 2.3                    | 3.0                    | pF   |

|                      |                                                           | 516-ball MAPBGA                              | 2.2                    | 2.9                    |      |

| 9 <sub>m</sub>       | Oscillator transconductance <sup>5</sup>                  | Low                                          | 3                      | 10                     | mA/V |

|                      |                                                           | Medium                                       | 10                     | 27                     | 1    |

|                      |                                                           | High                                         | 12                     | 35                     |      |

Table continues on the next page ...

# Table 14. External oscillator (XOSC) electrical specifications (continued)

| Symbol             | Parameter                                                         | Conditions | Va  | Unit |    |

|--------------------|-------------------------------------------------------------------|------------|-----|------|----|

| Symbol             | Falanielei                                                        | Min Max    | Max |      |    |

| V <sub>EXTAL</sub> | Oscillation amplitude on the EXTAL pin after startup <sup>6</sup> | _          | 0.5 | 1.6  | V  |

| V <sub>HYS</sub>   | Comparator hysteresis                                             | —          | 0.1 | 1.0  | V  |

| I <sub>XTAL</sub>  | XTAL current <sup>6, 7</sup>                                      | —          |     | 14   | mA |

1. This value is determined by the crystal manufacturer and board design.

- 2. Proper PC board layout procedures must be followed to achieve specifications.

- 3. Crystal recovery time is the time for the oscillator to settle to the correct frequency after adjustment of the integrated load capacitor value.

- 4. See crystal manufacturer's specification for recommended load capacitor (C<sub>L</sub>) values. The external oscillator requires external load capacitors when operating in a "low" transconductance range. Account for on-chip stray capacitance (C<sub>S\_EXTAL</sub>/C<sub>S\_XTAL</sub>) and PCB capacitance when selecting a load capacitor value. When operating in a "medium" or "high" transconductance range, the integrated load capacitor value is selected via software to match the crystal manufacturer's specification, while accounting for on-chip and PCB capacitance.

- 5. Select a "low," "medium," or "high" setting using the UTEST Miscellaneous DCF client's XOSC\_LF\_EN and XOSC\_EN\_HIGH fields. "Low" is the setting commonly used for crystals at 8 MHz, "medium" is commonly used for crystals greater than 8 MHz to 20 MHz, and "high" is commonly used for crystals greater than 20 MHz to 40 MHz. However, the user must characterize carefully to determine the best g<sub>m</sub> setting for the intended application because crystal load capacitance, board layout, and other factors affect the g<sub>m</sub> value that is needed. The user may need an additional Rshunt to optimize g<sub>m</sub> depending on the system environment. Use of overtone crystals is not recommended.

- 6. Amplitude on the EXTAL pin after startup is determined by the ALC block (that is, the Automatic Level Control Circuit). The function of the ALC is to provide high drive current during oscillator startup, while reducing current after oscillation to reduce power, distortion, and RFI, and to avoid over-driving the crystal. The operating point of the ALC is dependent on the crystal value and loading conditions.

- I<sub>XTAL</sub> is the oscillator bias current out of the XTAL pin with both EXTAL and XTAL pins grounded. This is the maximum current during startup of the oscillator. The current after oscillation is typically in the 2–3 mA range and is dependent on the load and series resistance of the crystal. Test circuit is shown in Figure 7.

| load_cap_sel[4:0] from DCF record | Load capacitance <sup>1, 2</sup> (pF) |

|-----------------------------------|---------------------------------------|

| 00000                             | 1.8                                   |

| 00001                             | 2.8                                   |

| 00010                             | 3.7                                   |

| 00011                             | 4.6                                   |

| 00100                             | 5.6                                   |

| 00101                             | 6.5                                   |

| 00110                             | 7.4                                   |

| 00111                             | 8.4                                   |

| 01000                             | 9.3                                   |

| 01001                             | 10.2                                  |

| 01010                             | 11.2                                  |

| 01011                             | 12.1                                  |

| 01100                             | 13.0                                  |

| 01101                             | 13.9                                  |

### Table 15. Selectable load capacitance

Table continues on the next page...

| Cumb - I             | Parameter                                         | Conditions                                               |                              | Value             |                                              |     |  |

|----------------------|---------------------------------------------------|----------------------------------------------------------|------------------------------|-------------------|----------------------------------------------|-----|--|

| Symbol               | Parameter                                         | Conditions                                               | Min                          | Тур               | Max                                          | Un  |  |

| F <sub>rolloff</sub> | Stop band attenuation                             | [0.5 * f <sub>ADCD_S</sub> , 1.0 * f <sub>ADCD_S</sub> ] | 40                           | _                 |                                              | dE  |  |

|                      |                                                   | [1.0 * f <sub>ADCD_S</sub> , 1.5 * f <sub>ADCD_S</sub> ] | 45                           |                   |                                              |     |  |

|                      |                                                   | [1.5 * f <sub>ADCD_S</sub> , 2.0 * f <sub>ADCD_S</sub> ] | 50                           |                   | _                                            |     |  |

|                      |                                                   | [2.0 * f <sub>ADCD_S</sub> , 2.5 * f <sub>ADCD_S</sub> ] | 55                           |                   |                                              |     |  |

|                      |                                                   | [2.5 * f <sub>ADCD_S</sub> , f <sub>ADCD_M</sub> /2]     | 60                           | _                 |                                              |     |  |

| δ <sub>GROUP</sub>   | Group delay                                       | Within pass band: Tclk is $f_{ADCD_M} / 2$               | _                            |                   |                                              |     |  |

|                      |                                                   | OSR = 24                                                 | _                            |                   | 235.5                                        | Tcl |  |

|                      |                                                   | OSR = 28                                                 | _                            |                   | 275                                          |     |  |

|                      |                                                   | OSR = 32                                                 | _                            |                   | 314.5                                        |     |  |

|                      |                                                   | OSR = 36                                                 | _                            |                   | 354                                          |     |  |

|                      |                                                   | OSR = 40                                                 | _                            |                   | 393.5                                        |     |  |

|                      |                                                   | OSR = 44                                                 | _                            |                   | 433                                          |     |  |

|                      |                                                   | OSR = 48                                                 | _                            |                   | 472.5                                        |     |  |

|                      |                                                   | OSR = 56                                                 | _                            |                   | 551.5                                        |     |  |

|                      |                                                   | OSR = 64                                                 | _                            |                   | 630.5                                        |     |  |

|                      |                                                   | OSR = 72                                                 | _                            |                   | 709.5                                        |     |  |

|                      |                                                   | OSR = 75                                                 | _                            |                   | 696                                          |     |  |

|                      |                                                   | OSR = 80                                                 |                              |                   | 788.5                                        |     |  |

|                      |                                                   | OSR = 88                                                 | _                            | _                 | 867.5                                        |     |  |

|                      |                                                   | OSR = 96                                                 | _                            |                   | 946.5                                        |     |  |

|                      |                                                   | OSR = 112                                                |                              |                   | 1104.5                                       |     |  |

|                      |                                                   | OSR = 128                                                | _                            |                   | 1262.5                                       |     |  |

|                      |                                                   | OSR = 144                                                | _                            | _                 | 1420.5                                       |     |  |

|                      |                                                   | OSR = 160                                                |                              |                   | 1578.5                                       |     |  |

|                      |                                                   | OSR = 176                                                | _                            | _                 | 1736.5                                       |     |  |

|                      |                                                   | OSR = 192                                                | _                            |                   | 1894.5                                       |     |  |

|                      |                                                   | OSR = 224                                                | _                            |                   | 2210.5                                       |     |  |

|                      |                                                   | OSR = 256                                                | _                            | _                 | 2526.5                                       |     |  |

|                      |                                                   | Distortion within pass band                              | -0.5/<br>f <sub>ADCD_S</sub> | _                 | +0.5/ f <sub>ADCD_S</sub>                    | -   |  |

| f <sub>HIGH</sub>    | High pass filter 3 dB frequency                   | Enabled                                                  | —                            | 10e–5*<br>fADCD_S | _                                            | -   |  |

| t <sub>STARTUP</sub> | Startup time from power down state                | _                                                        | —                            |                   | 100                                          | μ   |  |

| t <sub>LATENCY</sub> | Latency between input data and converted          | HPF = ON                                                 | —                            | —                 | δ <sub>GROUP</sub> +<br>f <sub>ADCD_</sub> s | -   |  |

|                      | data when input mux does not change <sup>15</sup> | HPF = OFF                                                | —                            | —                 | δ <sub>GROUP</sub>                           | 1   |  |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page...

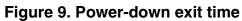

Figure 10. Rise/fall time

# 3.10.2 LFAST and MSC/DSPI LVDS interface electrical characteristics

The following table contains the electrical characteristics for the LFAST interface.

### Table 20. LVDS pad startup and receiver electrical characteristics<sup>1</sup>

| Symbol                              | Parameter                                        | Conditions | Value |     |     | Unit |

|-------------------------------------|--------------------------------------------------|------------|-------|-----|-----|------|

| Symbol                              | Farameter                                        | Conditions | Min   | Тур | Max |      |

| STARTUP <sup>2</sup> , <sup>3</sup> |                                                  |            |       |     |     |      |

| t <sub>STRT_BIAS</sub>              | Bias current reference startup time <sup>4</sup> | —          | —     | 0.5 | 4   | μs   |

Table continues on the next page...

The SMPS regulator characteristics appear in the following table.

| Symbol                | Parameter                  | Conditions | Value<br>Min Typ Max |       |      | Unit |

|-----------------------|----------------------------|------------|----------------------|-------|------|------|

| Symbol                | Farameter                  | Conditions |                      |       |      |      |

| SMPS <sub>CLOCK</sub> | SMPS oscillator frequency  | Trimmed    | 825                  | 1000  | 1220 | kHz  |

| SMPS <sub>SLOPE</sub> | SMPS soft-start ramp slope | —          | 0.01                 | 0.025 | 0.05 | V/µs |

| SMPS <sub>EFF</sub>   | SMPS typical efficiency    | —          | —                    | 70    | —    | %    |

Table 27. SMPS electrical characteristics

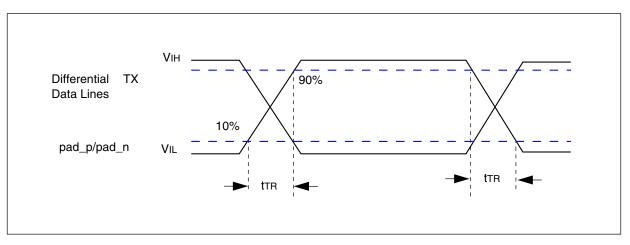

# 3.11.2 Power management integration

To ensure correct functionality of the device, use the following recommended integration scheme for LDO mode.

Figure 14. Recommended supply pin circuits

## NOTE

In these descriptions, *star route layout* means a track split as close as possible to the power supply source. Each of the split tracks is routed individually to the intended end connection.

- 1. For both LDO mode and SMPS mode, V<sub>DDPMC</sub> and V<sub>DDPWR</sub> must be connected together (shorted) to ensure aligned voltage ramping up/down. In addition:

- For SMPS mode, a star route layout of the power track is required to minimize mutual noise. If SMPS mode is not used, the star route layout is not required. V<sub>DDPWR</sub> is the supply pin for the SMPS circuitry.

- For 3.3 V operation,  $V_{DDFLA}$  must also be star routed and shorted to  $V_{DDPWR}$ and  $V_{DDPMC}$ . This triple connection is required because 3.3 V does not guarantee correct functionality of the internal  $V_{DDFLA}$  regulator. Consequently,  $V_{DDFLA}$  is supplied externally.

- 2. V<sub>DDA MISC</sub>: IRC operation is required to provide the clock for chip startup.

- The V<sub>DDPMC</sub>, V<sub>DD</sub>, and V<sub>DDEH1</sub> (reset pin pad segment) supplies are monitored. They hold IRC until all of them reach operational voltage. In other words, V<sub>DDA\_MISC</sub> must reach its specified minimum operating voltage before or at the same time that all of these monitored voltages reach their respective specified minimum voltages.

- An alternative is to connect the same supply voltage to both  $V_{DDEH1}$  and  $V_{DDA\_MISC}$ . This alternative approach requires a star route layout to minimize mutual noise.

- 3. Multiple  $V_{DDEx}$  supplies can be powered up in any order.

During any time when  $V_{DD}$  is powered up but  $V_{DDEx}$  is not yet powered up: pad outputs are unpowered.

During any time when  $V_{DDEx}$  is powered up before all other supplies: all pad output buffers are tristated.

- 4. Ramp up  $V_{DDA EQ}$  before  $V_{DD}$ . Otherwise, a reset might occur.

- 5. When the device is powering down while using the internal SMPS regulator,  $V_{DDPMC}$  and  $V_{DDPWR}$  supplies must ramp down through the voltage range from 2.5 V to 1.5 V in less than 1 second. Slower ramp-down times might result in reduced lifetime reliability of the device.

## 3.12.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                 | Characteristic                                                | Min    | Typical | Max <sup>1</sup>             | Units<br>2 |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|------------|

| t <sub>ai16kseq</sub>  | Array Integrity time for sequential sequence on 16 KB block.  | -      | _       | 512 x<br>Tperiod x<br>Nread  |            |

| t <sub>ai32kseq</sub>  | Array Integrity time for sequential sequence on 32 KB block.  | _      | _       | 1024 x<br>Tperiod x<br>Nread | _          |

| t <sub>ai64kseq</sub>  | Array Integrity time for sequential sequence on 64 KB block.  | _      | _       | 2048 x<br>Tperiod x<br>Nread | _          |

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | -      | _       | 8192 x<br>Tperiod x<br>Nread | _          |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | _       | 110.7                        | μs         |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | —       | 192.6                        | μs         |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 | —       | 356.5                        | μs         |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 | —       | 1,339.5                      | μs         |

- Array Integrity times need to be calculated and is dependent on system frequency and number of clocks per read. The

equation presented require Tperiod (which is the unit accurate period, thus for 200 MHz, Tperiod would equal 5e-9) and

Nread (which is the number of clocks required for read, including pipeline contribution. Thus for a read setup that requires

6 clocks to read with no pipeline, Nread would equal 6. For a read setup that requires 6 clocks to read, and has the

address pipeline set to 2, Nread would equal 4 (or 6 2).)

- 2. The units for Array Integrity are determined by the period of the system clock. If unit accurate period is used in the equation, the results of the equation are also unit accurate.

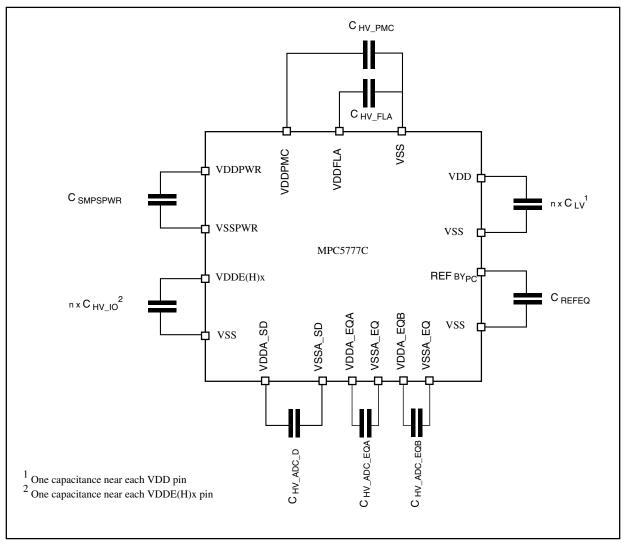

# 3.12.3 Flash memory module life specifications

| Symbol              | Characteristic                                                                              | Conditions                        | Min     | Typical | Units         |

|---------------------|---------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|---------------|

| Array P/E<br>cycles | Number of program/erase cycles per block<br>for 16 KB, 32 KB and 64 KB blocks. <sup>1</sup> | —                                 | 250,000 | _       | P/E<br>cycles |

|                     | Number of program/erase cycles per block for 256 KB blocks. <sup>2</sup>                    | —                                 | 1,000   | 250,000 | P/E<br>cycles |

| Data retention      | Minimum data retention.                                                                     | Blocks with 0 - 1,000 P/E cycles. | 50      | —       | Years         |

|                     |                                                                                             | Blocks with 100,000 P/E cycles.   | 20      | _       | Years         |

|                     |                                                                                             | Blocks with 250,000 P/E cycles.   | 10      | _       | Years         |

Table 32.

Flash memory module life specifications

- 1. Program and erase supported across standard temperature specs.

- 2. Program and erase supported across standard temperature specs.

## 3.12.4 Data retention vs program/erase cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits.

## 3.12.5 Flash memory AC timing specifications Table 33. Flash memory AC timing specifications

| Symbol            | Characteristic                                                                | Min | Typical                                        | Max                                             | Units |

|-------------------|-------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub> | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.          |     | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>esus</sub> | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.          |     | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>res</sub>  | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low. | _   | _                                              | 100                                             | ns    |

Table continues on the next page...

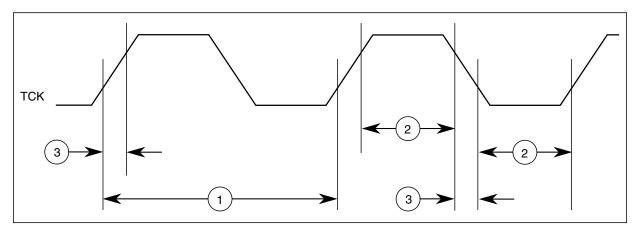

Figure 19. JTAG test clock input timing

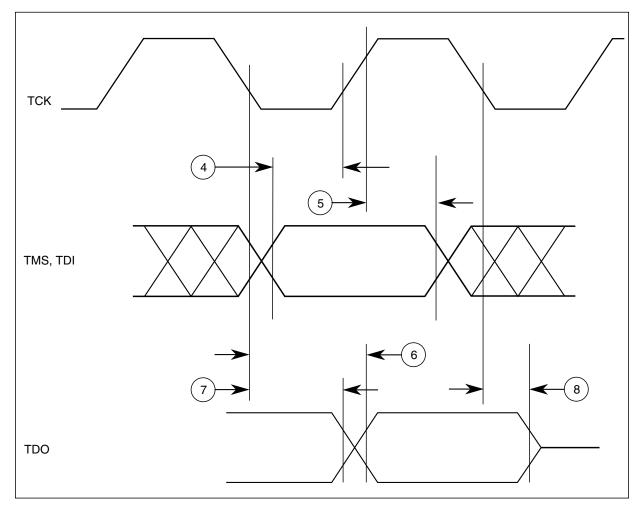

Figure 20. JTAG test access port timing

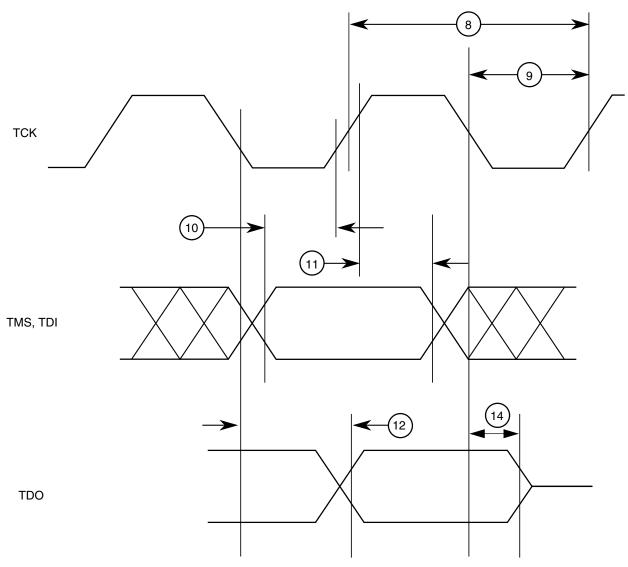

Figure 24. Nexus TCK, TDI, TMS, TDO Timing

## 3.13.5 External Bus Interface (EBI) timing Table 38. Bus operation timing<sup>1</sup>

| Spec | Characteristic      | Symbol           | 66 MHz (Ext. | bus freq.) <sup>2, 3</sup> | Unit           | Notes                                         |

|------|---------------------|------------------|--------------|----------------------------|----------------|-----------------------------------------------|

| Spec | Characteristic      | Symbol           | Min          | Мах                        | Onit           | NOLES                                         |

| 1    | D_CLKOUT Period     | t <sub>C</sub>   | 15.2         | —                          | ns             | Signals are measured at 50% $V_{\text{DDE}}.$ |

| 2    | D_CLKOUT Duty Cycle | t <sub>CDC</sub> | 45%          | 55%                        | t <sub>C</sub> | —                                             |

| 3    | D_CLKOUT Rise Time  | t <sub>CRT</sub> | _            | 4                          | ns             | —                                             |

| 4    | D_CLKOUT Fall Time  | t <sub>CFT</sub> |              | 4                          | ns             | —                                             |

Table continues on the next page...

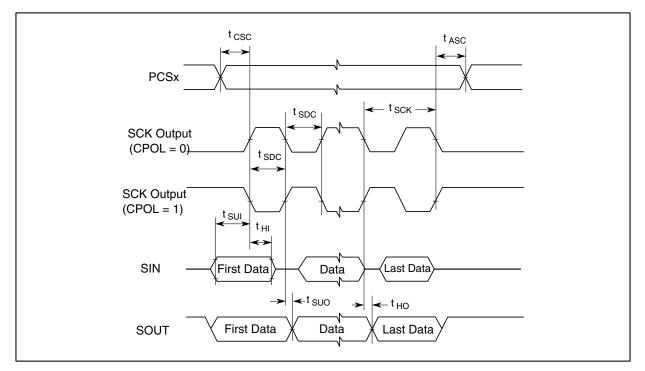

Figure 35. DSPI CMOS master mode – modified timing, CPHA = 0

Figure 36. DSPI CMOS master mode – modified timing, CPHA = 1