#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z7                                                                  |

| Core Size                  | 32-Bit Tri-Core                                                         |

| Speed                      | 264MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                 |

| Peripherals                | DMA, LVD, POR, Zipwire                                                  |

| Number of I/O              | -                                                                       |

| Program Memory Size        | 8MB (8M × 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 516-BGA                                                                 |

| Supplier Device Package    | 516-MAPBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777csk3mmo3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

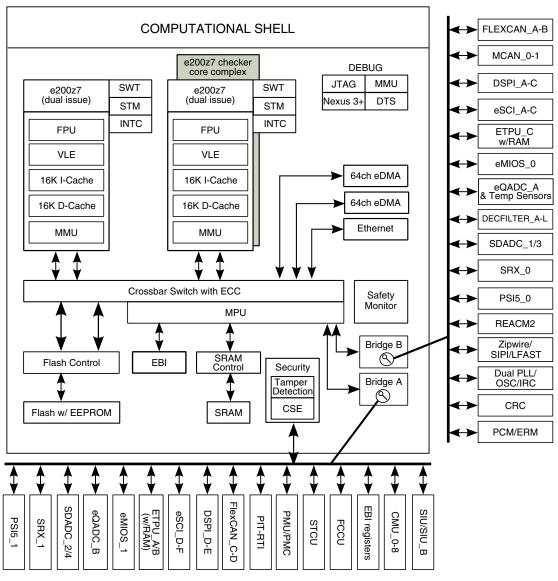

# 1.2 Block diagram

The following figure shows a top-level block diagram of the MPC5777C. The purpose of the block diagram is to show the general interconnection of functional modules through the crossbar switch.

Figure 1. MPC5777C block diagram

# 2 Pinouts

# 2.1 416-ball MAPBGA pin assignments

Figure 2 shows the 416-ball MAPBGA pin assignments.

| O-multiple                                        | Parameter                                               | O a se aliti a se a          |      |                     |                   |      |

|---------------------------------------------------|---------------------------------------------------------|------------------------------|------|---------------------|-------------------|------|

| Symbol                                            | Farameter                                               | Conditions                   | Min  | Тур                 | Max               | Unit |

| V <sub>STBY_BO</sub>                              | Standby RAM brownout flag trip point voltage            | —                            | -    | —                   | 0.9 <sup>12</sup> | V    |

| V <sub>RL_SD</sub> SDADC ground reference voltage |                                                         | —                            |      | V <sub>SSA_SD</sub> |                   | V    |

| V <sub>DDA_SD</sub>                               | SDADC supply voltage <sup>13</sup>                      | —                            | 4.5  | —                   | 5.5               | V    |

| V <sub>DDA_EQA/B</sub>                            | eQADC supply voltage                                    | —                            | 4.75 | _                   | 5.25              | V    |

| V <sub>RH_SD</sub>                                | SDADC reference                                         | -                            | 4.5  | V <sub>DDA_SD</sub> | 5.5               | V    |

| $V_{DDA\_SD} - V_{RH\_SD}$                        | SDADC reference differential voltage                    | —                            | —    | —                   | 25                | mV   |

| $V_{SSA\_SD} - V_{RL\_SD}$                        | V <sub>RL_SD</sub> differential voltage                 | -                            | -25  | —                   | 25                | mV   |

| V <sub>RH_EQ</sub>                                | eQADC reference                                         | -                            | 4.75 | —                   | 5.25              | V    |

| V <sub>DDA_EQA/B</sub> –<br>V <sub>RH_EQ</sub>    | eQADC reference differential voltage                    | —                            | _    | —                   | 25                | mV   |

| $V_{SSA\_EQ} - V_{RL\_EQ}$                        | V <sub>RL_EQ</sub> differential voltage                 | -                            | -25  | —                   | 25                | mV   |

| $V_{SSA_{EQ}} - V_{SS}$                           | V <sub>SSA_EQ</sub> differential voltage                | —                            | -25  | —                   | 25                | mV   |

| $V_{SSA\_SD} - V_{SS}$                            | V <sub>SSA_SD</sub> differential voltage                | —                            | -25  | —                   | 25                | mV   |

| V <sub>RAMP</sub>                                 | Slew rate on power supply pins                          | —                            | _    | —                   | 100               | V/ms |

|                                                   |                                                         | Current                      |      |                     |                   | _    |

| I <sub>IC</sub>                                   | DC injection current (per pin) <sup>14,</sup><br>15, 16 | Digital pins and analog pins | -3.0 | —                   | 3.0               | mA   |

| I <sub>MAXSEG</sub>                               | Maximum current per power segment <sup>17, 18</sup>     | —                            | -80  | —                   | 80                | mA   |

| Table 3. | <b>Device</b> o | perating | conditions ( | (continued) | ) |

|----------|-----------------|----------|--------------|-------------|---|

|----------|-----------------|----------|--------------|-------------|---|

- Maximum operating frequency is applicable to the computational cores and platform for the device. See the Clocking chapter in the MPC5777C Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 2. If frequency modulation (FM) is enabled, the maximum frequency still cannot exceed this value.

- 3. The maximum specification for operating junction temperature T<sub>J</sub> must be respected. Thermal characteristics provides details.

- 4. Core voltage as measured on device pin to guarantee published silicon performance

- 5. During power ramp, voltage measured on silicon might be lower. Maximum performance is not guaranteed, but correct silicon operation is guaranteed. See power management and reset management for description.

- 6. Maximum core voltage is not permitted for entire product life. See absolute maximum rating.

- 7. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device.

- 8. This LVD/HVD disabled supply voltage condition only applies after LVD/HVD are disabled by the application during the reset sequence, and the LVD/HVD are active until that point.

- 9. This spec does not apply to  $V_{DDEH1}$ .

- 10. When internal flash memory regulator is used:

- Flash memory read operation is supported for a minimum  $V_{DDPMC}$  value of 3.15 V.

- Flash memory read, program, and erase operations are supported for a minimum V<sub>DDPMC</sub> value of 3.5 V.

When flash memory power is supplied externally ( $V_{DDPMC}$  shorted to  $V_{DDFLA}$ ): The  $V_{DDPMC}$  range must be within the limits specified for LVD\_FLASH and HVD\_FLASH monitoring. Table 29 provides the monitored LVD\_FLASH and HVD\_FLASH limits.

- 11. If the standby RAM regulator is not used, the  $V_{STBY}$  supply input pin must be tied to ground.

- 12. V<sub>STBY\_BO</sub> is the maximum voltage that sets the standby RAM brownout flag in the device logic. The minimum voltage for RAM data retention is guaranteed always to be less than the V<sub>STBY\_BO</sub> maximum value.

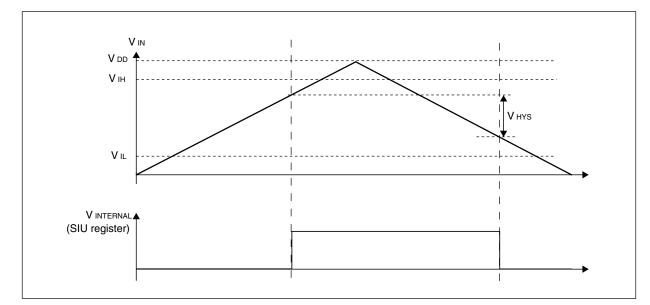

Figure 4. I/O input DC electrical characteristics definition

| Symbol                | Parameter                                                 | Conditions                                                                     |                          | Value |                          | Unit |  |

|-----------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|--|

| Symbol                | Parameter                                                 | Conditions                                                                     | Min                      | Тур   | Max                      |      |  |

| V <sub>IHCMOS_H</sub> | Input high level CMOS (with                               | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                          | 0.65 * V <sub>DDEx</sub> | _     | V <sub>DDEx</sub> + 0.3  | V    |  |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                              |                          |       |                          |      |  |

| VIHCMOS               | Input high level CMOS (without                            | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ and                   | 0.55 * V <sub>DDEx</sub> |       | V <sub>DDEx</sub> + 0.3  | V    |  |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                              |                          |       |                          |      |  |

| V <sub>ILCMOS_H</sub> | Input low level CMOS (with                                | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                          | -0.3                     |       | 0.35 * V <sub>DDEx</sub> | V    |  |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                              |                          |       |                          |      |  |

| VILCMOS               | Input low level CMOS (without                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ and                   | -0.3                     | _     | 0.4 * V <sub>DDEx</sub>  | V    |  |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                              |                          |       |                          |      |  |

| V <sub>HYSCMOS</sub>  | Input hysteresis CMOS                                     | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ and                   | 0.1 * V <sub>DDEx</sub>  |       | —                        | V    |  |

|                       |                                                           | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                              |                          |       |                          |      |  |

|                       |                                                           | Input Characteristics <sup>1</sup>                                             |                          |       |                          |      |  |

| I <sub>LKG</sub>      | Digital input leakage                                     | $V_{SS} < V_{IN} < V_{DDEx}/V_{DDEHx}$                                         |                          |       | 2.5                      | μA   |  |

| I <sub>LKG_FAST</sub> | Digital input leakage for EBI address/control signal pads | $V_{SS} < V_{IN} < V_{DDEx}/V_{DDEHx}$                                         | —                        | —     | 2.5                      | μA   |  |

| I <sub>LKGA</sub>     | Analog pin input leakage (5 V range)                      | $V_{SSA\_SD} < V_{IN} < V_{DDA\_SD}, \\ V_{SSA\_EQ} < V_{IN} < V_{DDA\_EQA/B}$ | —                        |       | 220                      | nA   |  |

| C <sub>IN</sub>       | Digital input capacitance                                 | GPIO and EBI input pins                                                        | —                        | _     | 7                        | pF   |  |

| Table 6. | I/O input DC electrical characteristics |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

1. For LFAST, microsecond bus, and LVDS input characteristics, see dedicated communication module sections.

Table 7 provides current specifications for weak pullup and pulldown.

# Table 9. GPIO and EBI data pad output buffer electrical characteristics (SR pads)<sup>1</sup> (continued)

| Symbol           | Parameter                             | Conditions <sup>2</sup>           |                                               |     | Value <sup>3</sup> |      | Unit |

|------------------|---------------------------------------|-----------------------------------|-----------------------------------------------|-----|--------------------|------|------|

| Symbol           |                                       |                                   |                                               | Min | Тур                | Max  |      |

| t <sub>R_F</sub> | GPIO pad output                       | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF                        |     |                    | 1.2  | ns   |

|                  | transition time (rise/fall)           | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 50 pF                        | _   |                    | 2.5  |      |

|                  |                                       |                                   | C <sub>L</sub> = 200 pF                       | _   | _                  | 8    |      |

|                  |                                       | PCR[SRC] = 11b                    | C <sub>L</sub> = 25 pF                        | _   | _                  | 1.7  |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 50 pF                        | _   | —                  | 3.25 |      |

|                  |                                       |                                   | C <sub>L</sub> = 200 pF                       | _   | —                  | 12   |      |

|                  |                                       | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     | _                  | 5    |      |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   | —                  | 18   | ]    |

|                  |                                       | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     | —                  | 7    |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       | _   | —                  | 25   |      |

|                  |                                       | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        | _   |                    | 13   |      |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   |                    | 24   | 1    |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF                        | _   |                    | 25   |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 30   |      |

|                  |                                       | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        | _   |                    | 24   |      |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 50   |      |

|                  |                                       | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        |     |                    | 40   |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       | _   |                    | 51   |      |

| t <sub>PD</sub>  | GPIO pad output                       |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 6    | ns   |

|                  | propagation delay time                | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       | _   |                    | 13   |      |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 8.25 |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 19.5 |      |

|                  |                                       | PCR[SRC] = 10b                    | C <sub>L</sub> = 50 pF                        |     |                    | 9    |      |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     | _                  | 22   |      |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 12.5 |      |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     | _                  | 35   |      |

|                  |                                       | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        |     |                    | 27   |      |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 40   |      |

|                  |                                       | PCR[SRC] = 01b                    | C <sub>L</sub> = 50 pF                        |     |                    | 45   | 1    |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V | C <sub>L</sub> = 200 pF                       |     |                    | 65   | 1    |

|                  |                                       | PCR[SRC] = 00b                    | C <sub>L</sub> = 50 pF                        |     |                    | 40   | 1    |

|                  |                                       | 4.5 V < V <sub>DDEx</sub> < 5.5 V | C <sub>L</sub> = 200 pF                       |     |                    | 65   | 1    |

|                  |                                       |                                   | C <sub>L</sub> = 50 pF                        |     |                    | 75   | 1    |

|                  |                                       | 3.0 V < V <sub>DDEx</sub> < 3.6 V |                                               |     |                    | 100  | 1    |

| SKEW_W           | Difference between rise and fall time |                                   | <u>  -                                   </u> | — — |                    | 25   | %    |

1. All GPIO pad output specifications are valid for 3.0 V <  $V_{DDEx}$  < 5.5 V, except where explicitly stated.

1. PCR[DSC] values refer to the setting of that register field in the SIU.

## 3.6.3 I/O pad current specifications

The I/O pads are distributed across the I/O supply segments. Each I/O supply segment is associated with a  $V_{DDEx}$  supply segment.

Table 11 provides I/O consumption figures.

To ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 1.

To ensure device functionality, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 3.

## NOTE

The MPC5777C I/O Signal Description and Input Multiplexing Tables are contained in a Microsoft Excel® file attached to the Reference Manual. In the spreadsheet, select the I/O Signal Table tab.

| Symbol                | Parameter                         | Conditions                                                  | Value |     |      | Unit |

|-----------------------|-----------------------------------|-------------------------------------------------------------|-------|-----|------|------|

| Symbol                |                                   | Conditions                                                  | Min   | Тур | Мах  |      |

| I <sub>AVG_GPIO</sub> | Average I/O current for GPIO pads | C <sub>L</sub> = 25 pF, 2 MHz                               | —     | —   | 0.42 | mA   |

|                       | (per pad)                         | $V_{DDEx} = 5.0 V \pm 10\%$                                 |       |     |      |      |

|                       |                                   | C <sub>L</sub> = 50 pF, 1 MHz                               | —     | —   | 0.35 |      |

|                       |                                   | $V_{DDEx} = 5.0 V \pm 10\%$                                 |       |     |      |      |

| I <sub>AVG_EBI</sub>  |                                   | $C_{DRV} = 10 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |       |     | 9    | mA   |

|                       | bus output pins (per pad)         | $V_{DDEx} = 3.3 V \pm 10\%$                                 |       |     |      |      |

|                       |                                   | $C_{DRV} = 20 \text{ pF}, f_{EBI} = 66 \text{ MHz}$         |       | _   | 18   |      |

|                       |                                   | $V_{DDEx} = 3.3 V \pm 10\%$                                 |       |     |      |      |

|                       |                                   | $C_{DRV} = 30 \text{ pF}, \text{ f}_{EBI} = 66 \text{ MHz}$ |       | _   | 30   |      |

|                       |                                   | $V_{DDEx} = 3.3 V \pm 10\%$                                 |       |     |      |      |

Table 11. I/O consumption

# 3.7 Oscillator and PLL electrical specifications

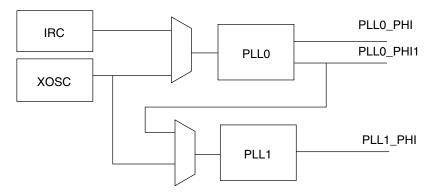

The on-chip dual PLL—consisting of the peripheral clock and reference PLL (PLL0) and the frequency-modulated system PLL (PLL1)—generates the system and auxiliary clocks from the main oscillator driver.

Figure 6. PLL integration

# 3.7.1 PLL electrical specifications

### Table 12. PLL0 electrical characteristics

| Symphol                  | Parameter                                 | Conditions                                                                 | Value |     |                  | Unit |

|--------------------------|-------------------------------------------|----------------------------------------------------------------------------|-------|-----|------------------|------|

| Symbol                   | Farameter                                 | Conditions                                                                 | Min   | Тур | Max              |      |

| f <sub>PLL0IN</sub>      | PLL0 input clock <sup>1, 2</sup>          | —                                                                          | 8     | _   | 44               | MHz  |

| Δ <sub>PLL0IN</sub>      | PLL0 input clock duty cycle <sup>2</sup>  | —                                                                          | 40    | —   | 60               | %    |

| f <sub>PLL0VCO</sub>     | PLL0 VCO frequency                        | —                                                                          | 600   |     | 1250             | MHz  |

| f <sub>PLL0PHI</sub>     | PLL0 output frequency                     | —                                                                          | 4.762 | _   | 200              | MHz  |

| t <sub>PLL0LOCK</sub>    | PLL0 lock time                            | —                                                                          | _     |     | 110              | μs   |

| $ \Delta_{PLL0PHISPJ} $  | PLL0_PHI single period jitter             | f <sub>PLL0PHI</sub> = 200 MHz, 6-sigma                                    | _     |     | 200              | ps   |

|                          | f <sub>PLL0IN</sub> = 20 MHz (resonator)  |                                                                            |       |     |                  |      |

| Δ <sub>PLL0PHI1SPJ</sub> | PLL0_PHI1 single period jitter            | f <sub>PLL0PHI1</sub> = 40 MHz, 6-sigma                                    | _     | _   | 300 <sup>3</sup> | ps   |

|                          | f <sub>PLL0IN</sub> = 20 MHz (resonator)  |                                                                            |       |     |                  |      |

| Δ <sub>PLL0LTJ</sub>     | PLL0 output long term jitter <sup>3</sup> | 10 periods accumulated jitter (80 MHz                                      |       | _   | ±250             | ps   |

|                          | f <sub>PLL0IN</sub> = 20 MHz (resonator), | equivalent frequency), 6-sigma pk-pk                                       |       |     |                  |      |

|                          | VCO frequency = 800 MHz                   | 16 periods accumulated jitter (50 MHz equivalent frequency), 6-sigma pk-pk | —     | _   | ±300             | ps   |

|                          |                                           | long term jitter (< 1 MHz equivalent frequency), 6-sigma pk-pk)            | —     | _   | ±500             | ps   |

| I <sub>PLL0</sub>        | PLL0 consumption                          | FINE LOCK state                                                            | _     | —   | 7.5              | mA   |

f<sub>PLLOIN</sub> frequency must be scaled down using PLLDIG\_PLL0DV[PREDIV] to ensure PFD input signal is in the range 8 MHz to 20 MHz.

2. PLLOIN clock retrieved directly from either internal IRC or external XOSC clock. Input characteristics are granted when using internal IRC or external oscillator is used in functional mode.

3. Noise on the V<sub>DD</sub> supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the V<sub>DD</sub> supply with frequency content in the range of 40 kHz – 50 MHz must be filtered externally to the device.

- 5. Below disruptive current conditions, the channel being stressed has conversion values of \$3FF for analog inputs greater than V<sub>BH</sub> and \$000 for values less than V<sub>BL</sub>. Other channels are not affected by non-disruptive conditions.

- 6. Exceeding limit may cause conversion error on stressed channels and on unstressed channels. Transitions within the limit do not affect device reliability or cause permanent damage.

- Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values using V<sub>POSCLAMP</sub> = V<sub>DDA</sub> + 0.5 V and V<sub>NEGCLAMP</sub> = -0.3 V, then use the larger of the calculated values.

- 8. Condition applies to two adjacent pins at injection limits.

- 9. Performance expected with production silicon.

- 10. All channels have same 10 k $\Omega$  < Rs < 100 k $\Omega$  Channel under test has Rs = 10 k $\Omega$ ,  $I_{INJ}=I_{INJMAX}$ ,  $I_{INJMIN}$ .

- 11. The TUE specification is always less than the sum of the INL, DNL, offset, and gain errors due to cancelling errors.

- 12. TUE does not apply to differential conversions.

- Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed as indicated.

- 14. Guaranteed 10-bit monotonicity.

- 15. At  $V_{RH\_EQ} V_{RL\_EQ}$  = 5.12 V, one LSB = 1.25 mV.

# 3.8.2 Sigma-Delta ADC (SDADC)

The SDADC is a 16-bit Sigma-Delta analog-to-digital converter with a 333 Ksps maximum output conversion rate.

## NOTE

The voltage range is 4.5 V to 5.5 V for SDADC specifications, except where noted otherwise.

| Symbol                  | Parameter                                | Conditions                                                     |     | Value                  | 9                   | Unit |

|-------------------------|------------------------------------------|----------------------------------------------------------------|-----|------------------------|---------------------|------|

| Symbol                  | Falameter                                | Conditions                                                     | Min | Тур                    | Мах                 |      |

| V <sub>IN</sub>         | ADC input signal                         | —                                                              | 0   | _                      | V <sub>DDA_SD</sub> | V    |

| V <sub>IN_PK2PK</sub> 1 | Input range peak to peak                 | Single ended<br>V <sub>INM</sub> = V <sub>RL_SD</sub>          |     | V <sub>RH_SD</sub> /G  | iAIN                | V    |

|                         | $V_{IN_{PK2PK}} = V_{INP}^2 - V_{INM}^3$ | Single ended<br>$V_{INM} = 0.5^*V_{RH_{SD}}$<br>GAIN = 1       |     | ±0.5*V <sub>RF</sub>   | I_SD                |      |

|                         |                                          | Single ended<br>$V_{INM} = 0.5^* V_{RH_SD}$<br>GAIN = 2,4,8,16 |     | ±V <sub>RH_SD</sub> /( | GAIN                |      |

|                         |                                          | Differential<br>0 < V <sub>IN</sub> < V <sub>DDEx</sub>        |     | ±V <sub>RH_SD</sub> /0 | GAIN                |      |

| f <sub>ADCD_M</sub>     | SD clock frequency <sup>4</sup>          | —                                                              | 4   | 14.4                   | 16                  | MHz  |

| f <sub>ADCD_S</sub>     | Conversion rate                          | —                                                              | —   | _                      | 333                 | Ksps |

| _                       | Oversampling ratio                       | Internal modulator                                             | 24  | —                      | 256                 | —    |

| RESOLUTION              | SD register resolution <sup>5</sup>      | 2's complement notation                                        |     | 16                     |                     | bit  |

### Table 18. SDADC electrical specifications

Table continues on the next page...

| Symbol                 | Parameter                                  | Conditions                                                       |     | Value |     | Unit |

|------------------------|--------------------------------------------|------------------------------------------------------------------|-----|-------|-----|------|

| Symbol                 |                                            | Conditions                                                       | Min | Тур   | Max |      |

| SNR <sub>DIFF150</sub> | Signal to noise ratio in                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 80  | _     | _   | dB   |

|                        | differential mode, 150<br>Ksps output rate | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 1                                                         |     |       |     |      |

|                        |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 77  | _     | _   |      |

|                        |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 2                                                         |     |       |     |      |

|                        |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 74  | _     | —   |      |

|                        |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 4                                                         |     |       |     |      |

|                        |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 71  | _     | —   |      |

|                        |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 8                                                         |     |       |     |      |

|                        |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 68  | _     | _   |      |

|                        |                                            | $V_{RH_SD} = V_{DDA_SD}$                                         |     |       |     |      |

|                        |                                            | GAIN = 16                                                        |     |       |     |      |

| SNR <sub>DIFF333</sub> |                                            | $4.5 \text{ V} < \text{V}_{\text{DDA}SD} < 5.5 \text{ V}^{8, 9}$ | 71  | -     | —   | dE   |

|                        | differential mode, 333<br>Ksps output rate | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 1                                                         |     |       |     |      |

|                        |                                            | $4.5 \text{ V} < \text{V}_{\text{DDA}SD} < 5.5 \text{ V}^{8, 9}$ | 70  | -     | —   |      |

|                        |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 2                                                         |     |       |     |      |

|                        |                                            | $4.5 \text{ V} < \text{V}_{\text{DDA}SD} < 5.5 \text{ V}^{8, 9}$ | 68  | -     | _   |      |

|                        |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |      |

|                        |                                            | GAIN = 4                                                         |     |       |     |      |

|                        |                                            | $4.5 \text{ V} < \text{V}_{\text{DDA}SD} < 5.5 \text{ V}^{8, 9}$ | 65  | _     | _   |      |

|                        |                                            | $V_{RH_SD} = V_{DDA_SD}$                                         |     |       |     |      |

|                        |                                            | GAIN = 8                                                         |     |       |     |      |

|                        |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 62  | _     | _   |      |

|                        |                                            | $V_{RH\_SD} = V_{DDA\_SD}$                                       |     |       |     |      |

|                        |                                            | GAIN = 16                                                        |     |       |     |      |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Cumhal                   | Parameter                                                        | Conditions                                          |      | Value |     | 11   |

|--------------------------|------------------------------------------------------------------|-----------------------------------------------------|------|-------|-----|------|

| Symbol                   | Falameter                                                        | Conditions                                          | Min  | Тур   | Max | Unit |

| SNR <sub>SE150</sub>     | Signal to noise ratio in single ended mode, 150 Ksps output rate | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 72   | _     | _   | dB   |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | GAIN = 1                                            |      |       |     |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 69   | _     | _   |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | GAIN = 2                                            |      |       |     |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 66   | _     | _   |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | GAIN = 4                                            |      |       |     |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 62   | _     | _   |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | GAIN = 8                                            |      |       |     |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup> | 54   | _     | _   |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | GAIN = 16                                           |      |       |     |      |

| SINAD <sub>DIFF150</sub> | Signal to noise and                                              | Gain = 1                                            | 72   | -     | —   | dBFS |

|                          | distortion ratio in differential mode, 150                       | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          | Ksps output rate                                                 | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | Gain = 2                                            | 72   | -     | —   |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | Gain = 4                                            | 69   | —     | —   |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | Gain = 8                                            | 68.8 | —     | _   |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

|                          |                                                                  | Gain = 16                                           | 64.8 | —     | _   |      |

|                          |                                                                  | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V                 |      |       |     |      |

|                          |                                                                  | $V_{RH_SD} = V_{DDA_SD}$                            |      |       |     |      |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Cumhal                 | Devementer                                                     | Conditions                          |     | Value |     | L Insite |  |

|------------------------|----------------------------------------------------------------|-------------------------------------|-----|-------|-----|----------|--|

| Symbol                 | Parameter                                                      | Conditions                          | Min | Тур   | Мах | Unit     |  |

| THD <sub>DIFF150</sub> | Total harmonic<br>distortion in differential<br>mode, 150 Ksps | Gain = 1                            | 65  | _     | _   | dBFS     |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        | output rate                                                    | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 2                            | 68  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 4                            | 74  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 8                            | 80  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 16                           | 80  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

| THD <sub>DIFF333</sub> | Total harmonic                                                 | Gain = 1                            | 65  | _     | —   | dBFS     |  |

|                        | distortion in differential mode, 333 Ksps                      | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        | output rate                                                    | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 2                            | 68  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 4                            | 74  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 8                            | 80  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

|                        |                                                                | Gain = 16                           | 80  | _     | _   |          |  |

|                        |                                                                | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |          |  |

|                        |                                                                | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |          |  |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Symbol                | Parameter                                         | Conditions                          | Value |                       |                             |      |

|-----------------------|---------------------------------------------------|-------------------------------------|-------|-----------------------|-----------------------------|------|

| Symbol                | Farameter                                         | Min                                 |       | Typ Max               |                             | Unit |

| THD <sub>SE150</sub>  | Total harmonic                                    | Gain = 1                            | 68    | _                     | —                           | dBFS |

|                       | distortion in single-<br>ended mode, 150          | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |       |                       |                             |      |

|                       | Ksps output rate                                  | $V_{RH_{SD}} = V_{DDA_{SD}}$        |       |                       |                             |      |

|                       |                                                   | Gain = 2                            | 68    | -                     | —                           |      |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |       |                       |                             |      |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |       |                       |                             |      |

|                       |                                                   | Gain = 4                            | 66    |                       | _                           |      |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |       |                       |                             |      |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |       |                       |                             |      |

|                       |                                                   | Gain = 8                            | 68    | _                     |                             |      |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |       |                       |                             |      |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |       |                       |                             |      |

|                       |                                                   | Gain = 16                           | 68    | _                     | _                           |      |

|                       |                                                   | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |       |                       |                             |      |

|                       |                                                   | $V_{RH_{SD}} = V_{DDA_{SD}}$        |       |                       |                             |      |

| SFDR                  | Spurious free dynamic                             |                                     | 60    | _                     | _                           | dB   |

|                       | range                                             |                                     |       |                       |                             |      |

| Z <sub>DIFF</sub>     | Differential input<br>impedance <sup>10, 11</sup> | GAIN = 1                            | 1000  | 1250                  | 1500                        | kΩ   |

|                       |                                                   | GAIN = 2                            | 600   | 800                   | 1000                        |      |

|                       |                                                   | GAIN = 4                            | 300   | 400                   | 500                         |      |

|                       |                                                   | GAIN = 8                            | 200   | 250                   | 300                         |      |

|                       |                                                   | GAIN = 16                           | 200   | 250                   | 300                         |      |

| Z <sub>CM</sub>       | Common Mode input impedance <sup>11, 12</sup>     | GAIN = 1                            | 1400  | 1800                  | 2200                        | kΩ   |

|                       |                                                   | GAIN = 2                            | 1000  | 1300                  | 1600                        |      |

|                       |                                                   | GAIN = 4                            | 700   | 950                   | 1150                        |      |

|                       |                                                   | GAIN = 8                            | 500   | 650                   | 800                         |      |

|                       |                                                   | GAIN = 16                           | 500   | 650                   | 800                         |      |

| R <sub>BIAS</sub>     | Bare bias resistance                              | —                                   | 110   | 144                   | 180                         | kΩ   |

| $\Delta V_{INTCM}$    | Common Mode input reference voltage <sup>13</sup> | —                                   | -12   | —                     | +12                         | %    |

| V <sub>BIAS</sub>     | Bias voltage                                      | —                                   | _     | V <sub>RH_SD</sub> /2 | _                           | V    |

| $\delta V_{BIAS}$     | Bias voltage accuracy                             | —                                   | -2.5  | _                     | +2.5                        | %    |

| CMRR                  | Common mode rejection ratio                       | _                                   | 20    | _                     | —                           | dB   |

| R <sub>Caaf</sub>     | Anti-aliasing filter                              | External series resistance          |       |                       | 20                          | kΩ   |

|                       |                                                   | Filter capacitances                 | 220   |                       | _                           | pF   |

| f <sub>PASSBAND</sub> | Pass band <sup>9</sup>                            | —                                   | 0.01  |                       | 0.333 * f <sub>ADCD_S</sub> | kHz  |

| δ <sub>RIPPLE</sub>   | Pass band ripple <sup>14</sup>                    | 0.333 * f <sub>ADCD_S</sub>         | 1     |                       | 1                           | %    |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page...

## Table 21. LFAST transmitter electrical characteristics<sup>1</sup> (continued)

| Symphol              | Parameter                                                       | Conditions               |      | Unit |      |    |

|----------------------|-----------------------------------------------------------------|--------------------------|------|------|------|----|

| Symbol               | Parameter                                                       | Conditions               | Min  | Тур  | Мах  |    |

| V <sub>OS</sub>      | Common mode voltage                                             | —                        | 1.08 |      | 1.32 | V  |

| IV <sub>OD</sub> I   | Differential output voltage swing (terminated) <sup>2,3</sup>   | —                        | 110  | 200  | 285  | mV |

| t <sub>TR</sub>      | Rise/fall time (10% – 90% of swing) <sup>2</sup> , <sup>3</sup> | —                        | 0.26 |      | 1.5  | ns |

| CL                   | External lumped differential load capacitance <sup>2</sup>      | V <sub>DDE</sub> = 4.5 V | —    | —    | 12.0 | pF |

|                      |                                                                 | V <sub>DDE</sub> = 3.0 V | _    |      | 8.5  |    |

| I <sub>LVDS_TX</sub> | Transmitter DC current consumption                              | Enabled                  |      | —    | 3.2  | mA |

1. The LFAST pad electrical characteristics are based on worst-case internal capacitance values shown in Figure 11.

Valid for maximum data rate f<sub>DATA</sub>. Value given is the capacitance on each terminal of the differential pair, as shown in Figure 11.

3. Valid for maximum external load CL.

## Table 22. MSC/DSPI LVDS transmitter electrical characteristics<sup>1</sup>

| Symbol               | Parameter                                                     | Conditions               |      | Unit |      |      |

|----------------------|---------------------------------------------------------------|--------------------------|------|------|------|------|

| Symbol               | Farameter                                                     | Conditions               | Min  | Тур  | Мах  |      |

| f <sub>DATA</sub>    | Data rate                                                     | —                        | —    | —    | 80   | Mbps |

| V <sub>OS</sub>      | Common mode voltage                                           | —                        | 1.08 | —    | 1.32 | V    |

| IV <sub>OD</sub> I   | Differential output voltage swing (terminated) <sup>2,3</sup> | —                        | 150  | 200  | 400  | mV   |

| t <sub>TR</sub>      | Rise/Fall time (10%–90% of swing) <sup>2</sup> , <sup>3</sup> | —                        | 0.8  | —    | 4.0  | ns   |

| CL                   | External lumped differential load capacitance <sup>2</sup>    | V <sub>DDE</sub> = 4.5 V | _    | _    | 50   | pF   |

|                      |                                                               | V <sub>DDE</sub> = 3.0 V | —    | —    | 39   |      |

| I <sub>LVDS_TX</sub> | Transmitter DC current consumption                            | Enabled                  | _    | _    | 4.0  | mA   |

1. The MSC and DSPI LVDS pad electrical characteristics are based on the application circuit and typical worst-case internal capacitance values given in Figure 11.

Valid for maximum data rate f<sub>DATA</sub>. Value given is the capacitance on each terminal of the differential pair, as shown in Figure 11.

3. Valid for maximum external load C<sub>L</sub>.

The following table describes the supply stability capacitances required on the device for proper operation.

| Symbol                    | Parameter                                                                       | Conditions | Value <sup>1</sup> |                  |     | Unit |

|---------------------------|---------------------------------------------------------------------------------|------------|--------------------|------------------|-----|------|

| Symbol                    | Farameter                                                                       | Conditions | Min                | Тур              | Max | Unit |

| C <sub>LV</sub>           | Minimum V <sub>DD</sub> external bulk capacitance <sup>2, 3</sup>               | LDO mode   | 4.7                | _                | —   | μF   |

|                           |                                                                                 | SMPS mode  | 22                 | _                | _   | μF   |

| C <sub>SMPSPWR</sub>      | Minimum SMPS driver supply capacitance                                          | —          | 22                 | _                | _   | μF   |

| C <sub>HV_PMC</sub>       | Minimum V <sub>DDPMC</sub> external bulk capacitance <sup>4, 5</sup>            | LDO mode   | 22                 | _                | —   | μF   |

|                           |                                                                                 | SMPS mode  | 22                 | _                | —   | μF   |

| C <sub>HV_IO</sub>        | Minimum V <sub>DDEx</sub> /V <sub>DDEHx</sub> external capacitance <sup>2</sup> | —          | —                  | 4.7 <sup>6</sup> | _   | μF   |

| C <sub>HV_FLA</sub>       | Minimum V <sub>DD_FLA</sub> external capacitance <sup>7</sup>                   | —          | 1.0                | 2.0              | _   | μF   |

| C <sub>HV_ADC_EQA/B</sub> | Minimum V <sub>DDA_EQA/B</sub> external capacitance <sup>8</sup>                | —          | 0.01               | _                | _   | μF   |

| C <sub>REFEQ</sub>        | Minimum REF <sub>BYPCA/B</sub> external capacitance <sup>9</sup>                | —          | 0.01               | _                |     | μF   |

| C <sub>HV_ADC_SD</sub>    | Minimum V <sub>DDA_SD</sub> external capacitance <sup>10</sup>                  | —          | 1.0                | 2.2              |     | μF   |

Table 28. Device power supply integration

1. See Figure 14 for capacitor integration.

- 2. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 3. Each V<sub>DD</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 4. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 5. Each V<sub>DDPMC</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 6. The actual capacitance should be selected based on the I/O usage in order to keep the supply voltage within its operating range.

- 7. The recommended flash regulator composition capacitor is 2.0  $\mu$ F typical X7R or X5R, with -50% and +35% as min and max. This puts the min cap at 0.75  $\mu$ F.

- For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_EQA/B</sub> and V<sub>SSA\_EQ</sub>.

- 9. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 µF between REF<sub>BYPCA/B</sub> and V<sub>SS</sub>.

- 10. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_SD</sub> and V<sub>SSA\_SD</sub>.

# 3.11.3 Device voltage monitoring

The LVD/HVDs for the device and their levels are given in the following table. Voltage monitoring threshold definition is provided in the following figure.

# 3.12 Flash memory specifications

# 3.12.1 Flash memory program and erase specifications

NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 30 shows the estimated Program/Erase times.

| Symbol               | Symbol Characteristic <sup>1</sup>    |     |                               | tory<br>nming <sup>3, 4</sup>   | F                                      | ield Upda                 | te                  | Unit |

|----------------------|---------------------------------------|-----|-------------------------------|---------------------------------|----------------------------------------|---------------------------|---------------------|------|

|                      |                                       |     | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifetime Max <sup>6</sup> |                     |      |

|                      |                                       |     | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles         | ≤ 250,000<br>cycles |      |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time     | 43  | 100                           | 150                             | 55                                     | 500                       |                     | μs   |

| t <sub>ppgm</sub>    | Page (256 bits) program time          | 73  | 200                           | 300                             | 108                                    | 500                       |                     | μs   |

| t <sub>qppgm</sub>   | Quad-page (1024 bits) program<br>time | 268 | 800                           | 1,200                           | 396                                    | 2,000                     |                     | μs   |

| t <sub>16kers</sub>  | 16 KB Block erase time                | 168 | 290                           | 320                             | 250                                    | 1,000                     |                     | ms   |

| t <sub>16kpgm</sub>  | 16 KB Block program time              | 34  | 45                            | 50                              | 40                                     | 1,000                     |                     | ms   |

| t <sub>32kers</sub>  | 32 KB Block erase time                | 217 | 360                           | 390                             | 310                                    | 1,200                     |                     | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time              | 69  | 100                           | 110                             | 90                                     | 1,200                     |                     | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time                | 315 | 490                           | 590                             | 420                                    | 1,600                     |                     | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time              | 138 | 180                           | 210                             | 170                                    | 1,600                     |                     | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time               | 884 | 1,520                         | 2,030                           | 1,080                                  | 4,000                     | _                   | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time             | 552 | 720                           | 880                             | 650                                    | 4,000                     | _                   | ms   |

Table 30.

Flash memory program and erase specifications

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

- 3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical                                       | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------|

| t <sub>done</sub>    | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.                                                                                                                          | —                                                | _                                             | 5                                                | ns    |

| t <sub>dones</sub>   | program/erase until the MCR-DONE bit is set to a 1.                                                                                                                                                                                   |                                                  | 16<br>plus four<br>system<br>clock<br>periods | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>drov</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  |                                               | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP |                                                  |                                               | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       | _                                                |                                               | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods | -                                             | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

## Table 33. Flash memory AC timing specifications (continued)

# 3.12.6 Flash memory read wait-state and address-pipeline control settings

The following table describes the recommended settings of the Flash Memory Controller's PFCR1[RWSC] and PFCR1[APC] fields at various flash memory operating frequencies, based on specified intrinsic flash memory access times of the C55FMC array at 150°C.

Table 34.

Flash memory read wait-state and address-pipeline control combinations

| Flash memory frequency                           | RWSC | APC | Flash memory read latency on<br>mini-cache miss (# of f <sub>PLATF</sub><br>clock periods) | Flash memory read latency on<br>mini-cache hit (# of f <sub>PLATF</sub> clock<br>periods) |

|--------------------------------------------------|------|-----|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 0 MHz < f <sub>PLATF</sub> ≤ 33 MHz              | 0    | 0   | 3                                                                                          | 1                                                                                         |

| $33 \text{ MHz} < f_{PLATF} \le 100 \text{ MHz}$ | 2    | 1   | 5                                                                                          | 1                                                                                         |

Table continues on the next page...

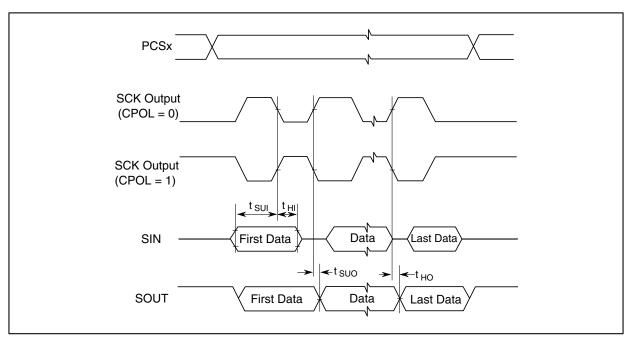

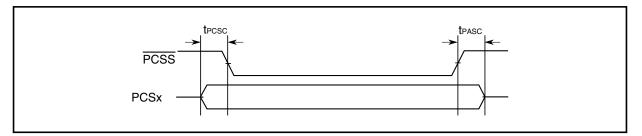

Figure 33. DSPI CMOS master mode – classic timing, CPHA = 1

Figure 34. DSPI PCS strobe (PCSS) timing (master mode)

### 3.13.9.1.2 DSPI CMOS Master Mode – Modified Timing Table 44. DSPI CMOS master modified timing (full duplex and output only) – MTFE = 1, CPHA = 0 or 1<sup>1</sup>

| # | Symbol Characteristic |                  | Condition <sup>2</sup> | Condition <sup>2</sup> |                                   | Value <sup>3</sup> |      |  |

|---|-----------------------|------------------|------------------------|------------------------|-----------------------------------|--------------------|------|--|

| # | Symbol                | Characteristic   | Pad drive <sup>4</sup> | Load (C <sub>L</sub> ) | Min                               | Мах                | Unit |  |

| 1 | t <sub>SCK</sub>      | SCK cycle time   | PCR[SRC]=11b           | 25 pF                  | 33.0                              | —                  | ns   |  |

|   |                       |                  | PCR[SRC]=10b           | 50 pF                  | 80.0                              | _                  |      |  |

|   |                       |                  | PCR[SRC]=01b           | 50 pF                  | 200.0                             |                    |      |  |

| 2 | t <sub>CSC</sub>      | PCS to SCK delay | PCR[SRC]=11b           | 25 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 16$ |                    | ns   |  |

|   |                       |                  | PCR[SRC]=10b           | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 16$ | _                  |      |  |

|   |                       |                  | PCR[SRC]=01b           | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 18$ |                    |      |  |

|   |                       |                  | PCS: PCR[SRC]=01b      | 50 pF                  | $(N^5 \times t_{SYS}^{, 6}) - 45$ | _                  |      |  |

|   |                       |                  | SCK: PCR[SRC]=10b      |                        |                                   |                    |      |  |

Table continues on the next page ...

## 3.13.9.1.4 DSPI Master Mode – Output Only

# Table 46. DSPI LVDS master timing — output only — timed serial bus mode TSB = 1 or ITSB = 1, CPOL = 0 or 1, continuous SCK clock<sup>1, 2</sup>

| " | Cumbal                               | Characteriatia                                               | Condit                 | ion <sup>3</sup>               | Va                      | lue <sup>4</sup>        | 11     |  |

|---|--------------------------------------|--------------------------------------------------------------|------------------------|--------------------------------|-------------------------|-------------------------|--------|--|

| # | Symbol                               | Characteristic                                               | Pad drive <sup>5</sup> | Load (C <sub>L</sub> )         | Min                     | Мах                     | - Unit |  |

| 1 | t <sub>SCK</sub>                     | SCK cycle time                                               | LVDS                   | 15 pF to 50 pF<br>differential | 25                      | —                       | ns     |  |