Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 201010                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga110-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

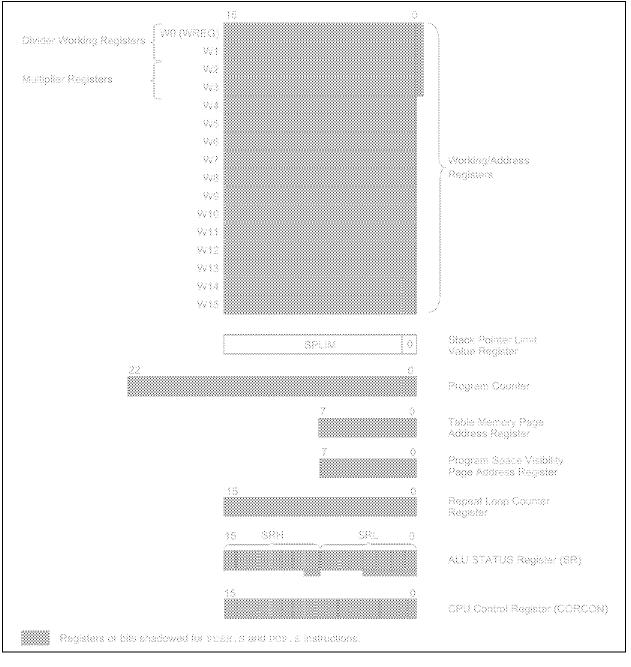

### TABLE 3-1: CPU CORE REGISTERS

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

#### FIGURE 3-2: PROGRAMMER'S MODEL

#### TABLE 4-27: SYSTEM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON         | 0740 | TRAPR  | IOPUWR | —      | _      |        | —      | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON       | 0742 | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | —     | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV       | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | —       | —      | —      |       | —     | _      | _      | —     | 0100          |

| OSCTUN       | 0748 | —      | —      | —      | _      | —      | —      | —      | —      | —       | —      | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON      | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 |         | -      | —      | _     | -     | _      | _      | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-28: NVM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|--------|--------|--------|---------------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  |        | _      |        | _     | _     |       | ERASE |       |       | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY       | 0766 | -      | —      | _      |        | _      | _      | _     | _     |       |       |       | NVMK  | EY<7:0> |        |        |        | 0000                |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-29: PMD REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | -      | —      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      |        | ADC1MD | 0000          |

| PMD2         | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0774 | _      | —      | _      | —      | —      | CMPMD  | RTCCMD | PMPMD | CRCMD  | —     | —     | —      | U3MD   | I2C3MD | I2C2MD | —      | 0000          |

| PMD4         | 0776 | _      | _      | _      | _      | —      | —      | _      | _     | _      | _     | U4MD  | _      | REFOMD | CTMUMD | LVDMD  | _      | 0000          |

| PMD5         | 0778 | _      | —      | —      | —      | —      | —      | —      | IC9MD | —      | —     | —     | —      | —      | —      | _      | OC9MD  | 0000          |

| PMD6         | 077A | _      | —      | _      | -      | -      | -      | _      | —     | -      |       | _     | _      | _      | _      | _      | SPI3MD | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0        | U-0                                 | U-0                                                                                                                | U-0             | U-0               | U-0    | U-0              | U-0   |  |  |  |

|--------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|--------|------------------|-------|--|--|--|

| NSTDIS       | —                                   |                                                                                                                    |                 | —                 | —      | —                | —     |  |  |  |

| bit 15       |                                     |                                                                                                                    |                 |                   |        |                  | bit 8 |  |  |  |

|              |                                     |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

| U-0          | U-0                                 | U-0                                                                                                                | R/W-0           | R/W-0             | R/W-0  | R/W-0            | U-0   |  |  |  |

|              | —                                   |                                                                                                                    | MATHERR         | ADDRERR           | STKERR | OSCFAIL          | —     |  |  |  |

| bit 7        |                                     |                                                                                                                    |                 |                   |        |                  | bit 0 |  |  |  |

|              |                                     |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

| Legend:      |                                     |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

| R = Readab   | ole bit                             | W = Writable                                                                                                       | bit             | U = Unimplem      |        | d as '0'         |       |  |  |  |

| -n = Value a | at POR                              | '1' = Bit is set                                                                                                   |                 | '0' = Bit is clea | ired   | x = Bit is unkno | own   |  |  |  |

|              |                                     |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

| bit 15       |                                     | rrupt Nesting E                                                                                                    |                 |                   |        |                  |       |  |  |  |

|              |                                     | nesting is disat<br>nesting is enab                                                                                |                 |                   |        |                  |       |  |  |  |

| bit 14-5     | Unimplement                         | ted: Read as '                                                                                                     | 0'              |                   |        |                  |       |  |  |  |

| bit 4        | MATHERR: A                          | rithmetic Error                                                                                                    | Trap Status bi  | t                 |        |                  |       |  |  |  |

|              |                                     | trap has occur<br>trap has not oc                                                                                  |                 |                   |        |                  |       |  |  |  |

| bit 3        |                                     | Address Error                                                                                                      |                 |                   |        |                  |       |  |  |  |

| DIL D        |                                     | error trap has c                                                                                                   | •               |                   |        |                  |       |  |  |  |

|              |                                     | error trap has c                                                                                                   |                 |                   |        |                  |       |  |  |  |

| bit 2        | STKERR: Stack Error Trap Status bit |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

|              | 1 = Stack erro                      | or trap has occ                                                                                                    | urred           |                   |        |                  |       |  |  |  |

|              | 0 = Stack erro                      | or trap has not                                                                                                    | occurred        |                   |        |                  |       |  |  |  |

| bit 1        |                                     |                                                                                                                    | Trap Status bit | t                 |        |                  |       |  |  |  |

|              |                                     | <ul> <li>1 = Oscillator failure trap has occurred</li> <li>0 = Oscillator failure trap has not occurred</li> </ul> |                 |                   |        |                  |       |  |  |  |

| 1.1.0        |                                     |                                                                                                                    |                 |                   |        |                  |       |  |  |  |

| bit 0        | Unimplement                         | ted: Read as '                                                                                                     | 0.              |                   |        |                  |       |  |  |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| <b>REGISTER 7-19:</b> IPC2: INTERRUPT PRIORITY CONTROL REGISTER |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| U-0          | R/W-1                                                      | R/W-0                                                            | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

|--------------|------------------------------------------------------------|------------------------------------------------------------------|-------------------|------------------|-----------------|-----------------|---------|--|--|--|--|--|--|--|

|              | U1RXIP2                                                    | U1RXIP1                                                          | U1RXIP0           |                  | SPI1IP2         | SPI1IP1         | SPI1IP0 |  |  |  |  |  |  |  |

| oit 15       |                                                            |                                                                  |                   |                  |                 |                 | bit     |  |  |  |  |  |  |  |

|              |                                                            |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                            | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

| —            | SPF1IP2                                                    | SPF1IP1                                                          | SPF1IP0           | —                | T3IP2           | T3IP1           | T3IP0   |  |  |  |  |  |  |  |

| bit 7        |                                                            |                                                                  |                   |                  |                 |                 | bit     |  |  |  |  |  |  |  |

|              |                                                            |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| Legend:      |                                                            |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| R = Readab   | ole bit                                                    | W = Writable                                                     | bit               | U = Unimple      | mented bit, rea | d as '0'        |         |  |  |  |  |  |  |  |

| -n = Value a | It POR                                                     | '1' = Bit is set                                                 |                   | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |  |  |  |

| L:1 4 F      | Unimalaman                                                 | tad: Daad as (                                                   | o'                |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 15       | -                                                          | ted: Read as '                                                   |                   | Driarity bita    |                 |                 |         |  |  |  |  |  |  |  |

| bit 14-12    |                                                            | : UART1 Rece<br>pt is priority 7 (I                              | =                 | -                |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  | ingricor priority |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          | ntio maiority 1                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | 001 = Interru<br>000 = Interru                             |                                                                  | abled             |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 11       |                                                            | 000 = Interrupt source is disabled<br>Unimplemented: Read as '0' |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 10-8     | -                                                          | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          | p                                                                |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                         | nt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                            | pt is priority i<br>pt source is dis                             | abled             |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 7        |                                                            | ted: Read as '                                                   |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 6-4      | -                                                          | SPI1 Fault In                                                    |                   | bits             |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                            | pt is priority 7 (I                                              |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  | /                 | • /              |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                         | pt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                            | pt source is dis                                                 | abled             |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 3        | Unimplemen                                                 | ted: Read as '                                                   | o'                |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 2-0      | T3IP<2:0>: ⊺                                               | imer3 Interrupt                                                  | Priority bits     |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | 111 = Interru                                              | pt is priority 7 (I                                              | highest priority  | interrupt)       |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                          |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                         | pt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

### REGISTER 7-25: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | SPI2IP2 | SPI2IP1 | SPI2IP0 | —   | SPF2IP2 | SPF2IP1 | SPF2IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:                                  |            |                                 |                       |                    |

|------------------------------------------|------------|---------------------------------|-----------------------|--------------------|

| R = Readab                               | ole bit    | W = Writable bit                | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR                        |            | '1' = Bit is set                | '0' = Bit is cleared  | x = Bit is unknown |

|                                          |            |                                 |                       |                    |

| bit 15-7                                 | Unimplen   | nented: Read as '0'             |                       |                    |

| bit 6-4 SPI2IP<2:0>: SPI2 Event Interrup |            |                                 | iority bits           |                    |

|                                          | 111 = Inte | errupt is priority 7 (highest p | riority interrupt)    |                    |

|                                          | •          |                                 |                       |                    |

|                                          | •          |                                 |                       |                    |

|                                          | •          |                                 |                       |                    |

|                                          | 001 = Inte | errupt is priority 1            |                       |                    |

| 000 = Interrupt sou                      |            | errupt source is disabled       |                       |                    |

| bit 3                                    | Unimplen   | nented: Read as '0'             |                       |                    |

| bit 2-0 | SPF2IP<2:0>: SPI2 Fault Interrupt Priority bits         |

|---------|---------------------------------------------------------|

|         | 111 – Interrupt is priority 7 (highest priority interru |

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

# 10.0 I/O PORTS

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |

|-------|------------------------------------------------------------------------------------|

|       | $\frac{1}{102}$                                                                    |

|       | intended to be a comprehensive reference                                           |

|       | source. For more information, refer to the                                         |

|       | "PIC24F Family Reference Manual",                                                  |

|       | Section 12. "I/O Ports with Peripheral                                             |

|       | Pin Select (PPS)" (DS39711).                                                       |

All of the device pins (except VDD, VSS, MCLR and OSCI/CLKI) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

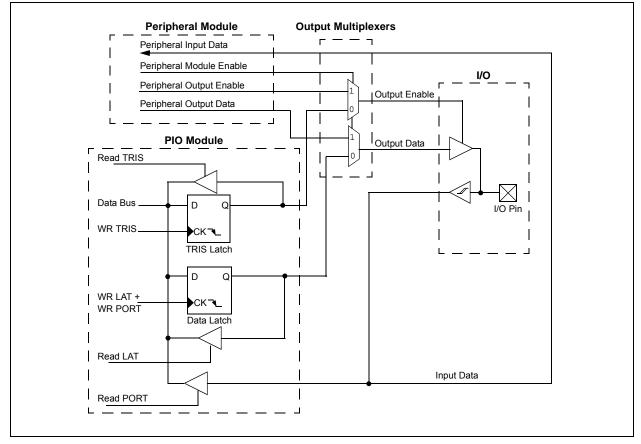

### 10.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRIS) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LAT and TRIS registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is regarded as a dedicated port because there is no other competing source of outputs.

#### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

## 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

Peripheral Pin Select is not available for  $I^2C^{TM}$ , change notification inputs, RTCC alarm outputs or peripherals with analog inputs.

A key difference between pin select and non pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g. OC, UART Transmit) take priority over general purpose digital functions on a pin, such as PMP and port I/O. Specialized digital outputs, such as USB functionality, will take priority over PPS outputs on the same pin. The pin diagrams provided at the beginning of this data sheet list peripheral outputs in order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin-selectable peripheral inputs never take ownership of a pin. The pin's output buffer is controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 10.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

# 10.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-21). Each register contains two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Select options supported by the device.

### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 10-22 through Register 10-37). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-3).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

### 10.4.3.3 Alternate Fixed Pin Mapping

To provide a migration option from earlier high pin count PIC24F devices, PIC24FJ256GA110 family devices implement an additional option for mapping the clock output (SCK) of SPI1. This option permits users to map SCK10UT specifically to the fixed pin function, ASCK1. The SCK1CM bit (ALTRP<0>) controls this mapping; setting the bit maps SCK10UT to ASCK1.

The SCK1CM bit must be set (= 1) before enabling the SPI module. It must remain set while transactions using SPI1 are in progress, in order to prevent transmission errors; when the module is disabled, the bit must be cleared. Additionally, no other RPOUT register should be configured to output the SCK1OUT function while SCK1CM is set.

x = Bit is unknown

#### REGISTER 10-21: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| —            |       | —            |       | —            | —                | _        | —     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| U-0          | U-0   | R/W-1        | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

| —            | _     | SS3R5        | SS3R4 | SS3R3        | SS3R2            | SS3R1    | SS3R0 |

| bit 7        |       |              |       |              |                  | bit 0    |       |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplem | nented bit, read | l as '0' |       |

'0' = Bit is cleared

bit 15-6 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS31IN) to Corresponding RPn or RPIn Pin bits

#### REGISTER 10-36: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

|        | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0    |

|--------|--------|--------|--------|--------|--------|--------|-----|--------|

| bit 15 | RP29R0 | RP29R1 | RP29R2 | RP29R3 | RP29R4 | RP29R5 | —   | —      |

|        | bit 8  |        |        |        |        |        |     | bit 15 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP29R<5:0>: RP29 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP29 (see Table 10-3 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP28R<5:0>: RP28 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP28 (see Table 10-3 for peripheral function numbers). |

### REGISTER 10-37: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15

| U-0    | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> |

| bit 15 |     |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 |

| bit 7 | •   |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP31R<5:0>:** RP31 Output Pin Mapping bits<sup>(1)</sup><br/>Peripheral output number n is assigned to pin, RP31 (see Table 10-3 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP30R<5:0>:** RP30 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP30 (see Table 10-3 for peripheral function numbers).

Note 1: Unimplemented in 64-pin and 80-pin devices; read as '0'.

#### REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL 1 REGISTER

| U-0        | U-0                                                                                                                                         | R/W-0            | R/W-0                                                   | R/W-0             | R/W-0               | U-0                 | U-0                 |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------|-------------------|---------------------|---------------------|---------------------|--|--|--|--|

|            | _                                                                                                                                           | OCSIDL           | OCTSEL2                                                 | OCTSEL1           | OCTSEL0             | —                   | —                   |  |  |  |  |

| bit 15     |                                                                                                                                             |                  |                                                         |                   |                     |                     | bit 8               |  |  |  |  |

| R/W-0      | U-0                                                                                                                                         | U-0              | R/W-0, HCS                                              | R/W-0             | R/W-0               | R/W-0               | R/W-0               |  |  |  |  |

| ENFLT0     |                                                                                                                                             |                  | OCFLT0                                                  | TRIGMODE          | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup> |  |  |  |  |

| bit 7      | •                                                                                                                                           | -                | •                                                       | •                 | •                   | •                   | bit C               |  |  |  |  |

| Legend:    |                                                                                                                                             | HCS = Hardw      | vare Clearable/S                                        | Settable bit      |                     |                     |                     |  |  |  |  |

| R = Reada  | able bit                                                                                                                                    | W = Writable     | bit                                                     | U = Unimplem      | ented bit, read     | as '0'              |                     |  |  |  |  |

| -n = Value | at POR                                                                                                                                      | '1' = Bit is set |                                                         | '0' = Bit is clea | ared                | x = Bit is unkn     | own                 |  |  |  |  |

| bit 15-14  | Unimplemen                                                                                                                                  | ted: Read as '   | כי                                                      |                   |                     |                     |                     |  |  |  |  |

| bit 13     | OCSIDL: Sto                                                                                                                                 | p Output Comp    | are x in Idle Mo                                        | de Control bit    |                     |                     |                     |  |  |  |  |

|            | •                                                                                                                                           | •                | in CPU Idle mo                                          |                   |                     |                     |                     |  |  |  |  |

|            | -                                                                                                                                           |                  | nues to operate                                         |                   | ode                 |                     |                     |  |  |  |  |

| bit 12-10  |                                                                                                                                             | •                | pare x Timer Se                                         | elect bits        |                     |                     |                     |  |  |  |  |

|            | 111 = Periph<br>110 = Reserv                                                                                                                | eral Clock (FCY  | )                                                       |                   |                     |                     |                     |  |  |  |  |

|            | 101 = Reserv                                                                                                                                |                  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            | 100 = Timer1                                                                                                                                |                  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             | 011 = Timer5     |                                                         |                   |                     |                     |                     |  |  |  |  |

|            | 010 = Timer4<br>001 = Timer3                                                                                                                |                  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            | 000 = Timer3                                                                                                                                |                  |                                                         |                   |                     |                     |                     |  |  |  |  |

| bit 9-8    | Unimplemen                                                                                                                                  | ted: Read as '   | כי                                                      |                   |                     |                     |                     |  |  |  |  |

| bit 7      | ENFLT0: Fau                                                                                                                                 | ult 0 Input Enab | le bit                                                  |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             | nput is enabled  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             | nput is disabled |                                                         |                   |                     |                     |                     |  |  |  |  |

| bit 6-5    | -                                                                                                                                           | ted: Read as '   |                                                         |                   |                     |                     |                     |  |  |  |  |

| bit 4      |                                                                                                                                             | /M Fault Condit  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             |                  | s occurred (clean has occurred (                        |                   |                     | M<2:0> = 111)       |                     |  |  |  |  |

| bit 3      | TRIGMODE:                                                                                                                                   | Trigger Status   | Mode Select bit                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             |                  | <6>) is cleared v                                       | vhen OCxRS =      | OCxTMR or in        | software            |                     |  |  |  |  |

|            |                                                                                                                                             | AT is only clear | -                                                       |                   |                     |                     |                     |  |  |  |  |

| bit 2-0    |                                                                                                                                             |                  | e x Mode Select                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             |                  | mode on OCx <sup>(2</sup><br>node on OCx <sup>(2)</sup> | -,                |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             |                  |                                                         | mode: initialize  | OCx pin low, t      | oggle OCx stat      | e continuously      |  |  |  |  |

|            | 101 = Double Compare Continuous Pulse mode: initialize OCx pin low, toggle OCx state continuously<br>on alternate matches of OCxR and OCxRS |                  |                                                         |                   |                     |                     |                     |  |  |  |  |

|            |                                                                                                                                             |                  | gle-Shot mode:                                          | initialize OCx p  | in low, toggle O    | Cx state on ma      | tches of OCxR       |  |  |  |  |

|            |                                                                                                                                             | CxRS for one of  | cycle<br>tinuous Pulse m                                | odo: comparo      | ovente continu      | ously togglo OC     | 'v nin              |  |  |  |  |

|            |                                                                                                                                             |                  | le-Shot mode: i                                         |                   |                     |                     |                     |  |  |  |  |

|            | 001 = Single                                                                                                                                |                  | le-Shot mode: i                                         |                   |                     |                     |                     |  |  |  |  |

| Note 1:    | The OCx output                                                                                                                              | t must also be c |                                                         | available RPn     | pin. For more ii    | nformation, see     | Section 10.4        |  |  |  |  |

| о.         | "Peripheral Pir                                                                                                                             |                  |                                                         | nin controla tha  |                     |                     |                     |  |  |  |  |

| <b>Z</b>   | UUTA DILI CONTO                                                                                                                             | いっ いしょうししみ C     |                                                         | ont controls me   |                     |                     |                     |  |  |  |  |

2: OCFA pin controls OC1-OC4 channels; OCFB pin controls the OC5-OC9 channels. OCxR and OCxRS are double-buffered only in PWM modes.

| U-0                | U-0                                  | U-0                              | R/W-0                                 | R/W-0                 | R/W-0                                  | R/W-0              | R/W-0              |

|--------------------|--------------------------------------|----------------------------------|---------------------------------------|-----------------------|----------------------------------------|--------------------|--------------------|

| _                  |                                      |                                  | DISSCK <sup>(1)</sup>                 | DISSDO <sup>(2)</sup> | MODE16                                 | SMP                | CKE <sup>(3)</sup> |

| oit 15             |                                      |                                  |                                       |                       |                                        |                    | bit                |

| R/W-0              | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0                 | R/W-0                                  | R/W-0              | R/W-0              |

| SSEN <sup>(4</sup> |                                      |                                  | -                                     |                       | -                                      |                    |                    |

| bit 7              | ) CKP                                | MSTEN                            | SPRE2                                 | SPRE1                 | SPRE0                                  | PPRE1              | PPRE0<br>bit       |

|                    |                                      |                                  |                                       |                       |                                        |                    | bit                |

| Legend:            |                                      |                                  |                                       |                       |                                        |                    |                    |

| R = Reada          | able bit                             | W = Writable                     | bit                                   | U = Unimplem          | ented bit, read                        | as '0'             |                    |

| -n = Value         | at POR                               | '1' = Bit is set                 |                                       | '0' = Bit is clea     | ared                                   | x = Bit is unkn    | own                |

| bit 15-13          | Unimplemen                           | ted: Read as '                   | 0'                                    |                       |                                        |                    |                    |

| bit 12             | =                                    |                                  | bit (SPI Master                       | modes only)(1)        |                                        |                    |                    |

| 511 12             | 1 = Internal S                       | -                                | abled; pin funct                      | • •                   |                                        |                    |                    |

| bit 11             |                                      | able SDOx pin                    |                                       |                       |                                        |                    |                    |

|                    | 1 = SDOx pi                          |                                  | y module; pin fu                      | inctions as I/O       |                                        |                    |                    |

| bit 10             | -                                    |                                  | nunication Sele                       | ct bit                |                                        |                    |                    |

|                    |                                      | ication is word                  |                                       |                       |                                        |                    |                    |

|                    | 0 = Commun                           | ication is byte-                 | wide (8 bits)                         |                       |                                        |                    |                    |

| bit 9              | SMP: SPIx D                          | ata Input Sam                    | ole Phase bit                         |                       |                                        |                    |                    |

|                    |                                      | a sampled at e                   | nd of data outp<br>niddle of data o   |                       |                                        |                    |                    |

|                    | Slave mode:                          |                                  | SPIx is used in                       |                       |                                        |                    |                    |

| bit 8              |                                      | lock Edge Sele                   |                                       |                       |                                        |                    |                    |

|                    | 1 = Serial ou                        | tput data chan                   | ges on transitio                      |                       | ock state to Idle<br>k state to active |                    |                    |

| bit 7              |                                      |                                  | (Slave mode) b                        |                       |                                        |                    |                    |

|                    |                                      | used for Slave<br>not used by mo | mode<br>dule; pin contro              | olled by port fur     | nction                                 |                    |                    |

| bit 6              | CKP: Clock F                         | Polarity Select I                | oit                                   |                       |                                        |                    |                    |

|                    |                                      |                                  | nigh level; activ<br>ow level; active |                       |                                        |                    |                    |

| bit 5              | MSTEN: Mas                           | ter Mode Enat                    | ole bit                               |                       |                                        |                    |                    |

|                    | 1 = Master m<br>0 = Slave mo         |                                  |                                       |                       |                                        |                    |                    |

| Note 1:            | If DISSCK = 0, S<br>Section 10.4 "Pe |                                  |                                       |                       | pin (or to ASCk                        | (1 for SPI1). Se   | ee                 |

| 2:                 | If DISSDO = 0, S<br>Select" for more | DOx must be o                    |                                       |                       | pin. See Section                       | on 10.4 "Perip     | oheral Pin         |

| 3:                 | The CKE bit is no<br>SPI modes (FRM  | ot used in the F                 | ramed SPI mod                         | les. The user s       | hould program                          | this bit to '0' fo | r the Frame        |

| 4:                 | If SSEN = 1, $\overline{SSx}$        |                                  | gured to an avai                      | ilable RPn pin.       | See Section 10                         | ).4 "Periphera     | I Pin Select       |

# 17.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 17.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 17.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 17.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK to set up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG; this loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

## 17.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 17.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 17.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear to Send (UxCTS) and Request to Send (UxRTS) are the two hardware controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 17.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder. Note that because the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

### 17.7.1 IrDA CLOCK OUTPUT FOR EXTERNAL IrDA SUPPORT

To support external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UART module is enabled. It can be used to support the IrDA codec chip.

# 17.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

#### REGISTER 18-5: PMSTAT: PARALLEL MASTER PORT STATUS REGISTER

|                        | <b>BMMMM</b>                                                                                                                                     |                   |                 |                    |                  |                 |       |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------------------|------------------|-----------------|-------|--|

| R-0                    | R/W-0, HS                                                                                                                                        | U-0               | U-0             | R-0                | R-0              | R-0             | R-0   |  |

| IBF                    | IBOV                                                                                                                                             | —                 | —               | IB3F               | IB2F             | IB1F            | IB0F  |  |

| bit 15                 |                                                                                                                                                  |                   |                 |                    |                  |                 | bit 8 |  |

|                        |                                                                                                                                                  |                   |                 |                    |                  |                 |       |  |

| R-1                    | R/W-0, HS                                                                                                                                        | U-0               | U-0             | R-1                | R-1              | R-1             | R-1   |  |

| OBE                    | OBUF                                                                                                                                             |                   |                 | OB3E               | OB2E             | OB1E            | OB0E  |  |

| bit 7                  |                                                                                                                                                  |                   |                 |                    |                  |                 | bit 0 |  |

| Logondy                |                                                                                                                                                  | HS = Hardwa       | o Cottoblo bit  |                    |                  |                 |       |  |

| Legend:<br>R = Readabl | a hit                                                                                                                                            |                   |                 |                    | anted bit read   |                 |       |  |

|                        |                                                                                                                                                  | W = Writable      | אנ              | U = Unimplem       |                  |                 |       |  |

| -n = Value at          | POR                                                                                                                                              | '1' = Bit is set  |                 | '0' = Bit is clea  | ared             | x = Bit is unkn | own   |  |

| 64.4 <b>F</b>          |                                                                                                                                                  |                   | . :.            |                    |                  |                 |       |  |

| bit 15                 | IBF: Input Buffer Full Status bit                                                                                                                |                   |                 |                    |                  |                 |       |  |

|                        | <ol> <li>All writable input buffer registers are full</li> <li>Some or all of the writable input buffer registers are empty</li> </ol>           |                   |                 |                    |                  |                 |       |  |

| bit 14                 | <b>IBOV:</b> Input Buffer Overflow Status bit                                                                                                    |                   |                 |                    |                  |                 |       |  |

|                        | 1 = A write attempt to a full input byte register occurred (must be cleared in software)                                                         |                   |                 |                    |                  |                 |       |  |

|                        | <ul> <li>a write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul>       |                   |                 |                    |                  |                 |       |  |

| bit 13-12              | Unimplemen                                                                                                                                       | ted: Read as 'd   | )'              |                    |                  |                 |       |  |

| bit 11-8               | IB3F:IB0F Inp                                                                                                                                    | out Buffer x Sta  | tus Full bits   |                    |                  |                 |       |  |

|                        |                                                                                                                                                  |                   |                 | been read (read    | ding buffer will | clear this bit) |       |  |

|                        |                                                                                                                                                  | er does not co    |                 | ad data            |                  |                 |       |  |

| bit 7                  |                                                                                                                                                  | Buffer Empty S    |                 |                    |                  |                 |       |  |

|                        | <ul> <li>1 = All readable output buffer registers are empty</li> <li>0 = Some or all of the readable output buffer registers are full</li> </ul> |                   |                 |                    |                  |                 |       |  |

| bit 6                  |                                                                                                                                                  |                   | -               |                    |                  |                 |       |  |

|                        | <b>OBUF:</b> Output Buffer Underflow Status bit                                                                                                  |                   |                 |                    |                  |                 |       |  |

|                        | <ul> <li>1 = A read occurred from an empty output byte register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul>      |                   |                 |                    |                  |                 |       |  |

| bit 5-4                | Unimplemen                                                                                                                                       | ted: Read as 'd   | )'              |                    |                  |                 |       |  |

| bit 3-0                | OB3E:OB0E                                                                                                                                        | Output Buffer x   | Status Empty    | bits               |                  |                 |       |  |

|                        | 1 = Output bu                                                                                                                                    | uffer is empty (\ | vriting data to | the buffer will cl | ear this bit)    |                 |       |  |

|                        | 0 = Output bu                                                                                                                                    | uffer contains d  | ata that has no | ot been transmit   | ted              |                 |       |  |

#### 19.1.5 ALRMVAL REGISTER MAPPINGS

# REGISTER 19-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0                                                                | U-0              | R/W-x          | R/W-x                              | R/W-x         | R/W-x              | R/W-x   |  |  |

|--------------|--------------------------------------------------------------------|------------------|----------------|------------------------------------|---------------|--------------------|---------|--|--|

|              |                                                                    | _                | MTHTEN0        | MTHONE3                            | MTHONE2       | MTHONE1            | MTHONE0 |  |  |

| bit 15       | •                                                                  | -                | -              | -                                  | -             | -                  | bit 8   |  |  |