Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 192KB (65.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192ga106t-i-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA106 PIC24FJ64GA110

- PIC24FJ128GA106 PIC24F

- PIC24FJ128GA110

PIC24FJ192GA110

- PIC24FJ192GA106PIC24FJ256GA106

- PIC24FJ256GA110

- PIC24FJ64GA108

- PIC24FJ128GA108

- PIC24FJ192GA108

- PIC24FJ256GA108

This family expands on the existing line of Microchip's 16-bit general purpose microcontrollers, combining enhanced computational performance with an expanded and highly configurable peripheral feature set. The PIC24FJ256GA110 family provides a new platform for high-performance applications, which have outgrown their 8-bit platforms, but don't require the power of a digital signal processor.

### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- · Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FJ256GA110 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

• **On-the-Fly Clock Switching:** The device clock can be changed under software control to the Timer1 source or the internal, low-power RC Oscillator during operation, allowing the user to incorporate power-saving ideas into their software designs.

- **Doze Mode Operation:** When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: The microcontroller can suspend all operations, or selectively shut down its core while leaving its peripherals active, with a single instruction in software.

### 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ256GA110 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- A Fast Internal Oscillator (FRC) with a nominal 8 MHz output, which can also be divided under software control to provide clock speeds as low as 31 kHz.

- A Phase Lock Loop (PLL) frequency multiplier available to the external oscillator modes and the FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor. This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

### 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. The consistent pinout scheme used throughout the entire family also aids in migrating from one device to the next larger, or even in jumping from 64-pin to 100-pin devices.

The PIC24F family is pin-compatible with devices in the dsPIC33 and PIC32 families, and shares some compatibility with the pinout schema for PIC18 and dsPIC30 devices. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

|          | Pin Number          |                |                 |     | _                |                                                       |

|----------|---------------------|----------------|-----------------|-----|------------------|-------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer  | Description                                           |

| AN0      | 16                  | 20             | 25              | Ι   | ANA              | A/D Analog Inputs.                                    |

| AN1      | 15                  | 19             | 24              | I   | ANA              |                                                       |

| AN2      | 14                  | 18             | 23              | I   | ANA              |                                                       |

| AN3      | 13                  | 17             | 22              | I   | ANA              |                                                       |

| AN4      | 12                  | 16             | 21              | I   | ANA              |                                                       |

| AN5      | 11                  | 15             | 20              | I   | ANA              |                                                       |

| AN6      | 17                  | 21             | 26              | I   | ANA              |                                                       |

| AN7      | 18                  | 22             | 27              | I   | ANA              |                                                       |

| AN8      | 21                  | 27             | 32              | I   | ANA              |                                                       |

| AN9      | 22                  | 28             | 33              | I   | ANA              |                                                       |

| AN10     | 23                  | 29             | 34              | I   | ANA              |                                                       |

| AN11     | 24                  | 30             | 35              | I   | ANA              |                                                       |

| AN12     | 27                  | 33             | 41              | I   | ANA              |                                                       |

| AN13     | 28                  | 34             | 42              | I   | ANA              |                                                       |

| AN14     | 29                  | 35             | 43              | I   | ANA              |                                                       |

| AN15     | 30                  | 36             | 44              | I   | ANA              |                                                       |

| ASCL2    | —                   | _              | 66              | I/O | l <sup>2</sup> C | Alternate I2C2 Synchronous Serial Clock Input/Output. |

| ASDA2    | —                   | _              | 67              | I/O | l <sup>2</sup> C | Alternate I2C2 Data Input/Output.                     |

| AVDD     | 19                  | 25             | 30              | Р   | —                | Positive Supply for Analog modules.                   |

| AVss     | 20                  | 26             | 31              | Р   | —                | Ground Reference for Analog modules.                  |

| C1INA    | 11                  | 15             | 20              | I   | ANA              | Comparator 1 Input A.                                 |

| C1INB    | 12                  | 16             | 21              | I   | ANA              | Comparator 1 Input B.                                 |

| C1INC    | 5                   | 7              | 11              | I   | ANA              | Comparator 1 Input C.                                 |

| C1IND    | 4                   | 6              | 10              | I   | ANA              | Comparator 1 Input D.                                 |

| C2INA    | 13                  | 17             | 22              | I   | ANA              | Comparator 2 Input A.                                 |

| C2INB    | 14                  | 18             | 23              | I   | ANA              | Comparator 2 Input B.                                 |

| C2INC    | 8                   | 10             | 14              | I   | ANA              | Comparator 2 Input C.                                 |

| C2IND    | 6                   | 8              | 12              | I   | ANA              | Comparator 2 Input D.                                 |

| C3INA    | 55                  | 69             | 84              | I   | ANA              | Comparator 3 Input A.                                 |

| C3INB    | 54                  | 68             | 83              | Ι   | ANA              | Comparator 3 Input B.                                 |

| C3INC    | 48                  | 60             | 74              | Ι   | ANA              | Comparator 3 Input C.                                 |

| C3IND    | 47                  | 59             | 73              | Ι   | ANA              | Comparator 3 Input D.                                 |

| CLKI     | 39                  | 49             | 63              | Ι   | ANA              | Main Clock Input Connection.                          |

| CLKO     | 40                  | 50             | 64              | 0   | _                | System Clock Output.                                  |

| l egend: | TTI = TTI in        |                |                 |     | OT (             | Schmitt Trigger input buffer                          |

| TABLE 1-4: | PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS |

|------------|--------------------------------------------|

|            |                                            |

Legend:

TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

### 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. Depending on the particular device, this is done by setting all bits in the ADnPCFG register(s), or clearing all bit in the ANSx registers.

All PIC24F devices will have either one or more ADnPCFG registers or several ANSx registers (one for each port); no device will have both. Refer to (**choose one xref:** or

#### ) for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the ADC module, as follows:

- For devices with an ADnPCFG register, clear the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

- For devices with ANSx registers, set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ADnPCFG or ANSx registers. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IABLE        | 4-3. | CFUC   |                    |        | K2 MAP |        |        |        |             |              |           |            |                |              |              |       |       |               |

|--------------|------|--------|--------------------|--------|--------|--------|--------|--------|-------------|--------------|-----------|------------|----------------|--------------|--------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6     | Bit 5      | Bit 4          | Bit 3        | Bit 2        | Bit 1 | Bit 0 | All<br>Resets |

| WREG0        | 0000 |        | Working Register 0 |        |        |        |        |        |             |              | 0000      |            |                |              |              |       |       |               |

| WREG1        | 0002 |        |                    |        |        |        |        |        | Working I   | Register 1   |           |            |                |              |              |       |       | 0000          |

| WREG2        | 0004 |        |                    |        |        |        |        |        | Working I   | Register 2   |           |            |                |              |              |       |       | 0000          |

| WREG3        | 0006 |        |                    |        |        |        |        |        | Working I   | Register 3   |           |            |                |              |              |       |       | 0000          |

| WREG4        | 0008 |        |                    |        |        |        |        |        | Working I   | Register 4   |           |            |                |              |              |       |       | 0000          |

| WREG5        | 000A |        |                    |        |        |        |        |        | Working I   | Register 5   |           |            |                |              |              |       |       | 0000          |

| WREG6        | 000C |        |                    |        |        |        |        |        | Working I   | Register 6   |           |            |                |              |              |       |       | 0000          |

| WREG7        | 000E |        |                    |        |        |        |        |        | Working I   | Register 7   |           |            |                |              |              |       |       | 0000          |

| WREG8        | 0010 |        |                    |        |        |        |        |        | Working I   | Register 8   |           |            |                |              |              |       |       | 0000          |

| WREG9        | 0012 |        |                    |        |        |        |        |        | Working I   | Register 9   |           |            |                |              |              |       |       | 0000          |

| WREG10       | 0014 |        |                    |        |        |        |        |        | Working F   | Register 10  |           |            |                |              |              |       |       | 0000          |

| WREG11       | 0016 |        |                    |        |        |        |        |        | Working F   | Register 11  |           |            |                |              |              |       |       | 0000          |

| WREG12       | 0018 |        |                    |        |        |        |        |        | Working F   | Register 12  |           |            |                |              |              |       |       | 0000          |

| WREG13       | 001A |        |                    |        |        |        |        |        | Working F   | Register 13  |           |            |                |              |              |       |       | 0000          |

| WREG14       | 001C |        |                    |        |        |        |        |        | Working F   | Register 14  |           |            |                |              |              |       |       | 0000          |

| WREG15       | 001E |        |                    |        |        |        |        |        | Working F   | Register 15  |           |            |                |              |              |       |       | 0800          |

| SPLIM        | 0020 |        |                    |        |        |        |        | Stack  | Pointer Lin | nit Value Re | egister   |            |                |              |              |       |       | xxxx          |

| PCL          | 002E |        |                    |        |        |        |        | Progra | m Counter I | Low Word F   | Register  |            |                |              |              |       |       | 0000          |

| PCH          | 0030 | _      | —                  | —      | —      | —      | —      | —      | —           |              |           | Progra     | m Counter      | Register Hig | gh Byte      |       |       | 0000          |

| TBLPAG       | 0032 | _      | —                  | —      | —      | —      | _      | —      | —           |              |           | Table N    | lemory Pag     | e Address I  | Register     |       |       | 0000          |

| PSVPAG       | 0034 | _      | —                  | —      | —      | —      | _      | —      | —           |              | P         | rogram Spa | ace Visibility | Page Add     | ress Registe | er    |       | 0000          |

| RCOUNT       | 0036 |        |                    |        |        |        |        | Rep    | eat Loop C  | ounter Reg   | ister     |            |                |              |              |       |       | xxxx          |

| SR           | 0042 | _      |                    | -      | —      | _      |        | —      | DC          | IPL2         | IPL1      | IPL0       | RA             | N            | OV           | Z     | С     | 0000          |

| CORCON       | 0044 | _      |                    | _      | _      | _      | -      | -      | _           | _            | _         | -          | _              | IPL3         | PSV          | —     | _     | 0000          |

| DISICNT      | 0052 | _      |                    |        |        |        |        |        | Disabl      | e Interrupts | Counter R | egister    |                |              |              |       |       | xxxx          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

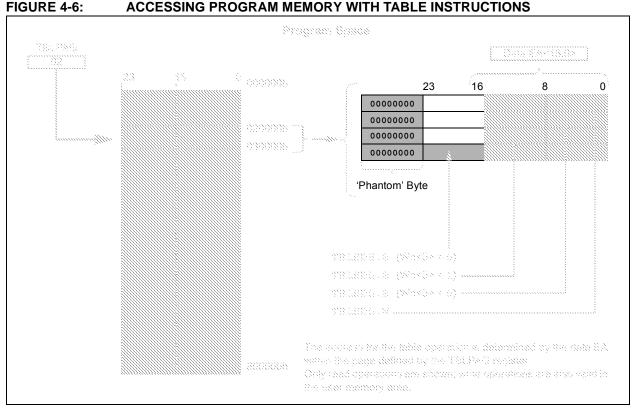

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when the byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address (TBLPAG) register. TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

© 2010 Microchip Technology Inc.

#### REGISTER 7-31: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                 | U-0             | U-0                | R/W-1            | R/W-0                         | R/W-0  |  |

|---------------|---------------|---------------------|-----------------|--------------------|------------------|-------------------------------|--------|--|

| —             | —             | —                   |                 | —                  | RTCIP2           | RTCIP1                        | RTCIP0 |  |

| bit 15        | ·             | ·                   |                 |                    |                  |                               | bit 8  |  |

|               |               |                     |                 |                    |                  |                               |        |  |

| U-0           | U-0           | U-0                 | U-0             | U-0                | U-0              | U-0                           | U-0    |  |

| —             | —             | —                   | _               | —                  | —                | —                             | —      |  |

| bit 7         |               |                     |                 |                    |                  |                               | bit 0  |  |

|               |               |                     |                 |                    |                  |                               |        |  |

| Legend:       |               |                     |                 |                    |                  |                               |        |  |

| R = Readable  | e bit         | W = Writable b      | bit             | U = Unimplem       | nented bit, read | l as '0'                      |        |  |

| -n = Value at | POR           | '1' = Bit is set    |                 | '0' = Bit is clea  | x = Bit is unkr  | <pre>c = Bit is unknown</pre> |        |  |

|               |               |                     |                 |                    |                  |                               |        |  |

| bit 15-11     | Unimplemen    | ted: Read as '0     | 3               |                    |                  |                               |        |  |

| bit 10-8      | RTCIP<2:0>:   | Real-Time Cloc      | k/Calendar In   | terrupt Priority I | bits             |                               |        |  |

|               | 111 = Interru | pt is priority 7 (h | ighest priority | interrupt)         |                  |                               |        |  |

|               | •             |                     |                 |                    |                  |                               |        |  |

|               | •             |                     |                 |                    |                  |                               |        |  |

|               | 001 = Interru | pt is priority 1    |                 |                    |                  |                               |        |  |

|               |               | pt source is disa   | bled            |                    |                  |                               |        |  |

| bit 7-0       | Unimplemen    | ted: Read as '0     | 3               |                    |                  |                               |        |  |

|               |               |                     |                 |                    |                  |                               |        |  |

|                    | R/W-1                                                                                        | R/W-0                                                                                                                                                                              | R/W-0                                                                                   | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|------------------|-----------------|---------|--|--|--|--|

|                    | U3TXIP2                                                                                      | U3TXIP1                                                                                                                                                                            | U3TXIP0                                                                                 |                  | U3RXIP2          | U3RXIP1         | U3RXIP0 |  |  |  |  |

| bit 15             |                                                                                              | •                                                                                                                                                                                  |                                                                                         |                  |                  |                 | bit 8   |  |  |  |  |

| U-0                | R/W-1                                                                                        | R/W-0                                                                                                                                                                              | R/W-0                                                                                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

| _                  | U3ERIP2                                                                                      | U3ERIP1                                                                                                                                                                            | U3ERIP0                                                                                 |                  | _                | —               | _       |  |  |  |  |

| bit 7              |                                                                                              |                                                                                                                                                                                    |                                                                                         |                  |                  |                 | bit (   |  |  |  |  |

| Legend:            |                                                                                              |                                                                                                                                                                                    |                                                                                         |                  |                  |                 |         |  |  |  |  |

| R = Readab         | ole bit                                                                                      | W = Writable                                                                                                                                                                       | bit                                                                                     | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |  |

| -n = Value a       | at POR                                                                                       | '1' = Bit is set                                                                                                                                                                   |                                                                                         | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |  |  |  |  |

|                    |                                                                                              |                                                                                                                                                                                    |                                                                                         |                  |                  |                 |         |  |  |  |  |

| bit 15             | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                                     | י'                                                                                      |                  |                  |                 |         |  |  |  |  |

| bit 14-12          | U3TXIP<2:0>                                                                                  | : UART3 Trans                                                                                                                                                                      | smitter Interrup                                                                        | ot Priority bits |                  |                 |         |  |  |  |  |

|                    | 111 = Interru                                                                                | pt is priority 7 (l                                                                                                                                                                | nighest priority                                                                        | interrupt)       |                  |                 |         |  |  |  |  |

|                    | •                                                                                            |                                                                                                                                                                                    |                                                                                         |                  |                  |                 |         |  |  |  |  |

|                    |                                                                                              |                                                                                                                                                                                    |                                                                                         |                  |                  |                 |         |  |  |  |  |

|                    | 001 = Interru                                                                                |                                                                                                                                                                                    | abled                                                                                   |                  |                  |                 |         |  |  |  |  |

|                    | 000 = Interrupt source is disabled                                                           |                                                                                                                                                                                    |                                                                                         |                  |                  |                 |         |  |  |  |  |

| bit 11             | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                                     | כ'                                                                                      |                  |                  |                 |         |  |  |  |  |

| bit 11<br>bit 10-8 | -                                                                                            | ted: Read as '<br>: UART3 Rece                                                                                                                                                     |                                                                                         | Prioritv bits    |                  |                 |         |  |  |  |  |

|                    | U3RXIP<2:0>                                                                                  | ted: Read as '<br>>: UART3 Rece<br>pt is priority 7 (l                                                                                                                             | eiver Interrupt                                                                         | •                |                  |                 |         |  |  |  |  |

|                    | U3RXIP<2:0>                                                                                  | : UART3 Rece                                                                                                                                                                       | eiver Interrupt                                                                         | •                |                  |                 |         |  |  |  |  |

|                    | U3RXIP<2:0><br>111 = Interru<br>•                                                            | ▶: UART3 Rece<br>pt is priority 7 (I                                                                                                                                               | eiver Interrupt                                                                         | •                |                  |                 |         |  |  |  |  |

|                    | U3RXIP<2:0> 111 = Interru                                                                    | ▶: UART3 Rece<br>pt is priority 7 (I                                                                                                                                               | iver Interrupt                                                                          | •                |                  |                 |         |  |  |  |  |

| bit 10-8           | U3RXIP<2:0> 111 = Interru                                                                    | UART3 Rece<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis                                                                                                          | iver Interrupt<br>nighest priority<br>abled                                             | •                |                  |                 |         |  |  |  |  |

|                    | U3RXIP<2:0> 111 = Interru                                                                    | >: UART3 Rece<br>pt is priority 7 (l<br>pt is priority 1<br>pt source is dis<br><b>ted:</b> Read as 'u                                                                             | iver Interrupt<br>highest priority<br>abled                                             | vinterrupt)      |                  |                 |         |  |  |  |  |

| bit 10-8<br>bit 7  | U3RXIP<2:0><br>111 = Interru                                                                 | UART3 Rece<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis                                                                                                          | iver Interrupt<br>nighest priority<br>abled<br>o <sup>2</sup> Interrupt Prio            | v interrupt)     |                  |                 |         |  |  |  |  |

| bit 10-8<br>bit 7  | U3RXIP<2:0><br>111 = Interru                                                                 | UART3 Rece<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br>ted: Read as 'i<br>>: UART3 Error                                                                     | iver Interrupt<br>nighest priority<br>abled<br>o <sup>2</sup> Interrupt Prio            | v interrupt)     |                  |                 |         |  |  |  |  |

| bit 10-8           | U3RXIP<2:0><br>111 = Interru                                                                 | UART3 Rece<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br>ted: Read as 'i<br>>: UART3 Error                                                                     | iver Interrupt<br>nighest priority<br>abled<br>o <sup>2</sup> Interrupt Prio            | v interrupt)     |                  |                 |         |  |  |  |  |

| bit 10-8<br>bit 7  | U3RXIP<2:0> 111 = Interru 001 = Interru 000 = Interru Unimplemen U3ERIP<2:0> 111 = Interru . | <ul> <li>UART3 Recept is priority 7 (1)</li> <li>pt is priority 1</li> <li>pt source is dis</li> <li>ted: Read as '0</li> <li>UART3 Error</li> <li>pt is priority 7 (1)</li> </ul> | iver Interrupt<br>nighest priority<br>abled<br>o <sup>2</sup> Interrupt Prio            | v interrupt)     |                  |                 |         |  |  |  |  |

| bit 10-8           | U3RXIP<2:0> 111 = Interru                                                                    | <ul> <li>UART3 Recept is priority 7 (1)</li> <li>pt is priority 1</li> <li>pt source is dis</li> <li>ted: Read as '0</li> <li>UART3 Error</li> <li>pt is priority 7 (1)</li> </ul> | iver Interrupt<br>highest priority<br>abled<br>o'<br>Interrupt Prio<br>highest priority | v interrupt)     |                  |                 |         |  |  |  |  |

#### REGISTER 7-35: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

### 8.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 8-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. The CLKDIV register (Register 8-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The OSCTUN register (Register 8-3) allows the user to fine tune the FRC Oscillator over a range of approximately  $\pm 12\%$ .

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | CO = Clearable Only bit | SO = Settable Only bit      |                    |

|-------------------|-------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

#### bit 11 Unimplemented: Read as '0'

#### bit 10-8 **NOSC<2:0>:** New Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: Also, resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

#### 10.4.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Select options introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '111111' and all RPORx registers reset to '000000', all Peripheral Pin Select inputs are tied to Vss and all Peripheral Pin Select outputs are disconnected.

| Note: | In tying Peripheral Pin Select inputs to    |

|-------|---------------------------------------------|

|       | RP63, RP63 does not have to exist on a      |

|       | device for the registers to be reset to it. |

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in C or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use. Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs, nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a Peripheral Pin Select.

Example 10-2 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 10-2: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

// Unlock Registers \_\_builtin\_write\_OSCCONL(OSCCON & 0xBF); // Configure Input Functions (Table 9-1)) // Assign UIRX To Pin RP0 RPINR18bits.U1RXR = 0; // Assign U1CTS To Pin RP1 RPINR18bits.U1CTSR = 1; // Configure Output Functions (Table 9-2) // Assign U1TX To Pin RP2 RPOR1bits.RP2R = 3; // Assign U1RTS To Pin RP3 RPOR1bits.RP3R = 4; // Lock Registers

```

__builtin_write_OSCCONL(OSCCON | 0x40);

```

#### REGISTER 10-9: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

| U-0                                | U-0 | R/W-1 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |

|------------------------------------|-----|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| —                                  | —   | IC8R5 | IC8R4                                   | IC8R3                              | IC8R2 | IC8R1 | IC8R0 |  |

| bit 15                             |     |       |                                         |                                    |       | •     | bit 8 |  |

|                                    |     |       |                                         |                                    |       |       |       |  |

| U-0                                | U-0 | R/W-1 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |

|                                    | —   | IC7R5 | IC7R4                                   | IC7R3                              | IC7R2 | IC7R1 | IC7R0 |  |

| bit 7                              |     |       |                                         |                                    |       |       | bit 0 |  |

|                                    |     |       |                                         |                                    |       |       |       |  |

| Legend:                            |     |       |                                         |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |     |       | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |       |  |

|                                    |     |       |                                         |                                    |       |       |       |  |

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC8R<5:0>: Assign Input Capture 8 (IC8) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC7R<5:0>: Assign Input Capture 7 (IC7) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 10-10: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **OCFBR<5:0>:** Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 OCFAR<5:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits

#### REGISTER 10-15: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      |     | SCK1R5 | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK1R<5:0>: Assign SPI1 Clock Input (SCK1IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI1R<5:0>: Assign SPI1 Data Input (SDI1) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 10-16: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U3CTSR5 | U3CTSR4 | U3CTSR3 | U3CTSR2 | U3CTSR1 | U3CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3CTSR<5:0>: Assign UART3 Clear to Send (U3CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS1R<5:0>: Assign SPI1 Slave Select Input (SS1IN) to Corresponding RPn or RPIn Pin bits

#### REGISTER 10-38: ALTRP: ALTERNATE PERIPHERAL PIN MAPPING REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 15 |     |     |     |     |     |     | bit 8  |

|        |     |     |     |     |     |     |        |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| —      | —   | —   | —   | —   | —   | —   | SCK1CM |

| bit 7  |     |     |     |     |     |     | bit 0  |

|        |     |     |     |     |     |     |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0

SCK1CM: SCK1 Output Mapping Select bit

1 = SCK1 output function is mapped to ASCK1 pin only

0 = SCK1 output function is mapped according to RPORn registers

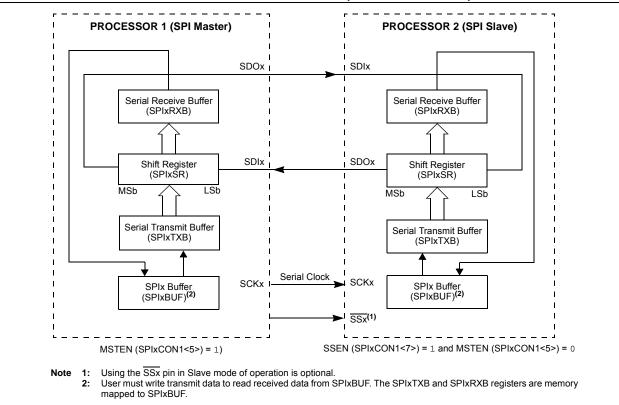

#### FIGURE 15-3: SPI MASTER/SLAVE CONNECTION (STANDARD MODE)

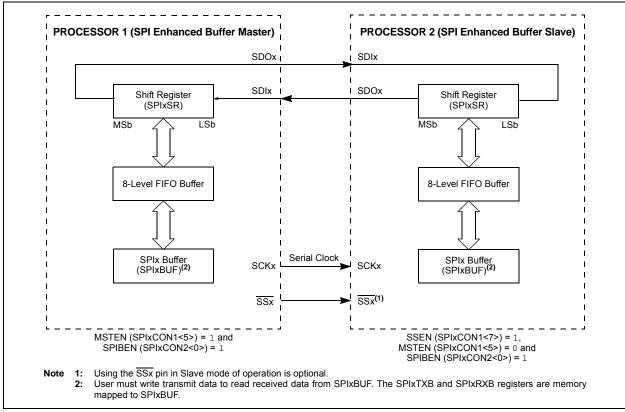

#### FIGURE 15-4: SPI MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                               |

|         | <ul><li>1 = High-Speed mode (baud clock generated from FcY/4)</li><li>0 = Standard mode (baud clock generated from FcY/16)</li></ul>                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                    |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                 |

|         | <ul><li>1 = Two Stop bits</li><li>0 = One Stop bit</li></ul>                                                                                                  |

- **Note 1:** If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See **Section 10.4 "Peripheral Pin Select"** for more information.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

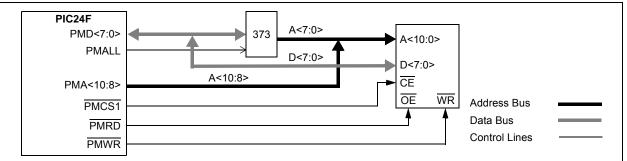

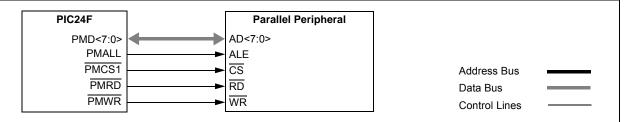

#### FIGURE 18-8: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

#### FIGURE 18-9: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

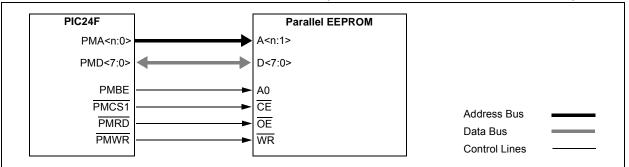

#### FIGURE 18-10: PARALLEL EEPROM EXAMPLE (UP TO 15-BIT ADDRESS, 8-BIT DATA)

| PIC24F                |                       | Parallel EEPROM |                                          |  |

|-----------------------|-----------------------|-----------------|------------------------------------------|--|

| PMA <n:0></n:0>       |                       | A <n:0></n:0>   |                                          |  |

| PMD<7:0>              | $\longleftrightarrow$ | D<7:0>          |                                          |  |

| PMCS1<br>PMRD<br>PMWR |                       | CE<br>OE<br>WR  | Address Bus<br>Data Bus<br>Control Lines |  |

#### FIGURE 18-11: PARALLEL EEPROM EXAMPLE (UP TO 15-BIT ADDRESS, 16-BIT DATA)

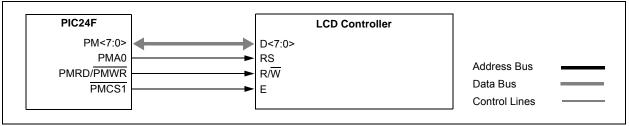

#### FIGURE 18-12: LCD CONTROL EXAMPLE (BYTE MODE OPERATION)

#### 19.3 Alarm

- · Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>, Register 19-3)

- One-time alarm and repeat alarm options available

#### 19.3.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 19-2, the interval selection of the alarm is configured through the AMASK bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs once the alarm is enabled is stored in the ARPT bits, ARPT<7:0> (ALCFGRPT<7:0>). When the value of the ARPT bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

#### FIGURE 19-2: ALARM MASK SETTINGS

After each alarm is issued, the value of the ARPT bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPT bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

#### 19.3.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a trigger clock to other peripherals.

| Note: | Changing any of the registers, other then    |

|-------|----------------------------------------------|

|       | the RCFGCAL and ALCFGRPT registers,          |

|       | and the CHIME bit while the alarm is         |

|       | enabled (ALRMEN = 1), can result in a        |

|       | false alarm event leading to a false alarm   |

|       | interrupt. To avoid a false alarm event, the |

|       | timer and alarm values should only be        |

|       | changed while the alarm is disabled          |

|       | (ALRMEN = 0). It is recommended that         |

|       | the ALCFGRPT register and CHIME bit be       |

|       | changed when RTCSYNC = 0.                    |

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month Day       | Hours Minutes Seconds |

|-------------------------------------------------|-----------------------|-----------------|-----------------------|

| 0000 – Every half second<br>0001 – Every second |                       |                 |                       |

| 0010 – Every 10 seconds                         |                       |                 |                       |

| 0011 – Every minute                             |                       |                 |                       |

| 0100 – Every 10 minutes                         |                       |                 | <b>m</b> : <b>s s</b> |

| 0101 – Every hour                               |                       |                 |                       |

| 0110 – Every day                                |                       |                 | h h : m m : s s       |

| 0111 – Every week                               | d                     |                 | h h ; m m ; s s       |

| 1000 – Every month                              |                       | / d_ d          | h h : m m : s s       |

| 1001 – Every year <sup>(1)</sup>                |                       | m m / d d       | h h : m m : s s       |

| Note 1: Annually, except when co                | onfigured fo          | or February 29. |                       |

### 21.0 10-BIT HIGH-SPEED A/D CONVERTER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 17. "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- Successive Approximation (SAR) Conversion

- Conversion Speeds of up to 500 ksps

- 16 Analog Input pins

- External Voltage Reference Input pins

- Internal Band Gap Reference Inputs

- · Automatic Channel Scan mode

- Selectable Conversion Trigger Source

- 16-Word Conversion Result Buffer

- Selectable Buffer Fill modes

- Four Result Alignment Options

- Operation during CPU Sleep and Idle modes

On all PIC24FJ256GA110 family devices, the 10-bit A/D Converter has 16 analog input pins, designated AN0 through AN15. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is shown in Figure 21-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- Configure port pins as analog inputs and/or select band gap reference input (AD1PCFGL<15:0> and AD1PCFGH<1:0>).

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

#### 27.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 27.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 27.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 27.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 27.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

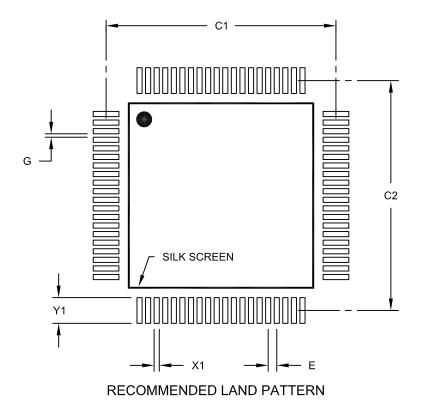

### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIM | ETERS    |      |

|--------------------------|--------|--------|----------|------|

| Dimension                | Limits | MIN    | NOM      | MAX  |

| Contact Pitch            | E      |        | 0.50 BSC |      |

| Contact Pad Spacing      | C1     |        | 13.40    |      |

| Contact Pad Spacing      | C2     |        | 13.40    |      |

| Contact Pad Width (X80)  | X1     |        |          | 0.30 |

| Contact Pad Length (X80) | Y1     |        |          | 1.50 |

| Distance Between Pads    | G      | 0.20   |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092A

| Output Compare                      |     |

|-------------------------------------|-----|

| Cascaded (32-Bit) Mode              | 167 |

| Operations                          | 168 |

| Synchronous and Trigger Modes       | 167 |

| Output Compare with Dedicated Timer | 167 |

| Ρ                                                       |     |

|---------------------------------------------------------|-----|

| Packaging                                               | 305 |

| Details                                                 | 307 |

| Marking                                                 | 305 |

| Parallel Master Port. See PMP.                          | 201 |

| Peripheral Enable Bits                                  | 126 |

| Peripheral Module Disable Bits                          | 126 |

| Peripheral Pin Select (PPS)                             | 129 |

| Alternate Fixed Pin Mapping                             |     |

| Available Peripherals and Pins                          |     |

| Configuration Control                                   |     |

| Considerations for Use                                  |     |

| Input Mapping                                           |     |

| Mapping Exceptions                                      |     |

| Output Mapping                                          |     |

| Peripheral Priority                                     |     |

| Pinout Descriptions                                     |     |

| PMSLP Bit                                               |     |

| and Wake-up Time                                        | 125 |

| PMSLP bit                                               |     |

| and Wake-up Time                                        |     |

| Power-Saving Features                                   | 125 |

| Modes                                                   |     |

| Doze                                                    |     |

| Idle                                                    |     |

| Sleep                                                   |     |

| Power-up Requirements                                   |     |

| Product Identification System                           | 328 |

| Program Memory                                          |     |

| Access Using Table Instructions                         |     |

| Address Space                                           |     |

| Addressing                                              |     |

| Flash Configuration Words                               |     |

| Memory Maps                                             |     |

| Organization                                            |     |

| Program Space Visibility                                |     |

| Program Space Visibility (PSV)                          |     |

| Program Verification                                    |     |

| Programmer's Model<br>Pulse-Width Modulation (PWM) Mode |     |

| Pulse-Width Modulation (PWM) Mode                       | 169 |

| Pulse-width Modulation. See PWM.<br>PWM                 |     |

| Duty Cycle and Period                                   | 170 |

|                                                         | 170 |

| R                                                       |     |

| Reader Response<br>Register Maps | 327 |

|----------------------------------|-----|

| ADC                              |     |

| Comparators                      |     |

| CPU Core                         |     |

| CRC                              |     |

| CTMU                             |     |

| I <sup>2</sup> C                 |     |

| ICN                              |     |

| Input Capture                    |     |

| Interrupt Controller             | 41  |

| NVM                              |     |

| Output Compare                   |     |

| Pad Configuration                |     |

| Parallel Master/Slave Port       | 50  |

|                                  |     |

| Peripheral Pin Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|