Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 192KB (65.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | •                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192ga108-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         |     |

| 5.0   | Flash Program Memory                                        | 57  |

| 6.0   | Resets                                                      | 65  |

| 7.0   | Interrupt Controller                                        | 71  |

| 8.0   | Oscillator Configuration                                    | 115 |

| 9.0   | Power-Saving Features                                       | 125 |

| 10.0  | I/O Ports                                                   | 127 |

| 11.0  | Timer1                                                      | 155 |

| 12.0  | Timer2/3 and Timer4/5                                       | 157 |

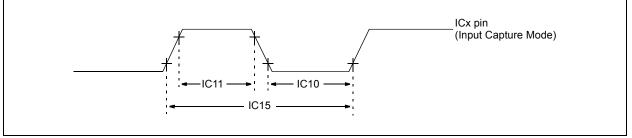

| 13.0  | Input Capture with Dedicated Timer                          |     |

| 14.0  | Output Compare with Dedicated Timer                         | 167 |

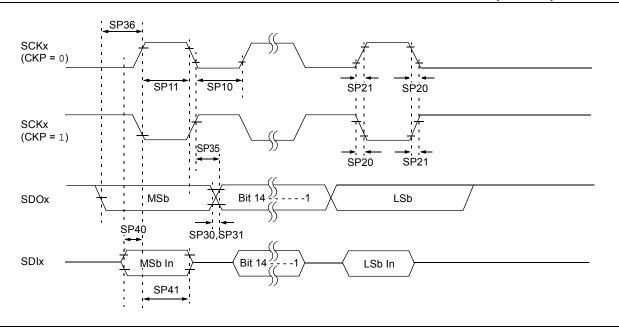

| 15.0  | Serial Peripheral Interface (SPI)                           | 175 |

| 16.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )   | 185 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)          |     |

| 18.0  | Parallel Master Port (PMP)                                  | 201 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 20.0  | Programmable Cyclic Redundancy Check (CRC) Generator        |     |

| 21.0  | 10-Bit High-Speed A/D Converter                             |     |

| 22.0  | Triple Comparator Module                                    |     |

| 23.0  | Comparator Voltage Reference                                | 239 |

|       | Charge Time Measurement Unit (CTMU)                         |     |

| 25.0  | Special Features                                            | 245 |

| 26.0  | Instruction Set Summary                                     | 257 |

| 27.0  | Development Support                                         |     |

| 28.0  | Electrical Characteristics                                  | 269 |

| 29.0  | Packaging Information                                       | 305 |

| Appe  | ndix A: Revision History                                    | 319 |

| Index | <                                                           | 321 |

| The N | Vicrochip Web Site                                          | 327 |

| Custo | omer Change Notification Service                            | 327 |

| Custo | omer Support                                                | 327 |

| Read  | ler Response                                                | 328 |

| Produ | uct Identification System                                   | 329 |

|          |                     | Pin Number     |                 |    | Incost          |                             |

|----------|---------------------|----------------|-----------------|----|-----------------|-----------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | ٧o | Input<br>Buffer | Description                 |

| CN43     | —                   | 52             | 66              | I  | ST              | Interrupt-on-Change Inputs. |

| CN44     | —                   | 53             | 67              | I  | ST              |                             |

| CN45     | —                   | 4              | 6               | I  | ST              |                             |

| CN46     | —                   | —              | 7               | I  | ST              |                             |

| CN47     | —                   | 5              | 8               | I  | ST              |                             |

| CN48     | —                   | _              | 9               | I  | ST              |                             |

| CN49     | 46                  | 58             | 72              | I  | ST              |                             |

| CN50     | 49                  | 61             | 76              | I  | ST              |                             |

| CN51     | 50                  | 62             | 77              | I  | ST              |                             |

| CN52     | 51                  | 63             | 78              | I  | ST              |                             |

| CN53     | 42                  | 54             | 68              | I  | ST              |                             |

| CN54     | 43                  | 55             | 69              | I  | ST              |                             |

| CN55     | 44                  | 56             | 70              | I  | ST              |                             |

| CN56     | 45                  | 57             | 71              | I  | ST              |                             |

| CN57     | —                   | 64             | 79              | I  | ST              |                             |

| CN58     | 60                  | 76             | 93              | I  | ST              |                             |

| CN59     | 61                  | 77             | 94              | I  | ST              | -                           |

| CN60     | 62                  | 78             | 98              | I  | ST              | -                           |

| CN61     | 63                  | 79             | 99              | I  | ST              | -                           |

| CN62     | 64                  | 80             | 100             | I  | ST              | -                           |

| CN63     | 1                   | 1              | 3               | I  | ST              | -                           |

| CN64     | 2                   | 2              | 4               | I  | ST              | -                           |

| CN65     | 3                   | 3              | 5               | I  | ST              |                             |

| CN66     | —                   | 13             | 18              | I  | ST              |                             |

| CN67     | —                   | 14             | 19              | I  | ST              |                             |

| CN68     | 58                  | 72             | 87              | I  | ST              |                             |

| CN69     | 59                  | 73             | 88              | I  | ST              |                             |

| CN70     | 34                  | 42             | 52              | I  | ST              |                             |

| CN71     | 33                  | 41             | 51              | I  | ST              | 1                           |

| CN72     | 35                  | 45             | 55              | I  | ST              |                             |

| CN73     | —                   | 44             | 54              | I  | ST              |                             |

| CN74     | —                   | 43             | 53              | Ι  | ST              | 4                           |

| CN75     | —                   | _              | 40              | Ι  | ST              | 4                           |

| CN76     | —                   | _              | 39              | Ι  | ST              | 4                           |

| CN77     | —                   | 75             | 90              | I  | ST              |                             |

| CN78     | —                   | 74             | 89              | Ι  | ST              | 4                           |

| CN79     | —                   | —              | 96              | I  | ST              |                             |

| CN80     |                     | —              | 97              | I  | ST              |                             |

| CN81     | —                   | —              | 95              | I  | ST              |                             |

| CN82     | —                   | _              | 1               | Ι  | ST              |                             |

| CN83     | 37                  | 47             | 57              | Ι  | ST              |                             |

| CN84     | 36                  | 46             | 56              | I  | ST              |                             |

#### TABLE 1-4: PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend:

TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

© 2010 Microchip Technology Inc.

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and busses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 **Program Address Space**

The program address memory space of the PIC24FJ256GA110 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

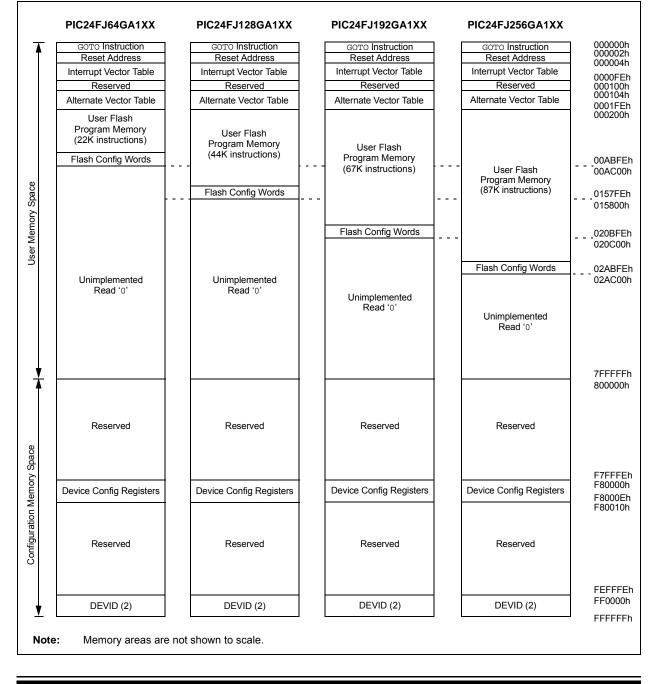

Memory maps for the PIC24FJ256GA110 family of devices are shown in Figure 4-1.

#### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ256GA110 FAMILY DEVICES

### TABLE 4-26: PERIPHERAL PIN SELECT REGISTER MAP

| IADLE        | 4-20. |        |        | AL PIN 3              |                       | INE OIS I             |                       |                       |                       |       |       |        |        |        |        |        |        |               |

|--------------|-------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| File<br>Name | Addr  | Bit 15 | Bit 14 | Bit 13                | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| RPINR0       | 0680  | —      | _      | INT1R5                | INT1R4                | INT1R3                | INT1R2                | INT1R1                | INT1R0                | —     | _     | —      | —      | —      | —      | —      | —      | 3F00          |

| RPINR1       | 0682  |        |        | INT3R5                | INT3R4                | INT3R3                | INT3R2                | INT3R1                | INT3R0                | —     | -     | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 | 3F3F          |

| RPINR2       | 0684  |        |        | —                     | —                     |                       |                       | —                     | —                     | —     | -     | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 | 003F          |

| RPINR3       | 0686  | _      | _      | T3CKR5                | T3CKR4                | T3CKR3                | T3CKR2                | T3CKR1                | T3CKR0                | _     | _     | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 | 3F3F          |

| RPINR4       | 0688  | _      | _      | T5CKR5                | T5CKR4                | T5CKR3                | T5CKR2                | T5CKR1                | T5CKR0                | _     | _     | T4CKR5 | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 | 3F3F          |

| RPINR7       | 068E  | _      | _      | IC2R5                 | IC2R4                 | IC2R3                 | IC2R2                 | IC2R1                 | IC2R0                 | _     | _     | IC1R5  | IC1R4  | IC1R3  | IC1R2  | IC1R1  | IC1R0  | 3F3F          |

| RPINR8       | 0690  | _      | _      | IC4R5                 | IC4R4                 | IC4R3                 | IC4R2                 | IC4R1                 | IC4R0                 | _     | _     | IC3R5  | IC3R4  | IC3R3  | IC3R2  | IC3R1  | IC3R0  | 3F3F          |

| RPINR9       | 0692  | _      | _      | IC6R5                 | IC6R4                 | IC6R3                 | IC6R2                 | IC6R1                 | IC6R0                 | _     | _     | IC5R5  | IC5R4  | IC5R3  | IC5R2  | IC5R1  | IC5R0  | 3F3F          |

| RPINR10      | 0694  | _      | _      | IC8R5                 | IC8R4                 | IC8R3                 | IC8R2                 | IC8R1                 | IC8R0                 | _     | _     | IC7R5  | IC7R4  | IC7R3  | IC7R2  | IC7R1  | IC7R0  | 3F3F          |

| RPINR11      | 0696  | _      | _      | OCFBR5                | OCFBR4                | OCFBR3                | OCFBR2                | OCFBR1                | OCFBR0                | _     | _     | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 | 3F3F          |

| RPINR15      | 069E  | _      | _      | IC9R5                 | IC9R4                 | IC9R3                 | IC9R2                 | IC9R1                 | IC9R0                 | _     | _     | _      | _      | _      | _      | _      | _      | 3F00          |

| RPINR17      | 06A2  | _      | _      | U3RXR5                | U3RXR4                | U3RXR3                | U3RXR2                | U3RXR1                | U3RXR0                | _     | _     | _      | _      | _      | _      | _      | _      | 3F00          |

| RPINR18      | 06A4  | _      | _      | U1CTSR5               | U1CTSR4               | U1CTSR3               | U1CTSR2               | U1CTSR1               | U1CTSR0               | _     | _     | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 | 3F3F          |

| RPINR19      | 06A6  | _      | _      | U2CTSR5               | U2CTSR4               | U2CTSR3               | U2CTSR2               | U2CTSR1               | U2CTSR0               | _     | _     | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 | 3F3F          |

| RPINR20      | 06A8  | _      | _      | SCK1R5                | SCK1R4                | SCK1R3                | SCK1R2                | SCK1R1                | SCK1R0                | _     | _     | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 | 3F3F          |

| RPINR21      | 06AA  | _      | _      | U3CTSR5               | U3CTSR4               | U3CTSR3               | U3CTSR2               | U3CTSR1               | U3CTSR0               | _     | _     | SS1R5  | SS1R4  | SS1R3  | SS1R2  | SS1R1  | SS1R0  | 3F3F          |

| RPINR22      | 06AC  | _      | _      | SCK2R5                | SCK2R4                | SCK2R3                | SCK2R2                | SCK2R1                | SCK2R0                | _     | _     | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 | 3F3F          |

| RPINR23      | 06AE  | _      | _      | _                     |                       | _                     | _                     |                       |                       | _     | _     | SS2R5  | SS2R4  | SS2R3  | SS2R2  | SS2R1  | SS2R0  | 3F3F          |

| RPINR27      | 06B6  | _      | _      | U4CTSR5               | U4CTSR4               | U4CTSR3               | U4CTSR2               | U4CTSR1               | U4CTSR0               | _     | _     | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 | 3F3F          |

| RPINR28      | 06B8  | _      | _      | SCK3R5                | SCK3R4                | SCK3R3                | SCK3R2                | SCK3R1                | SCK3R0                | _     | _     | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 | 003F          |

| RPINR29      | 06BA  | _      | _      | _                     |                       | _                     | _                     |                       |                       | _     | _     | SS3R5  | SS3R4  | SS3R3  | SS3R2  | SS3R1  | SS3R0  | 003F          |

| RPOR0        | 06C0  | _      | _      | RP1R5                 | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | _     | _     | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06C2  | _      | _      | RP3R5                 | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06C4  | _      | _      | RP5R5 <sup>(1)</sup>  | RP5R4 <sup>(1)</sup>  | RP5R3 <sup>(1)</sup>  | RP5R2 <sup>(1)</sup>  | RP5R1 <sup>(1)</sup>  | RP5R0 <sup>(1)</sup>  | _     | _     | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06C6  | _      | _      | RP7R5                 | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | _     | _     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4        | 06C8  | _      | _      | RP9R5                 | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | _     | _     | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5        | 06CA  | _      | _      | RP11R5                | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | _     | _     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6        | 06CC  | _      | _      | RP13R5                | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | _     | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 | 0000          |

| RPOR7        | 06CE  | _      | _      | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> | _     | _     | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR8        | 06D0  | _      | _      | RP17R5                | RP17R4                | RP17R3                | RP17R2                | RP17R1                | RP17R0                | _     | _     | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 | 0000          |

| RPOR9        | 06D2  | _      |        | RP19R5                | RP19R4                | RP19R3                | RP19R2                | RP19R1                | RP19R0                | _     | _     | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 | 0000          |

| RPOR10       | 06D4  | _      | _      | RP21R5                | RP21R4                | RP21R3                | RP21R2                | RP21R1                | RP21R0                | _     | _     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 | 0000          |

| RPOR11       | 06D6  | _      | _      | RP23R5                | RP23R4                | RP23R3                | RP23R2                | RP23R1                | RP23R0                | _     | _     | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 | 0000          |

| RPOR12       | 06D8  | _      |        | RP25R5                | RP25R4                | RP25R3                | RP25R2                | RP25R1                | RP25R0                | _     |       | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 | 0000          |

| RPOR13       | 06DA  | _      |        | RP27R5                | RP27R4                | RP27R3                | RP27R2                | RP27R1                | RP27R0                | _     |       | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 | 0000          |

| RPOR14       | 06DC  | _      | _      | RP29R5                | RP29R4                | RP29R3                | RP29R2                | RP29R1                | RP29R0                | _     | _     | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 | 0000          |

| RPOR15       | 06DE  | _      | _      | RP31R5 <sup>(2)</sup> | RP31R4 <sup>(2)</sup> | RP31R3(2)             | RP31R2 <sup>(2)</sup> | RP31R1 <sup>(2)</sup> | RP31R0 <sup>(2)</sup> | _     |       | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 | 0000          |

| ALTRP        | 06E2  | _      | _      | _                     | _                     | _                     | _                     | _                     | _                     | _     | _     | _      | _      | _      |        | _      | SCK1CM | xxx0          |

| Legend:      |       |        |        | s '0' Reset v         |                       |                       |                       |                       |                       |       |       |        |        |        |        |        | 20.0.0 |               |

DS39905E-page 51

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are unimplemented in 64-pin devices; read as '0'.

2: Bits are unimplemented in 64-pin and 80-pin devices; read as '0'.

#### FLASH PROGRAM MEMORY 5.0

| Note: | This data sheet summarizes the features of |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |  |  |  |

|       | Section 4. "Program Memory"                |  |  |  |  |  |  |  |  |  |

|       | (DS39715).                                 |  |  |  |  |  |  |  |  |  |

The PIC24FJ256GA110 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 2.35V. If the regulator is disabled, the VDDCORE voltage must be over 2.25V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ256GA110 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

#### 5.1 **Table Instructions and Flash** Programming

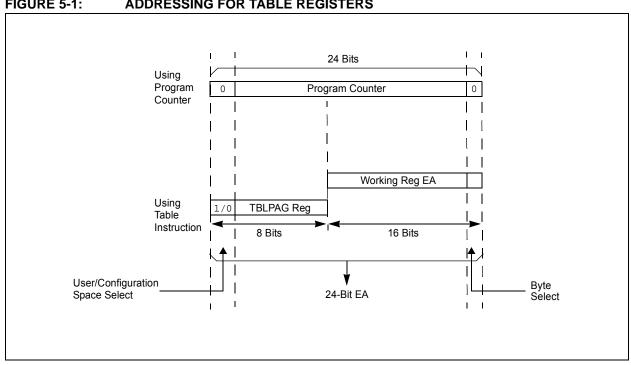

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

| Reset Type         | Clock Source | SYSRST Delay        | System Clock<br>Delay | Notes         |

|--------------------|--------------|---------------------|-----------------------|---------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT + TRST | _                     | 1, 2, 7       |

|                    | FRC, FRCDIV  | TPOR + TPWRT + TRST | TFRC                  | 1, 2, 3, 7    |

|                    | LPRC         | TPOR + TPWRT + TRST | TLPRC                 | 1, 2, 3, 7    |

|                    | ECPLL        | TPOR + TPWRT + TRST | TLOCK                 | 1, 2, 4, 7    |

|                    | FRCPLL       | TPOR + TPWRT + TRST | TFRC + TLOCK          | 1, 2, 3, 4, 7 |

|                    | XT, HS, SOSC | TPOR + TPWRT + TRST | Tost                  | 1, 2, 5, 7    |

|                    | XTPLL, HSPLL | TPOR + TPWRT + TRST | Tost + Tlock          | 1, 2, 4, 5, 7 |

| BOR                | EC           | TPWRT + TRST        | —                     | 2, 7          |

|                    | FRC, FRCDIV  | TPWRT + TRST        | TFRC                  | 2, 3, 7       |

|                    | LPRC         | TPWRT + TRST        | TLPRC                 | 2, 3, 7       |

|                    | ECPLL        | TPWRT + TRST        | TLOCK                 | 2, 4, 7       |

|                    | FRCPLL       | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

|                    | XT, HS, SOSC | TPWRT + TRST        | Тоѕт                  | 2, 5, 7       |

|                    | XTPLL, HSPLL | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

| All Others         | Any Clock    | Trst                | —                     | 7             |

**Note 1:** TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if regulator is disabled (ENVREG tied to Vss).

- 3: TFRC and TLPRC = RC Oscillator start-up times.

- **4:** TLOCK = PLL lock time.

**5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

6: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

7: TRST = Internal State Reset Timer

Note: For detailed operating frequency and timing specifications, see Section 28.0 "Electrical Characteristics".

| R/W-0                       | R-0                                                                                                                 | U-0                                                   | U-0                                                                   | U-0               | U-0             | U-0             | U-0    |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|-------------------|-----------------|-----------------|--------|

| ALTIVT                      | DISI                                                                                                                | _                                                     | —                                                                     | —                 | _               | _               | _      |

| bit 15                      |                                                                                                                     | •<br>•                                                | ·                                                                     |                   |                 |                 | bit 8  |

| U-0                         | U-0                                                                                                                 | U-0                                                   | R/W-0                                                                 | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| _                           |                                                                                                                     | _                                                     | INT4EP                                                                | INT3EP            | INT2EP          | INT1EP          | INTOEP |

| bit 7                       |                                                                                                                     |                                                       |                                                                       |                   |                 |                 | bit (  |

| Legend:                     |                                                                                                                     |                                                       |                                                                       |                   |                 |                 |        |

| R = Readab                  | le bit                                                                                                              | W = Writable                                          | bit                                                                   | U = Unimplem      | ented bit, read | d as '0'        |        |

| -n = Value at               | t POR                                                                                                               | '1' = Bit is se                                       | t                                                                     | '0' = Bit is clea | ared            | x = Bit is unkr | iown   |

| bit 14<br>bit 13-5<br>bit 4 | 0 = Use stand<br>DISI: DISI In<br>1 = DISI inst<br>0 = DISI inst<br>Unimplement<br>INT4EP: Exte<br>1 = Interrupt of |                                                       | vector table<br>is bit<br>e<br>active<br>10'<br>4 Edge Detect F<br>ge | Polarity Select b | it              |                 |        |

| bit 3                       | 1 = Interrupt c                                                                                                     |                                                       | ge                                                                    | Polarity Select b | vit             |                 |        |

| bit 2                       | 1 = Interrupt o                                                                                                     | rnal Interrupt 2<br>on negative ed<br>on positive edg | ge                                                                    | Polarity Select b | vit             |                 |        |

| bit 1                       | 1 = Interrupt c                                                                                                     | rnal Interrupt<br>on negative ed<br>on positive edg   | ge                                                                    | Polarity Select b | vit             |                 |        |

| bit 0                       | 1 = Interrupt c                                                                                                     | rnal Interrupt on negative ed                         | ge                                                                    | Polarity Select b | vit             |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0                                   | R/W-1                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                   | U-0                                                 | R/W-1            | R/W-0           | R/W-0          |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|----------------|

| _                                     | T1IP2                                                                                                                                                                                       | T1IP1                                                                                                                                                                                                                                        | T1IP0                                                                                   |                                                     | OC1IP2           | OC1IP1          | OC1IP0         |

| bit 15                                |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 | bit 8          |

|                                       | D/// 4                                                                                                                                                                                      | DAVA                                                                                                                                                                                                                                         | <b>D</b> /// 0                                                                          |                                                     | <b>D</b> 0.01 4  | DAALO           | <b>D</b> 444.0 |

| U-0                                   | R/W-1                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                   | U-0                                                 | R/W-1            | R/W-0           | R/W-0          |

| <br>bit 7                             | IC1IP2                                                                                                                                                                                      | IC1IP1                                                                                                                                                                                                                                       | IC1IP0                                                                                  | _                                                   | INT0IP2          | INT0IP1         | INT0IP0<br>bit |

|                                       |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 | DIL            |

| Legend:                               |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |

| R = Readab                            | le bit                                                                                                                                                                                      | W = Writable I                                                                                                                                                                                                                               | oit                                                                                     | U = Unimplen                                        | nented bit, read | d as '0'        |                |

| -n = Value a                          | t POR                                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                             |                                                                                         | '0' = Bit is clea                                   | ared             | x = Bit is unkr | nown           |

| bit 15                                | Unimplemen                                                                                                                                                                                  | nted: Read as '0                                                                                                                                                                                                                             | )'                                                                                      |                                                     |                  |                 |                |

| bit 14-12                             | -                                                                                                                                                                                           | imer1 Interrupt                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |

|                                       |                                                                                                                                                                                             | ipt is priority 7 (h                                                                                                                                                                                                                         | 2                                                                                       | y interrupt)                                        |                  |                 |                |

|                                       | •                                                                                                                                                                                           |                                                                                                                                                                                                                                              | • • •                                                                                   |                                                     |                  |                 |                |

|                                       | •                                                                                                                                                                                           |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |

|                                       | 001 = Interru                                                                                                                                                                               | pt is priority 1                                                                                                                                                                                                                             |                                                                                         |                                                     |                  |                 |                |

|                                       |                                                                                                                                                                                             | pt source is disa                                                                                                                                                                                                                            | abled                                                                                   |                                                     |                  |                 |                |

|                                       |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |

| bit 11                                | Unimplemer                                                                                                                                                                                  | nted: Read as 'o                                                                                                                                                                                                                             | )'                                                                                      |                                                     |                  |                 |                |

|                                       | -                                                                                                                                                                                           | nted: Read as '0<br>: Output Compa                                                                                                                                                                                                           |                                                                                         | Interrupt Priority                                  | y bits           |                 |                |

|                                       | OC1IP<2:0>                                                                                                                                                                                  |                                                                                                                                                                                                                                              | re Channel 1                                                                            |                                                     | y bits           |                 |                |

| bit 11<br>bit 10-8                    | OC1IP<2:0>                                                                                                                                                                                  | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                            |                                                     | y bits           |                 |                |

|                                       | OC1IP<2:0>                                                                                                                                                                                  | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                            |                                                     | y bits           |                 |                |

|                                       | OC1IP<2:0><br>111 = Interru<br>001 = Interru                                                                                                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1                                                                                                                                                                                    | re Channel 1<br>highest priorit                                                         |                                                     | y bits           |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru                                                                                                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                                                                                                                               | re Channel 1<br>highest priority<br>abled                                               |                                                     | y bits           |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru                                                                                                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br>nted: Read as '0                                                                                                                                           | re Channel 1<br>nighest priority<br>abled                                               | y interrupt)                                        |                  |                 |                |

|                                       | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br>nted: Read as '0                                                                                                                                           | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C<br>pt is priority 7 (h                                                                                          | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h                                                                                          | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority          | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8<br>bit 7<br>bit 6-4          | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru                                               | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                 | re Channel 1<br>highest priority<br>abled<br>,<br>hannel 1 Inte<br>highest priority     | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                      | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                      | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemer<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemer<br>INT0IP<2:0><br>111 = Interru | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |

### REGISTER 7-31: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                 | U-0             | U-0                                     | R/W-1            | R/W-0    | R/W-0  |  |

|---------------|---------------|---------------------|-----------------|-----------------------------------------|------------------|----------|--------|--|

| —             | —             | —                   |                 | —                                       | RTCIP2           | RTCIP1   | RTCIP0 |  |

| bit 15        | ·             | ·                   |                 |                                         |                  |          | bit 8  |  |

|               |               |                     |                 |                                         |                  |          |        |  |

| U-0           | U-0           | U-0                 | U-0             | U-0                                     | U-0              | U-0      | U-0    |  |

| —             | —             | —                   | _               | —                                       | —                | —        | —      |  |

| bit 7         |               |                     |                 |                                         |                  |          | bit 0  |  |

|               |               |                     |                 |                                         |                  |          |        |  |

| Legend:       |               |                     |                 |                                         |                  |          |        |  |

| R = Readable  | e bit         | W = Writable b      | bit             | U = Unimplem                            | nented bit, read | l as '0' |        |  |

| -n = Value at | POR           | '1' = Bit is set    |                 | '0' = Bit is cleared x = Bit is unknown |                  |          |        |  |

|               |               |                     |                 |                                         |                  |          |        |  |

| bit 15-11     | Unimplemen    | ted: Read as '0     | 3               |                                         |                  |          |        |  |

| bit 10-8      | RTCIP<2:0>:   | Real-Time Cloc      | k/Calendar In   | terrupt Priority I                      | bits             |          |        |  |

|               | 111 = Interru | pt is priority 7 (h | ighest priority | interrupt)                              |                  |          |        |  |

|               | •             |                     |                 |                                         |                  |          |        |  |

|               | •             |                     |                 |                                         |                  |          |        |  |

|               | 001 = Interru | pt is priority 1    |                 |                                         |                  |          |        |  |

|               |               | pt source is disa   | bled            |                                         |                  |          |        |  |

| bit 7-0       | Unimplemen    | ted: Read as '0     | 3               |                                         |                  |          |        |  |

|               |               |                     |                 |                                         |                  |          |        |  |

| U-0        | U-0                      | U-0                 | U-0                       | U-0                 | U-0                 | U-0                 | U-0                 |

|------------|--------------------------|---------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|

| _          | —                        | —                   | _                         | —                   | —                   | —                   | —                   |

| bit 15     |                          |                     |                           |                     |                     |                     | bit 8               |

|            |                          |                     |                           |                     |                     |                     |                     |

| U-0        | U-0                      | R/W-0               | R/W-0                     | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| —          | —                        | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7      |                          |                     |                           | ·                   |                     |                     | bit 0               |

|            |                          |                     |                           |                     |                     |                     |                     |

| Legend:    |                          |                     |                           |                     |                     |                     |                     |

| R = Reada  | ble bit                  | W = Writable        | bit                       | U = Unimplen        | nented bit, read    | l as '0'            |                     |

| -n = Value | at POR                   | '1' = Bit is set    |                           | '0' = Bit is clea   | ared                | x = Bit is unkr     | nown                |

|            |                          |                     |                           |                     |                     |                     |                     |

| bit 15-6   | Unimplemen               | ted: Read as '      | 0'                        |                     |                     |                     |                     |

| bit 5-0    | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator T     | uning bits <sup>(1)</sup> |                     |                     |                     |                     |

|            | 011111 <b>= Ma</b>       | iximum frequer      | ncy deviation             |                     |                     |                     |                     |

|            | 011110 =                 |                     |                           |                     |                     |                     |                     |

|            | •                        |                     |                           |                     |                     |                     |                     |

|            | •                        |                     |                           |                     |                     |                     |                     |

|            | • 000001 =               |                     |                           |                     |                     |                     |                     |

|            |                          | nter frequency      | oscillator is ri          | inning at factory   | v calibrated free   | nuency              |                     |

|            | 111111 =                 |                     |                           | ar laotory          |                     | 100109              |                     |

|            | •                        |                     |                           |                     |                     |                     |                     |

|            | •                        |                     |                           |                     |                     |                     |                     |

|            | •                        |                     |                           |                     |                     |                     |                     |

#### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

# 8.4 Clock Switching Operation

100001 =

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

100000 = Minimum frequency deviation

| Note: | The Primary Oscillator mode has three<br>different submodes (XT, HS and EC)<br>which are determined by the POSCMDx<br>Configuration bits. While an application |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | can switch to and from Primary Oscillator<br>mode in software, it cannot switch<br>between the different primary submodes<br>without reprogramming the device. |

## 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in CW 2 must be programmed to '0'. (Refer to **Section 25.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

| R/W-0         | U-0                           | R/W-0                             | U-0             | U-0              | U-0              | U-0              | U-0 |  |  |  |

|---------------|-------------------------------|-----------------------------------|-----------------|------------------|------------------|------------------|-----|--|--|--|

| TON           | —                             | TSIDL                             | _               | —                |                  | —                | _   |  |  |  |

| bit 15        |                               |                                   |                 |                  |                  |                  | bit |  |  |  |

|               |                               |                                   |                 |                  |                  |                  |     |  |  |  |

| U-0           | R/W-0                         | R/W-0                             | R/W-0           | U-0              | R/W-0            | R/W-0            | U-0 |  |  |  |

|               | TGATE                         | TCKPS1                            | TCKPS0          | —                | TSYNC            | TCS              |     |  |  |  |

| bit 7         |                               |                                   |                 |                  |                  |                  | bit |  |  |  |

| Legend:       |                               |                                   |                 |                  |                  |                  |     |  |  |  |

| R = Readabl   | e bit                         | W = Writable                      | bit             | U = Unimpler     | nented bit, read | 1 as '0'         |     |  |  |  |

| -n = Value at |                               | '1' = Bit is set                  |                 | '0' = Bit is cle |                  | x = Bit is unkno | own |  |  |  |

|               |                               |                                   |                 |                  |                  |                  |     |  |  |  |

| bit 15        | TON: Timer1                   | On bit                            |                 |                  |                  |                  |     |  |  |  |

|               | 1 = Starts 16                 |                                   |                 |                  |                  |                  |     |  |  |  |

|               | 0 = Stops 16                  |                                   |                 |                  |                  |                  |     |  |  |  |

| bit 14        | -                             | nted: Read as '                   |                 |                  |                  |                  |     |  |  |  |

| bit 13        | TSIDL: Stop in Idle Mode bit  |                                   |                 |                  |                  |                  |     |  |  |  |

|               |                               | nue module ope<br>e module operat |                 |                  | e mode           |                  |     |  |  |  |

| bit 12-7      |                               | -                                 |                 | e                |                  |                  |     |  |  |  |

|               | •                             | nted: Read as '                   |                 | Enchla hit       |                  |                  |     |  |  |  |

| bit 6         | When TCS =                    | er1 Gated Time                    | Accumulation    | Enable bit       |                  |                  |     |  |  |  |

|               | This bit is igr               |                                   |                 |                  |                  |                  |     |  |  |  |

|               | When TCS =                    |                                   |                 |                  |                  |                  |     |  |  |  |

|               |                               | me accumulatio                    | n enabled       |                  |                  |                  |     |  |  |  |

|               | 0 = Gated ti                  | me accumulatio                    | n disabled      |                  |                  |                  |     |  |  |  |

| bit 5-4       |                               | >: Timer1 Input                   | Clock Prescale  | e Select bits    |                  |                  |     |  |  |  |

|               | 11 = 1:256                    |                                   |                 |                  |                  |                  |     |  |  |  |

|               | 10 = 1:64<br>01 = 1:8         |                                   |                 |                  |                  |                  |     |  |  |  |

|               | 00 = 1:1                      |                                   |                 |                  |                  |                  |     |  |  |  |

| bit 3         | Unimpleme                     | nted: Read as '                   | o'              |                  |                  |                  |     |  |  |  |

| bit 2         | TSYNC: Tim                    | er1 External Clo                  | ock Input Syncl | hronization Sel  | ect bit          |                  |     |  |  |  |

|               | When TCS =                    | <u>: 1:</u>                       |                 |                  |                  |                  |     |  |  |  |

|               |                               | onize external c                  |                 |                  |                  |                  |     |  |  |  |

|               |                               | synchronize ext                   | ernal clock inp | ut               |                  |                  |     |  |  |  |

|               | When TCS =<br>This bit is igr |                                   |                 |                  |                  |                  |     |  |  |  |

| bit 1         | •                             | Clock Source S                    | Select hit      |                  |                  |                  |     |  |  |  |

|               |                               | l clock from T1                   |                 | risina edae)     |                  |                  |     |  |  |  |

|               |                               | clock (Fosc/2)                    |                 |                  |                  |                  |     |  |  |  |

|               |                               |                                   |                 |                  |                  |                  |     |  |  |  |

**Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

For 32-bit cascaded operation, these steps are also necessary:

- 1. Set the OC32 bits for both registers (OCyCON2<8> and (OCxCON2<8>). Enable the even-numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2<7>), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCyCON2.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.