Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 192КВ (65.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192ga110-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                     | Pin Number     |                       |     |                  |                                                                      |

|----------|---------------------|----------------|-----------------------|-----|------------------|----------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP       | I/O | Input<br>Buffer  | Description                                                          |

| RPI32    | _                   | _              | 40                    | I   | ST               | Remappable Peripheral (input only).                                  |

| RPI33    | _                   | 13             | 18                    | I   | ST               |                                                                      |

| RPI34    | _                   | 14             | 19                    | I   | ST               |                                                                      |

| RPI35    | _                   | 53             | 67                    | I   | ST               | -                                                                    |

| RPI36    | _                   | 52             | 66                    | I   | ST               |                                                                      |

| RPI37    | 48                  | 60             | 74                    | I   | ST               | -                                                                    |

| RPI38    | _                   | 4              | 6                     | I   | ST               | -                                                                    |

| RPI39    | _                   | _              | 7                     | I   | ST               |                                                                      |

| RPI40    | _                   | 5              | 8                     | I   | ST               | -                                                                    |

| RPI41    | _                   | _              | 9                     | I   | ST               | -                                                                    |

| RPI42    | _                   | 64             | 79                    | I   | ST               | -                                                                    |

| RPI43    | _                   | 37             | 47                    | I   | ST               |                                                                      |

| RPI44    | _                   | 44             | 54                    | I   | ST               | -                                                                    |

| RPI45    | 35                  | 45             | 55                    | I   | ST               | -                                                                    |

| RTCC     | 42                  | 54             | 68                    | 0   | _                | Real-Time Clock Alarm/Seconds Pulse Output.                          |

| SCL1     | 37                  | 47             | 57                    | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output.                          |

| SCL2     | 32                  | 52             | 58                    | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output.                          |

| SCL3     | 2                   | 2              | 4                     | I/O | l <sup>2</sup> C | I2C3 Synchronous Serial Clock Input/Output.                          |

| SDA1     | 36                  | 46             | 56                    | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                                              |

| SDA2     | 31                  | 53             | 59                    | I/O | I <sup>2</sup> C | I2C2 Data Input/Output.                                              |

| SDA3     | 3                   | 3              | 5                     | I/O | I <sup>2</sup> C | I2C3 Data Input/Output.                                              |

| SOSCI    | 47                  | 59             | 73                    | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.                             |

| SOSCO    | 48                  | 60             | 74                    | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.                            |

| T1CK     | 48                  | 60             | 74                    | I   | ST               | Timer1 Clock.                                                        |

| ТСК      | 27                  | 33             | 38                    | I   | ST               | JTAG Test Clock Input.                                               |

| TDI      | 28                  | 34             | 60                    | I   | ST               | JTAG Test Data Input.                                                |

| TDO      | 24                  | 14             | 61                    | 0   | _                | JTAG Test Data Output.                                               |

| TMS      | 23                  | 13             | 17                    | I   | ST               | JTAG Test Mode Select Input.                                         |

| VCAP     | 56                  | 70             | 85                    | Р   | _                | External Filter Capacitor Connection (regulator enabled).            |

| Vdd      | 10, 26, 38          | 12, 32, 48     | 2, 16, 37,<br>46, 62  | Р   | —                | Positive Supply for Peripheral Digital Logic and I/O Pins.           |

| VDDCORE  | 56                  | 70             | 85                    | Р   | —                | Positive Supply for Microcontroller Core Logic (regulator disabled). |

| VREF-    | 15                  | 23             | 28                    | Ι   | ANA              | A/D and Comparator Reference Voltage (low) Input.                    |

| VREF+    | 16                  | 24             | 29                    | I   | ANA              | A/D and Comparator Reference Voltage (high) Input.                   |

| Vss      | 9, 25, 41           | 11, 31, 51     | 15, 36, 45,<br>65, 75 | Р   | —                | Ground Reference for Logic and I/O Pins.                             |

#### TABLE 1-4: PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

DS39905E-page 22

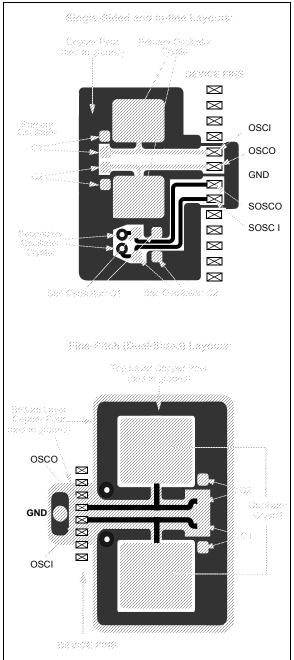

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| U-0          | U-0            | R/W-0                                                                                                                     | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0  |  |  |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-----------------|-----------------|--------|--|--|

| —            | —              | PMPIF                                                                                                                     | OC8IF            | OC7IF              | OC6IF           | OC5IF           | IC6IF  |  |  |

| bit 15       |                |                                                                                                                           |                  |                    |                 |                 | bit 8  |  |  |

|              |                |                                                                                                                           |                  |                    |                 |                 |        |  |  |

| R/W-0        | R/W-0          | R/W-0                                                                                                                     | U-0              | U-0                | U-0             | R/W-0           | R/W-0  |  |  |

| IC5IF        | IC4IF          | IC3IF                                                                                                                     |                  | _                  |                 | SPI2IF          | SPF2IF |  |  |

| bit 7        |                |                                                                                                                           |                  |                    |                 |                 | bit    |  |  |

| Legend:      |                |                                                                                                                           |                  |                    |                 |                 |        |  |  |

| R = Readab   | le bit         | W = Writable                                                                                                              | bit              | U = Unimplen       | nented bit, rea | d as '0'        |        |  |  |

| -n = Value a | t POR          | '1' = Bit is set                                                                                                          |                  | '0' = Bit is clea  |                 | x = Bit is unkr | nown   |  |  |

|              |                |                                                                                                                           |                  |                    |                 |                 |        |  |  |

| bit 15-14    | Unimplemen     | ted: Read as '                                                                                                            | 0'               |                    |                 |                 |        |  |  |

| bit 13       | PMPIF: Para    | llel Master Port                                                                                                          | Interrupt Flag   | Status bit         |                 |                 |        |  |  |

|              |                | request has oc<br>request has no                                                                                          |                  |                    |                 |                 |        |  |  |

| bit 12       |                | •                                                                                                                         |                  | ipt Flag Status I  | oit             |                 |        |  |  |

|              | •              | request has oc                                                                                                            |                  | ipt ing change     |                 |                 |        |  |  |

|              | 0 = Interrupt  | request has no                                                                                                            | toccurred        |                    |                 |                 |        |  |  |

| bit 11       | -              | -                                                                                                                         |                  | ipt Flag Status I  | oit             |                 |        |  |  |

|              | •              | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |

| oit 10       | •              | <ul> <li>Interrupt request has not occurred</li> <li>OC6IF: Output Compare Channel 6 Interrupt Flag Status bit</li> </ul> |                  |                    |                 |                 |        |  |  |

|              | -              | request has oc                                                                                                            |                  | ipt i lag Status i | Jit             |                 |        |  |  |

|              |                | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |

| bit 9        | OC5IF: Outp    | ut Compare Ch                                                                                                             | annel 5 Interru  | ipt Flag Status I  | oit             |                 |        |  |  |

|              |                | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |

| L:1 0        |                | request has no                                                                                                            |                  | les Ctatus bit     |                 |                 |        |  |  |

| bit 8        | -              | Capture Chann<br>request has oc                                                                                           |                  | lag Status bit     |                 |                 |        |  |  |

|              |                | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |

| bit 7        | IC5IF: Input ( | Capture Chann                                                                                                             | el 5 Interrupt F | lag Status bit     |                 |                 |        |  |  |

|              |                | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |

|              | •              | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |

| bit 6        | -              | Capture Chann                                                                                                             | -                | lag Status bit     |                 |                 |        |  |  |

|              |                | request has oc<br>request has no                                                                                          |                  |                    |                 |                 |        |  |  |

| bit 5        |                | Capture Chann                                                                                                             |                  | lag Status bit     |                 |                 |        |  |  |

|              | -              | request has oc                                                                                                            | -                | •                  |                 |                 |        |  |  |

|              | -              | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |

| oit 4-2      | -              | ted: Read as '                                                                                                            |                  |                    |                 |                 |        |  |  |

| bit 1        |                | Event Interrup                                                                                                            | -                | It                 |                 |                 |        |  |  |

|              |                | request has oc<br>request has no                                                                                          |                  |                    |                 |                 |        |  |  |

| bit 0        | -              | 2 Fault Interrup                                                                                                          |                  | it                 |                 |                 |        |  |  |

|              |                | request has oc                                                                                                            | -                |                    |                 |                 |        |  |  |

|              |                | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0           | U-0             | R/W-0                             | R/W-0                     | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|-----------------|-----------------------------------|---------------------------|-------------------|------------------|-----------------|--------|

|               |                 | AD1IE                             | U1TXIE                    | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |

| bit 15        |                 |                                   |                           |                   |                  |                 | bit 8  |

| R/W-0         | R/W-0           | R/W-0                             | U-0                       | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE           | IC2IE                             | <u> </u>                  | T1IE              | OC1IE            | IC1IE           | INTOIE |

| bit 7         | UUZIL           | ICZIL                             |                           |                   | OCTIL            | IGHE            | bit (  |

|               |                 |                                   |                           |                   |                  |                 | bit (  |

| Legend:       |                 |                                   |                           |                   |                  |                 |        |

| R = Readab    | le bit          | W = Writable                      | bit                       | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at | t POR           | '1' = Bit is set                  |                           | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

| bit 15-14     | Unimplemen      | ted: Read as '                    | 0'                        |                   |                  |                 |        |

| bit 13        | -               |                                   | nplete Interrup           | t Enable bit      |                  |                 |        |

|               | 1 = Interrupt r | request enable                    | d                         |                   |                  |                 |        |

| bit 12        | •               | •                                 | r Interrupt Enal          | ble bit           |                  |                 |        |

|               |                 | equest enable                     |                           |                   |                  |                 |        |

| bit 11        |                 | request not ena                   | abled<br>nterrupt Enable  | bit               |                  |                 |        |

|               |                 | request enable                    |                           |                   |                  |                 |        |

|               |                 | equest not ena                    |                           |                   |                  |                 |        |

| bit 10        |                 |                                   | plete Interrupt           | Enable bit        |                  |                 |        |

|               |                 | request enable<br>request not ena |                           |                   |                  |                 |        |

| bit 9         | •               | Fault Interrup                    |                           |                   |                  |                 |        |

|               | 1 = Interrupt r | equest enable                     | d                         |                   |                  |                 |        |

|               | •               | request not ena                   |                           |                   |                  |                 |        |

| bit 8         |                 | Interrupt Enab<br>request enable  |                           |                   |                  |                 |        |

|               |                 | request not enable                |                           |                   |                  |                 |        |

| bit 7         |                 | Interrupt Enab                    |                           |                   |                  |                 |        |

|               |                 | request enable                    |                           |                   |                  |                 |        |

| bit 6         | •               | request not ena                   | iannel 2 Interru          | int Enable bit    |                  |                 |        |

|               |                 | request enable                    |                           | ipt Enable bit    |                  |                 |        |

|               |                 | equest not ena                    |                           |                   |                  |                 |        |

| bit 5         |                 |                                   | el 2 Interrupt E          | nable bit         |                  |                 |        |

|               |                 | request enable<br>request not ena |                           |                   |                  |                 |        |

| bit 4         | -               | ted: Read as '                    |                           |                   |                  |                 |        |

| bit 3         | T1IE: Timer1    | Interrupt Enab                    | le bit                    |                   |                  |                 |        |

|               |                 | equest enable                     |                           |                   |                  |                 |        |

| bit 2         | •               | request not ena                   | abled<br>Iannel 1 Interru | unt Encollo bit   |                  |                 |        |

|               |                 | request enable                    |                           |                   |                  |                 |        |

|               |                 | request not ena                   |                           |                   |                  |                 |        |

| bit 1         |                 |                                   | el 1 Interrupt E          | nable bit         |                  |                 |        |

|               |                 | request enable<br>request not ena |                           |                   |                  |                 |        |

| bit 0         |                 | nal Interrupt 0                   |                           |                   |                  |                 |        |

|               | 1 = Interrupt r | equest enable                     | d                         |                   |                  |                 |        |

|               | 0 - Interrupt r | request not ena                   | ahled                     |                   |                  |                 |        |

### REGISTER 7-11: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |             |                                   |               |                   |                  |                 |       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-----------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|

| bit 15       bit         U-0       U-0       U-0       R/W-0       R/W-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0          | U-0         | R/W-0                             | U-0           | U-0               | U-0              | U-0             | R/W-0 |  |  |

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       U-0         -       -       -       CRCIE       U2ERIE       U1ERIE       -         bit 7       bit       bit       bit       Bit       U=0       U=0       U=0       D=0         constraints       R= Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         Dit 15-14       Unimplemented: Read as '0'       D= Bit is cleared       x = Bit is unknown         Dit 15-14       Unimplemented: Read as '0'       D= Interrupt request enabled       0 = Interrupt request as '0'         Dit 12-9       Unimplemented: Read as '0'       Dit 12:       D= Interrupt request enabled       D= Interrupt request not enabled         Dit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request enabled       D= Interrupt request not enabled         Dit 7-4       Unimplemented: Read as '0'       Dit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled         Dit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request enabled       D = Interrupt request enabled         Dit 1       UIERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request enabled       D = Interrupt request enabled         Di Interrupt request enabled </td <td>—</td> <td>—</td> <td>CTMUIE</td> <td>—</td> <td>—</td> <td></td> <td>—</td> <td>LVDIE</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —            | —           | CTMUIE                            | —             | —                 |                  | —               | LVDIE |  |  |

| Image: Section of the section of t | bit 15       |             |                                   |               |                   |                  |                 | bit 8 |  |  |

| Image: Section of the section of t |              |             |                                   |               |                   |                  |                 |       |  |  |

| bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 12-9       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 12-9       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 7-4       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request enabled       0 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0          | U-0         | U-0                               | U-0           |                   |                  |                 | U-0   |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'          bit 15-14       Unimplemented: Read as '0'          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled         bit 12-9       Unimplemented: Read as '0'         bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled <t< td=""><td></td><td></td><td>_</td><td>—</td><td>CRCIE</td><td>U2ERIE</td><td>U1ERIE</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |             | _                                 | —             | CRCIE             | U2ERIE           | U1ERIE          |       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'           bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request not enabled          bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request not enabled          bit 7-4       Unimplemented: Read as '0'            bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled          bit 4       Interrupt request ont enabled             bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled           bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |             |                                   |               |                   |                  |                 | bit C |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'           bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request not enabled          bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request not enabled          bit 7-4       Unimplemented: Read as '0'            bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled          bit 4       Interrupt request ont enabled             bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled           bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Legend:      |             |                                   |               |                   |                  |                 |       |  |  |

| bit 15-14       Unimplemented: Read as '0'         0 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -            | ole bit     | W = Writable b                    | oit           | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |

| bit 13       CTMUIE: CTMU Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -n = Value a | It POR      | '1' = Bit is set                  |               | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |

| bit 13       CTMUIE: CTMU Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |             |                                   |               |                   |                  |                 |       |  |  |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request ont enabled         0 = Interrupt request not enabled         bit 7-4         Unimplemented: Read as '0'         cRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 3         CRCIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2         U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         bit 1         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15-14    | Unimplemer  | nted: Read as '0                  | ,             |                   |                  |                 |       |  |  |

| <ul> <li>o = Interrupt request not enabled</li> <li>bit 12-9</li> <li>Unimplemented: Read as '0'</li> <li>LVDIE: Low-Voltage Detect Interrupt Enable bit         <ol> <li>= Interrupt request enabled</li> <li>= Interrupt request enabled</li> <li>o = Interrupt request not enabled</li> </ol> </li> <li>bit 3</li> <li>CRCIE: CRC Generator Interrupt Enable bit         <ol> <li>= Interrupt request enabled</li> <li>= Interrupt request not enabled</li> </ol> </li> <li>bit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit         <ol> <li>I = Interrupt request enabled</li> <li>= Interrupt request not enabled</li> <li>I = Interrupt request not enabled</li> <li>= Interrupt request not</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 13       | CTMUIE: CT  | CTMUIE: CTMU Interrupt Enable bit |               |                   |                  |                 |       |  |  |

| bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 7-4       Unimplemented: Read as '0'         bit 3       CRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 1       Interrupt request enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |             |                                   |               |                   |                  |                 |       |  |  |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = CRCIE: CRC Generator Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 12-9     | Unimplemer  | nted: Read as '0                  | ,             |                   |                  |                 |       |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>bit 7-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CRCIE: CRC Generator Interrupt Enable bit         <ol> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit                 <ol> <li>a = Interrupt request enabled</li> <li>bit 1 = Interrupt request enabled</li> <li>bit 2</li> <li>U1ERIE: UART2 Error Interrupt Enable bit                     <ol> <li>a = Interrupt request enabled</li> <li>bit 1 = Interrupt request not enabled</li> <li>bit 1 = Interrupt request not enabled</li> <li>bit 1 = Interrupt request not enabled</li></ol></li></ol></li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 8        | LVDIE: Low- | Voltage Detect I                  | nterrupt Enat | ole bit           |                  |                 |       |  |  |

| bit 3       CRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1         U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |             | •                                 |               |                   |                  |                 |       |  |  |

| <pre>1 = Interrupt request enabled 0 = Interrupt request not enabled bit 2 U2ERIE: UART2 Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 1 U1ERIE: UART1 Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request enabled 0 = Interrupt request enabled</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7-4      | Unimplemer  | nted: Read as '0                  | '             |                   |                  |                 |       |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>Dit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>Dit 1</li> <li>U1ERIE: UART1 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3        | CRCIE: CRC  | Generator Inter                   | rupt Enable I | oit               |                  |                 |       |  |  |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1         U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |             |                                   |               |                   |                  |                 |       |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>Dit 1</li> <li>DIERIE: UART1 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 2        | U2ERIE: UA  |                                   |               |                   |                  |                 |       |  |  |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |             |                                   |               |                   |                  |                 |       |  |  |

| 0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1        |             |                                   |               |                   |                  |                 |       |  |  |