Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 192KB (65.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192ga110t-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Features                                         | PIC24FJ64GA106 | PIC24FJ128GA106                                 | PIC24FJ192GA106      | PIC24FJ256GA106 |

|--------------------------------------------------|----------------|-------------------------------------------------|----------------------|-----------------|

| Operating Frequency                              |                | DC – 3                                          | 32 MHz               | •               |

| Program Memory (bytes)                           | 64K            | 128K                                            | 192K                 | 256K            |

| Program Memory (instructions)                    | 22,016         | 44,032                                          | 67,072               | 87,552          |

| Data Memory (bytes)                              |                | . 16,                                           | 384                  |                 |

| Interrupt Sources<br>(soft vectors/NMI traps)    |                | 66 (                                            | 62/4)                |                 |

| I/O Ports                                        |                | Ports B, C                                      | , D, E, F, G         |                 |

| Total I/O Pins                                   |                | 5                                               | 53                   |                 |

| Remappable Pins                                  |                | 31 (29 I/O, 1                                   | 2 input only)        |                 |

| Timers:                                          |                |                                                 |                      |                 |

| Total Number (16-bit)                            |                | 5                                               | (1)                  |                 |

| 32-Bit (from paired 16-bit timers)               |                |                                                 | 2                    |                 |

| Input Capture Channels                           |                | 9                                               | (1)                  |                 |

| Output Compare/PWM<br>Channels                   |                | 9                                               | (1)                  |                 |

| Input Change Notification<br>Interrupt           |                | 5                                               | 53                   |                 |

| Serial Communications:                           |                |                                                 |                      |                 |

| UART                                             |                | 4                                               | (1)                  |                 |

| SPI (3-wire/4-wire)                              |                | 3                                               | (1)                  |                 |

| I <sup>2</sup> C™                                |                |                                                 | 3                    |                 |

| Parallel Communications<br>(PMP/PSP)             |                | Y                                               | es                   |                 |

| JTAG Boundary Scan                               |                | Y                                               | es                   |                 |

| 10-Bit Analog-to-Digital Module (input channels) |                | 1                                               | 6                    |                 |

| Analog Comparators                               |                | :                                               | 3                    |                 |

| CTMU Interface                                   |                | Y                                               | es                   |                 |

| Resets (and delays)                              |                | r Instruction, MCLR, V<br>ps, Configuration Wor |                      |                 |

| Instruction Set                                  | 76 Bas         | e Instructions, Multiple                        | e Addressing Mode Va | ariations       |

| Packages                                         |                | 64-Pin                                          | TQFP                 |                 |

|                                                  |                |                                                 |                      |                 |

## TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ256GA110 FAMILY: 64-PIN DEVICES

**Note 1:** Peripherals are accessible through remappable pins.

### TABLE 4-22: PARALLEL MASTER/SLAVE PORT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                                                | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9          | Bit 8        | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|-------------------------------------------------------|--------|---------|---------|--------|----------------|--------------|---------------|--------------|--------|--------|--------|--------|--------|--------|---------------|

| PMCON        | 0600 | PMPEN  |                                                       | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN         | PTRDEN       | CSF1          | CSF0         | ALP    | CS2P   | CS1P   | BEP    | WRSP   | RDSP   | 0000          |

| PMMODE       | 0602 | BUSY   | IRQM1                                                 | IRQM0  | INCM1   | INCM0   | MODE16 | MODE1          | MODE0        | WAITB1        | WAITB0       | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 | WAITE0 | 0000          |

| PMADDR       | 0604 | CS2    | CS1                                                   | ADDR13 | ADDR12  | ADDR11  | ADDR10 | ADDR9          | ADDR8        | ADDR7         | ADDR6        | ADDR5  | ADDR4  | ADDR3  | ADDR2  | ADDR1  | ADDR0  | 0000          |

| PMDOUT1      |      |        | Parallel Port Data Out Register 1 (Buffers 0 and 1) 0 |        |         |         |        |                |              |               |              |        | 0000   |        |        |        |        |               |

| PMDOUT2      | 0606 |        |                                                       |        |         |         | Pa     | rallel Port D  | ata Out Reg  | gister 2 (Buf | fers 2 and 3 | )      |        |        |        |        |        | 0000          |

| PMDIN1       | 0608 |        |                                                       |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 1 (Buffe | ers 0 and 1) |        |        |        |        |        |        | 0000          |

| PMDIN2       | 060A |        |                                                       |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 2 (Buffe | ers 2 and 3) |        |        |        |        |        |        | 0000          |

| PMAEN        | 060C | PTEN15 | PTEN14                                                | PTEN13 | PTEN12  | PTEN11  | PTEN10 | PTEN9          | PTEN8        | PTEN7         | PTEN6        | PTEN5  | PTEN4  | PTEN3  | PTEN2  | PTEN1  | PTEN0  | 0000          |

| PMSTAT       | 060E | IBF    | IBOV                                                  | _      |         | IB3F    | IB2F   | IB1F           | IB0F         | OBE           | OBUF         |        |        | OB3E   | OB2E   | OB1E   | OB0E   | 0000          |

| PMSTAT       | 060E | IBF    | IBOV                                                  |        | —       | IB3F    | IB2F   | IB1F           | IB0F         | OBE           | OBUF         | —      | —      | OB3E   | OB2E   | OB1E   | OB0E   | L             |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-23: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| Bit 11 Bit 10                                        | Bit 9 Bit                         | it 8 Bit 7                                                                                                     | Bit 6                                                                                                                                                            | Bit 5                                                                                                                                                                               | Bit 4                                                                                                                                                                                                                                                                                          | Bit 3                                                                                                                                                                                                                                                                                                                 | Bit 2                                                                                                                                                                                                                                                                                                                                        | Bit 1                                                                                                                                                                                                                                                                                                                                                             | Bit 0                                                                                                                                                                                                                                                                                                                                                           | All<br>Resets                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alarm Value Register Window Based on ALRMPTR<1:0>    |                                   |                                                                                                                |                                                                                                                                                                  |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                 | xxxx                                                                                                                                                                                                                                                                                                                                                                                   |

| AMASK1 AMASK0 A                                      | ALRMPTR1 ALRM                     | MPTR0 ARPT7                                                                                                    | ARPT6                                                                                                                                                            | ARPT5                                                                                                                                                                               | ARPT4                                                                                                                                                                                                                                                                                          | ARPT3                                                                                                                                                                                                                                                                                                                 | ARPT2                                                                                                                                                                                                                                                                                                                                        | ARPT1                                                                                                                                                                                                                                                                                                                                                             | ARPT0                                                                                                                                                                                                                                                                                                                                                           | 0000                                                                                                                                                                                                                                                                                                                                                                                   |

| RTCC Value Register Window Based on RTCPTR<1:0> xxxx |                                   |                                                                                                                |                                                                                                                                                                  |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                   | xxxx                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |

| IALFSEC RTCOE F                                      | RTCPTR1 RTCF                      | PTR0 CAL7                                                                                                      | CAL6                                                                                                                                                             | CAL5                                                                                                                                                                                | CAL4                                                                                                                                                                                                                                                                                           | CAL3                                                                                                                                                                                                                                                                                                                  | CAL2                                                                                                                                                                                                                                                                                                                                         | CAL1                                                                                                                                                                                                                                                                                                                                                              | CAL0                                                                                                                                                                                                                                                                                                                                                            | xxxx                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                                                    | Alarm V<br>MASK1 AMASK0 A<br>RTCC | Alarm Value Register Wind<br>MASK1 AMASK0 ALRMPTR1 ALRM<br>RTCC Value Register Win<br>ALFSEC RTCOE RTCPTR1 RTC | Alarm Value Register Window Based on ALR<br>MASK1 AMASK0 ALRMPTR1 ALRMPTR0 ARPT7<br>RTCC Value Register Window Based on RT0<br>ALFSEC RTCOE RTCPTR1 RTCPTR0 CAL7 | Alarm Value Register Window Based on ALRMPTR<1:0> MASK1 AMASK0 ALRMPTR1 ALRMPTR0 ARPT7 ARPT6 RTCC Value Register Window Based on RTCPTR<1:0> ALFSEC RTCOE RTCPTR1 RTCPTR0 CAL7 CAL6 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5         RTCC Value Register Window Based on RTCPTR<1:0>         ALFSEC       RTCOE       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5       ARPT4         RTCC Value Register Window Based on RTCPTR<1:0>         ALFSEC       RTCOE       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5       CAL4 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5       ARPT4       ARPT3         RTCC Value Register Window Based on RTCPTR<1:0>         ALFSEC       RTCOE       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5       CAL4       CAL3 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5       ARPT4       ARPT3       ARPT2         RTCC Value Register Window Based on RTCPTR<1:0>       ALFSEC       RTCOE       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5       CAL4       CAL3       CAL2 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5       ARPT4       ARPT3       ARPT2       ARPT1         RTCC Value Register Window Based on RTCPTR<1:0>       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5       CAL4       CAL3       CAL2       CAL1 | Alarm Value Register Window Based on ALRMPTR<1:0>         MASK1       AMASK0       ALRMPTR1       ALRMPTR0       ARPT7       ARPT6       ARPT5       ARPT4       ARPT3       ARPT2       ARPT1       ARPT0         RTCC Value Register Window Based on RTCPTR<1:0>       RTCPTR1       RTCPTR0       CAL7       CAL6       CAL5       CAL4       CAL3       CAL2       CAL1       CAL0 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: COMPARATORS REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT       | 0630 | CMIDL  | -      | —      | _      | -      | C3EVT  | C2EVT | C1EVT | —      | —      |       | —     | —     | C3OUT | C2OUT | C10UT | 0000          |

| CVRCON       | 0632 | —      | —      | —      | —      | —      | —      | —     | —     | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON       | 0634 | CEN    | COE    | CPOL   | —      | —      | —      | CEVT  | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | 0000          |

| CM2CON       | 0636 | CEN    | COE    | CPOL   | —      | —      | —      | CEVT  | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | 0000          |

| CM3CON       | 0638 | CEN    | COE    | CPOL   | _      | _      |        | CEVT  | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | _     |       | CCH1  | CCH0  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-25: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON       | 0640 | —      |                         | CSIDL  | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 | CRCFUL | CRCMPT |       | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0040          |

| CRCXOR       | 0642 | X15    | X14                     | X13    | X12    | X11    | X10    | X9     | X8     | X7     | X6     | X5    | X4    | X3    | X2    | X1    | _     | 0000          |

| CRCDAT       | 0644 |        | CRC Data Input Register |        |        |        |        |        |        |        |        |       | 0000  |       |       |       |       |               |

| CRCWDAT      | 0646 |        | CRC Result Register     |        |        |        |        |        |        |        |        |       | 0000  |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### FLASH PROGRAM MEMORY 5.0

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 4. "Program Memory"                |

|       | (DS39715).                                 |

The PIC24FJ256GA110 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 2.35V. If the regulator is disabled, the VDDCORE voltage must be over 2.25V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ256GA110 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

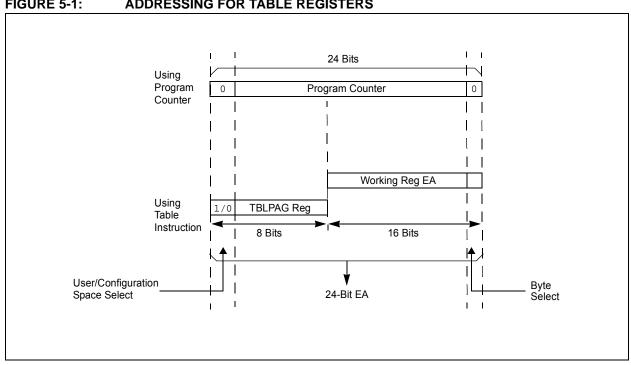

#### 5.1 **Table Instructions and Flash** Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| U-0          | U-0           | R/W-0                                  | R/W-0    | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|--------------|---------------|----------------------------------------|----------|-------------------|------------------|-----------------|--------|

| _            | _             | IC9IF                                  | OC9IF    | SPI3IF            | SPF3IF           | U4TXIF          | U4RXIF |

| bit 15       |               |                                        |          |                   |                  |                 | bit    |

| DAMO         | 11.0          |                                        |          |                   |                  |                 |        |

| R/W-0        | U-0           | R/W-0                                  | R/W-0    | R/W-0             | R/W-0            | R/W-0           | U-0    |

| U4ERIF       |               | MI2C3IF                                | SI2C3IF  | U3TXIF            | U3RXIF           | U3ERIF          |        |

| oit 7        |               |                                        |          |                   |                  |                 | bit    |

| _egend:      |               |                                        |          |                   |                  |                 |        |

| R = Readabl  | e bit         | W = Writable I                         | oit      | U = Unimplen      | nented bit, read | d as '0'        |        |

| n = Value at | POR           | '1' = Bit is set                       |          | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|              |               |                                        |          |                   |                  |                 |        |

| oit 15-14    | Unimpleme     | nted: Read as '0                       | )'       |                   |                  |                 |        |

| oit 13       |               | Capture Channe                         |          | lag Status bit    |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | •             | request has not                        |          | nt Elan Otatua I  | _: <b>.</b>      |                 |        |

| bit 12       |               | out Compare Cha<br>t request has occ   |          | pi riag Status i  | JIL              |                 |        |

|              |               | request has not                        |          |                   |                  |                 |        |

| oit 11       |               | 3 Event Interrupt                      |          | t                 |                  |                 |        |

|              |               | request has occ                        | -        |                   |                  |                 |        |

|              | 0 = Interrupt | request has not                        | occurred |                   |                  |                 |        |

| pit 10       |               | 13 Fault Interrupt                     | -        | t                 |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | •             | request has not                        |          |                   |                  |                 |        |

| oit 9        |               | RT4 Transmitter                        |          | Status bit        |                  |                 |        |

|              |               | request has not                        |          |                   |                  |                 |        |

| oit 8        |               | RT4 Receiver In                        |          | atus bit          |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | 0 = Interrupt | request has not                        | occurred |                   |                  |                 |        |

| oit 7        |               | RT4 Error Interro                      |          | s bit             |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | -             | request has not                        |          |                   |                  |                 |        |

| oit 6        | -             | nted: Read as '0                       |          | 0                 |                  |                 |        |

| oit 5        |               | aster I2C3 Event<br>request has occ    |          | Status bit        |                  |                 |        |

|              |               | request has not                        |          |                   |                  |                 |        |

| oit 4        | •             | ave I2C3 Event li                      |          | Status bit        |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | 0 = Interrupt | request has not                        | occurred |                   |                  |                 |        |

| oit 3        |               | RT3 Transmitter                        |          | Status bit        |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              | -             | request has not                        |          |                   |                  |                 |        |

| oit 2        |               | RT3 Receiver In                        |          | atus dit          |                  |                 |        |

|              |               | t request has occ<br>t request has not |          |                   |                  |                 |        |

| oit 1        | -             | RT3 Error Interro                      |          | s bit             |                  |                 |        |

|              |               | request has occ                        |          |                   |                  |                 |        |

|              |               | request has not                        |          |                   |                  |                 |        |

|              |               |                                        |          |                   |                  |                 |        |

| <b>REGISTER 7-19:</b> IPC2: INTERRUPT PRIORITY CONTROL REGISTER |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| U-0          | R/W-1                                                               | R/W-0                                                            | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------|------------------------------------------------------------------|-------------------|------------------|-----------------|-----------------|---------|--|--|--|--|--|--|--|

|              | U1RXIP2                                                             | U1RXIP1                                                          | U1RXIP0           |                  | SPI1IP2         | SPI1IP1         | SPI1IP0 |  |  |  |  |  |  |  |

| pit 15       |                                                                     |                                                                  |                   |                  |                 |                 | bit     |  |  |  |  |  |  |  |

|              |                                                                     |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| U-0          | R/W-1                                                               | R/W-0                                                            | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

| —            | SPF1IP2                                                             | SPF1IP1                                                          | SPF1IP0           | —                | T3IP2           | T3IP1           | T3IP0   |  |  |  |  |  |  |  |

| bit 7        |                                                                     |                                                                  |                   |                  |                 |                 | bit     |  |  |  |  |  |  |  |

|              |                                                                     |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| Legend:      |                                                                     |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| R = Readab   | ole bit                                                             | W = Writable                                                     | bit               | U = Unimple      | mented bit, rea | d as '0'        |         |  |  |  |  |  |  |  |

| -n = Value a | It POR                                                              | '1' = Bit is set                                                 |                   | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |  |  |  |

| L:1 4 F      | Unimalaman                                                          | tad: Daad as f                                                   | o'                |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 15       | -                                                                   | ted: Read as '                                                   |                   | Driarity bita    |                 |                 |         |  |  |  |  |  |  |  |

| bit 14-12    |                                                                     | : UART1 Rece<br>pt is priority 7 (I                              | =                 | -                |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  | ingricor priority | apt)             |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   | ntio maiority 1                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 11       |                                                                     | 000 = Interrupt source is disabled<br>Unimplemented: Read as '0' |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 10-8     | -                                                                   | SPI1 Event In                                                    |                   | hits             |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                                     | pt is priority 7 (I                                              |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   | p                                                                |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                                  | nt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                                     | pt is priority i<br>pt source is dis                             | abled             |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 7        |                                                                     | ted: Read as '                                                   |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 6-4      | -                                                                   | SPI1 Fault In                                                    |                   | bits             |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                                     | pt is priority 7 (I                                              |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  | /                 | • /              |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                                  | pt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              |                                                                     | pt source is dis                                                 | abled             |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 3        | Unimplemen                                                          | ted: Read as '                                                   | o'                |                  |                 |                 |         |  |  |  |  |  |  |  |

| bit 2-0      | T3IP<2:0>: ⊺                                                        | imer3 Interrupt                                                  | Priority bits     |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | 111 = Interru                                                       | pt is priority 7 (I                                              | highest priority  | interrupt)       |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •                                                                   |                                                                  |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

|              | •<br>001 = Interru                                                  | pt is priority 1                                                 |                   |                  |                 |                 |         |  |  |  |  |  |  |  |

### REGISTER 10-3: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 15-6 Unimplemented: Read as '0'

bit 5-0 INT4R<5:0>: Assign External Interrupt 4 (INT4) to Corresponding RPn or RPIn Pin bits

### REGISTER 10-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0          | U-0   | R/W-1        | R/W-1  | R/W-1                              | R/W-1  | R/W-1  | R/W-1  |

|--------------|-------|--------------|--------|------------------------------------|--------|--------|--------|

| _            | _     | T3CKR5       | T3CKR4 | T3CKR3                             | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15       |       |              |        |                                    |        |        | bit 8  |

|              |       |              |        |                                    |        |        |        |

| U-0          | U-0   | R/W-1        | R/W-1  | R/W-1                              | R/W-1  | R/W-1  | R/W-1  |

| _            | _     | T2CKR5       | T2CKR4 | T2CKR3                             | T2CKR2 | T2CKR1 | T2CKR0 |

| bit 7        |       |              |        |                                    |        |        | bit 0  |

|              |       |              |        |                                    |        |        |        |

| Legend:      |       |              |        |                                    |        |        |        |

| R = Readable | e bit | W = Writable | bit    | U = Unimplemented bit, read as '0' |        |        |        |

'0' = Bit is cleared

bit 15-14 **Unimplemented:** Read as '0'

'1' = Bit is set

bit 13-8 T3CKR<5:0>: Assign Timer3 External Clock (T3CK) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 T2CKR<5:0>: Assign Timer2 External Clock (T2CK) to Corresponding RPn or RPIn Pin bits

-n = Value at POR

x = Bit is unknown

### REGISTER 10-17: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      |     | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK2R<5:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI2R<5:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 10-18: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS2R<5:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

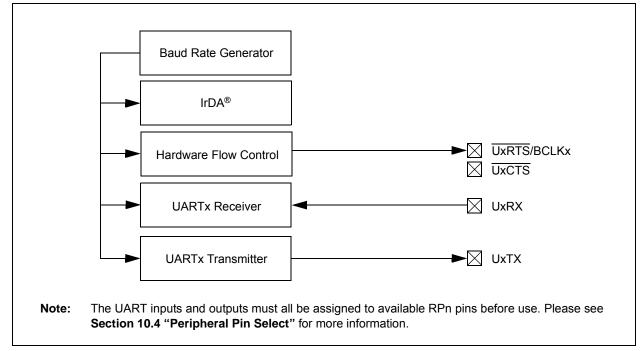

# 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | Section 21. "UART" (DS39708).              |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- · IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 17-1. The UART module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

# FIGURE 17-1: UART SIMPLIFIED BLOCK DIAGRAM

# REGISTER 18-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER (CONTINUED)

| bit 2 | <b>BEP:</b> Byte Enable Polarity bit<br>1 = Byte enable active-high (PMBE)<br>0 = Byte enable active-low (PMBE)                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                                            |

|       | For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):<br>1 = Write strobe active-high (PMWR)<br>0 = Write strobe active-low (PMWR) |

|       | For Master Mode 1 (PMMODE<9:8> = 11):<br>1 = Enable strobe active-high (PMENB)<br>0 = Enable strobe active-low (PMENB)                     |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                                             |

|       | For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):<br>1 = Read strobe active-high (PMRD)<br>0 = Read strobe active-low (PMRD)   |

|       | For Master Mode 1 (PMMODE<9:8> = 11):<br>1 = Read/write strobe active-high (PMRD/PMWR)<br>0 = Read/write strobe active-low (PMRD/PMWR)     |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

| R-0                   | R/W-0                                                                                                                                                                          | R/W-0                                                                                  | R/W-0          | R/W-0             | R/W-0                                | R/W-0                 | R/W-0                 |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------|-------------------|--------------------------------------|-----------------------|-----------------------|--|--|--|

| BUSY                  | IRQM1                                                                                                                                                                          | IRQM0                                                                                  | INCM1          | INCM0             | MODE16                               | MODE1                 | MODE0                 |  |  |  |

| bit 15                |                                                                                                                                                                                |                                                                                        |                |                   |                                      |                       | bit 8                 |  |  |  |

| R/W-0                 | R/W-0                                                                                                                                                                          | R/W-0                                                                                  | R/W-0          | R/W-0             | R/W-0                                | R/W-0                 | R/W-0                 |  |  |  |

| WAITB1 <sup>(1)</sup> | WAITB0 <sup>(1)</sup>                                                                                                                                                          | WAITM3                                                                                 | WAITM2         | WAITM1            | WAITM0                               | WAITE1 <sup>(1)</sup> | WAITE0 <sup>(1)</sup> |  |  |  |

| bit 7                 |                                                                                                                                                                                |                                                                                        |                |                   |                                      |                       | bit C                 |  |  |  |

| Legend:               |                                                                                                                                                                                |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

| R = Readab            | ole bit                                                                                                                                                                        | W = Writable                                                                           | bit            | U = Unimple       | mented bit, read                     | d as '0'              |                       |  |  |  |

| -n = Value a          | It POR                                                                                                                                                                         | '1' = Bit is set                                                                       |                | ʻ0' = Bit is cle  | eared                                | x = Bit is unkr       | nown                  |  |  |  |

| bit 15                | BUSY: Busy b                                                                                                                                                                   | oit (Master mod                                                                        | le only)       |                   |                                      |                       |                       |  |  |  |

|                       | -                                                                                                                                                                              | sy (not useful                                                                         | • •            | essor stall is a  | ctive)                               |                       |                       |  |  |  |

| bit 14-13             |                                                                                                                                                                                | nterrupt Reque                                                                         | et Mode hits   |                   |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                |                                                                                        |                | er 3 is read or V | Write Buffer 3 is                    | written (Buffere      | ed PSP mode)          |  |  |  |

|                       |                                                                                                                                                                                |                                                                                        |                |                   | 11 (Addressable                      | e PSP mode or         | ıly)                  |  |  |  |

|                       |                                                                                                                                                                                | rrupt generated at                                                                     |                |                   | cle                                  |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | rrupt generated                                                                        |                | read, write by    |                                      |                       |                       |  |  |  |

| bit 12-11             | INCM<1:0>: Increment Mode bits                                                                                                                                                 |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

|                       | 11 = PSP read and write buffers auto-increment (Legacy PSP mode only)                                                                                                          |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

|                       | <ul> <li>10 = Decrement ADDR&lt;10:0&gt; by 1 every read/write cycle</li> <li>01 = Increment ADDR&lt;10:0&gt; by 1 every read/write cycle</li> </ul>                           |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | ement or decre                                                                         | • •            | •                 |                                      |                       |                       |  |  |  |

| bit 10                | MODE16: 8/1                                                                                                                                                                    | 6-Bit Mode bit                                                                         |                |                   |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                |                                                                                        |                |                   | o the Data regis<br>the Data registe |                       |                       |  |  |  |

| bit 9-8               |                                                                                                                                                                                | Parallel Port N                                                                        |                |                   | C C                                  |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | 11 = Master Mode 1 (PMCS1, PMRD/PMWR, PMENB, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)</x:0> |                |                   |                                      |                       |                       |  |  |  |

|                       | 10 = Master Mode 2 (PMCS1, PMRD, PMWR, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)<br/>01 = Enhanced PSP, control signals (PMRD, PMWR, PMCS1, PMD&lt;7:0&gt; and PMA&lt;1:0&gt;)</x:0> |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

|                       | 01 = Ennanced PSP, control signals (PMRD, PMWR, PMCS1, PMD<7:0> and PMA<1:0>)<br>00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1 and PMD<7:0>)             |                                                                                        |                |                   |                                      |                       |                       |  |  |  |

| bit 7-6               | WAITB<1:0>:                                                                                                                                                                    | Data Setup to                                                                          | Read/Write W   | ait State Conf    | iguration bits <sup>(1)</sup>        |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | ait of 4 TCY; mu                                                                       | •              | •                 |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | ait of 3 TCY; mu<br>ait of 2 TCY; mu                                                   |                |                   |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | ait of 1 Tcy; mu                                                                       |                |                   |                                      |                       |                       |  |  |  |

| bit 5-2               | WAITM<3:0>:                                                                                                                                                                    | Read to Byte                                                                           | Enable Strobe  | Wait State Co     | onfiguration bits                    |                       |                       |  |  |  |

|                       | 1111 <b>= Wait c</b>                                                                                                                                                           | of additional 15                                                                       | Тсү            |                   |                                      |                       |                       |  |  |  |

|                       | <br>0001 = Wait o                                                                                                                                                              | of additional 1                                                                        | <b>I</b> CY    |                   |                                      |                       |                       |  |  |  |

|                       |                                                                                                                                                                                | ditional wait cy                                                                       |                | n forced into o   | ne Tcy) <sup>(2)</sup>               |                       |                       |  |  |  |