Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 192KB (65.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192ga110t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-670-8

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 64/80/100-Pin, 16-Bit, General Purpose Flash Microcontrollers with Peripheral Pin Select

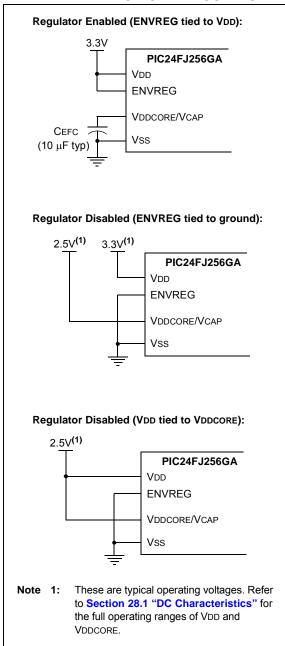

#### **Power Management:**

- On-Chip 2.5V Voltage Regulator

- · Switch between Clock Sources in Real Time

- Idle, Sleep and Doze modes with Fast Wake-up and Two-Speed Start-up

- Run mode: 1 mA/MIPS, 2.0V Typical

- Standby Current with 32 kHz Oscillator: 2.6 μA, 2.0V Typical

#### **High-Performance CPU:**

- Modified Harvard Architecture

- Up to 16 MIPS Operation at 32 MHz

- 8 MHz Internal Oscillator

- 17-Bit x 17-Bit Single-Cycle Hardware Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture with Flexible Addressing modes

- Linear Program Memory Addressing, Up to 12 Mbytes

- Linear Data Memory Addressing, Up to 64 Kbytes

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

#### **Analog Features:**

- 10-Bit, Up to 16-Channel Analog-to-Digital (A/D) Converter at 500 ksps:

- Conversions available in Sleep mode

- Three Analog Comparators with Programmable Input/ Output Configuration

- Charge Time Measurement Unit (CTMU)

#### **Peripheral Features:**

- Peripheral Pin Select:

- Allows independent I/O mapping of many peripherals at run time

- Continuous hardware integrity checking and safety interlocks prevent unintentional configuration changes

Up to 46 available pins (100-pin devices)

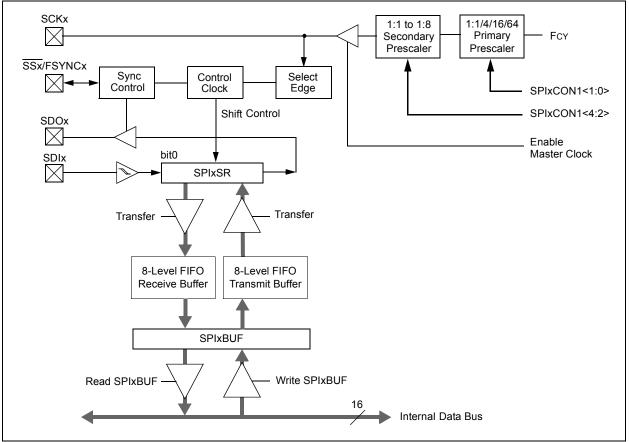

- Three 3-Wire/4-Wire SPI modules (supports 4 Frame modes) with 8-Level FIFO Buffer

- Three I<sup>2</sup>C<sup>™</sup> modules support Multi-Master/Slave modes and 7-Bit/10-Bit Addressing

- Four UART modules:

- Supports RS-485, RS-232, LIN/J2602 protocols and IrDA  $^{\ensuremath{\mathbb{R}}}$

- On-chip hardware encoder/decoder for IrDA

- Auto-wake-up and Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Five 16-Bit Timers/Counters with Programmable Prescaler

- Nine 16-Bit Capture Inputs, each with a Dedicated Time Base

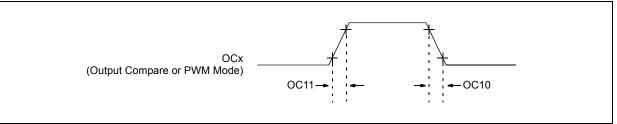

- Nine 16-Bit Compare/PWM Outputs, each with a Dedicated Time Base

- 8-Bit Parallel Master Port (PMP/PSP):

- Up to 16 address pins

- Programmable polarity on control lines

- Hardware Real-Time Clock/Calendar (RTCC):

Provides clock, calendar and alarm functions

- Programmable Cyclic Redundancy Check (CRC) Generator

- Up to 5 External Interrupt Sources

|                   |      | s)                        | ()           |                    | Rema          | ppable        | e Periph               | erals                     |     |      | (1              |             |         |      |      |

|-------------------|------|---------------------------|--------------|--------------------|---------------|---------------|------------------------|---------------------------|-----|------|-----------------|-------------|---------|------|------|

| PIC24FJ<br>Device | Pins | Program<br>Memory (Bytes) | SRAM (Bytes) | Remappable<br>Pins | Timers 16-Bit | Capture Input | Compare/<br>PWM Output | UART w/ IrDA <sup>®</sup> | SPI | I²C™ | 10-Bit A/D (ch) | Comparators | PMP/PSP | JTAG | CTMU |

| 64GA106           | 64   | 64K                       | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 128GA106          | 64   | 128K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 192GA106          | 64   | 192K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 256GA106          | 64   | 256K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 64GA108           | 80   | 64K                       | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 128GA108          | 80   | 128K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 192GA108          | 80   | 192K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 256GA108          | 80   | 256K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 64GA110           | 100  | 64K                       | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 128GA110          | 100  | 128K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 192GA110          | 100  | 192K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 256GA110          | 100  | 256K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

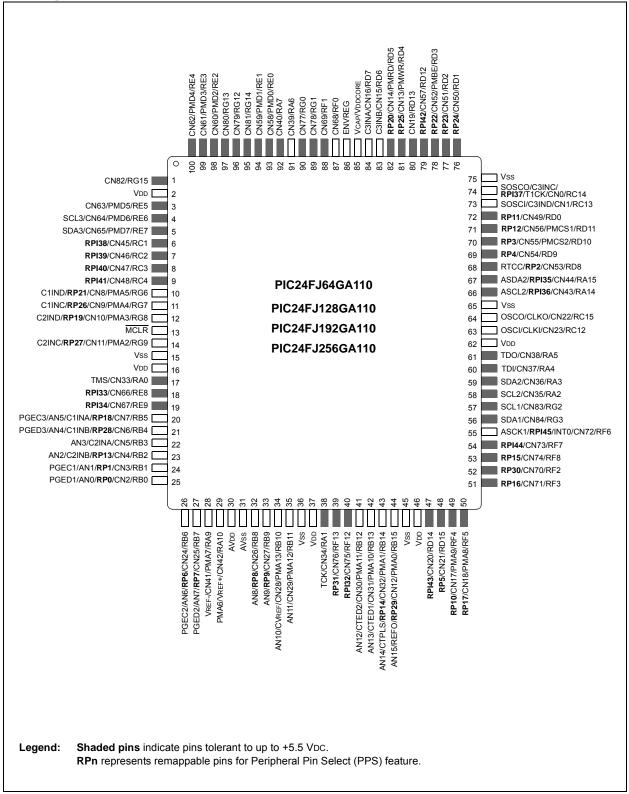

#### Pin Diagram (100-Pin TQFP)

|          |                     | Pin Number     |                 |     |                   |                                                                                            |

|----------|---------------------|----------------|-----------------|-----|-------------------|--------------------------------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer   | Description                                                                                |

| CTED1    | 28                  | 34             | 42              | I   | ANA               | CTMU External Edge Input 1.                                                                |

| CTED2    | 27                  | 33             | 41              | I   | ANA               | CTMU External Edge Input 2.                                                                |

| CTPLS    | 29                  | 35             | 43              | 0   |                   | CTMU Pulse Output.                                                                         |

| CVREF    | 23                  | 29             | 34              | 0   | _                 | Comparator Voltage Reference Output.                                                       |

| ENVREG   | 57                  | 71             | 86              | I   | ST                | Voltage Regulator Enable.                                                                  |

| INT0     | 35                  | 45             | 55              | I   | ST                | External Interrupt Input.                                                                  |

| MCLR     | 7                   | 9              | 13              | I   | ST                | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 39                  | 49             | 63              | I   | ANA               | Main Oscillator Input Connection.                                                          |

| OSCO     | 40                  | 50             | 64              | 0   | ANA               | Main Oscillator Output Connection.                                                         |

| PGEC1    | 15                  | 19             | 24              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 16                  | 20             | 25              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 17                  | 21             | 26              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 18                  | 22             | 27              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 11                  | 15             | 20              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 12                  | 16             | 21              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PMA0     | 30                  | 36             | 44              | I/O | ST                | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29                  | 35             | 43              | I/O | ST                | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8                   | 10             | 14              | 0   |                   | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | 6                   | 8              | 12              | 0   |                   | modes).                                                                                    |

| PMA4     | 5                   | 7              | 11              | 0   | _                 |                                                                                            |

| PMA5     | 4                   | 6              | 10              | 0   |                   |                                                                                            |

| PMA6     | 16                  | 24             | 29              | 0   |                   |                                                                                            |

| PMA7     | 22                  | 23             | 28              | 0   |                   |                                                                                            |

| PMA8     | 32                  | 40             | 50              | 0   |                   |                                                                                            |

| PMA9     | 31                  | 39             | 49              | 0   | _                 |                                                                                            |

| PMA10    | 28                  | 34             | 42              | 0   | _                 |                                                                                            |

| PMA11    | 27                  | 33             | 41              | 0   | _                 |                                                                                            |

| PMA12    | 24                  | 30             | 35              | 0   | _                 |                                                                                            |

| PMA13    | 23                  | 29             | 34              | 0   | _                 |                                                                                            |

| PMCS1    | 45                  | 57             | 71              | I/O | ST/TTL            | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMCS2    | 44                  | 56             | 70              | 0   | ST                | Parallel Master Port Chip Select 2 Strobe/Address Bit 14.                                  |

| PMBE     | 51                  | 63             | 78              | 0   | _                 | Parallel Master Port Byte Enable Strobe.                                                   |

| PMD0     | 60                  | 76             | 93              | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) or                                   |

| PMD1     | 61                  | 77             | 94              | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 62                  | 78             | 98              | I/O | ST/TTL            | 1                                                                                          |

| PMD3     | 63                  | 79             | 99              | I/O | ST/TTL            | 1                                                                                          |

| PMD4     | 64                  | 80             | 100             | I/O | ST/TTL            | 1                                                                                          |

| PMD5     | 1                   | 1              | 3               | I/O | ST/TTL            |                                                                                            |

| PMD6     | 2                   | 2              | 4               | I/O | ST/TTL            |                                                                                            |

| PMD7     | 3                   | 3              | 5               | I/O | ST/TTL            |                                                                                            |

| PMRD     | 53                  | 67             | 82              | 0   | _                 | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 52                  | 66             | 81              | 0   | _                 | Parallel Master Port Write Strobe.                                                         |

| Legend:  | TTL = TTL in        |                |                 | -   | ST = 5            | Schmitt Trigger input buffer                                                               |

|          | ANA = Analog        |                | utput           |     | I <sup>2</sup> C™ | = I <sup>2</sup> C/SMBus input buffer                                                      |

#### TABLE 1-4: PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                     | Pin Number     |                 |     | Incut           |                              |

|----------|---------------------|----------------|-----------------|-----|-----------------|------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | VO  | Input<br>Buffer | Description                  |

| RA0      | —                   | _              | 17              | I/O | ST              | PORTA Digital I/O.           |

| RA1      | _                   |                | 38              | I/O | ST              |                              |

| RA2      | _                   | _              | 58              | I/O | ST              |                              |

| RA3      | _                   | _              | 59              | I/O | ST              |                              |

| RA4      | _                   |                | 60              | I/O | ST              |                              |

| RA5      | —                   |                | 61              | I/O | ST              |                              |

| RA6      | _                   |                | 91              | I/O | ST              |                              |

| RA7      | —                   |                | 92              | I/O | ST              |                              |

| RA9      | _                   | 23             | 28              | I/O | ST              |                              |

| RA10     | _                   | 24             | 29              | I/O | ST              |                              |

| RA14     | _                   | 52             | 66              | I/O | ST              |                              |

| RA15     | _                   | 53             | 67              | I/O | ST              |                              |

| RB0      | 16                  | 20             | 25              | I/O | ST              | PORTB Digital I/O.           |

| RB1      | 15                  | 19             | 24              | I/O | ST              |                              |

| RB2      | 14                  | 18             | 23              | I/O | ST              |                              |

| RB3      | 13                  | 17             | 22              | I/O | ST              |                              |

| RB4      | 12                  | 16             | 21              | I/O | ST              | -                            |

| RB5      | 11                  | 15             | 20              | I/O | ST              |                              |

| RB6      | 17                  | 21             | 26              | I/O | ST              |                              |

| RB7      | 18                  | 22             | 27              | I/O | ST              |                              |

| RB8      | 21                  | 27             | 32              | I/O | ST              |                              |

| RB9      | 22                  | 28             | 33              | I/O | ST              |                              |

| RB10     | 23                  | 29             | 34              | I/O | ST              |                              |

| RB11     | 24                  | 30             | 35              | I/O | ST              |                              |

| RB12     | 27                  | 33             | 41              | I/O | ST              |                              |

| RB13     | 28                  | 34             | 42              | I/O | ST              |                              |

| RB14     | 29                  | 35             | 43              | I/O | ST              | 1                            |

| RB15     | 30                  | 36             | 44              | I/O | ST              | 1                            |

| RC1      | —                   | 4              | 6               | I/O | ST              | PORTC Digital I/O.           |

| RC2      | _                   | _              | 7               | I/O | ST              | 1                            |

| RC3      | _                   | 5              | 8               | I/O | ST              | 1                            |

| RC4      | _                   | _              | 9               | I/O | ST              | 1                            |

| RC12     | 39                  | 49             | 63              | I/O | ST              | 1                            |

| RC13     | 47                  | 59             | 73              | I/O | ST              | 1                            |

| RC14     | 48                  | 60             | 74              | I/O | ST              | 1                            |

| RC15     | 40                  | 50             | 64              | I/O | ST              | 1                            |

| Legend:  | TTI = TTI inr       |                | 1               | I   |                 | Schmitt Trigger innut huffer |

| TABLE 1-4:    | PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED) |

|---------------|--------------------------------------------------------|

| $IADLL I^{-}$ |                                                        |

**Legend:** TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer

I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

| R/W-0         | R/W-0                                  | R/W-0                                                    | R/W-0                     | R/W-0             | R/W-0           | R/W-0           | U-0     |

|---------------|----------------------------------------|----------------------------------------------------------|---------------------------|-------------------|-----------------|-----------------|---------|

| U2TXIF        | U2RXIF                                 | INT2IF                                                   | T5IF                      | T4IF              | OC4IF           | OC3IF           | —       |

| bit 15        | ·                                      | •                                                        |                           |                   |                 |                 | bit 8   |

| R/W-0         | R/W-0                                  | U-0                                                      | R/W-0                     | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| IC8IF         | IC7IF                                  | 0-0                                                      | INT1IF                    | CNIF              | CMIF            | MI2C1IF         | SI2C1IF |

| bit 7         | 10711                                  |                                                          |                           | CINII             | Civili          | WIZCTI          | bit C   |

| Legend:       |                                        |                                                          |                           |                   |                 |                 |         |

| R = Readabl   | le bit                                 | W = Writable I                                           | oit                       | U = Unimplerr     | nented bit, rea | d as '0'        |         |

| -n = Value at |                                        | '1' = Bit is set                                         |                           | '0' = Bit is clea |                 | x = Bit is unkn | own     |

|               |                                        |                                                          |                           |                   |                 |                 | -       |

| bit 15        | 1 = Interrupt i                        | RT2 Transmitter<br>request has occ<br>request has not    | urred                     | Status bit        |                 |                 |         |

| bit 14        | U2RXIF: UAF<br>1 = Interrupt I         | RT2 Receiver In<br>request has occ<br>request has not    | terrupt Flag St<br>urred  | atus bit          |                 |                 |         |

| bit 13        | INT2IF: Exter<br>1 = Interrupt I       | request has not<br>request has occ<br>request has not    | Flag Status bit<br>surred |                   |                 |                 |         |

| bit 12        | 1 = Interrupt i                        | Interrupt Flag S<br>request has occ<br>request has not   | urred                     |                   |                 |                 |         |

| bit 11        | 1 = Interrupt i                        | Interrupt Flag S<br>request has occ<br>request has not   | urred                     |                   |                 |                 |         |

| bit 10        | 1 = Interrupt i                        | ut Compare Cha<br>request has occ<br>request has not     | urred                     | pt Flag Status b  | bit             |                 |         |

| bit 9         | 1 = Interrupt i                        | ut Compare Cha<br>request has occ<br>request has not     | urred                     | pt Flag Status b  | bit             |                 |         |

| bit 8         | Unimplemen                             | ted: Read as 'o                                          | )'                        |                   |                 |                 |         |

| bit 7         | 1 = Interrupt i                        | Capture Channe<br>request has occ<br>request has not     | urred                     | lag Status bit    |                 |                 |         |

| bit 6         | 1 = Interrupt i                        | Capture Channe<br>request has occ<br>request has not     | urred                     | lag Status bit    |                 |                 |         |

| bit 5         | Unimplemen                             | ted: Read as 'o                                          | )'                        |                   |                 |                 |         |

| bit 4         | 1 = Interrupt i                        | rnal Interrupt 1 I<br>request has occ<br>request has not | urred                     |                   |                 |                 |         |

| bit 3         | 1 = Interrupt i                        | Change Notificat<br>request has occ<br>request has not   | urred                     | lag Status bit    |                 |                 |         |

| bit 2         | <b>CMIF:</b> Compa<br>1 = Interrupt i  | arator Interrupt<br>request has occ<br>request has not   | Flag Status bit<br>urred  |                   |                 |                 |         |

| bit 1         | <b>MI2C1IF:</b> Mai<br>1 = Interrupt i | ster I2C1 Event<br>request has occ<br>request has not    | Interrupt Flag<br>urred   | Status bit        |                 |                 |         |

| bit 0         | SI2C1IF: Slav                          | ve I2C1 Event li<br>request has occ                      | nterrupt Flag S           | Status bit        |                 |                 |         |

|                             | R/W-1                                                                                     | R/W-0                                                                                                      | R/W-0                                                         | U-0                 | R/W-1  | R/W-0           | R/W-0  |  |  |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|--------|-----------------|--------|--|--|--|--|--|--|

| _                           | IC5IP2                                                                                    | IC5IP1                                                                                                     | IC5IP0                                                        |                     | IC4IP2 | IC4IP1          | IC4IP0 |  |  |  |  |  |  |

| bit 15                      |                                                                                           |                                                                                                            |                                                               |                     |        |                 | bit    |  |  |  |  |  |  |

| U-0                         | R/W-1                                                                                     | R/W-0                                                                                                      | R/W-0                                                         | U-0                 | U-0    | U-0             | U-0    |  |  |  |  |  |  |

| _                           | IC3IP2                                                                                    | IC3IP1                                                                                                     | IC3IP0                                                        | _                   | _      | _               | _      |  |  |  |  |  |  |

| bit 7                       |                                                                                           |                                                                                                            |                                                               |                     |        |                 | bit    |  |  |  |  |  |  |

| Legend:                     |                                                                                           |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

| R = Readat                  | ole bit                                                                                   | W = Writable                                                                                               | able bit U = Unimplemented bit, read as '0'                   |                     |        |                 |        |  |  |  |  |  |  |

| -n = Value a                | at POR                                                                                    | '1' = Bit is set                                                                                           |                                                               | '0' = Bit is clea   | ared   | x = Bit is unkn | own    |  |  |  |  |  |  |

| bit 15                      | Unimplemer                                                                                | nted: Read as '                                                                                            | כי                                                            |                     |        |                 |        |  |  |  |  |  |  |

| bit 14-12                   | Unimplemented: Read as '0'<br>IC5IP<2:0>: Input Capture Channel 5 Interrupt Priority bits |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

| 511 14-12                   |                                                                                           | 111 = Interrupt is priority 7 (highest priority interrupt)                                                 |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         | ipt is priority / (                                                                                        | lighest phoney                                                | mienupi)            |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         | •                                                                                                          |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             |                                                                                           | ipt is priority 1<br>ipt source is dis                                                                     | abled                                                         |                     |        |                 |        |  |  |  |  |  |  |

| bit 11                      | Unimplemer                                                                                | nted: Read as '                                                                                            | כ'                                                            |                     |        |                 |        |  |  |  |  |  |  |

| bit 10-8                    | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits                               |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | 111 = Interrupt is priority 7 (highest priority interrupt)                                |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | •                                                                                         |                                                                                                            |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | 001 - Interru                                                                             | unt in priority 1                                                                                          |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             |                                                                                           | upt is priority 1                                                                                          | abled                                                         |                     |        |                 |        |  |  |  |  |  |  |

| hit 7                       | 000 = Interru                                                                             | ipt source is dis                                                                                          |                                                               |                     |        |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer                                                               | ipt source is dis<br>nted: Read as '                                                                       | )'                                                            | rrunt Priority hits |        |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer<br>IC3IP<2:0>:                                                | ipt source is dis<br><b>ted:</b> Read as '<br>Input Capture C                                              | o'<br>Channel 3 Inter                                         | rupt Priority bits  | 3      |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer<br>IC3IP<2:0>:                                                | ipt source is dis<br>nted: Read as '                                                                       | o'<br>Channel 3 Inter                                         |                     | 3      |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer<br>IC3IP<2:0>:                                                | ipt source is dis<br><b>ted:</b> Read as '<br>Input Capture C                                              | o'<br>Channel 3 Inter                                         |                     | 3      |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer<br>IC3IP<2:0>:<br>111 = Interru<br>•                          | ipt source is dis<br>nted: Read as '<br>Input Capture C<br>ipt is priority 7 (                             | o'<br>Channel 3 Inter                                         |                     | 5      |                 |        |  |  |  |  |  |  |

|                             | 000 = Interru<br>Unimplemer<br>IC3IP<2:0>:<br>111 = Interru                               | ipt source is dis<br><b>nted:</b> Read as '<br>Input Capture C<br>ipt is priority 7 (<br>upt is priority 1 | <sup>)'</sup><br>Channel 3 Inter<br>nighest priority          |                     | 3      |                 |        |  |  |  |  |  |  |

| bit 7<br>bit 6-4<br>bit 3-0 | 000 = Interru<br>Unimplemen<br>IC3IP<2:0>:<br>111 = Interru                               | ipt source is dis<br>nted: Read as '<br>Input Capture C<br>ipt is priority 7 (                             | <sup>),</sup><br>Channel 3 Inter<br>nighest priority<br>abled |                     | 3      |                 |        |  |  |  |  |  |  |

#### REGISTER 7-26: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

#### REGISTER 7-29: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | —   | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 |

| bit 15 |     |     |     |     |          |          | bit 8    |

| U-0   | R/W-1    | R/W-0    | R/W-0    | U-0 | U-0 | U-0 | U-0   |

|-------|----------|----------|----------|-----|-----|-----|-------|

| —     | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | —   | —   | —   | —     |

| bit 7 |          |          |          |     |     |     | bit 0 |

| Legend:       |                                                                       |                                  |                        |                    |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------|----------------------------------|------------------------|--------------------|--|--|--|--|--|--|

| R = Readab    | le bit                                                                | W = Writable bit                 | U = Unimplemented bit, | , read as '0'      |  |  |  |  |  |  |

| -n = Value at | t POR                                                                 | '1' = Bit is set                 | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |  |

|               |                                                                       |                                  |                        |                    |  |  |  |  |  |  |

| bit 15-11     | Unimpler                                                              | mented: Read as '0'              |                        |                    |  |  |  |  |  |  |

| bit 10-8      | MI2C2IP<                                                              | <2:0>: Master I2C2 Event Inf     | terrupt Priority bits  |                    |  |  |  |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                                  |                        |                    |  |  |  |  |  |  |

|               | •                                                                     |                                  |                        |                    |  |  |  |  |  |  |

|               | •                                                                     |                                  |                        |                    |  |  |  |  |  |  |

|               |                                                                       |                                  |                        |                    |  |  |  |  |  |  |

|               | 001 = Interrupt is priority 1                                         |                                  |                        |                    |  |  |  |  |  |  |

|               |                                                                       | errupt source is disabled        |                        |                    |  |  |  |  |  |  |

| bit 7         | Unimpler                                                              | nented: Read as '0'              |                        |                    |  |  |  |  |  |  |

| bit 6-4       | SI2C2IP<                                                              | 2:0>: Slave I2C2 Event Inte      | rrupt Priority bits    |                    |  |  |  |  |  |  |

|               | 111 = Inte                                                            | errupt is priority 7 (highest pr | riority interrupt)     |                    |  |  |  |  |  |  |

|               | •                                                                     |                                  |                        |                    |  |  |  |  |  |  |

|               | •                                                                     |                                  |                        |                    |  |  |  |  |  |  |

|               | •                                                                     |                                  |                        |                    |  |  |  |  |  |  |

|               |                                                                       | errupt is priority 1             |                        |                    |  |  |  |  |  |  |

|               |                                                                       | errupt source is disabled        |                        |                    |  |  |  |  |  |  |

| bit 3-0       | Unimpler                                                              | mented: Read as '0'              |                        |                    |  |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                      | R/W-0                                  | R/W-0        | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| —            | SPI3IP2                                                                                                                    | SPI3IP1                                | SPI3IP0      | —                | SPF3IP2          | SPF3IP1         | SPF3IP0 |  |  |  |  |  |  |

| bit 15       |                                                                                                                            |                                        |              |                  |                  |                 | bit     |  |  |  |  |  |  |

|              |                                                                                                                            |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                      | R/W-0                                  | R/W-0        | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

| _            | U4TXIP2                                                                                                                    | U4TXIP1                                | U4TXIP0      | _                | U4RXIP2          | U4RXIP1         | U4RXIP0 |  |  |  |  |  |  |

| bit 7        |                                                                                                                            |                                        |              |                  |                  |                 | bit     |  |  |  |  |  |  |

|              |                                                                                                                            |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| Legend:      | 1 - 1-14                                                                                                                   |                                        | L:4          |                  |                  | l = = (0)       |         |  |  |  |  |  |  |

| R = Readab   |                                                                                                                            | W = Writable                           |              | -                | mented bit, read |                 |         |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                      | '1' = Bit is set                       |              | '0' = Bit is cle | eared            | x = Bit is unkr | lown    |  |  |  |  |  |  |

| bit 15       | Unimplomo                                                                                                                  | ntod: Dood op '                        | o'           |                  |                  |                 |         |  |  |  |  |  |  |

| bit 14-12    | Unimplemented: Read as '0'                                                                                                 |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| 011 14-12    | <b>SPI3IP&lt;2:0&gt;:</b> SPI3 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          | •                                      |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                        |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 11       |                                                                                                                            | -                                      |              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 10-8     | Unimplemented: Read as '0'<br>SPF3IP<2:0>: SPI3 Fault Interrupt Priority bits                                              |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                 |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                        |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 7        |                                                                                                                            | nted: Read as '                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 6-4      | -                                                                                                                          | >: UART4 Trans                         |              | t Priority hits  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                            | upt is priority 7 (                    | -            | -                |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        | geet prienty |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •<br>001 - Intern                                                                                                          | unt in priority 1                      |              |                  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                            | upt is priority 1<br>upt source is dis | abled        |                  |                  |                 |         |  |  |  |  |  |  |

| bit 3        |                                                                                                                            | nted: Read as '                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 2-0      | -                                                                                                                          | >: UART4 Rece                          |              | Priority bits    |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                            | upt is priority 7 (                    |              | -                |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                          |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

|              | •<br>001 - Interr                                                                                                          | upt is priority 1                      |              |                  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                            |                                        |              |                  |                  |                 |         |  |  |  |  |  |  |

| U-0                               | U-0                       | U-0                 | U-0                       | U-0                                     | U-0                 | U-0                 | U-0                 |  |  |  |

|-----------------------------------|---------------------------|---------------------|---------------------------|-----------------------------------------|---------------------|---------------------|---------------------|--|--|--|

|                                   | —                         |                     | —                         | —                                       | —                   | _                   | —                   |  |  |  |

| bit 15                            |                           |                     |                           |                                         |                     |                     | bit 8               |  |  |  |

|                                   |                           |                     |                           |                                         |                     |                     |                     |  |  |  |

| U-0                               | U-0                       | R/W-0               | R/W-0                     | R/W-0                                   | R/W-0               | R/W-0               | R/W-0               |  |  |  |

| _                                 | —                         | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup>                     | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |  |  |  |

| bit 7                             |                           |                     | •                         |                                         | •                   |                     | bit 0               |  |  |  |

|                                   |                           |                     |                           |                                         |                     |                     |                     |  |  |  |

| Legend:                           |                           |                     |                           |                                         |                     |                     |                     |  |  |  |

| R = Readable bit W = Writable bit |                           |                     |                           | U = Unimplemented bit, read as '0'      |                     |                     |                     |  |  |  |

| -n = Value a                      | at POR                    | '1' = Bit is set    |                           | '0' = Bit is cleared x = Bit is unknown |                     |                     |                     |  |  |  |

|                                   |                           |                     |                           |                                         |                     |                     |                     |  |  |  |

| bit 15-6                          | Unimplemen                | ted: Read as '      | D'                        |                                         |                     |                     |                     |  |  |  |

| bit 5-0                           | <b>TUN&lt;5:0&gt;:</b> Fl | RC Oscillator T     | uning bits <sup>(1)</sup> |                                         |                     |                     |                     |  |  |  |

|                                   | 011111 <b>= Ma</b>        | iximum frequer      | ncy deviation             |                                         |                     |                     |                     |  |  |  |

|                                   | 011110 =                  |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   | •                         |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   | •                         |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   | 000001 =                  |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   |                           | nter frequency      | oscillator is ru          | inning at factory                       | calibrated free     | uencv               |                     |  |  |  |

|                                   | 111111 =                  |                     |                           |                                         | ,                   | 1                   |                     |  |  |  |

|                                   | •                         |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   | •                         |                     |                           |                                         |                     |                     |                     |  |  |  |

|                                   | •                         |                     |                           |                                         |                     |                     |                     |  |  |  |

#### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

#### 8.4 Clock Switching Operation

100001 =

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

100000 = Minimum frequency deviation

| Note: | The Primary Oscillator mode has three different submodes (XT, HS and EC) |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------|--|--|--|--|--|--|

|       | which are determined by the POSCMDx                                      |  |  |  |  |  |  |

|       | Configuration bits. While an application                                 |  |  |  |  |  |  |

|       | can switch to and from Primary Oscillator                                |  |  |  |  |  |  |

|       | mode in software, it cannot switch                                       |  |  |  |  |  |  |

|       | between the different primary submodes                                   |  |  |  |  |  |  |

|       | without reprogramming the device.                                        |  |  |  |  |  |  |

#### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in CW 2 must be programmed to '0'. (Refer to **Section 25.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

Peripheral Pin Select is not available for  $I^2C^{TM}$ , change notification inputs, RTCC alarm outputs or peripherals with analog inputs.

A key difference between pin select and non pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g. OC, UART Transmit) take priority over general purpose digital functions on a pin, such as PMP and port I/O. Specialized digital outputs, such as USB functionality, will take priority over PPS outputs on the same pin. The pin diagrams provided at the beginning of this data sheet list peripheral outputs in order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin-selectable peripheral inputs never take ownership of a pin. The pin's output buffer is controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 10.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

#### 10.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-21). Each register contains two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Select options supported by the device.

#### 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 10-22 through Register 10-37). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-3).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

#### 10.4.3.3 Alternate Fixed Pin Mapping

To provide a migration option from earlier high pin count PIC24F devices, PIC24FJ256GA110 family devices implement an additional option for mapping the clock output (SCK) of SPI1. This option permits users to map SCK10UT specifically to the fixed pin function, ASCK1. The SCK1CM bit (ALTRP<0>) controls this mapping; setting the bit maps SCK10UT to ASCK1.

The SCK1CM bit must be set (= 1) before enabling the SPI module. It must remain set while transactions using SPI1 are in progress, in order to prevent transmission errors; when the module is disabled, the bit must be cleared. Additionally, no other RPOUT register should be configured to output the SCK1OUT function while SCK1CM is set.

#### REGISTER 10-9: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

| U-0                                | U-0 | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------------------------------------|-----|-------|-----------------------------------------|-------|-------|-------|-------|

| —                                  | —   | IC8R5 | IC8R4                                   | IC8R3 | IC8R2 | IC8R1 | IC8R0 |

| bit 15                             |     |       |                                         |       |       | •     | bit 8 |

|                                    |     |       |                                         |       |       |       |       |

| U-0                                | U-0 | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|                                    | —   | IC7R5 | IC7R4                                   | IC7R3 | IC7R2 | IC7R1 | IC7R0 |

| bit 7                              |     |       |                                         |       |       |       | bit 0 |

|                                    |     |       |                                         |       |       |       |       |

| Legend:                            |     |       |                                         |       |       |       |       |

| R = Readable bit W = Writable bit  |     | bit   | U = Unimplemented bit, read as '0'      |       |       |       |       |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is cleared x = Bit is unknown |       | nown  |       |       |

|                                    |     |       |                                         |       |       |       |       |

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC8R<5:0>: Assign Input Capture 8 (IC8) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC7R<5:0>: Assign Input Capture 7 (IC7) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 10-10: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |