Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga106-e-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

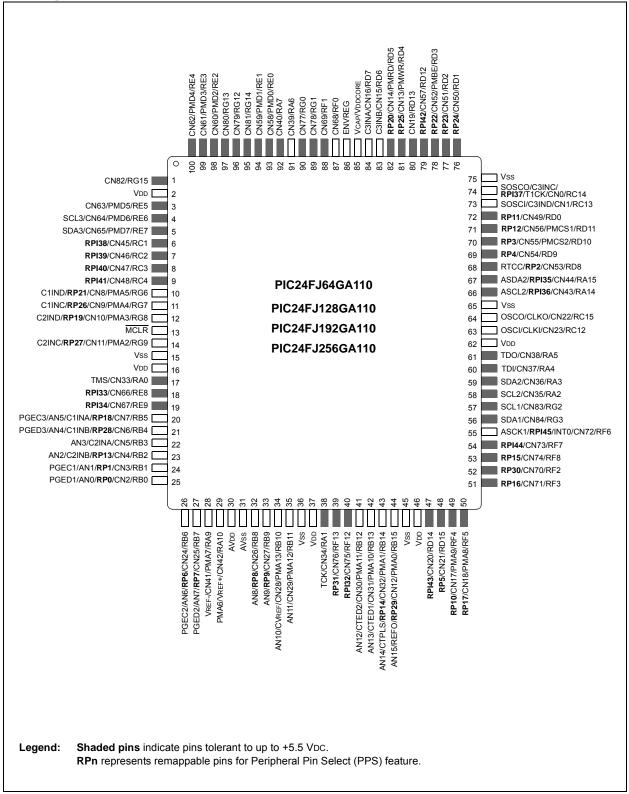

## Pin Diagram (100-Pin TQFP)

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

## 3.3.2 DIVIDER

The divide block supports signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

#### TABLE 4-20: ADC REGISTER MAP

| File<br>Name | Addr   | Bit 15     | Bit 14      | Bit 13     | Bit 12      | Bit 11      | Bit 10     | Bit 9       | Bit 8       | Bit 7       | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|--------|------------|-------------|------------|-------------|-------------|------------|-------------|-------------|-------------|-------|-------|--------|--------|--------|--------|--------|---------------|

|              | 0200   |            |             |            |             |             |            |             |             | - Duffer 0  |       |       |        |        |        |        |        |               |

| ADC1BUF0     | 0300   |            |             |            |             |             |            |             |             | a Buffer 0  |       |       |        |        |        |        |        | XXXX          |

| ADC1BUF1     | 0302   |            |             |            |             |             |            |             | ADC Dat     |             |       |       |        |        |        |        |        | XXXX          |

| ADC1BUF2     | 0304   |            |             |            |             |             |            |             |             | a Buffer 2  |       |       |        |        |        |        |        | XXXX          |

| ADC1BUF3     | 0306   |            |             |            |             |             |            |             |             | a Buffer 3  |       |       |        |        |        |        |        | XXXX          |

| ADC1BUF4     | 0308   |            |             |            |             |             |            |             |             | a Buffer 4  |       |       |        |        |        |        |        | XXXX          |

| ADC1BUF5     | 030A   |            |             |            |             |             |            |             |             | a Buffer 5  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF6     | 030C   |            |             |            |             |             |            |             |             | a Buffer 6  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF7     | 030E   |            |             |            |             |             |            |             | ADC Dat     | a Buffer 7  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF8     | 0310   |            |             |            |             |             |            |             | ADC Dat     | a Buffer 8  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF9     | 0312   |            |             |            |             |             |            |             | ADC Data    | a Buffer 9  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFA     | 0314   |            |             |            |             |             |            |             | ADC Data    | a Buffer 10 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFB     | 0316   |            |             |            |             |             |            |             | ADC Data    | a Buffer 11 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFC     | 0318   |            |             |            |             |             |            |             | ADC Data    | a Buffer 12 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFD     | 031A   |            |             |            |             |             |            |             | ADC Data    | a Buffer 13 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFE     | 031C   |            |             |            |             |             |            |             | ADC Data    | a Buffer 14 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFF     | 031E   |            |             |            |             |             |            |             | ADC Data    | a Buffer 15 |       |       |        |        |        |        |        | xxxx          |

| AD1CON1      | 0320   | ADON       | _           | ADSIDL     | _           | _           | _          | FORM1       | FORM0       | SSRC2       | SSRC1 | SSRC0 | _      | _      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2      | 0322   | VCFG2      | VCFG1       | VCFG0      | r           | _           | CSCNA      | _           | _           | BUFS        |       | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3      | 0324   | ADRC       | r           | r          | SAMC4       | SAMC3       | SAMC2      | SAMC1       | SAMC0       | ADCS7       | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0328   | CH0NB      | _           | _          | CH0SB4      | CH0SB3      | CH0SB2     | CH0SB1      | CH0SB0      | CH0NA       |       | _     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFGL     | 032C   | PCFG15     | PCFG14      | PCFG13     | PCFG12      | PCFG11      | PCFG10     | PCFG9       | PCFG8       | PCFG7       | PCFG6 | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1PCFGH     | 032A   | _          | _           | _          | _           | _           | _          | —           | _           | _           | _     | _     | —      | _      | —      | PCFG17 | PCFG16 | 0000          |

| AD1CSSL      | 0330   | CSSL15     | CSSL14      | CSSL13     | CSSL12      | CSSL11      | CSSL10     | CSSL9       | CSSL8       | CSSL7       | CSSL6 | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

| Legend:      | = unii | mplemented | , se hear h | r = record | Vod maintai | n as 'o' Pe | sot values | are shown i | in hevadeci | mal         |       |       |        |        |        |        |        | 4             |

Legend: — = unimplemented, read as '0', r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: CTMU REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON      | 033C | CTMUEN |        | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON     | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  | _       | _        | _        | -       |          | -        | _        | -        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

## 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

## 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |  |  |  |

- 3. Clear the interrupt status flag bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value E0h with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enabled bit                                                |

|---------|------------------------------------------------------------------------------------------|

|         | <u>If FSCM is enabled (FCKSM1 = 1):</u>                                                  |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | <u>If FSCM is disabled (FCKSM1 = 0):</u>                                                 |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                               |

|         | 1 = I/O lock is active                                                                   |

|         | 0 = I/O lock is not active                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                 |

|         | 1 = PLL module is in lock or PLL module start-up timer is satisfied                      |

|         | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled          |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | POSCEN: Primary Oscillator Sleep Enable bit                                              |

|         | 1 = Primary Oscillator continues to operate during Sleep mode                            |

|         | 0 = Primary Oscillator disabled during Sleep mode                                        |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enable Secondary Oscillator                                                          |

|         | 0 = Disable Secondary Oscillator                                                         |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiate an oscillator switch to clock source specified by NOSC<2:0> bits            |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1. | Departurely on far theory hits are determined by the ENOCO Configuration hits            |

- **Note 1:** Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- **3:** Also, resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

| R/W-0        | U-0                        | R/W-0                                                 | R/W-0                  | R/W-0             | R/W-0            | R/W-0            | R/W-0         |

|--------------|----------------------------|-------------------------------------------------------|------------------------|-------------------|------------------|------------------|---------------|

| ROEN         |                            | ROSSLP                                                | ROSEL                  | RODIV3            | RODIV2           | RODIV1           | RODIV0        |

| bit 15       |                            |                                                       |                        |                   |                  |                  | bit 8         |

| U-0          | U-0                        | U-0                                                   | U-0                    | U-0               | U-0              | U-0              | U-0           |

| _            | _                          | _                                                     | _                      | _                 | _                | _                | _             |

| bit 7        |                            |                                                       |                        |                   |                  |                  | bit C         |

| Legend:      |                            |                                                       |                        |                   |                  |                  |               |

| R = Readab   | ole bit                    | W = Writable                                          | bit                    | U = Unimplem      | nented bit, read | d as '0'         |               |

| -n = Value a | It POR                     | '1' = Bit is set                                      |                        | '0' = Bit is clea | ared             | x = Bit is unkn  | own           |

|              |                            |                                                       |                        |                   |                  |                  |               |

| bit 15       |                            | ence Oscillator                                       | -                      |                   |                  |                  |               |

|              |                            | e oscillator ena<br>e oscillator disa                 |                        | pin               |                  |                  |               |

| bit 14       | Unimplemen                 | ted: Read as '                                        | 0'                     |                   |                  |                  |               |

| bit 13       | ROSSLP: Re                 | ference Oscilla                                       | tor Output Sto         | p in Sleep bit    |                  |                  |               |

|              |                            | e oscillator con                                      |                        |                   |                  |                  |               |

|              | 0 = Reference              | e oscillator is d                                     | isabled in Slee        | р                 |                  |                  |               |

| bit 12       |                            | erence Oscillato                                      |                        |                   |                  |                  |               |

|              |                            |                                                       |                        | the operation ir  |                  | illator must be  | enabled using |

|              |                            | •                                                     |                        |                   | •                | switching of the | device        |

| bit 11-8     | RODIV<3:0>:                | Reference Os                                          | cillator Divisor       | Select bits       |                  |                  |               |

|              |                            | clock value div                                       | •                      |                   |                  |                  |               |

|              |                            | clock value div<br>clock value div                    | •                      | ļ.                |                  |                  |               |

|              |                            | clock value div                                       |                        |                   |                  |                  |               |

|              | 1011 <b>= Base</b>         | clock value div                                       | ided by 2,048          |                   |                  |                  |               |

|              |                            | clock value div                                       |                        |                   |                  |                  |               |

|              |                            | clock value div<br>clock value div                    |                        |                   |                  |                  |               |

|              | 0111 = Base                | clock value div                                       | ided by 128            |                   |                  |                  |               |

|              |                            | clock value div<br>clock value div                    |                        |                   |                  |                  |               |

|              |                            | clock value div                                       |                        |                   |                  |                  |               |

|              |                            |                                                       |                        |                   |                  |                  |               |

|              | 0011 = Base                | clock value div                                       | ided by 8              |                   |                  |                  |               |

|              | 0011 = Base<br>0010 = Base | clock value div<br>clock value div                    | ided by 8<br>ided by 4 |                   |                  |                  |               |

|              | 0011 = Base<br>0010 = Base | clock value div<br>clock value div<br>clock value div | ided by 8<br>ided by 4 |                   |                  |                  |               |

## © 2010 Microchip Technology Inc.

NOTES:

#### REGISTER 10-22: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0            | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0            | R/W-0         |

|---------------|----------------|------------------|----------------|-------------------|------------------|------------------|---------------|

| _             |                | RP1R5            | RP1R4          | RP1R3             | RP1R2            | RP1R1            | RP1R0         |

| bit 15        |                |                  |                |                   |                  |                  | bit 8         |

|               |                |                  |                |                   |                  |                  |               |

| U-0           | U-0            | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0            | R/W-0         |

| —             | _              | RP0R5            | RP0R4          | RP0R3             | RP0R2            | RP0R1            | RP0R0         |

| bit 7         |                |                  |                |                   |                  |                  | bit 0         |

|               |                |                  |                |                   |                  |                  |               |

| Legend:       |                |                  |                |                   |                  |                  |               |

| R = Readable  | e bit          | W = Writable I   | bit            | U = Unimplen      | nented bit, read | l as '0'         |               |

| -n = Value at | POR            | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr  | nown          |

|               |                |                  |                |                   |                  |                  |               |

| bit 15-14     | Unimplemen     | ted: Read as 'o  | )'             |                   |                  |                  |               |

| bit 13-8      | RP1R<5:0>:     | RP1 Output Pin   | n Mapping bits | i                 |                  |                  |               |

|               | Peripheral out | tput number n i  | s assigned to  | pin, RP1 (see T   | able 10-3 for p  | eripheral functi | ion numbers). |

|               |                |                  |                |                   |                  |                  |               |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP0R<5:0>:** RP0 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP0 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-23: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP3R5 | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RP2R5 | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP3 (see Table 10-3 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP2 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-36: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

|        | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0    |

|--------|--------|--------|--------|--------|--------|--------|-----|--------|

| bit 15 | RP29R0 | RP29R1 | RP29R2 | RP29R3 | RP29R4 | RP29R5 | —   | —      |

|        | bit 8  |        |        |        |        |        |     | bit 15 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP29R<5:0>: RP29 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP29 (see Table 10-3 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP28R<5:0>: RP28 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP28 (see Table 10-3 for peripheral function numbers). |

#### REGISTER 10-37: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15

| U-0    | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> |

| bit 15 |     |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 |

| bit 7 | •   |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP31R<5:0>:** RP31 Output Pin Mapping bits<sup>(1)</sup><br/>Peripheral output number n is assigned to pin, RP31 (see Table 10-3 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP30R<5:0>:** RP30 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP30 (see Table 10-3 for peripheral function numbers).

Note 1: Unimplemented in 64-pin and 80-pin devices; read as '0'.

#### REGISTER 13-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0          | U-0                        | R/W-0                                                                                                    | R/W-0            | R/W-0             | R/W-0               | U-0                 | U-0                 |  |  |

|--------------|----------------------------|----------------------------------------------------------------------------------------------------------|------------------|-------------------|---------------------|---------------------|---------------------|--|--|

| —            | _                          | ICSIDL                                                                                                   | ICTSEL2          | ICTSEL1           | ICTSEL0             |                     | —                   |  |  |

| bit 15       |                            |                                                                                                          |                  |                   |                     |                     | bit 8               |  |  |

|              |                            |                                                                                                          |                  |                   |                     |                     |                     |  |  |

| U-0          | R/W-0                      | R/W-0                                                                                                    | R-0, HCS         | R-0, HCS          | R/W-0               | R/W-0               | R/W-0               |  |  |

|              | ICI1                       | ICI0                                                                                                     | ICOV             | ICBNE             | ICM2 <sup>(1)</sup> | ICM1 <sup>(1)</sup> | ICM0 <sup>(1)</sup> |  |  |

| bit 7        |                            |                                                                                                          |                  |                   |                     |                     | bit (               |  |  |

| Legend:      |                            | HCS = Hardv                                                                                              | vare Clearable/  | Settable bit      |                     |                     |                     |  |  |

| R = Readat   | ole bit                    | W = Writable                                                                                             | bit              | U = Unimplen      | nented bit, read    | d as '0'            |                     |  |  |

| -n = Value a | at POR                     | '1' = Bit is set                                                                                         | t                | '0' = Bit is clea |                     | x = Bit is unkr     | nown                |  |  |

|              |                            |                                                                                                          |                  |                   |                     |                     |                     |  |  |

| bit 15-14    | Unimpleme                  | nted: Read as '                                                                                          | 0'               |                   |                     |                     |                     |  |  |

| bit 13       | ICSIDL: Inpu               | it Capture x Mo                                                                                          | dule Stop in Idl | e Control bit     |                     |                     |                     |  |  |

|              |                            | oture module ha                                                                                          |                  |                   |                     |                     |                     |  |  |

|              |                            | oture module co                                                                                          | •                |                   | e mode              |                     |                     |  |  |

| bit 12-10    |                            | >: Input Captur                                                                                          |                  | DITS              |                     |                     |                     |  |  |

|              | 111 = Syste<br>110 = Reser | m clock (Fosc/:<br>wed                                                                                   | 2)               |                   |                     |                     |                     |  |  |

|              | 101 = Reser                |                                                                                                          |                  |                   |                     |                     |                     |  |  |

|              | 100 <b>= Time</b> r        | 1                                                                                                        |                  |                   |                     |                     |                     |  |  |

|              | 011 = Timer                | -                                                                                                        |                  |                   |                     |                     |                     |  |  |

|              | 010 = Timer<br>001 = Timer |                                                                                                          |                  |                   |                     |                     |                     |  |  |

|              | 000 = Timer                |                                                                                                          |                  |                   |                     |                     |                     |  |  |

| bit 9-7      | Unimpleme                  | nted: Read as '                                                                                          | 0'               |                   |                     |                     |                     |  |  |

| bit 6-5      | ICI<1:0>: Se               | elect Number of                                                                                          | Captures per li  | nterrupt bits     |                     |                     |                     |  |  |

|              |                            | ot on every four                                                                                         |                  | t                 |                     |                     |                     |  |  |

|              |                            | ot on every third                                                                                        |                  |                   |                     |                     |                     |  |  |

|              |                            | ot on every seco<br>ot on every capt                                                                     | •                | ent               |                     |                     |                     |  |  |

| bit 4        |                            | Capture x Over                                                                                           |                  | a hit (rood only  | <b>N</b>            |                     |                     |  |  |

| DIL 4        |                            | oture overflow c                                                                                         |                  | g bit (read-only  | )                   |                     |                     |  |  |

|              |                            | capture overflo                                                                                          |                  |                   |                     |                     |                     |  |  |

| bit 3        | -                          | t Capture x Buf                                                                                          |                  | is bit (read-only | <b>y</b> )          |                     |                     |  |  |

|              |                            | oture buffer is n                                                                                        |                  |                   |                     | n be read           |                     |  |  |

|              |                            | oture buffer is e                                                                                        |                  |                   |                     |                     |                     |  |  |

| bit 2-0      |                            | nput Capture M                                                                                           |                  |                   |                     |                     |                     |  |  |

|              |                            | 111 = Interrupt mode: Input capture functions as interrupt pin only when device is in Sleep or Idle mode |                  |                   |                     |                     |                     |  |  |

|              |                            | g edge detect o<br>ed (module disa                                                                       |                  | ntrol bits are no | ot applicable)      |                     |                     |  |  |

|              |                            | aler Capture m                                                                                           | ,                | n every 16th rig  | sina edae           |                     |                     |  |  |

|              |                            | aler Capture m                                                                                           |                  |                   |                     |                     |                     |  |  |

|              | 011 = Simpl                | le Capture mod                                                                                           | e: Capture on e  | every rising edg  | ge                  |                     |                     |  |  |

|              |                            | e Capture mod                                                                                            |                  |                   |                     |                     | 0. 1.1.             |  |  |

|              |                            | Detect Captur<br>ol interrupt gene                                                                       |                  |                   | ige (rising and     | falling), ICI<1:    | u> bits do no       |  |  |

|              |                            | capture module                                                                                           |                  |                   |                     |                     |                     |  |  |

|              | ooo mput                   | sapta o module                                                                                           |                  |                   |                     |                     |                     |  |  |

Note 1: The ICx input must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select".

## 17.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

## 17.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 17.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

## 17.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK to set up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG; this loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 17.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 17.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

## 17.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear to Send (UxCTS) and Request to Send (UxRTS) are the two hardware controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

## 17.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder. Note that because the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 17.7.1 IrDA CLOCK OUTPUT FOR EXTERNAL IrDA SUPPORT

To support external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UART module is enabled. It can be used to support the IrDA codec chip.

## 17.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

| R/W-0                     | U-0                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                       | R/W-0                                     | R/W-0            | R/W-0            | R/W-0          |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|------------------|----------------|

| PMPEN                     | _                                                                                                                                                                                                                                       | PSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADRMUX1                                                                                                                                                                                                                     | ADRMUX0                                   | PTBEEN           | PTWREN           | PTRDEN         |

| bit 15                    |                                                                                                                                                                                                                                         | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                             | •                                         |                  |                  | bit 8          |

|                           |                                                                                                                                                                                                                                         | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                        | R/W-0 <sup>(1)</sup>                      |                  |                  |                |

| R/W-0                     | R/W-0                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                           |                                           | R/W-0            | R/W-0            | R/W-0          |

| CSF1<br>bit 7             | CSF0                                                                                                                                                                                                                                    | ALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CS2P                                                                                                                                                                                                                        | CS1P                                      | BEP              | WRSP             | RDSP<br>bit 0  |