Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

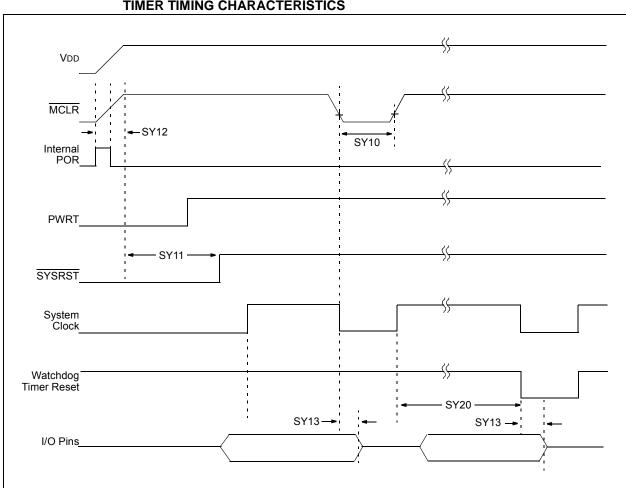

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga106-i-mr |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         |     |

| 5.0   | Flash Program Memory                                        | 57  |

| 6.0   | Resets                                                      | 65  |

| 7.0   | Interrupt Controller                                        | 71  |

| 8.0   | Oscillator Configuration                                    | 115 |

| 9.0   | Power-Saving Features                                       | 125 |

| 10.0  | I/O Ports                                                   | 127 |

| 11.0  | Timer1                                                      | 155 |

| 12.0  | Timer2/3 and Timer4/5                                       | 157 |

| 13.0  | Input Capture with Dedicated Timer                          |     |

| 14.0  | Output Compare with Dedicated Timer                         | 167 |

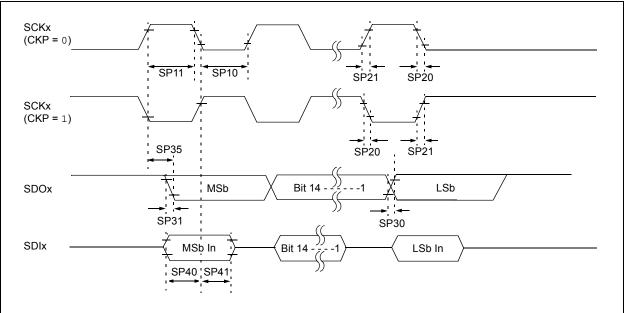

| 15.0  | Serial Peripheral Interface (SPI)                           | 175 |

| 16.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )   | 185 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)          |     |

| 18.0  | Parallel Master Port (PMP)                                  | 201 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 20.0  | Programmable Cyclic Redundancy Check (CRC) Generator        |     |

| 21.0  | 10-Bit High-Speed A/D Converter                             |     |

| 22.0  | Triple Comparator Module                                    |     |

| 23.0  | Comparator Voltage Reference                                | 239 |

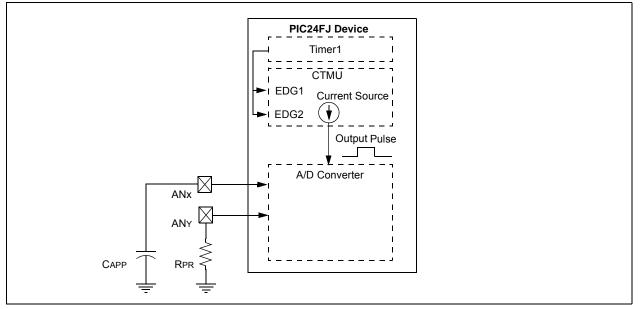

|       | Charge Time Measurement Unit (CTMU)                         |     |

| 25.0  | Special Features                                            | 245 |

| 26.0  | Instruction Set Summary                                     | 257 |

| 27.0  | Development Support                                         |     |

| 28.0  | Electrical Characteristics                                  | 269 |

| 29.0  | Packaging Information                                       | 305 |

| Appe  | ndix A: Revision History                                    | 319 |

| Index | <                                                           | 321 |

| The N | Vicrochip Web Site                                          | 327 |

| Custo | omer Change Notification Service                            | 327 |

| Custo | omer Support                                                | 327 |

| Read  | ler Response                                                | 328 |

| Produ | uct Identification System                                   | 329 |

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA106 PIC24FJ64GA110

- PIC24FJ128GA106 PIC24F

- PIC24FJ128GA110

PIC24FJ192GA110

- PIC24FJ192GA106PIC24FJ256GA106

- PIC24FJ256GA110

- PIC24FJ64GA108

- PIC24FJ128GA108

- PIC24FJ192GA108

- PIC24FJ256GA108

This family expands on the existing line of Microchip's 16-bit general purpose microcontrollers, combining enhanced computational performance with an expanded and highly configurable peripheral feature set. The PIC24FJ256GA110 family provides a new platform for high-performance applications, which have outgrown their 8-bit platforms, but don't require the power of a digital signal processor.

## 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- · Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FJ256GA110 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

• **On-the-Fly Clock Switching:** The device clock can be changed under software control to the Timer1 source or the internal, low-power RC Oscillator during operation, allowing the user to incorporate power-saving ideas into their software designs.

- **Doze Mode Operation:** When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: The microcontroller can suspend all operations, or selectively shut down its core while leaving its peripherals active, with a single instruction in software.

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ256GA110 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- A Fast Internal Oscillator (FRC) with a nominal 8 MHz output, which can also be divided under software control to provide clock speeds as low as 31 kHz.

- A Phase Lock Loop (PLL) frequency multiplier available to the external oscillator modes and the FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor. This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. The consistent pinout scheme used throughout the entire family also aids in migrating from one device to the next larger, or even in jumping from 64-pin to 100-pin devices.

The PIC24F family is pin-compatible with devices in the dsPIC33 and PIC32 families, and shares some compatibility with the pinout schema for PIC18 and dsPIC30 devices. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ256GA110 FAMILY: 80-PIN DEVICES

| Features                                                               | PIC24FJ64GA108                                                                                                                                      | PIC24FJ128GA108 | PIC24FJ192GA108 | PIC24FJ256GA108 |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--|--|--|

| Operating Frequency                                                    |                                                                                                                                                     | DC – 3          | 32 MHz          |                 |  |  |  |

| Program Memory (bytes)                                                 | 64K                                                                                                                                                 | 128K            | 192K            | 256K            |  |  |  |

| Program Memory (instructions)                                          | 22,016                                                                                                                                              | 44,032          | 67,072          | 87,552          |  |  |  |

| Data Memory (bytes)                                                    |                                                                                                                                                     | 16,             | 384             |                 |  |  |  |

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                                                                                                                                                     | 66 (            | 62/4)           |                 |  |  |  |

| I/O Ports                                                              |                                                                                                                                                     | Ports A, B,     | C, D, E, F, G   |                 |  |  |  |

| Total I/O Pins                                                         |                                                                                                                                                     | 6               | 9               |                 |  |  |  |

| Remappable Pins                                                        |                                                                                                                                                     | 42 (31 I/O, 1   | 11 input only)  |                 |  |  |  |

| Timers:<br>Total Number (16-bit)<br>32-Bit (from paired 16-bit timers) | 5(1)                                                                                                                                                |                 |                 |                 |  |  |  |

| Input Capture Channels                                                 |                                                                                                                                                     | 9               | (1)             |                 |  |  |  |

| Output Compare/PWM<br>Channels                                         |                                                                                                                                                     | 9               | (1)             |                 |  |  |  |

| Input Change Notification<br>Interrupt                                 |                                                                                                                                                     | 6               | 9               |                 |  |  |  |

| Serial Communications:                                                 |                                                                                                                                                     |                 |                 |                 |  |  |  |

| UART                                                                   | 4(1)                                                                                                                                                |                 |                 |                 |  |  |  |

| SPI (3-wire/4-wire)                                                    |                                                                                                                                                     | 3               | (1)             |                 |  |  |  |

| l <sup>2</sup> C™                                                      |                                                                                                                                                     |                 | 3               |                 |  |  |  |

| Parallel Communications<br>(PMP/PSP)                                   |                                                                                                                                                     | Y               | es              |                 |  |  |  |

| JTAG Boundary Scan                                                     |                                                                                                                                                     | Y               | es              |                 |  |  |  |

| 10-Bit Analog-to-Digital Module<br>(input channels)                    |                                                                                                                                                     | 1               | 6               |                 |  |  |  |

| Analog Comparators                                                     |                                                                                                                                                     |                 | 3               |                 |  |  |  |

| CTMU Interface                                                         |                                                                                                                                                     | Y               | es              |                 |  |  |  |

| Resets (and delays)                                                    | POR, BOR, RESET Instruction, MCLR, WDT; Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                 |                 |                 |  |  |  |

| Instruction Set                                                        | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                           |                 |                 |                 |  |  |  |

| Packages                                                               |                                                                                                                                                     | 80-Pir          | TQFP            |                 |  |  |  |

**Note 1:** Peripherals are accessible through remappable pins.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with  $PIC^{\circledast}$  devices and improve data space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address (EA) calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word which contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the data space is indirectly addressable. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

#### 4.2.4 SFR SPACE

The first 2 Kbytes of the near data space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where SFRs are actually implemented, is shown in Table 4-2. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is shown in Tables 4-3 through 4-29.

|      | SFR Space Address |          |          |                      |                |    |            |      |      |

|------|-------------------|----------|----------|----------------------|----------------|----|------------|------|------|

|      | xx00              | xx20     | xx40     | xx60                 | xx             | 80 | xxA0       | xxC0 | xxE0 |

| 000h |                   | Core     |          | ICN                  |                |    | Interrupts |      | _    |

| 100h | Tim               | ners     | (        | Capture              | apture Compare |    |            |      |      |

| 200h | l <sup>2</sup> C™ | UART     | SPI/UART | SPI/I <sup>2</sup> C | SPI            |    | UART I/    |      | 0    |

| 300h | A/D               | A/D/CTMU | _        | _                    | _              | _  | —          |      | _    |

| 400h | _                 | —        | _        | _                    | -              | _  |            |      | _    |

| 500h | -                 | —        | _        | _                    | _              | _  | —          | —    | _    |

| 600h | PMP               | RTC/Comp | CRC      | _                    |                |    | PPS        |      | —    |

| 700h | _                 | —        | System   | NVM/PMD              | _              | _  | —          | _    | —    |

TABLE 4-2:IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block

# TABLE 4-7: INPUT CAPTURE REGISTER MAP

| IADLE 4      |              |                                     |        | TOILE  | REGIS I |         |         |       |           |               |          |       |          |          |          |          |          |               |

|--------------|--------------|-------------------------------------|--------|--------|---------|---------|---------|-------|-----------|---------------|----------|-------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr         | Bit 15                              | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8     | Bit 7         | Bit 6    | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1 (    | 0140         | —                                   | _      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | -         | -             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2 0    | 0142         | —                                   |        | _      | —       | _       | —       | _     | IC32      | ICTRIG        | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF (     | 0144         | Input Capture 1 Buffer Register     |        |        |         |         |         |       |           |               |          |       | 0000     |          |          |          |          |               |

| IC1TMR 0     | 0146         |                                     |        |        |         |         |         |       | Timer     | Value 1 Re    | gister   |       |          |          |          |          |          | xxxx          |

| IC2CON1 0    | 0148         | —                                   | _      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     |           |               | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2 C    | 014A         | —                                   | —      | _      | —       | _       | —       | —     | IC32      | ICTRIG        | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF 0     | 014C         | Input Capture 2 Buffer Register     |        |        |         |         |         |       |           |               |          |       | 0000     |          |          |          |          |               |

| IC2TMR C     | 014E         |                                     |        |        |         |         |         |       | Timer     | Value 2 Re    | gister   |       |          |          |          | -        |          | xxxx          |

| IC3CON1 (    | 0150         | —                                   |        | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _         | _             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2 (    | 0152         | _                                   | —      | —      | —       | —       | —       | —     | IC32      | ICTRIG        | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF (     | 0154         |                                     |        |        |         |         |         |       | Input Cap | ture 3 Buffei | Register |       |          |          |          |          |          | 0000          |

| IC3TMR (     | 0156         |                                     |        |        |         |         |         |       | Timer     | Value 3 Re    | gister   |       |          |          |          |          |          | xxxx          |

| IC4CON1 (    | 0158         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _         | _             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2 C    | 015A         | —                                   | —      | —      | —       | _       | —       | _     | IC32      | ICTRIG        | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF 0     | 015C         |                                     |        |        |         |         |         |       | Input Cap | ture 4 Buffei | Register |       |          |          |          |          |          | 0000          |

| IC4TMR C     | 015E         |                                     |        |        |         |         |         |       | Timer     | Value 4 Re    | gister   |       |          |          |          |          |          | xxxx          |

| IC5CON1 (    | 0160         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —         | —             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC5CON2 (    | 0162         | —                                   | —      | —      | —       | —       | —       | —     | IC32      | ICTRIG        | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

|              | 0164         |                                     |        |        |         |         |         |       | Input Cap | ture 5 Buffei | Register |       |          |          |          |          |          | 0000          |

|              | 0166         |                                     |        |        |         |         | ,       |       | Timer     | Value 5 Re    | 5        |       |          |          | 1        |          |          | xxxx          |

| IC6CON1 (    | 0168         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —         | —             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC6CON2 C    | 016A         | —                                   | —      | —      | —       | —       | —       | —     | IC32      | ICTRIG        | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC6BUF 0     | 016C         |                                     |        |        |         |         |         |       | Input Cap | ture 6 Buffei | Register |       |          |          |          |          |          | 0000          |

| IC6TMR C     | 016E         | i                                   |        |        | ı       | -       |         |       | Timer     | Value 6 Re    | gister   |       |          |          | 1        |          |          | xxxx          |

| IC7CON1 (    | 0170         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —         | —             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC7CON2      | 0172         | _                                   |        | _      | —       | —       |         |       | IC32      | ICTRIG        | TRIGSTAT |       | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

|              | 0174         |                                     |        |        |         |         |         |       | Input Cap | ture 7 Buffei | Register |       |          |          |          |          |          | 0000          |

|              | 0176         |                                     |        |        |         |         |         |       | Timer     | Value 7 Re    |          |       |          |          | 1        |          |          | xxxx          |

| IC8CON1 (    | 0178         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —         | —             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

|              | 017A         | —                                   | —      | —      | —       | —       | —       | _     | IC32      | ICTRIG        | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC8BUF 0     | 017C         |                                     |        |        |         |         |         |       | Input Cap | ture 8 Buffei | Register |       |          |          |          |          |          | 0000          |

|              | 017E         |                                     |        |        | 1       |         |         |       | Timer     | Value 8 Re    |          |       |          | 1        | 1        | 1        |          | xxxx          |

|              | 0180         | —                                   | —      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | —         | —             | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC9CON2 (    | 0182         | —                                   | —      | —      | —       | —       | —       | —     | IC32      | ICTRIG        | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

|              |              | Input Capture 9 Buffer Register 000 |        |        |         |         |         |       |           |               | 0000     |       |          |          |          |          |          |               |

|              | 0184<br>0186 |                                     |        |        |         |         |         |       | input Cap | ture 9 Buffei | Register |       |          |          |          |          |          | 0000          |

PIC24FJ256GA110 FAMILY

Legend:

- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is as follows:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1 for an implementation in assembler):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-3 for the implementation in assembler).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat Steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPs, as shown in Example 5-5.

**Note:** The equivalent C code for these steps, prepared using Microchip's MPLAB C30 compiler and a specific library of built-in hardware functions, is shown in Examples 5-2, 5-4 and 5-6.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK (ASSEMBLY LANGUAGE CODE)

| ; Set up  | NVMCON | for block erase operation            |   |                                       |

|-----------|--------|--------------------------------------|---|---------------------------------------|

| M         | OV     | #0x4042, W0                          | ; |                                       |

| M         | OV     | W0, NVMCON                           | ; | Initialize NVMCON                     |

| ; Init po | ointer | to row to be ERASED                  |   |                                       |

| M         | OV     | <pre>#tblpage(PROG_ADDR), W0</pre>   | ; |                                       |

| M         | OV     | W0, TBLPAG                           | ; | Initialize PM Page Boundary SFR       |

| M         | OV     | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; | Initialize in-page EA[15:0] pointer   |

| TI        | BLWTL  | WO, [WO]                             | ; | Set base address of erase block       |

| D         | ISI    | #5                                   | ; | Block all interrupts with priority <7 |

|           |        |                                      | ; | for next 5 instructions               |

| M         | OV     | #0x55, W0                            |   |                                       |

| M         | OV     | W0, NVMKEY                           | ; | Write the 55 key                      |

| M         | OV     | #0xAA, W1                            | ; |                                       |

| M         | OV     | W1, NVMKEY                           | ; | Write the AA key                      |

| B         | SET    | NVMCON, #WR                          | ; | Start the erase sequence              |

| N         | OP     |                                      | ; | Insert two NOPs after the erase       |

| N         | OP     |                                      | ; | command is asserted                   |

|           |        |                                      |   |                                       |

## REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0                                   | R/W-1                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                   | U-0                                                 | R/W-1            | R/W-0           | R/W-0          |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|----------------|--|--|

| —                                     | T1IP2                                                                                                                                                                                       | T1IP1                                                                                                                                                                                                                                        | T1IP0                                                                                   |                                                     | OC1IP2           | OC1IP1          | OC1IP0         |  |  |

| bit 15                                |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 | bit 8          |  |  |

|                                       | <b>D</b> ////                                                                                                                                                                               | DAVA                                                                                                                                                                                                                                         | <b>D</b> /// 0                                                                          |                                                     | <b>D</b> 0.01 4  | DAALO           | <b>D</b> 444.0 |  |  |

| U-0                                   | R/W-1                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                   | U-0                                                 | R/W-1            | R/W-0           | R/W-0          |  |  |

| <br>bit 7                             | IC1IP2                                                                                                                                                                                      | IC1IP1                                                                                                                                                                                                                                       | IC1IP0                                                                                  | _                                                   | INT0IP2          | INT0IP1         | INT0IP0<br>bit |  |  |

|                                       |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 | DIL            |  |  |

| Legend:                               |                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |  |  |

| R = Readab                            | le bit                                                                                                                                                                                      | W = Writable I                                                                                                                                                                                                                               | oit                                                                                     | U = Unimplen                                        | nented bit, read | d as '0'        |                |  |  |

| -n = Value a                          | t POR                                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                             |                                                                                         | '0' = Bit is clea                                   | ared             | x = Bit is unkr | nown           |  |  |

| bit 15                                | Unimplemen                                                                                                                                                                                  | nted: Read as '0                                                                                                                                                                                                                             | )'                                                                                      |                                                     |                  |                 |                |  |  |

| bit 14-12                             | -                                                                                                                                                                                           | imer1 Interrupt                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |  |  |

|                                       |                                                                                                                                                                                             | ipt is priority 7 (h                                                                                                                                                                                                                         | 2                                                                                       | y interrupt)                                        |                  |                 |                |  |  |

|                                       | •                                                                                                                                                                                           |                                                                                                                                                                                                                                              | • • •                                                                                   |                                                     |                  |                 |                |  |  |

|                                       | •                                                                                                                                                                                           |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |  |  |

|                                       | 001 = Interru                                                                                                                                                                               | pt is priority 1                                                                                                                                                                                                                             |                                                                                         |                                                     |                  |                 |                |  |  |

|                                       |                                                                                                                                                                                             | pt source is disa                                                                                                                                                                                                                            | abled                                                                                   |                                                     |                  |                 |                |  |  |

|                                       | Unimplemented: Read as '0'                                                                                                                                                                  |                                                                                                                                                                                                                                              |                                                                                         |                                                     |                  |                 |                |  |  |

| bit 11                                | Unimplemer                                                                                                                                                                                  | nted: Read as 'o                                                                                                                                                                                                                             | )'                                                                                      |                                                     |                  |                 |                |  |  |

|                                       | -                                                                                                                                                                                           | nted: Read as '0<br>: Output Compa                                                                                                                                                                                                           |                                                                                         | Interrupt Priority                                  | y bits           |                 |                |  |  |

|                                       | OC1IP<2:0>                                                                                                                                                                                  |                                                                                                                                                                                                                                              | re Channel 1                                                                            |                                                     | y bits           |                 |                |  |  |

| bit 11<br>bit 10-8                    | OC1IP<2:0>                                                                                                                                                                                  | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                            |                                                     | y bits           |                 |                |  |  |

|                                       | OC1IP<2:0>                                                                                                                                                                                  | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                            |                                                     | y bits           |                 |                |  |  |

|                                       | OC1IP<2:0><br>111 = Interru<br>001 = Interru                                                                                                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1                                                                                                                                                                                    | re Channel 1<br>highest priorit                                                         |                                                     | y bits           |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru                                                                                                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                                                                                                                               | re Channel 1<br>highest priority<br>abled                                               |                                                     | y bits           |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru                                                                                                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br>nted: Read as '0                                                                                                                                           | re Channel 1<br>nighest priority<br>abled                                               | y interrupt)                                        |                  |                 |                |  |  |

|                                       | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br>nted: Read as '0                                                                                                                                           | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C<br>pt is priority 7 (h                                                                                          | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte                              | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h                                                                                          | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority          | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8<br>bit 7<br>bit 6-4          | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru                                               | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'c<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                 | re Channel 1<br>highest priority<br>abled<br>,<br>hannel 1 Inte<br>highest priority     | y interrupt)<br>rrupt Priority bits                 |                  |                 |                |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                      | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                      | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |  |  |

| bit 10-8                              | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0><br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemer<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemer<br>INT0IP<2:0><br>111 = Interru | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled | y interrupt)<br>rrupt Priority bits<br>y interrupt) |                  |                 |                |  |  |

### REGISTER 7-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0                                  | R/W-1                                                                                                                                                        | R/W-0                                                                                                                                                                                                                           | R/W-0                                                                                                                      | U-0                                                                         | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------------|--------|--|--|--|--|

|                                      | OC7IP2                                                                                                                                                       | OC7IP1                                                                                                                                                                                                                          | OC7IP0                                                                                                                     | —                                                                           | OC6IP2           | OC6IP1          | OC6IP0 |  |  |  |  |

| bit 15                               |                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 | bit 8  |  |  |  |  |

|                                      |                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

| U-0                                  | R/W-1                                                                                                                                                        | R/W-0                                                                                                                                                                                                                           | R/W-0                                                                                                                      | U-0                                                                         | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

|                                      | OC5IP2                                                                                                                                                       | OC5IP1                                                                                                                                                                                                                          | OC5IP0                                                                                                                     |                                                                             | IC6IP2           | IC6IP1          | IC6IP0 |  |  |  |  |

| bit 7                                |                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 | bit (  |  |  |  |  |

| Legend:                              |                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

| R = Readabl                          | le bit                                                                                                                                                       | W = Writable                                                                                                                                                                                                                    | bit                                                                                                                        | U = Unimplen                                                                | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at                        | t POR                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                                |                                                                                                                            | '0' = Bit is clea                                                           | ared             | x = Bit is unkr | nown   |  |  |  |  |

| bit 15                               | Unimplemen                                                                                                                                                   | ted: Read as '                                                                                                                                                                                                                  | 0'                                                                                                                         |                                                                             |                  |                 |        |  |  |  |  |

| bit 14-12                            | -                                                                                                                                                            |                                                                                                                                                                                                                                 |                                                                                                                            | Interrupt Priority                                                          | y bits           |                 |        |  |  |  |  |

|                                      |                                                                                                                                                              | pt is priority 7 (l                                                                                                                                                                                                             |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

|                                      | •                                                                                                                                                            |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

|                                      | •                                                                                                                                                            |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

|                                      | •<br>001 = Interrupt is priority 1                                                                                                                           |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

|                                      |                                                                                                                                                              | pt source is dis                                                                                                                                                                                                                | abled                                                                                                                      |                                                                             |                  |                 |        |  |  |  |  |

| bit 11                               | Unimplemen                                                                                                                                                   | ted: Read as '                                                                                                                                                                                                                  | 0'                                                                                                                         |                                                                             |                  |                 |        |  |  |  |  |

| h:+ 40 0                             | •                                                                                                                                                            |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             |                  |                 |        |  |  |  |  |

| 8-01 זונ                             | 0061P<2:0>:                                                                                                                                                  | Output Compa                                                                                                                                                                                                                    | are Channel 6                                                                                                              | Interrupt Priority                                                          | y bits           |                 |        |  |  |  |  |

| DIT 10-8                             |                                                                                                                                                              | Output Compa<br>pt is priority 7 (I                                                                                                                                                                                             |                                                                                                                            |                                                                             | y bits           |                 |        |  |  |  |  |

| 8-טר זוט                             |                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                            |                                                                             | y bits           |                 |        |  |  |  |  |