Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

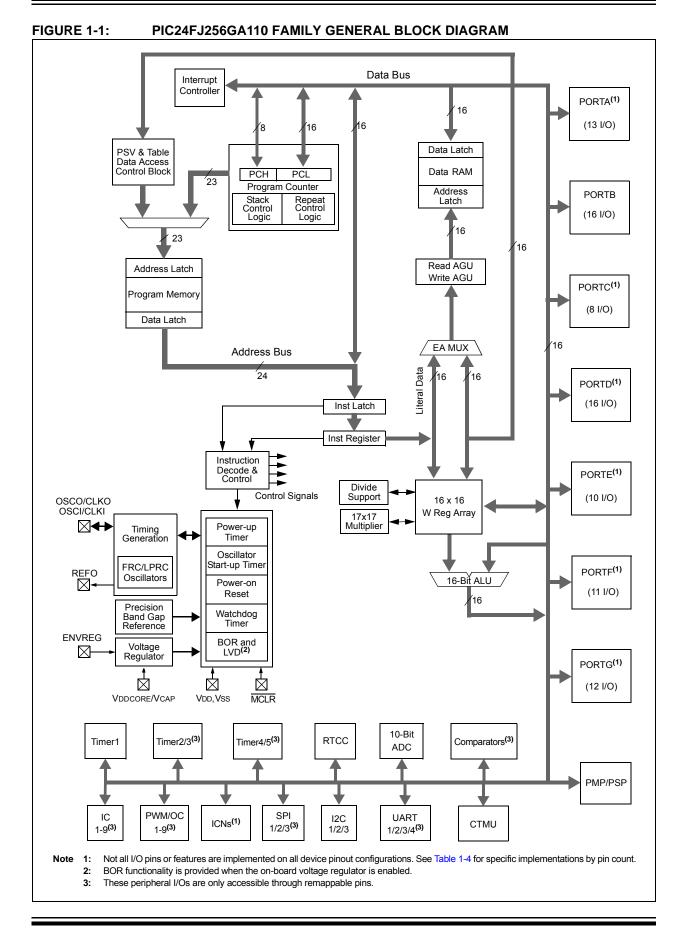

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga106t-i-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-670-8

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0 | U-0   |

|--------|-----|-----|-----|-------|-------|-----|-------|

| —      | —   | —   | —   | -     | —     | —   | —     |

| bit 15 |     |     |     |       |       |     | bit 8 |

|        |     |     |     |       |       |     |       |

| U-0    | U-0 | U-0 | U-0 | R/C-0 | R/W-0 | U-0 | U-0   |

| 00    | 00 | 00 | 00 | 1000                | 10000 | 00 | 00    |

|-------|----|----|----|---------------------|-------|----|-------|

| _     | —  |    |    | IPL3 <sup>(1)</sup> | PSV   |    | —     |

| bit 7 |    |    |    |                     |       |    | bit 0 |

|       |    |    |    |                     |       |    |       |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

- bit 3IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup>1 = CPU interrupt priority level is greater than 70 = CPU interrupt priority level is 7 or lessbit 2PSV: Program Space Visibility in Data Space Enable bit1 = Program space visible in data space0 = Program space not visible in data spacebit 1-0Unimplemented: Read as '0'

- **Note 1:** User interrupts are disabled when IPL3 = 1.

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

## 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

## 3.3.2 DIVIDER

The divide block supports signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

## TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

| TABLE 4-8: | OUTPUT COMPARE REGISTER MAP (CONTINUED) |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

|              |      |        |                                        |          |         |         | •       |       |       |             |          |        |          |          |          |          |          |               |

|--------------|------|--------|----------------------------------------|----------|---------|---------|---------|-------|-------|-------------|----------|--------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14                                 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8 | Bit 7       | Bit 6    | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC8CON1      | 01D6 | _      | —                                      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | -     | ENFLT0      | —        | _      | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC8CON2      | 01D8 | FLTMD  | FLTOUT                                 | FLTTRIEN | OCINV   | -       | —       | _     | OC32  | OCTRIG      | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC8RS        | 01DA |        | Output Compare 8 Secondary Register 00 |          |         |         |         |       |       |             |          | 0000   |          |          |          |          |          |               |

| OC8R         | 01DC |        | Output Compare 8 Register 0            |          |         |         |         |       |       |             |          | 0000   |          |          |          |          |          |               |

| OC8TMR       | 01DE |        |                                        |          |         |         |         |       | Timer | Value 8 Reg | gister   |        |          |          |          |          |          | xxxx          |

| OC9CON1      | 01E0 | _      | _                                      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | —     | ENFLT0      | —        | —      | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC9CON2      | 01E2 | FLTMD  | FLTOUT                                 | FLTTRIEN | OCINV   | -       | —       | _     | OC32  | OCTRIG      | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC9RS        | 01E4 |        | Output Compare 9 Secondary Register    |          |         |         |         |       |       |             | 0000     |        |          |          |          |          |          |               |

| OC9R         | 01E6 |        | Output Compare 9 Register 00           |          |         |         |         |       |       |             | 0000     |        |          |          |          |          |          |               |

| OC9TMR       | 01E8 |        | Timer Value 9 Register xx              |          |         |         |         |       |       |             | xxxx     |        |          |          |          |          |          |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### I<sup>2</sup>C<sup>~</sup> REGISTER MAP TABLE 4-9:

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                        | Bit 8                 | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|---------|--------|---------|--------|--------|--------|------------------------------|-----------------------|-------|-------|------------|-------------|------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200 | _       | —      | —       | —      | —      | _      | _                            |                       |       |       |            | Receive     | Register   |       |       |       | 0000          |

| I2C1TRN      | 0202 | _       | —      | _       | —      | —      | _      | —                            | —                     |       |       |            | Transmit    | Register   |       |       |       | OOFF          |

| I2C1BRG      | 0204 | _       | —      | —       | —      | —      | _      | —                            |                       |       |       | Baud Rat   | te Generato | r Register |       |       |       | 0000          |

| I2C1CON      | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN                  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208 | ACKSTAT | TRSTAT | _       | —      | _      | BCL    | GCSTAT                       | ADD10                 | IWCOL | I2COV | D/A        | Р           | S          | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A | _       | —      | —       | —      | —      | _      |                              |                       |       |       | Address    | Register    |            |       |       |       | 0000          |

| I2C1MSK      | 020C | _       | —      | —       | —      | —      | _      |                              | Address Mask Register |       |       |            |             |            | 0000  |       |       |               |

| I2C2RCV      | 0210 | _       | _      | _       | —      | —      | _      | _                            | Receive Register      |       |       |            |             | 0000       |       |       |       |               |

| I2C2TRN      | 0212 | _       | —      | _       | —      | —      | _      | —                            | Transmit Register     |       |       |            | 00FF        |            |       |       |       |               |

| I2C2BRG      | 0214 | _       | —      | —       | —      | —      | _      | Baud Rate Generator Register |                       |       |       |            |             | 0000       |       |       |       |               |

| I2C2CON      | 0216 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN                  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218 | ACKSTAT | TRSTAT | _       | -      | _      | BCL    | GCSTAT                       | ADD10                 | IWCOL | I2COV | D/A        | Р           | S          | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A | _       | —      | —       | —      | —      | _      |                              |                       |       |       | Address    | Register    |            |       |       |       | 0000          |

| I2C2MSK      | 021C | _       | —      | —       | —      | —      | _      |                              |                       |       |       | Address Ma | ask Registe | r          |       |       |       | 0000          |

| I2C3RCV      | 0270 | —       | —      | —       | —      | —      | _      | —                            | —                     |       |       |            | Receive     | Register   |       |       |       | 0000          |

| I2C3TRN      | 0272 | _       | —      | —       | —      | —      | _      | —                            | —                     |       |       |            | Transmit    | Register   |       |       |       | 00FF          |

| I2C3BRG      | 0274 | —       | _      | _       | -      | —      | —      | —                            |                       |       |       | Baud Rat   | te Generato | r Register |       |       |       | 0000          |

| I2C3CON      | 0276 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN                  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C3STAT     | 0278 | ACKSTAT | TRSTAT | _       | —      | _      | BCL    | GCSTAT                       | ADD10                 | IWCOL | I2COV | D/A        | Р           | S          | R/W   | RBF   | TBF   | 0000          |

| I2C3ADD      | 027A |         | —      | —       | —      | —      |        |                              |                       |       | •     | Address    | Register    | •          | •     | •     |       | 0000          |

| I2C3MSK      | 027C | _       | _      | _       | _      | _      | _      |                              |                       |       |       | Address Ma | ask Registe | r          |       |       |       | 0000          |

DS39905E-page 45

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                   | R/W-0 <sup>(1)</sup>                                                     | U-0                          | U-0                             | U-0                               | U-0                    | U-0                  |  |

|-----------------------|--------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|---------------------------------|-----------------------------------|------------------------|----------------------|--|

| WR                    | WREN                                                   | WRERR                                                                    | —                            | _                               |                                   |                        |                      |  |

| bit 15                |                                                        |                                                                          |                              |                                 |                                   |                        | bit                  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                   | U-0                                                                      | U-0                          | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> |  |

| _                     | ERASE                                                  | NVMOP2 <sup>(2)</sup>                                                    | NVMOP1 <sup>(2)</sup>        | NVMOP0(2                        |                                   |                        |                      |  |

| bit 7                 |                                                        |                                                                          |                              |                                 |                                   |                        | bit                  |  |

| Legend:               |                                                        | SO = Set Only                                                            | y bit                        |                                 |                                   |                        |                      |  |

| R = Readable          | e bit                                                  | W = Writable                                                             | bit                          | U = Unimplem                    | nented bit, read                  | l as '0'               |                      |  |

| -n = Value at         | POR                                                    | '1' = Bit is set                                                         |                              | '0' = Bit is clea               | ared                              | x = Bit is unkr        | iown                 |  |

| bit 15                | cleared b                                              | a Flash memor<br>by hardware one<br>or erase opera                       | ce the operation             | n is complete.                  | n. The operatio                   | n is self-timed        | and the bit          |  |

| bit 14                |                                                        | Enable bit <sup>(1)</sup><br>Iash program/e<br>ash program/er            |                              |                                 |                                   |                        |                      |  |

| bit 13                | 1 = An impre<br>automati                               | te Sequence Er<br>oper program<br>cally on any set<br>iram or erase o    | or erase seq                 | e WR bit)                       | t or terminatio                   | on has occurr          | ed (bit is so        |  |

| bit 12-7              | Unimplemen                                             | ted: Read as '                                                           | )'                           |                                 |                                   |                        |                      |  |

| bit 6                 | ERASE: Eras                                            | se/Program Ena                                                           | able bit <sup>(1)</sup>      |                                 |                                   |                        |                      |  |

|                       |                                                        | the erase opera<br>the program op                                        |                              |                                 |                                   |                        | nd                   |  |

| bit 5-4               | Unimplemen                                             | ted: Read as '                                                           | )'                           |                                 |                                   |                        |                      |  |

| bit 3-0               | NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> |                                                                          |                              |                                 |                                   |                        |                      |  |

|                       | 0011 = Memo<br>0010 = Memo                             | ory bulk erase o<br>ory word progra<br>ory page erase<br>ory row progran | m operation (E operation (ER | ERASE = 0) or<br>ASE = 1) or no | no operation (E<br>operation (ER/ | ERASE = 1)<br>ASE = 0) |                      |  |

| <b>2:</b> Al          | l other combina                                        | nly be reset on I<br>itions of NVMO                                      | P<3:0> are un                | •                               | ing specificatio                  | -                      |                      |  |

## REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

3: Available in ICSP<sup>™</sup> mode only. Refer to the device programming specification.

| R/W-0                       | R-0                                                                                                                 | U-0                                                                                                                                                                                                      | U-0                                                                   | U-0               | U-0             | U-0             | U-0    |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------|-----------------|-----------------|--------|--|--|

| ALTIVT                      | DISI                                                                                                                | _                                                                                                                                                                                                        | —                                                                     | —                 | _               | _               | _      |  |  |

| bit 15                      |                                                                                                                     | •<br>•                                                                                                                                                                                                   | ·                                                                     |                   |                 |                 | bit 8  |  |  |

| U-0                         | U-0                                                                                                                 | U-0                                                                                                                                                                                                      | R/W-0                                                                 | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |

| _                           |                                                                                                                     | _                                                                                                                                                                                                        | INT4EP                                                                | INT3EP            | INT2EP          | INT1EP          | INTOEP |  |  |

| bit 7                       |                                                                                                                     |                                                                                                                                                                                                          |                                                                       |                   |                 |                 | bit (  |  |  |

| Legend:                     |                                                                                                                     |                                                                                                                                                                                                          |                                                                       |                   |                 |                 |        |  |  |

| R = Readab                  | le bit                                                                                                              | W = Writable                                                                                                                                                                                             | bit                                                                   | U = Unimplem      | ented bit, read | d as '0'        |        |  |  |

| -n = Value at               | t POR                                                                                                               | '1' = Bit is se                                                                                                                                                                                          | t                                                                     | '0' = Bit is clea | ared            | x = Bit is unkr | iown   |  |  |

| bit 14<br>bit 13-5<br>bit 4 | 0 = Use stand<br>DISI: DISI In<br>1 = DISI inst<br>0 = DISI inst<br>Unimplement<br>INT4EP: Exte<br>1 = Interrupt of |                                                                                                                                                                                                          | vector table<br>is bit<br>e<br>active<br>10'<br>4 Edge Detect F<br>ge | Polarity Select b | it              |                 |        |  |  |

| bit 3                       | 1 = Interrupt c                                                                                                     |                                                                                                                                                                                                          | ge                                                                    | Polarity Select b | vit             |                 |        |  |  |

| bit 2                       | 1 = Interrupt o                                                                                                     | rnal Interrupt 2<br>on negative ed<br>on positive edg                                                                                                                                                    | ge                                                                    | Polarity Select b | vit             |                 |        |  |  |

| bit 1                       | 1 = Interrupt c                                                                                                     | on negative ed                                                                                                                                                                                           | ge                                                                    | Polarity Select b | vit             |                 |        |  |  |

| bit 0                       | 1 = Interrupt c                                                                                                     | <ul> <li>0 = Interrupt on positive edge</li> <li>INTOEP: External Interrupt 0 Edge Detect Polarity Select bit</li> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |                                                                       |                   |                 |                 |        |  |  |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 10.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ256GA110 family of devices implements a total of 37 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (21)

- Output Remappable Peripheral Registers (16)

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.4.1 "Control Register Lock" for a specific command sequence.

## REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                               | U-0 | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  |  |  |

|-----------------------------------|-----|------------------|--------|-----------------------------------------|--------|--------|--------|--|--|

|                                   | _   | INT1R5           | INT1R4 | INT1R3                                  | INT1R2 | INT1R1 | INT1R0 |  |  |

| bit 15                            |     |                  |        |                                         |        |        | bit 8  |  |  |

|                                   |     |                  |        |                                         |        |        |        |  |  |

| U-0                               | U-0 | U-0              | U-0    | U-0                                     | U-0    | U-0    | U-0    |  |  |

| —                                 | —   | —                | —      | —                                       | —      | —      | —      |  |  |

| bit 7                             |     |                  |        |                                         |        |        | bit 0  |  |  |

|                                   |     |                  |        |                                         |        |        |        |  |  |

| Legend:                           |     |                  |        |                                         |        |        |        |  |  |

| R = Readable bit W = Writable bit |     |                  |        | U = Unimplemented bit, read as '0'      |        |        |        |  |  |

| -n = Value at I                   | POR | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |        |        |  |  |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 13-8 INT1R<5:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      |     | INT3R5 | INT3R4 | INT3R3 | INT3R2 | INT3R1 | INT3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits |

## REGISTER 10-13: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U1CTSR5 | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U1CTSR<5:0:> Assign UART1 Clear to Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U1RXR<5:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

## REGISTER 10-14: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U2CTSR<5:0>: Assign UART2 Clear to Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 U2RXR<5:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

## REGISTER 10-34: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| _       | —   | RP25R5 | RP25R4 | RP25R3 | RP25R2 | RP25R1 | RP25R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|         | _   | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 |

| bit 7   |     |        | •      |        | •      |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

| Legena.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8

RP25R<5:0>: RP25 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP25 (see Table 10-3 for peripheral function numbers).

bit 7-6

Unimplemented: Read as '0'

- bit 5-0 **RP24R<5:0>:** RP24 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP24 (see Table 10-3 for peripheral function numbers).

## REGISTER 10-35: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP27R5 | RP27R4 | RP27R3 | RP27R2 | RP27R1 | RP27R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP27R<5:0>:** RP27 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP27 (see Table 10-3 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP26R<5:0>:** RP26 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP26 (see Table 10-3 for peripheral function numbers).

## 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 14. "Timers" (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two independent 16-bit timers with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- Single 32-bit synchronous counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- · Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- ADC Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC event trigger; this is implemented only with Timer3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON      |

|-------|--------------------------------------------|

|       | control bits are ignored. Only T2CON and   |

|       | T4CON control bits are used for setup and  |

|       | control. Timer2 and Timer4 clock and gate  |

|       | inputs are utilized for the 32-bit timer   |

|       | modules, but an interrupt is generated     |

|       | with the Timer3 or Timer5 interrupt flags. |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair: TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

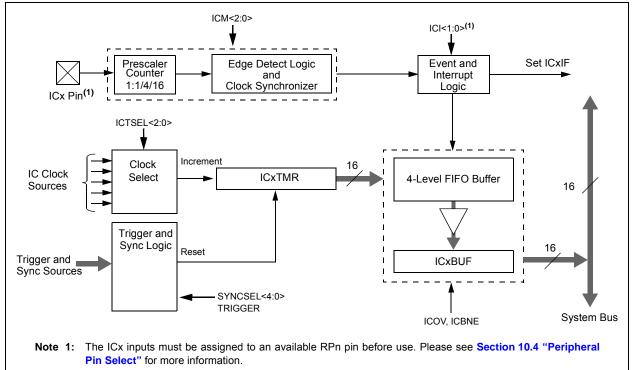

## 13.0 INPUT CAPTURE WITH DEDICATED TIMER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 34. *"Input Capture with* Dedicated Timer" (DS39722)

Devices in the PIC24FJ256GA110 family all feature 9 independent enhanced input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the enhanced output module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 30 user-selectable trigger/sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 13-1) and ICxCON2 (Register 13-2). A general block diagram of the module is shown in Figure 13-1.

## 13.1 General Operating Modes

#### 13.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the enhanced input capture module operates in a free-running mode. The internal 16-bit counter ICxTMR counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSEL bits to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSEL bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSEL bits determine the sync/trigger source.

When the SYNCSEL bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

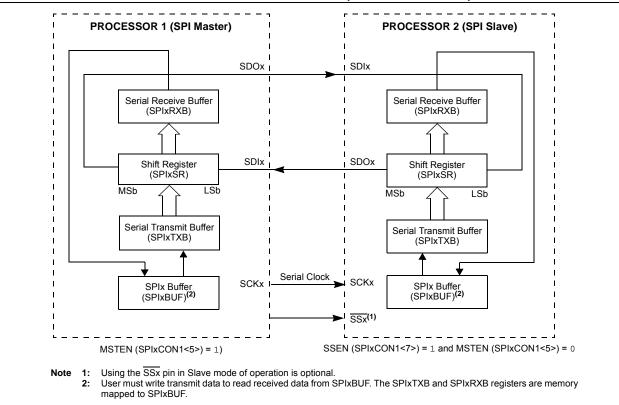

## FIGURE 15-3: SPI MASTER/SLAVE CONNECTION (STANDARD MODE)

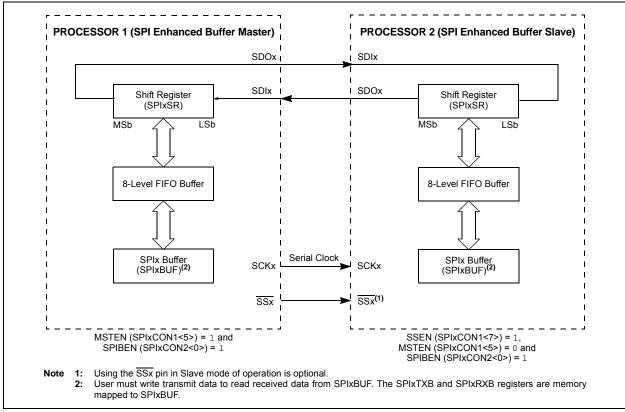

## FIGURE 15-4: SPI MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

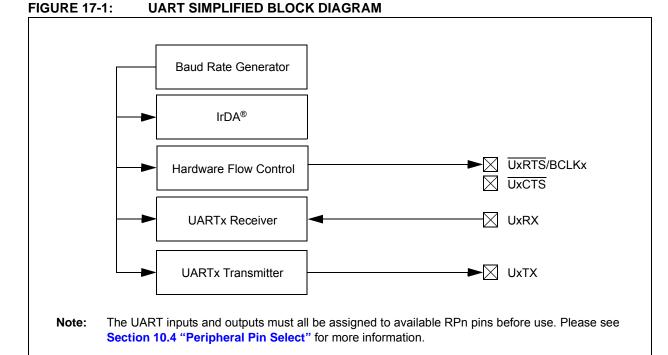

## 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |

|       | "PIC24F Family Reference Manual",          |  |  |  |  |  |  |

|       | Section 21. "UART" (DS39708).              |  |  |  |  |  |  |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- · IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 17-1. The UART module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

## REGISTER 21-2: AD1CON2: A/D CONTROL REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | r-0 | U-0 | R/W-0 | U-0 | U-0   |

|--------|-------|-------|-----|-----|-------|-----|-------|

| VCFG2  | VCFG1 | VCFG0 | r   | —   | CSCNA | —   | —     |

| bit 15 |       |       |     |     |       |     | bit 8 |

| R-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| BUFS  | —   | SMPI3 | SMPI2 | SMPI1 | SMPI0 | BUFM  | ALTS  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13

VCFG<2:0>: Voltage Reference Configuration bits

| VCFG<2:0> | VR+                | VR-                |

|-----------|--------------------|--------------------|

| 000       | AVDD               | AVss               |

| 001       | External VREF+ pin | AVss               |

| 010       | AVDD               | External VREF- pin |

| 011       | External VREF+ pin | External VREF- pin |

| lxx       | AVDD               | AVss               |

- bit 12 Reserved: Maintain as '0'

- bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Scan Input Selections for S/H Positive Input for MUX A Input Multiplexer Setting bit 1 = Scan inputs 0 = Do not scan inputs

- bit 9-8 Unimplemented: Read as '0'

- bit 7 **BUFS:** Buffer Fill Status bit (valid only when BUFM = 1)

- 1 = A/D is currently filling buffer 08-0F, user should access data in 00-07

- 0 = A/D is currently filling buffer 00-07, user should access data in 08-0F

- bit 6 Unimplemented: Read as '0'

- bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each 16th sample/convert sequence

- 1110 = Interrupts at the completion of conversion for each 15th sample/convert sequence

- 0001 = Interrupts at the completion of conversion for each 2nd sample/convert sequence

0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers (ADC1BUFn<15:8> and ADC1BUFn<7:0>)

- 0 = Buffer configured as one 16-word buffer (ADC1BUFn<15:0>)

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses MUX A input multiplexer settings for first sample, then alternates between MUX B and MUX A input multiplexer settings for all subsequent samples

- 0 = Always uses MUX A input multiplexer settings

| R/W-0                                   | U-0                                                                                            | U-0                                                                                                                                                          | R/W-0                                                                                                                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| CH0NB                                   | _                                                                                              |                                                                                                                                                              | CH0SB4 <sup>(1)</sup>                                                                                                | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup> | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |

| oit 15                                  |                                                                                                | ÷                                                                                                                                                            |                                                                                                                      |                       |                       |                       | bit 8                 |  |  |  |

|                                         | U-0                                                                                            | U-0                                                                                                                                                          |                                                                                                                      |                       |                       |                       | R/W-0                 |  |  |  |

| R/W-0<br>CH0NA                          | 0-0                                                                                            | 0-0                                                                                                                                                          | R/W-0<br>CH0SA4                                                                                                      | R/W-0<br>CH0SA3       | R/W-0<br>CH0SA2       | R/W-0<br>CH0SA1       | CH0SA0                |  |  |  |

| bit 7                                   |                                                                                                | _                                                                                                                                                            | CH05A4                                                                                                               | CHUSAS                | CHUSAZ                | CHUSAT                | bit                   |  |  |  |

|                                         |                                                                                                |                                                                                                                                                              |                                                                                                                      |                       |                       |                       | bit                   |  |  |  |

| Legend:                                 |                                                                                                |                                                                                                                                                              |                                                                                                                      |                       |                       |                       |                       |  |  |  |

| R = Readab                              | le bit                                                                                         | W = Writable                                                                                                                                                 | e bit                                                                                                                | U = Unimplem          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value a                            | t POR                                                                                          | '1' = Bit is se                                                                                                                                              | t                                                                                                                    | '0' = Bit is clea     | ared                  | x = Bit is unkn       | iown                  |  |  |  |

| bit 15                                  | CH0NB: Ch                                                                                      | annel 0 Negativ                                                                                                                                              | ve Input Select fo                                                                                                   | or MUX B Multi        | plexer Setting        | bit                   |                       |  |  |  |

|                                         | 1 = Channel                                                                                    | 0 negative inp<br>0 negative inp                                                                                                                             | ut is AN1                                                                                                            |                       |                       |                       |                       |  |  |  |

| bit 14-13                               |                                                                                                | nted: Read as                                                                                                                                                |                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 12-8                                | •                                                                                              |                                                                                                                                                              |                                                                                                                      | lect for MUX B        | Multiplexer Set       | ting hits(1)          |                       |  |  |  |

| 511 12 0                                |                                                                                                | CH0SB<4:0>: Channel 0 Positive Input Select for MUX B Multiplexer Setting bits <sup>(1)</sup>                                                                |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                |                                                                                                                                                              | e input is VBG/2                                                                                                     | i bana gap reie       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         | 01001 <b>= Ch</b>                                                                              | annel 0 positive                                                                                                                                             | e input is AN9                                                                                                       |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                |                                                                                                                                                              | 00101 = Channel 0 positive input is AN5                                                                              |                       |                       |                       |                       |  |  |  |

| 00101 = Channel 0 positive input is AN4 |                                                                                                |                                                                                                                                                              |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         | 00100 = Channel 0 positive input is AN4<br>00011 = Channel 0 positive input is AN3             |                                                                                                                                                              |                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                                         |                                                                                                | annel 0 positive                                                                                                                                             | e input is AN3                                                                                                       |                       |                       |                       |                       |  |  |  |

|                                         | 00010 <b>= Ch</b>                                                                              | annel 0 positive<br>annel 0 positive                                                                                                                         | e input is AN3<br>e input is AN2                                                                                     |                       |                       |                       |                       |  |  |  |

|                                         | 00010 = Ch<br>00001 = Ch                                                                       | annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                                     | e input is AN3<br>e input is AN2<br>e input is AN1                                                                   |                       |                       |                       |                       |  |  |  |

| bit 7                                   | 00010 = Ch<br>00001 = Ch<br>00000 = Ch                                                         | annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                 | e input is AN3<br>e input is AN2<br>e input is AN1<br>e input is AN0                                                 | or MUX A Multi        | plexer Setting        | bit                   |                       |  |  |  |

| bit 7                                   | 00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>CH0NA: Ch                                            | annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 Negative                                                             | e input is AN3<br>e input is AN2<br>e input is AN1<br>e input is AN0<br>ve Input Select fo                           | or MUX A Multi        | plexer Setting        | bit                   |                       |  |  |  |

| bit 7                                   | 00010 = Ch<br>00001 = Ch<br>00000 = Ch<br><b>CH0NA:</b> Ch<br>1 = Channel                      | annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                 | e input is AN3<br>e input is AN2<br>e input is AN1<br>e input is AN0<br>ve Input Select fo<br>ut is AN1              | or MUX A Multi        | plexer Setting        | bit                   |                       |  |  |  |

| bit 7<br>bit 6-5                        | 00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>CH0NA: Ch<br>1 = Channel<br>0 = Channel              | annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 Negative<br>0 negative input                                         | e input is AN3<br>e input is AN2<br>e input is AN1<br>e input is AN0<br>ve Input Select fo<br>ut is AN1<br>ut is VR- | or MUX A Multi        | plexer Setting        | bit                   |                       |  |  |  |

|                                         | 00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>CH0NA: Ch<br>1 = Channel<br>0 = Channel<br>Unimpleme | annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 Negative<br>0 negative inp<br>0 negative inp<br><b>nted:</b> Read as | e input is AN3<br>e input is AN2<br>e input is AN1<br>e input is AN0<br>ve Input Select fo<br>ut is AN1<br>ut is VR- |                       |                       |                       |                       |  |  |  |

## REGISTER 21-4: AD1CHS: A/D INPUT SELECT REGISTER

Note 1: Combinations, '10010' through '11111', are unimplemented; do not use.

| R = Readable                                         | POR                                                   | CTMUSIDL<br>R/W-0<br>EDG2SEL0<br>W = Writable I<br>'1' = Bit is set | TGEN<br>R/W-0<br>EDG1POL | EDGEN<br>R/W-0<br>EDG1SEL1<br>U = Unimplen<br>'0' = Bit is clea | EDGSEQEN<br>R/W-0<br>EDG1SEL0 | IDISSEN<br>R/W-0<br>EDG2STAT | CTTRIG<br>bit 8<br>R/W-0<br>EDG1STAT<br>bit 0 |

|------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------|-------------------------------|------------------------------|-----------------------------------------------|

| R/W-0<br>EDG2POL<br>bit 7<br>Legend:<br>R = Readable | EDG2SEL1<br>bit<br>POR<br>CTMUEN: CT<br>1 = Module is | EDG2SEL0<br>W = Writable H<br>'1' = Bit is set                      | EDG1POL                  | EDG1SEL1                                                        | EDG1SEL0                      | EDG2STAT                     | R/W-0<br>EDG1STAT                             |

| EDG2POL<br>bit 7<br>Legend:<br>R = Readable          | EDG2SEL1<br>bit<br>POR<br>CTMUEN: CT<br>1 = Module is | EDG2SEL0<br>W = Writable H<br>'1' = Bit is set                      | EDG1POL                  | EDG1SEL1                                                        | EDG1SEL0                      | EDG2STAT                     | EDG1STAT                                      |