Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | <u>.</u>                                                                       |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

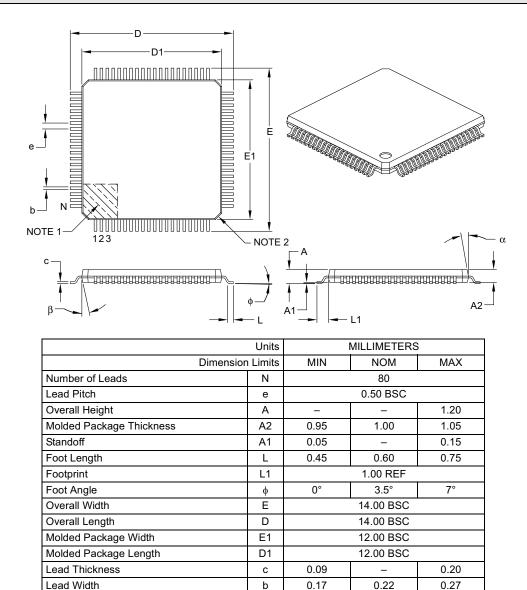

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga108-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-670-8

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 64/80/100-Pin, 16-Bit, General Purpose Flash Microcontrollers with Peripheral Pin Select

#### **Power Management:**

- On-Chip 2.5V Voltage Regulator

- · Switch between Clock Sources in Real Time

- Idle, Sleep and Doze modes with Fast Wake-up and Two-Speed Start-up

- Run mode: 1 mA/MIPS, 2.0V Typical

- Standby Current with 32 kHz Oscillator: 2.6 μA, 2.0V Typical

#### **High-Performance CPU:**

- Modified Harvard Architecture

- Up to 16 MIPS Operation at 32 MHz

- 8 MHz Internal Oscillator

- 17-Bit x 17-Bit Single-Cycle Hardware Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture with Flexible Addressing modes

- Linear Program Memory Addressing, Up to 12 Mbytes

- Linear Data Memory Addressing, Up to 64 Kbytes

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

#### **Analog Features:**

- 10-Bit, Up to 16-Channel Analog-to-Digital (A/D) Converter at 500 ksps:

- Conversions available in Sleep mode

- Three Analog Comparators with Programmable Input/ Output Configuration

- Charge Time Measurement Unit (CTMU)

#### **Peripheral Features:**

- Peripheral Pin Select:

- Allows independent I/O mapping of many peripherals at run time

- Continuous hardware integrity checking and safety interlocks prevent unintentional configuration changes

Up to 46 available pins (100-pin devices)

- Three 3-Wire/4-Wire SPI modules (supports 4 Frame modes) with 8-Level FIFO Buffer

- Three I<sup>2</sup>C<sup>™</sup> modules support Multi-Master/Slave modes and 7-Bit/10-Bit Addressing

- Four UART modules:

- Supports RS-485, RS-232, LIN/J2602 protocols and IrDA  $^{\ensuremath{\mathbb{R}}}$

- On-chip hardware encoder/decoder for IrDA

- Auto-wake-up and Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Five 16-Bit Timers/Counters with Programmable Prescaler

- Nine 16-Bit Capture Inputs, each with a Dedicated Time Base

- Nine 16-Bit Compare/PWM Outputs, each with a Dedicated Time Base

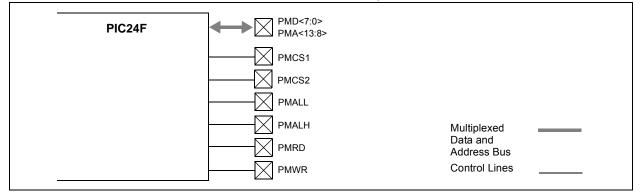

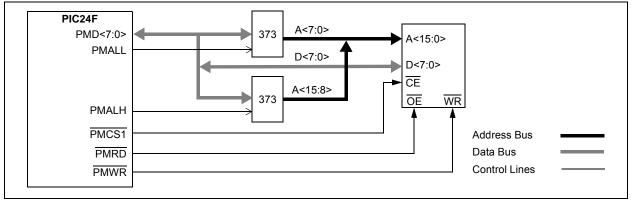

- 8-Bit Parallel Master Port (PMP/PSP):

- Up to 16 address pins

- Programmable polarity on control lines

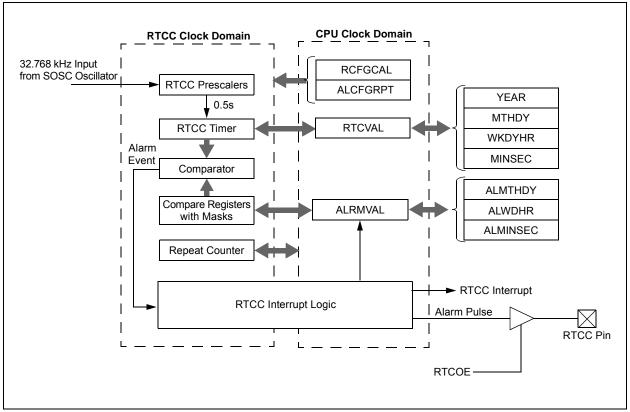

- Hardware Real-Time Clock/Calendar (RTCC):

Provides clock, calendar and alarm functions

- Programmable Cyclic Redundancy Check (CRC) Generator

- Up to 5 External Interrupt Sources

|                   |      | s)                        | ()           |                    | Rema          | ppable        | e Periph               | erals                     |     |      | (1              |             |         |      |      |

|-------------------|------|---------------------------|--------------|--------------------|---------------|---------------|------------------------|---------------------------|-----|------|-----------------|-------------|---------|------|------|

| PIC24FJ<br>Device | Pins | Program<br>Memory (Bytes) | SRAM (Bytes) | Remappable<br>Pins | Timers 16-Bit | Capture Input | Compare/<br>PWM Output | UART w/ IrDA <sup>®</sup> | SPI | I²C™ | 10-Bit A/D (ch) | Comparators | PMP/PSP | JTAG | CTMU |

| 64GA106           | 64   | 64K                       | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 128GA106          | 64   | 128K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 192GA106          | 64   | 192K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 256GA106          | 64   | 256K                      | 16K          | 31                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 64GA108           | 80   | 64K                       | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 128GA108          | 80   | 128K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 192GA108          | 80   | 192K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 256GA108          | 80   | 256K                      | 16K          | 42                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 64GA110           | 100  | 64K                       | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Υ    | Y    |

| 128GA110          | 100  | 128K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 192GA110          | 100  | 192K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| 256GA110          | 100  | 256K                      | 16K          | 46                 | 5             | 9             | 9                      | 4                         | 3   | 3    | 16              | 3           | Y       | Y    | Y    |

| TABLE 1-3: D | DEVICE FEATURES FOR THE PIC24FJ256GA110 FAMILY: 100-PIN DEVICES |

|--------------|-----------------------------------------------------------------|

|--------------|-----------------------------------------------------------------|

| Features                                            | PIC24FJ64GA110 | PIC24FJ128GA110                                               | PIC24FJ192GA110      | PIC24FJ256GA110 |

|-----------------------------------------------------|----------------|---------------------------------------------------------------|----------------------|-----------------|

| Operating Frequency                                 |                | DC – 3                                                        | 32 MHz               | •               |

| Program Memory (bytes)                              | 64K            | 128K                                                          | 192K                 | 256K            |

| Program Memory (instructions)                       | 22,016         | 44,032                                                        | 67,072               | 87,552          |

| Data Memory (bytes)                                 |                | 16,                                                           | 384                  |                 |

| Interrupt Sources<br>(soft vectors/NMI traps)       |                | 66 (                                                          | 62/4)                |                 |

| I/O Ports                                           |                | Ports A, B,                                                   | C, D, E, F, G        |                 |

| Total I/O Pins                                      |                | 8                                                             | 35                   |                 |

| Remappable Pins                                     |                | 46 (32 I/O, 1                                                 | 14 input only)       |                 |

| Timers:                                             |                |                                                               |                      |                 |

| Total Number (16-bit)                               |                | 5                                                             | (1)                  |                 |

| 32-Bit (from paired 16-bit timers)                  |                |                                                               | 2                    |                 |

| Input Capture Channels                              |                | 9                                                             | (1)                  |                 |

| Output Compare/PWM<br>Channels                      |                | 9                                                             | (1)                  |                 |

| Input Change Notification<br>Interrupt              |                | 8                                                             | 35                   |                 |

| Serial Communications:                              |                |                                                               |                      |                 |

| UART                                                |                | 4                                                             | (1)                  |                 |

| SPI (3-wire/4-wire)                                 |                | 3                                                             | (1)                  |                 |

| I <sup>2</sup> C™                                   |                |                                                               | 3                    |                 |

| Parallel Communications<br>(PMP/PSP)                |                | Y                                                             | es                   |                 |

| JTAG Boundary Scan                                  |                | Y                                                             | es                   |                 |

| 10-Bit Analog-to-Digital Module<br>(input channels) |                | 1                                                             | 6                    |                 |

| Analog Comparators                                  |                | :                                                             | 3                    |                 |

| CTMU Interface                                      |                | Y                                                             | es                   |                 |

| Resets (and delays)                                 |                | OR, RESET Instructior<br>struction, Hardware Tra<br>(PWRT, OS |                      |                 |

| Instruction Set                                     | 76 Bas         | e Instructions, Multiple                                      | e Addressing Mode Va | ariations       |

| Packages                                            |                | 100-Pi                                                        | n TQFP               |                 |

**Note 1:** Peripherals are accessible through remappable pins.

#### TABLE 4-6: TIMER REGISTER MAP

| DS39905E-pag |  |

|--------------|--|

| e 42         |  |

|              |  |

| File Name | Addr | Bit 15                 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8         | Bit 7        | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|------------------------|--------|--------|--------|--------|--------|-------------|---------------|--------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1      | 0100 |                        |        |        |        |        |        |             | Timer1        | Register     |              |        |        |       |       |       |       | 0000          |

| PR1       | 0102 |                        |        |        |        |        |        |             | Timer1 Peri   | iod Register | r            |        |        |       |       |       |       | FFFF          |

| T1CON     | 0104 | TON                    | —      | TSIDL  | _      | _      | _      | —           | _             | _            | TGATE        | TCKPS1 | TCKPS0 |       | TSYNC | TCS   |       | 0000          |

| TMR2      | 0106 |                        |        |        |        |        |        |             | Timer2        | Register     |              |        |        |       |       |       |       | 0000          |

| TMR3HLD   | 0108 |                        |        |        |        |        | Timer  | 3 Holding F | Register (for | 32-bit time  | r operations | only)  |        |       |       |       |       | 0000          |

| TMR3      | 010A |                        |        |        |        |        |        |             | Timer3        | Register     |              |        |        |       |       |       |       | 0000          |

| PR2       | 010C |                        |        |        |        |        |        |             | Timer2 Peri   | iod Register | r            |        |        |       |       |       |       | FFFF          |

| PR3       | 010E |                        |        |        |        |        |        |             | Timer3 Peri   | iod Register | r            |        |        |       |       |       |       | FFFF          |

| T2CON     | 0110 | TON                    | _      | TSIDL  | _      | _      | _      | _           | _             | _            | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON     | 0112 | TON                    | _      | TSIDL  | _      | _      | _      | _           | _             | _            | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4      | 0114 |                        |        |        |        |        |        |             | Timer4        | Register     |              |        |        |       |       |       |       | 0000          |

| TMR5HLD   | 0116 |                        |        |        |        |        | Tim    | ner5 Holdin | g Register (  | for 32-bit o | perations or | nly)   |        |       |       |       |       | 0000          |

| TMR5      | 0118 |                        |        |        |        |        |        |             | Timer5        | Register     |              |        |        |       |       |       |       | 0000          |

| PR4       | 011A |                        |        |        |        |        |        |             | Timer4 Peri   | iod Register | r            |        |        |       |       |       |       | FFFF          |

| PR5       | 011C | Timer5 Period Register |        |        |        |        |        |             | FFFF          |              |              |        |        |       |       |       |       |               |

| T4CON     | 011E | TON                    | _      | TSIDL  | —      | —      | —      | _           | _             | _            | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T5CON     | 0120 | TON                    |        | TSIDL  | _      | _      | _      | _           | _             |              | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>REGISTER 7-19:</b> IPC2: INTERRUPT PRIORITY CONTROL REGISTER |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| U-0          | R/W-1                                                      | R/W-0                                                                                                         | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|-----------------|---------|--|--|--|--|--|

|              | U1RXIP2                                                    | U1RXIP1                                                                                                       | U1RXIP0           |                  | SPI1IP2         | SPI1IP1         | SPI1IP0 |  |  |  |  |  |

| pit 15       |                                                            |                                                                                                               |                   |                  |                 |                 | bit     |  |  |  |  |  |

|              |                                                            |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                                                                         | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

| —            | SPF1IP2                                                    | SPF1IP1                                                                                                       | SPF1IP0           | —                | T3IP2           | T3IP1           | T3IP0   |  |  |  |  |  |

| bit 7        |                                                            |                                                                                                               |                   |                  |                 |                 | bit     |  |  |  |  |  |

|              |                                                            |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

| Legend:      |                                                            |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

| R = Readab   | ole bit                                                    | W = Writable                                                                                                  | bit               | U = Unimple      | mented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value a | It POR                                                     | '1' = Bit is set                                                                                              |                   | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |  |

| L:1 4 F      | Unimalanaa                                                 | tad: Daad as (                                                                                                | o'                |                  |                 |                 |         |  |  |  |  |  |

| bit 15       | -                                                          | ted: Read as '                                                                                                |                   | Driarity bita    |                 |                 |         |  |  |  |  |  |

| bit 14-12    |                                                            | : UART1 Rece<br>pt is priority 7 (I                                                                           | =                 | -                |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               | ingricor priority |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          | •<br>001 = Interrupt is priority 1                                                                            |                   |                  |                 |                 |         |  |  |  |  |  |

|              |                                                            | pt is priority 1<br>pt source is dis                                                                          | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 11       |                                                            | ted: Read as '                                                                                                |                   |                  |                 |                 |         |  |  |  |  |  |

| bit 10-8     | -                                                          |                                                                                                               |                   | hits             |                 |                 |         |  |  |  |  |  |

|              |                                                            | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          | p                                                                                                             |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •<br>001 = Interru                                         | nt is priority 1                                                                                              |                   |                  |                 |                 |         |  |  |  |  |  |

|              |                                                            | pt is priority i<br>pt source is dis                                                                          | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 7        |                                                            | ted: Read as '                                                                                                |                   |                  |                 |                 |         |  |  |  |  |  |

| bit 6-4      | -                                                          | SPI1 Fault In                                                                                                 |                   | bits             |                 |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               | /                 | • /              |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                         |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              |                                                            | pt source is dis                                                                                              | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 3        | Unimplemen                                                 | ted: Read as '                                                                                                | o'                |                  |                 |                 |         |  |  |  |  |  |

| bit 2-0      | T3IP<2:0>: ⊺                                               | imer3 Interrupt                                                                                               | Priority bits     |                  |                 |                 |         |  |  |  |  |  |

|              | 111 = Interru                                              | pt is priority 7 (I                                                                                           | highest priority  | interrupt)       |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                                               |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •<br>001 = Interru                                         | pt is priority 1                                                                                              |                   |                  |                 |                 |         |  |  |  |  |  |

#### REGISTER 7-38: IPC23: INTERRUPT PRIORITY CONTROL REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|-----|--------|--------|--------|

| —     | IC9IP2 | IC9IP1 | IC9IP0 | —   | OC9IP2 | OC9IP1 | OC9IP0 |

| bit 7 |        |        |        |     |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7<br>bit 6-4 | Unimplemented: Read as '0'<br>IC9IP<2:0>: Input Capture Channel 9 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                     |

| bit 3               | Unimplemented: Read as '0'                                                                                                                              |

| bit 2-0             | <pre>OC9IP&lt;2:0&gt;: Output Compare Channel 9 Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)</pre>                |

### 8.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FJ256GA110 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 8-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the Primary Oscillator modes (EC, HS or XT); otherwise, if the POSCEN bit is also not set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

#### REGISTER 10-26: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0           | U-0           | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

|---------------|---------------|------------------|----------------|-------------------|------------------|-----------------|---------------|

| _             | —             | RP9R5            | RP9R4          | RP9R3             | RP9R2            | RP9R1           | RP9R0         |

| bit 15        |               |                  |                |                   |                  |                 | bit 8         |

|               |               |                  |                |                   |                  |                 |               |

| U-0           | U-0           | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| —             | —             | RP8R5            | RP8R4          | RP8R3             | RP8R2            | RP8R1           | RP8R0         |

| bit 7         |               |                  |                |                   |                  |                 | bit 0         |

|               |               |                  |                |                   |                  |                 |               |

| Legend:       |               |                  |                |                   |                  |                 |               |

| R = Readabl   | e bit         | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |               |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unki | nown          |

|               |               |                  |                |                   |                  |                 |               |

| bit 15-14     | Unimplemen    | ted: Read as '   | o'             |                   |                  |                 |               |

| bit 13-8      | RP9R<5:0>:    | RP9 Output Pir   | n Mapping bits | ;                 |                  |                 |               |

|               | Peripheral ou | tput number n i  | is assigned to | pin, RP9 (see 1   | Table 10-3 for p | eripheral funct | ion numbers). |

| h# 7 0        |               | (ad. Deed as (   | ~!             |                   |                  |                 |               |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP8R<5:0>:** RP8 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP8 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-27: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP11 (see Table 10-3 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP10R<5:0>: RP10 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP10 (see Table 10-3 for peripheral function numbers).

| REGISTER 10-32: | RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 |

|-----------------|--------------------------------------------------|

|-----------------|--------------------------------------------------|

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8

RP21R<5:0>: RP21 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP21 (see Table 10-3 for peripheral function numbers).

bit 7-6

Unimplemented: Read as '0'

bit 5.0

RP22P = 5:0

- bit 5-0 **RP20R<5:0:>** RP20 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP20 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-33: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP23R5 | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP23R<5:0>:** RP23 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP23 (see Table 10-3 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP22R<5:0>:** RP22 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP22 (see Table 10-3 for peripheral function numbers).

### 16.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 16-1.

#### EQUATION 16-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1,2)</sup>

$$FSCL = \frac{FCY}{I2CxBRG + 1 + \frac{FCY}{10,000,000}}$$

or

$$I2CxBRG = \left(\frac{FCY}{FSCL} - \frac{FCY}{10,000,000}\right) - 1$$

Note 1: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

### TABLE 16-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1,2)</sup>

### 16.4 Slave Address Masking

The I2CxMSK register (Register 16-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00010000', the slave module will detect both addresses: '0000000' and '0010000'.

To enable address masking, the IPMI (Intelligent Peripheral Management Interface) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 16-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required System | Fcy    | I2CxBI    | RG Value      | Actual    |

|-----------------|--------|-----------|---------------|-----------|

| FSCL            | FCY    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz         | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz         | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz         | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz         | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz         | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz         | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz         | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz           | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz           | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz           | 4 MHz  | 3         | 3             | 0.909 MHz |

Note 1: Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

TABLE 16-2: I<sup>2</sup>C<sup>™</sup> RESERVED ADDRESSES<sup>(1)</sup>

| Slave Address | R/W Bit | Description                            |  |  |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|--|--|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |  |  |  |  |  |

| 0000 000      | 1       | Start Byte                             |  |  |  |  |  |

| 0000 001      | х       | Cbus Address                           |  |  |  |  |  |

| 0000 010      | х       | Reserved                               |  |  |  |  |  |

| 0000 011      | х       | Reserved                               |  |  |  |  |  |

| 0000 1xx      | x       | HS Mode Master Code                    |  |  |  |  |  |

| 1111 1xx      | х       | Reserved                               |  |  |  |  |  |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |  |  |

Note 1: The address bits listed here will never cause an address match, independent of address mask settings.

- 2: The address will be Acknowledged only if GCEN = 1.

- 3: Match on this address can only occur on the upper byte in 10-Bit Addressing mode.

| R/W-0         | U-0                                              | R/W-0                                  | R/W-1, HC                            | R/W-0                         | R/W-0                     | R/W-0             | R/W-0         |  |

|---------------|--------------------------------------------------|----------------------------------------|--------------------------------------|-------------------------------|---------------------------|-------------------|---------------|--|

| I2CEN         | _                                                | I2CSIDL                                | SCLREL                               | IPMIEN                        | A10M                      | DISSLW            | SMEN          |  |

| bit 15        |                                                  |                                        |                                      |                               |                           |                   | bit           |  |

| R/W-0         | R/W-0                                            | R/W-0                                  | R/W-0, HC                            | R/W-0, HC                     | R/W-0, HC                 | R/W-0, HC         | R/W-0, HC     |  |

| GCEN          | STREN                                            | ACKDT                                  | ACKEN                                | RCEN                          | PEN                       | RSEN              | SEN           |  |

| bit 7         |                                                  |                                        |                                      |                               |                           |                   | bit           |  |

| Legend:       |                                                  | HC = Hardwa                            | are Clearable bit                    | t                             |                           |                   |               |  |

| R = Readabl   | e bit                                            | W = Writable                           | bit                                  | U = Unimpler                  | nented bit, read          | l as '0'          |               |  |

| -n = Value at | POR                                              | '1' = Bit is set                       | t                                    | '0' = Bit is clea             |                           | x = Bit is unkr   | iown          |  |

| bit 15        | <b>12CEN:</b> 12Cx                               | Enable bit                             |                                      |                               |                           |                   |               |  |

|               |                                                  |                                        | le and configure                     | s the SDAx an                 | d SCLx pins as            | s serial port pin | s             |  |

|               |                                                  |                                        | All I <sup>2</sup> C pins are o      |                               |                           |                   |               |  |

| bit 14        | Unimplemer                                       | nted: Read as '                        | 0'                                   |                               |                           |                   |               |  |

| bit 13        |                                                  | op in Idle Mode                        |                                      |                               |                           |                   |               |  |

|               |                                                  |                                        | eration when de<br>ation in Idle mod |                               | Idle mode                 |                   |               |  |

| bit 12        | SCLREL: SC                                       | CLx Release Co                         | ontrol bit (when                     | operating as I <sup>2</sup>   | C Slave)                  |                   |               |  |

|               | 1 = Releases                                     |                                        |                                      |                               |                           |                   |               |  |

|               |                                                  | = Holds SCLx clock low (clock stretch) |                                      |                               |                           |                   |               |  |

|               | $\frac{\text{If STREN} = 1}{\text{Bit is } R/W}$ |                                        | y write '0' to ini                   | tiate stretch an              | d write '1' to re         | lease clock) H    | lardware cle  |  |

|               |                                                  |                                        | nission. Hardwa                      |                               |                           |                   |               |  |

|               | <u>If STREN = c</u>                              |                                        |                                      |                               |                           |                   |               |  |

|               | Bit is R/S (i.e transmission.                    |                                        | ay only write '1                     | ' to release cl               | ock). Hardware            | e clear at begi   | nning of slav |  |

| bit 11        |                                                  |                                        | al Management                        | t Interface (IPM              | 11) Enable bit            |                   |               |  |

|               |                                                  | port mode is e                         | nabled; all addr                     |                               |                           |                   |               |  |

| bit 10        |                                                  | t Slave Address                        | sina hit                             |                               |                           |                   |               |  |

|               |                                                  | ) is a 10-bit slav                     | -                                    |                               |                           |                   |               |  |

|               |                                                  | is a 7-bit slave                       |                                      |                               |                           |                   |               |  |

| bit 9         | DISSLW: Dis                                      | able Slew Rate                         | e Control bit                        |                               |                           |                   |               |  |

|               |                                                  | control disable                        |                                      |                               |                           |                   |               |  |

|               |                                                  | control enable                         |                                      |                               |                           |                   |               |  |

| bit 8         |                                                  | us Input Levels                        |                                      | ith SMPula ana                | oification                |                   |               |  |

|               |                                                  | SMBus input th                         | lds compliant wi<br>hresholds        | iti Sivibus sper              | Cilication                |                   |               |  |

| bit 7         | GCEN: Gene                                       | eral Call Enable                       | bit (when operation                  | ating as I <sup>2</sup> C sla | ave)                      |                   |               |  |

|               |                                                  |                                        | a general call a                     | ddress is receiv              | ved in the I2Cx           | RSR               |               |  |

|               |                                                  | s enabled for r                        | • •                                  |                               |                           |                   |               |  |

|               |                                                  | call address dis                       | auleu                                |                               |                           |                   |               |  |

| bit 6         | STREN: SOL                                       | v Clock Strata                         | n Enable bit (wb                     | en operating a                | e 12C elava               |                   |               |  |

| bit 6         |                                                  | x Clock Stretch                        | n Enable bit (wh<br>SCI RFL bit      | en operating a                | s I <sup>2</sup> C slave) |                   |               |  |

| R/W-0                 | U-0                                                                                                                      | R/W-0                                | R/W-0               | R/W-0             | U-0              | R/W-0              | R/W-0           |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------|-------------------|------------------|--------------------|-----------------|--|--|

| UARTEN <sup>(1)</sup> |                                                                                                                          | USIDL                                | IREN <sup>(2)</sup> | RTSMD             |                  | UEN1               | UEN0            |  |  |

| bit 15                |                                                                                                                          |                                      |                     |                   |                  |                    | bit 8           |  |  |

|                       |                                                                                                                          |                                      |                     |                   |                  |                    |                 |  |  |

| R/C-0, HC             | R/W-0                                                                                                                    | R/W-0, HC                            | R/W-0               | R/W-0             | R/W-0            | R/W-0              | R/W-0           |  |  |

| WAKE                  | LPBACK                                                                                                                   | ABAUD                                | RXINV               | BRGH              | PDSEL1           | PDSEL0             | STSEL           |  |  |

| bit 7                 |                                                                                                                          |                                      |                     |                   |                  |                    | bit 0           |  |  |

|                       |                                                                                                                          |                                      |                     |                   |                  |                    |                 |  |  |

| Legend:               |                                                                                                                          | C = Clearable                        |                     |                   | re Clearable bi  |                    |                 |  |  |

| R = Readable          |                                                                                                                          | W = Writable I                       | oit                 |                   | nented bit, read |                    |                 |  |  |

| -n = Value at         | POR                                                                                                                      | '1' = Bit is set                     |                     | '0' = Bit is clea | ared             | x = Bit is unkn    | iown            |  |  |

| bit 15                |                                                                                                                          | ARTx Enable bit                      | (1)                 |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | s enabled; all U                     |                     | controlled by L   | JARTx as defin   | ed by UEN<1:0      | )>              |  |  |

|                       |                                                                                                                          | s disabled; all L                    |                     |                   |                  |                    |                 |  |  |

|                       | minimal                                                                                                                  |                                      |                     |                   |                  |                    |                 |  |  |

| bit 14                | Unimplemen                                                                                                               | ted: Read as '0                      | )'                  |                   |                  |                    |                 |  |  |

| bit 13                | •                                                                                                                        | in Idle Mode bit                     |                     |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | nue module ope<br>e module operat    |                     |                   | s Idle mode      |                    |                 |  |  |

| bit 12                |                                                                                                                          | Encoder and De                       |                     |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | oder and decod                       |                     |                   |                  |                    |                 |  |  |

|                       | 0 = IrDA encoder and decoder disabled                                                                                    |                                      |                     |                   |                  |                    |                 |  |  |

| bit 11                | RTSMD: Mod                                                                                                               | de Selection for                     | UxRTS Pin bi        | t                 |                  |                    |                 |  |  |

|                       |                                                                                                                          | oin in Simplex m<br>oin in Flow Cont |                     |                   |                  |                    |                 |  |  |

| bit 10                | Unimplemen                                                                                                               | ted: Read as 'o                      | )'                  |                   |                  |                    |                 |  |  |

| bit 9-8               | UEN<1:0>: L                                                                                                              | JARTx Enable b                       | its                 |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | UxRX and BCL                         |                     |                   |                  | ontrolled by po    | rt latches      |  |  |

|                       |                                                                                                                          | UxRX, UxCTS                          |                     |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | UxRX and UxR<br>and UxRX pins        |                     |                   |                  |                    |                 |  |  |

|                       | latches                                                                                                                  | •                                    |                     |                   |                  |                    |                 |  |  |

| bit 7                 | WAKE: Wake                                                                                                               | e-up on Start Bit                    | Detect During       | g Sleep Mode E    | nable bit        |                    |                 |  |  |

|                       |                                                                                                                          | vill continue to s                   |                     | RX pin; interrup  | t generated on   | i falling edge, bi | it cleared in   |  |  |

|                       |                                                                                                                          | e on following ris                   | sing edge           |                   |                  |                    |                 |  |  |

| hit 6                 | 0 = No wake                                                                                                              | •                                    | Mada Salaat I       | ait               |                  |                    |                 |  |  |

| bit 6                 |                                                                                                                          | ARTx Loopback                        | wode Select         | JIL               |                  |                    |                 |  |  |

|                       |                                                                                                                          | k mode is disab                      | led                 |                   |                  |                    |                 |  |  |

| bit 5                 | -                                                                                                                        | o-Baud Enable                        |                     |                   |                  |                    |                 |  |  |

|                       |                                                                                                                          | aud rate measu                       |                     | e next characte   | er – requires re | ception of a Sy    | nc field (55h); |  |  |

|                       |                                                                                                                          | n hardware upo<br>e measurement      |                     | ompleted          |                  |                    |                 |  |  |

|                       |                                                                                                                          | he peripheral in                     |                     |                   | nfigured to an a | available RPn pi   | in. See         |  |  |

|                       | ction 10.4 "Peripheral Pin Select" for more information.<br>s feature is only available for the 16x BRG mode (BRGH = 0). |                                      |                     |                   |                  |                    |                 |  |  |

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER

| R/W-0                     | U-0                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                       | R/W-0                                     | R/W-0            | R/W-0            | R/W-0          |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|------------------|----------------|--|--|--|