Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 69                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga108t-i-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- Communications: The PIC24FJ256GA110 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C<sup>™</sup> modules that support both Master and Slave modes of operation. Devices also have, through the Peripheral Pin Select (PPS) feature, four independent UARTs with built-in IrDA<sup>®</sup> encoder/decoders and three SPI modules.

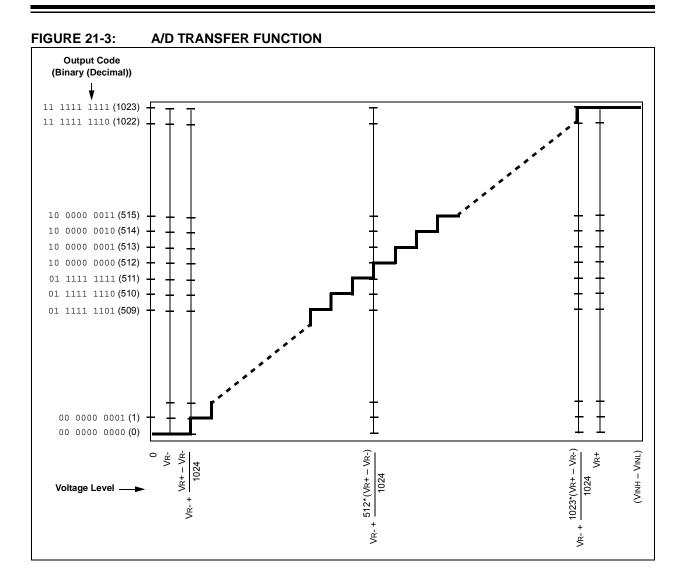

- Analog Features: All members of the PIC24FJ256GA110 family include a 10-bit A/D Converter module and a triple comparator module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256GA110 family include the brand new CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- **Parallel Master Port:** One of the general purpose I/O ports can be reconfigured for enhanced parallel data communications. In this mode, the port can be configured for both master and slave operations, and supports 8-bit transfers with up to 16 external address lines in Master modes.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up the timer resources and program memory space for the use of the core application.

## 1.3 Details on Individual Family Members

Devices in the PIC24FJ256GA110 family are available in 64-pin, 80-pin and 100-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four ways:

- Flash program memory (64 Kbytes for PIC24FJ64GA1 devices, 128 Kbytes for PIC24FJ128GA1 devices, 192 Kbytes for PIC24FJ192GA1 devices and 256 Kbytes for PIC24FJ256GA1 devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices, 69 pins on 7 ports for 80-pin devices and 85 pins on 7 ports for 100-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (same as the number of available I/O pins for all devices).

- 4. Available remappable pins (31 pins on 64-pin devices, 42 pins on 80-pin devices and 46 pins on 100-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1.

A list of the pin features available on the PIC24FJ256GA110 family devices, sorted by function, is shown in Table 1-4. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

### TABLE 4-27: SYSTEM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON         | 0740 | TRAPR  | IOPUWR | —      | _      |        | —      | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON       | 0742 | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | —     | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV       | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | —       | —      | —      |       | —     | _      | _      | —     | 0100          |

| OSCTUN       | 0748 | —      | —      | —      | -      | —      | —      | —      | —      | —       | —      | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON      | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 |         | -      | —      | _     | -     | _      | _      | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-28: NVM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|--------|--------|--------|---------------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  |        | _      |        | _     | _     |       | ERASE |       |       | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY       | 0766 | -      | —      | _      |        | _      | _      | _     | _     |       |       |       | NVMK  | EY<7:0> |        |        |        | 0000                |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-29: PMD REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | -      | —      | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      |        | ADC1MD | 0000          |

| PMD2         | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0774 | _      | —      | _      | —      | —      | CMPMD  | RTCCMD | PMPMD | CRCMD  | —     | —     | —      | U3MD   | I2C3MD | I2C2MD | —      | 0000          |

| PMD4         | 0776 | _      | _      | _      | _      | —      | —      | _      | _     | _      | _     | U4MD  | _      | REFOMD | CTMUMD | LVDMD  | _      | 0000          |

| PMD5         | 0778 | _      | —      | —      | —      | —      | —      | —      | IC9MD | —      | —     | —     | —      | —      | —      | _      | OC9MD  | 0000          |

| PMD6         | 077A | _      | —      | _      | -      | -      | -      | _      | —     | -      |       | _     | _      | _      | _      | _      | SPI3MD | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

## REGISTER 7-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 1 | <b>MI2C1IE:</b> Master I2C1 Event Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <b>SI2C1IE:</b> Slave I2C1 Event Interrupt Enable bit 1 = Interrupt request enabled                                          |

|       | 0 = Interrupt request not enabled                                                                                            |

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. See **Section 10.4 "Peripheral Pin Select"** for more information.

## REGISTER 7-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0           | U-0           | R/W-0                                                      | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|---------------|------------------------------------------------------------|------------------|-------------------|------------------|-----------------|--------|

| _             | —             | PMPIE                                                      | OC8IE            | OC7IE             | OC6IE            | OC5IE           | IC6IE  |

| bit 15        |               |                                                            |                  | •                 |                  |                 | bit 8  |

| R/W-0         | R/W-0         | R/W-0                                                      | U-0              | U-0               | U-0              | R/W-0           | R/W-0  |

| IC5IE         | IC4IE         | IC3IE                                                      | 0-0              | 0-0               | 0-0              | SPI2IE          | SPF2IE |

| bit 7         | IC4IE         | ICJIE                                                      |                  |                   | _                | JF121L          | bit (  |

|               |               |                                                            |                  |                   |                  |                 |        |

| Legend:       |               |                                                            |                  |                   |                  |                 |        |

| R = Readable  |               | W = Writable                                               | bit              | •                 | nented bit, read | d as '0'        |        |

| -n = Value at | POR           | '1' = Bit is set                                           |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 15-14     | Unimpleme     | ented: Read as '                                           | )'               |                   |                  |                 |        |

| bit 13        | PMPIE: Par    | allel Master Port                                          | Interrupt Enal   | ole bit           |                  |                 |        |

|               |               | t request enabled<br>t request not ena                     |                  |                   |                  |                 |        |

| bit 12        | OC8IE: Out    | put Compare Ch                                             | annel 8 Interru  | upt Enable bit    |                  |                 |        |

|               |               | t request enabled                                          |                  |                   |                  |                 |        |

|               | 0 = Interrup  | t request not ena                                          | bled             |                   |                  |                 |        |

| bit 11        | -             | put Compare Ch                                             |                  | upt Enable bit    |                  |                 |        |

|               |               | t request enabled<br>t request not ena                     |                  |                   |                  |                 |        |

| bit 10        | OC6IE: Out    | put Compare Ch                                             | annel 6 Interru  | upt Enable bit    |                  |                 |        |

|               |               | t request enabled<br>t request not ena                     |                  |                   |                  |                 |        |

| bit 9         | OC5IE: Out    | put Compare Ch                                             | annel 5 Interru  | upt Enable bit    |                  |                 |        |

|               | •             | t request enabled<br>t request not ena                     |                  |                   |                  |                 |        |

| bit 8         | IC6IE: Input  | Capture Channe                                             | el 6 Interrupt E | nable bit         |                  |                 |        |

|               |               | t request enable<br>t request not ena                      |                  |                   |                  |                 |        |

| bit 7         | IC5IE: Input  | Capture Channe                                             | el 5 Interrupt E | nable bit         |                  |                 |        |

|               |               | t request enabled<br>t request not ena                     |                  |                   |                  |                 |        |

| bit 6         | IC4IE: Input  | Capture Channe                                             | el 4 Interrupt E | nable bit         |                  |                 |        |

|               |               | t request enable<br>t request not ena                      |                  |                   |                  |                 |        |

| bit 5         | -             | Capture Channe                                             |                  | nable bit         |                  |                 |        |

|               | 1 = Interrupt | t request enable                                           | ł                |                   |                  |                 |        |

|               | 0 = Interrupt | t request not ena                                          | bled             |                   |                  |                 |        |

| bit 4-2       | Unimpleme     | nted: Read as '                                            | )'               |                   |                  |                 |        |

| bit 1         |               | 2 Event Interrup                                           |                  |                   |                  |                 |        |

|               |               | t request enable                                           |                  |                   |                  |                 |        |

|               |               |                                                            |                  |                   |                  |                 |        |

| -:+ O         | -             | t request not ena                                          |                  |                   |                  |                 |        |

| bit 0         | SPF2IE: SP    | t request not ena<br>l2 Fault Interrup<br>t request enable | Enable bit       |                   |                  |                 |        |

| REGISTER                        | 7-18: IPC1:                                                                            | INTERRUPT                                                                            | PRIORITY                    |                                    | EGISTER 1        |                 |        |

|---------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|------------------------------------|------------------|-----------------|--------|

| U-0                             | R/W-1                                                                                  | R/W-0                                                                                | R/W-0                       | U-0                                | R/W-1            | R/W-0           | R/W-0  |

| —                               | T2IP2                                                                                  | T2IP1                                                                                | T2IP0                       | —                                  | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15                          |                                                                                        |                                                                                      |                             |                                    |                  |                 | bit    |

| U-0                             | R/W-1                                                                                  | R/W-0                                                                                | R/W-0                       | U-0                                | U-0              | U-0             | U-0    |

| _                               | IC2IP2                                                                                 | IC2IP1                                                                               | IC2IP0                      | —                                  | _                |                 | _      |

| bit 7                           |                                                                                        |                                                                                      |                             |                                    |                  |                 | bit    |

| Legend:                         |                                                                                        |                                                                                      |                             |                                    |                  |                 |        |

| R = Readabl                     | le bit                                                                                 | W = Writable                                                                         | bit                         | U = Unimpler                       | nented bit, read | 1 as '0'        |        |

| -n = Value at                   | t POR                                                                                  | '1' = Bit is set                                                                     |                             | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown   |

| bit 14-12<br>bit 11<br>bit 10-8 | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC2IP<2:0>: | pt source is dis<br><b>ited:</b> Read as '(<br>: Output Compa<br>pt is priority 7 (I | abled<br>o'<br>re Channel 2 | Interrupt Priorit                  | y bits           |                 |        |

| bit 7<br>bit 6-4                | Unimplemen<br>IC2IP<2:0>:                                                              | pt is priority 7 (I                                                                  | )'<br>Channel 2 Inte        | rrupt Priority bit<br>/ interrupt) | 5                |                 |        |

| bit 3-0                         |                                                                                        | pt source is dis<br>nted: Read as 'o                                                 |                             |                                    |                  |                 |        |

## REGISTER 7-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

## 8.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

## 8.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to Section 25.1 "Configuration Bits" for further details). The Primary Configuration bits, POSCMD<1:0> Oscillator (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits. FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, shown in Table 8-1.

### 8.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|----------------------------------------------------|-------------------|-------------|------------|------|

| Fast RC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2 |

| (Reserved)                                         | Internal          | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 1    |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 11          | 100        | 1    |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |      |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |      |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |      |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |      |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |      |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1    |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 1    |

## TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### REGISTER 10-36: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

|        | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0    |

|--------|--------|--------|--------|--------|--------|--------|-----|--------|

| bit 15 | RP29R0 | RP29R1 | RP29R2 | RP29R3 | RP29R4 | RP29R5 | —   | —      |

|        | bit 8  |        |        |        |        |        |     | bit 15 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP29R<5:0>: RP29 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP29 (see Table 10-3 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP28R<5:0>: RP28 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP28 (see Table 10-3 for peripheral function numbers). |

## REGISTER 10-37: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15

| U-0    | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> |

| bit 15 |     |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 |

| bit 7 | •   |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP31R<5:0>:** RP31 Output Pin Mapping bits<sup>(1)</sup><br/>Peripheral output number n is assigned to pin, RP31 (see Table 10-3 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP30R<5:0>:** RP30 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP30 (see Table 10-3 for peripheral function numbers).

Note 1: Unimplemented in 64-pin and 80-pin devices; read as '0'.

## REGISTER 10-38: ALTRP: ALTERNATE PERIPHERAL PIN MAPPING REGISTER

| U-0    | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |  |  |  |

|--------|--------|-----|-----|-----|-----|-----|--------|--|--|--|

| —      | —      | —   | —   | —   | —   | —   | —      |  |  |  |

| bit 15 | bit 15 |     |     |     |     |     |        |  |  |  |

|        |        |     |     |     |     |     |        |  |  |  |

| U-0    | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |  |  |

| —      | —      | —   | —   | —   | —   | —   | SCK1CM |  |  |  |

| bit 7  |        |     |     |     |     |     | bit 0  |  |  |  |

|        |        |     |     |     |     |     |        |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0

SCK1CM: SCK1 Output Mapping Select bit

1 = SCK1 output function is mapped to ASCK1 pin only

0 = SCK1 output function is mapped according to RPORn registers

### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL 2 REGISTER (CONTINUED)

bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

11111 = This OC module<sup>(1)</sup> 11110 = Input Capture 9<sup>(2)</sup> 11101 = Input Capture 6<sup>(2)</sup> 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 10011 = Input Capture 8<sup>(2)</sup> 10010 = Input Capture 7<sup>(2)</sup> 1000x = reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1 01010 = Input Capture 5<sup>(2)</sup> 01001 = Output Compare 9<sup>(1)</sup> 01000 = Output Compare 8<sup>(1)</sup> 00111 = Output Compare 7<sup>(1)</sup> 00110 = Output Compare 6<sup>(1)</sup> 00101 = Output Compare 5<sup>(1)</sup> 00100 = Output Compare 4<sup>(1)</sup> 00011 = Output Compare 3<sup>(1)</sup> 00010 = Output Compare 2<sup>(1)</sup> 00001 = Output Compare 1<sup>(1)</sup> 00000 = Not synchronized to any other module

- **Note 1:** Never use an OC module as its own trigger source, either by selecting this mode or another equivalent SYNCSEL setting.

- **2:** Use these inputs as trigger sources only and never as sync sources.

## 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 23. "Serial Peripheral Interface (SPI)" (DS39699).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with Motorola's SPI and SIOP interfaces. All devices of the PIC24FJ256GA110 family include three SPI modules

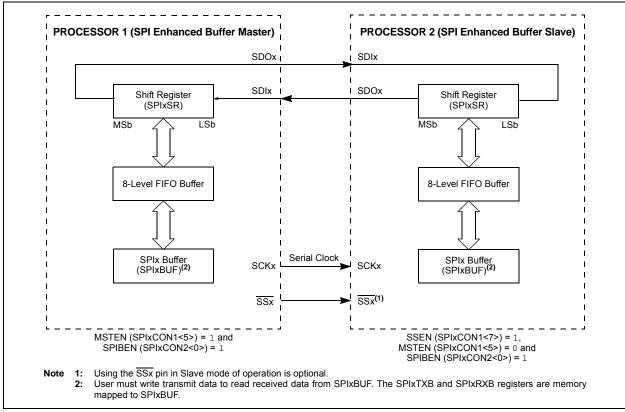

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported. The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode, SSx is not used. In the 2-pin mode, both SDOx and SSx are not used.

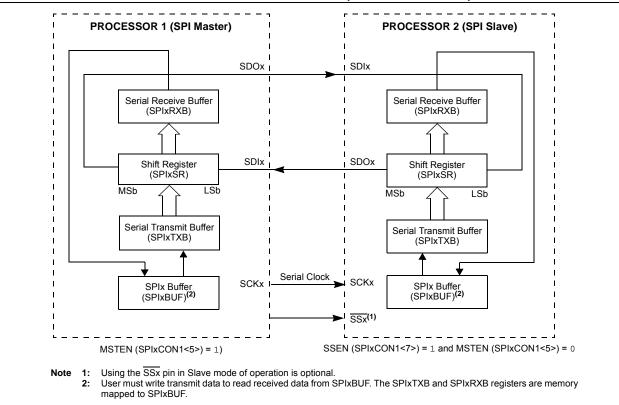

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the 3 SPI modules.

### FIGURE 15-3: SPI MASTER/SLAVE CONNECTION (STANDARD MODE)

## FIGURE 15-4: SPI MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                               |

|         | <ul><li>1 = High-Speed mode (baud clock generated from FcY/4)</li><li>0 = Standard mode (baud clock generated from FcY/16)</li></ul>                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                    |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                 |

|         | <ul><li>1 = Two Stop bits</li><li>0 = One Stop bit</li></ul>                                                                                                  |

- **Note 1:** If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See **Section 10.4 "Peripheral Pin Select"** for more information.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

...

011111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute

00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute

00000000 = No adjustment

11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute

10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute

- **Note 1:** The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- **3:** This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

## REGISTER 19-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0           | U-0          | U-0              | U-0              | U-0                                     | U-0             | U-0                     | U-0    |

|---------------|--------------|------------------|------------------|-----------------------------------------|-----------------|-------------------------|--------|

| —             | —            | _                | —                | —                                       | —               | —                       | —      |

| bit 15        |              |                  |                  |                                         |                 |                         | bit 8  |

|               |              |                  |                  |                                         |                 |                         |        |

| U-0           | U-0          | U-0              | U-0              | U-0                                     | U-0             | R/W-0                   | R/W-0  |

| —             | —            | —                | —                | —                                       | —               | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7         |              |                  |                  |                                         |                 |                         | bit 0  |

|               |              |                  |                  |                                         |                 |                         |        |

| Legend:       |              |                  |                  |                                         |                 |                         |        |

| R = Readabl   | le bit       | W = Writable I   | oit              | U = Unimplem                            | nented bit, rea | ad as '0'               |        |

| -n = Value at | t POR        | '1' = Bit is set |                  | '0' = Bit is cleared x = Bit is unknown |                 |                         |        |

|               |              |                  |                  |                                         |                 |                         |        |

| bit 15-2      | Unimplemen   | ted: Read as '0  | )'               |                                         |                 |                         |        |

| bit 1         | RTSECSEL:    | RTCC Seconds     | Clock Output     | Select bit <sup>(1)</sup>               |                 |                         |        |

|               | 1 = RTCC se  | conds clock is   | selected for the | e RTCC pin                              |                 |                         |        |

|               | 0 = RTCC ala | arm pulse is sel | ected for the F  | RTCC pin                                |                 |                         |        |

| bit 0         | PMPTTL: PM   | IP Module TTL    | Input Buffer Se  | elect bit                               |                 |                         |        |

|               | 1 = PMP mo   | dule inputs (PM  | Dx, PMCS1) u     | ise TTL input bi                        | uffers          |                         |        |

0 = PMP module inputs use Schmitt Trigger input buffers

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit must also be set.

## 20.3 Registers

There are four registers used to control programmable CRC operation:

- CRCCON

- CRCXOR

- CRCDAT

- CRCWDAT

## REGISTER 20-1: CRCCON: CRC CONTROL REGISTER

| U-0    | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| —      | —   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| CRCFUL | CRCMPT | —   | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 |

| bit 7  |        |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | CSIDL: CRC Stop in Idle Mode bit                                                                                                      |

|           | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |

| bit 12-8  | VWORD<4:0>: Pointer Value bits                                                                                                        |

|           | Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> > 7 or 16 when PLEN<3:0> $\leq$ 7.           |

| bit 7     | CRCFUL: FIFO Full bit                                                                                                                 |

|           | 1 = FIFO is full                                                                                                                      |

|           | 0 = FIFO is not full                                                                                                                  |

| bit 6     | CRCMPT: FIFO Empty Bit                                                                                                                |

|           | 1 = FIFO is empty                                                                                                                     |

|           | 0 = FIFO is not empty                                                                                                                 |

| bit 5     | Unimplemented: Read as '0'                                                                                                            |

| bit 4     | CRCGO: Start CRC bit                                                                                                                  |

|           | 1 = Start CRC serial shifter                                                                                                          |

|           | 0 = CRC serial shifter turned off                                                                                                     |

| bit 3-0   | PLEN<3:0>: Polynomial Length bits                                                                                                     |

|           | Denotes the length of the polynomial to be generated minus 1.                                                                         |

|           |                                                                                                                                       |

#### REGISTER 25-1: CW1: FLASH CONFIGURATION WORD 1 (CONTINUED)

bit 3-0 **WDTPS<3:0>:** Watchdog Timer Postscaler Select bits

1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 **= 1:2,048** 1010 = 1:1,024 1001 **= 1:512** 1000 **= 1:256** 0111 = 1:128 0110 **= 1:64** 0101 = 1:32 0100 = 1:16 0011 = 1:8 0010 = 1:4 0001 = 1:2 0000 = 1:1

## REGISTER 25-4: DEVID: DEVICE ID REGISTER

| U         | U                   | U               | U                 | U            | U          | U      | U      |

|-----------|---------------------|-----------------|-------------------|--------------|------------|--------|--------|

| —         | —                   | —               | —                 | —            | —          | —      | —      |

| bit 23    |                     |                 |                   |              |            |        | bit 16 |

|           |                     |                 |                   |              |            |        |        |

| U         | U                   | R               | R                 | R            | R          | R      | R      |

| _         | —                   | FAMID7          | FAMID6            | FAMID5       | FAMID4     | FAMID3 | FAMID2 |

| bit 15    |                     |                 |                   |              |            |        | bit 8  |

| R         | R                   | R               | R                 | R            | R          | R      | R      |

| FAMID1    | FAMIDO              | DEV5            | DEV4              | DEV3         | DEV2       | DEV1   | DEV0   |

| bit 7     |                     |                 |                   |              |            | 1      | bit 0  |

|           |                     |                 |                   |              |            |        |        |

| Legend: R | = Read-Only bit     | t               |                   | U = Unimplen | nented bit |        |        |

| bit 23-14 | Unimplement         | ted: Read as '  | 1'                |              |            |        |        |

| bit 13-6  | FAMID<7:0>:         | Device Family   | ldentifier bits   |              |            |        |        |

|           | 01000000 <b>=  </b> | PIC24FJ256G     | A110 family       |              |            |        |        |

| bit 5-0   | DEV<5:0>: In        | dividual Device | e Identifier bits |              |            |        |        |

|           | 000000 = PIC        | 24FJ64GA10      | 5                 |              |            |        |        |

|           | 000010 <b>= PIC</b> | 24FJ64GA108     | 3                 |              |            |        |        |

|           | 000110 = PIC        | 24FJ64GA110     | )                 |              |            |        |        |

|           | 001000 <b>= PIC</b> | 24FJ128GA1      | )6                |              |            |        |        |

|           |                     | 24FJ128GA1      |                   |              |            |        |        |

|           |                     | 24FJ128GA1      |                   |              |            |        |        |

|           |                     | 24FJ192GA1      |                   |              |            |        |        |

|           |                     | 24FJ192GA1      |                   |              |            |        |        |

|           |                     |                 |                   |              |            |        |        |

- 010110 = PIC24FJ192GA110

- 011000 = PIC24FJ256GA106

- 011010 = PIC24FJ256GA108

- 011110 = PIC24FJ256GA110

## REGISTER 25-5: DEVREV: DEVICE REVISION REGISTER

| U                                                               | U                                          | U             | U  | U | U    | U    | U      |  |  |

|-----------------------------------------------------------------|--------------------------------------------|---------------|----|---|------|------|--------|--|--|

| _                                                               | —                                          |               | —  | — | —    | —    | —      |  |  |

| bit 23                                                          |                                            |               |    |   |      |      | bit 16 |  |  |

|                                                                 |                                            |               |    |   |      |      |        |  |  |

| U                                                               | U                                          | U             | U  | U | U    | U    | R      |  |  |

| —                                                               | —                                          | —             |    | — | _    |      | MAJRV2 |  |  |

| bit 15                                                          |                                            |               |    |   |      |      | bit 8  |  |  |

|                                                                 |                                            |               |    |   |      |      |        |  |  |

| R                                                               | R                                          | U             | U  | U | R    | R    | R      |  |  |

| MAJRV1                                                          | MAJRV0                                     | —             | —  | — | DOT2 | DOT1 | DOT0   |  |  |

| bit 7                                                           |                                            |               |    |   |      |      | bit 0  |  |  |

| Legend:         R = Read-Only bit         U = Unimplemented bit |                                            |               |    |   |      |      |        |  |  |

| bit 23-9                                                        | Unimplement                                | ed: Read as ' | )' |   |      |      |        |  |  |

| bit 8-6                                                         | MAJRV<2:0>: Major Revision Identifier bits |               |    |   |      |      |        |  |  |

| bit 5-3                                                         | it 5-3 Unimplemented: Read as '0'          |               |    |   |      |      |        |  |  |

bit 2-0 DOT<2:0>: Minor Revision Identifier bits

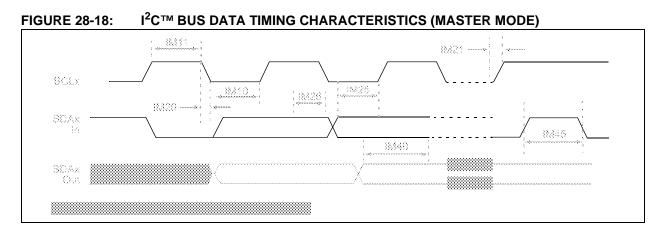

## TABLE 28-31: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS  |                           |                            |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                        |  |

|---------------------|---------------------------|----------------------------|---------------------------|-------------------------------------------------------|------|-------|----------------------------------------|--|

| Param<br>No. Symbol |                           | Charac                     | teristic                  | Min <sup>(1)</sup>                                    | Max  | Units | Conditions                             |  |

| IM10                | TLO:SCL                   | Clock Low Time             | 100 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μs    | _                                      |  |

|                     |                           |                            | 400 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μS    | —                                      |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       | _    | μs    | —                                      |  |

| IM11 THI:SCL        |                           | Clock High Time            | 100 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μs    | _                                      |  |

|                     |                           |                            | 400 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μs    | —                                      |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       | _    | μs    | —                                      |  |

| IM20 T              | TF:SCL                    | SDAx and SCLx<br>Fall Time | 100 kHz mode              | —                                                     | 300  | ns    | CB is specified to be                  |  |

|                     |                           |                            | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF                      |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | —                                                     | 100  | ns    | -                                      |  |

| IM21 Ti             | TR:SCL                    | SDAx and SCLx<br>Rise Time | 100 kHz mode              | —                                                     | 1000 | ns    | CB is specified to be                  |  |

|                     |                           |                            | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF                      |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | —                                                     | 300  | ns    | -                                      |  |

| IM25 TSU:DAT        | Data Input                | 100 kHz mode               | 250                       | _                                                     | ns   | —     |                                        |  |

|                     |                           | Setup Time                 | 400 kHz mode              | 100                                                   | _    | ns    | -                                      |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | TBD                                                   | _    | ns    |                                        |  |

| IM26 THD:DAT        | THD:DAT                   | Data Input                 | 100 kHz mode              | 0                                                     | _    | ns    | —                                      |  |

|                     |                           | Hold Time                  | 400 kHz mode              | 0                                                     | 0.9  | μS    |                                        |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | TBD                                                   |      | ns    |                                        |  |

| IM40                | TAA:SCL                   | Output Valid<br>From Clock | 100 kHz mode              | —                                                     | 3500 | ns    | _                                      |  |

|                     |                           |                            | 400 kHz mode              |                                                       | 1000 | ns    |                                        |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | _                                                     |      | ns    | _                                      |  |

| IM45                | TBF:SDA                   | Bus Free Time              | 100 kHz mode              | 4.7                                                   | _    | μs    | Time the bus must be free before a new |  |

|                     |                           |                            | 400 kHz mode              | 1.3                                                   | _    | μS    |                                        |  |

|                     |                           |                            | 1 MHz mode <sup>(2)</sup> | TBD                                                   | _    | μs    | transmission can start                 |  |

| IM50                | CB Bus Capacitive Loading |                            |                           | _                                                     | 400  | pF    | _                                      |  |

Legend: TBD = To Be Determined

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to **Section 16.3 "Setting Baud Rate When Operating as a Bus Master"** for details.

2: Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

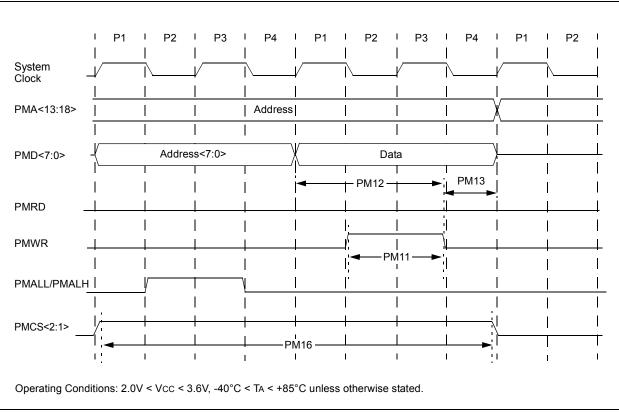

## FIGURE 28-23: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

| TABLE 28-36: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| AC CHARACTERISTICS |        |                                                                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |     |       |            |

|--------------------|--------|------------------------------------------------------------------------|-------------------------------------------------------|----------|-----|-------|------------|

| Param.<br>No       | Symbol | Characteristics <sup>(1)</sup>                                         | Min                                                   | Тур      | Max | Units | Conditions |

| PM11               |        | PMWR Pulse Width                                                       | —                                                     | 0.5 TCY  |     | ns    |            |

| PM12               |        | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup time) | —                                                     | 0.75 TCY | _   | ns    |            |

| PM13               |        | PMWR or PMEMB Invalid to Data Out<br>Invalid (data hold time)          | —                                                     | 0.25 TCY | _   | ns    |            |

| PM16               |        | PMCSx Pulse Width                                                      | TCY – 5                                               | _        | _   | ns    |            |

**Note 1:** Wait states disabled for all cases.