Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga110-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                     | Pin Number     |                 |     |                   |                                                                                            |

|----------|---------------------|----------------|-----------------|-----|-------------------|--------------------------------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer   | Description                                                                                |

| CTED1    | 28                  | 34             | 42              | I   | ANA               | CTMU External Edge Input 1.                                                                |

| CTED2    | 27                  | 33             | 41              | I   | ANA               | CTMU External Edge Input 2.                                                                |

| CTPLS    | 29                  | 35             | 43              | 0   |                   | CTMU Pulse Output.                                                                         |

| CVREF    | 23                  | 29             | 34              | 0   | _                 | Comparator Voltage Reference Output.                                                       |

| ENVREG   | 57                  | 71             | 86              | I   | ST                | Voltage Regulator Enable.                                                                  |

| INT0     | 35                  | 45             | 55              | I   | ST                | External Interrupt Input.                                                                  |

| MCLR     | 7                   | 9              | 13              | I   | ST                | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 39                  | 49             | 63              | I   | ANA               | Main Oscillator Input Connection.                                                          |

| OSCO     | 40                  | 50             | 64              | 0   | ANA               | Main Oscillator Output Connection.                                                         |

| PGEC1    | 15                  | 19             | 24              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 16                  | 20             | 25              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 17                  | 21             | 26              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 18                  | 22             | 27              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 11                  | 15             | 20              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 12                  | 16             | 21              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PMA0     | 30                  | 36             | 44              | I/O | ST                | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29                  | 35             | 43              | I/O | ST                | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8                   | 10             | 14              | 0   |                   | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | 6                   | 8              | 12              | 0   |                   | modes).                                                                                    |

| PMA4     | 5                   | 7              | 11              | 0   | _                 |                                                                                            |

| PMA5     | 4                   | 6              | 10              | 0   |                   |                                                                                            |

| PMA6     | 16                  | 24             | 29              | 0   |                   |                                                                                            |

| PMA7     | 22                  | 23             | 28              | 0   |                   |                                                                                            |

| PMA8     | 32                  | 40             | 50              | 0   |                   |                                                                                            |

| PMA9     | 31                  | 39             | 49              | 0   | _                 |                                                                                            |

| PMA10    | 28                  | 34             | 42              | 0   | _                 |                                                                                            |

| PMA11    | 27                  | 33             | 41              | 0   | _                 |                                                                                            |

| PMA12    | 24                  | 30             | 35              | 0   | _                 |                                                                                            |

| PMA13    | 23                  | 29             | 34              | 0   | _                 |                                                                                            |

| PMCS1    | 45                  | 57             | 71              | I/O | ST/TTL            | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMCS2    | 44                  | 56             | 70              | 0   | ST                | Parallel Master Port Chip Select 2 Strobe/Address Bit 14.                                  |

| PMBE     | 51                  | 63             | 78              | 0   | _                 | Parallel Master Port Byte Enable Strobe.                                                   |

| PMD0     | 60                  | 76             | 93              | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) or                                   |

| PMD1     | 61                  | 77             | 94              | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 62                  | 78             | 98              | I/O | ST/TTL            | 1                                                                                          |

| PMD3     | 63                  | 79             | 99              | I/O | ST/TTL            | 1                                                                                          |

| PMD4     | 64                  | 80             | 100             | I/O | ST/TTL            | 1                                                                                          |

| PMD5     | 1                   | 1              | 3               | I/O | ST/TTL            |                                                                                            |

| PMD6     | 2                   | 2              | 4               | I/O | ST/TTL            |                                                                                            |

| PMD7     | 3                   | 3              | 5               | I/O | ST/TTL            |                                                                                            |

| PMRD     | 53                  | 67             | 82              | 0   | _                 | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 52                  | 66             | 81              | 0   | _                 | Parallel Master Port Write Strobe.                                                         |

| Legend:  | TTL = TTL in        |                |                 | -   | ST = 5            | Schmitt Trigger input buffer                                                               |

|          | ANA = Analog        |                | utput           |     | I <sup>2</sup> C™ | = I <sup>2</sup> C/SMBus input buffer                                                      |

### TABLE 1-4: PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

### TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14                 | Bit 13                 | Bit 12                 | Bit 11                 | Bit 10                 | Bit 9                  | Bit 8                 | Bit 7                  | Bit 6                 | Bit 5                  | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-----------------------|------------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------|

| CNPD1        | 0054 | CN15PDE                | CN14PDE                | CN13PDE                | CN12PDE                | CN11PDE                | CN10PDE                | CN9PDE                 | CN8PDE                | CN7PDE                 | CN6PDE                | CN5PDE                 | CN4PDE                 | CN3PDE                 | CN2PDE                 | CN1PDE                 | CN0PDE                 | 0000          |

| CNPD2        | 0056 | CN31PDE                | CN30PDE                | CN29PDE                | CN28PDE                | CN27PDE                | CN26PDE                | CN25PDE                | CN24PDE               | CN23PDE                | CN22PDE               | CN21PDE <sup>(1)</sup> | CN20PDE <sup>(1)</sup> | CN19PDE <sup>(1)</sup> | CN18PDE                | CN17PDE                | CN16PDE                | 0000          |

| CNPD3        | 0058 | CN47PDE(1)             | CN46PDE <sup>(2)</sup> | CN45PDE <sup>(1)</sup> | CN44PDE <sup>(1)</sup> | CN43PDE <sup>(1)</sup> | CN42PDE <sup>(1)</sup> | CN41PDE <sup>(1)</sup> | CN40PDE(2)            | CN39PDE <sup>(2)</sup> | CN38PDE(2)            | CN37PDE <sup>(2)</sup> | CN36PDE <sup>(2)</sup> | CN35PDE <sup>(2)</sup> | CN34PDE <sup>(2)</sup> | CN33PDE <sup>(2)</sup> | CN32PDE                | 0000          |

| CNPD4        | 005A | CN63PDE                | CN62PDE                | CN61PDE                | CN60PDE                | CN59PDE                | CN58PDE                | CN57PDE <sup>(1)</sup> | CN56PDE               | CN55PDE                | CN54PDE               | CN53PDE                | CN52PDE                | CN51PDE                | CN50PDE                | CN49PDE                | CN48PDE <sup>(2)</sup> | 0000          |

| CNPD5        | 005C | CN79PDE(2)             | CN78PDE <sup>(1)</sup> | CN77PDE <sup>(1)</sup> | CN76PDE <sup>(2)</sup> | CN75PDE <sup>(2)</sup> | CN74PDE <sup>(1)</sup> | CN73PDE <sup>(1)</sup> | CN72PDE               | CN71PDE                | CN70PDE               | CN69PDE                | CN68PDE                | CN67PDE <sup>(1)</sup> | CN66PDE <sup>(1)</sup> | CN65PDE                | CN64PDE                | 0000          |

| CNPD6        | 005E | _                      | _                      | _                      | -                      | _                      | _                      | _                      | _                     | _                      | _                     | _                      | CN84PDE                | CN83PDE                | CN82PDE <sup>(2)</sup> | CN81PDE(2)             | CN80PDE(2)             | 0000          |

| CNEN1        | 0060 | CN15IE                 | CN14IE                 | CN13IE                 | CN12IE                 | CN11IE                 | CN10IE                 | CN9IE                  | CN8IE                 | CN7IE                  | CN6IE                 | CN5IE                  | CN4IE                  | CN3IE                  | CN2IE                  | CN1IE                  | CN0IE                  | 0000          |

| CNEN2        | 0062 | CN31IE                 | CN30IE                 | CN29IE                 | CN28IE                 | CN27IE                 | CN26IE                 | CN25IE                 | CN24IE                | CN23IE                 | CN22IE                | CN21IE <sup>(1)</sup>  | CN20IE <sup>(1)</sup>  | CN19IE <sup>(1)</sup>  | CN18IE                 | CN17IE                 | CN16IE                 | 0000          |

| CNEN3        | 0064 | CN47IE <sup>(1)</sup>  | CN46IE <sup>(2)</sup>  | CN45IE <sup>(1)</sup>  | CN44IE <sup>(1)</sup>  | CN43IE <sup>(1)</sup>  | CN42IE <sup>(1)</sup>  | CN41IE <sup>(1)</sup>  | CN40IE <sup>(2)</sup> | CN39IE <sup>(2)</sup>  | CN38IE <sup>(2)</sup> | CN37IE <sup>(2)</sup>  | CN36IE <sup>(2)</sup>  | CN35IE <sup>(2)</sup>  | CN34IE <sup>(2)</sup>  | CN33IE <sup>(2)</sup>  | CN32IE                 | 0000          |

| CNEN4        | 0066 | CN63IE                 | CN62IE                 | CN61IE                 | CN60IE                 | CN59IE                 | CN58IE                 | CN57IE <sup>(1)</sup>  | CN56IE                | CN55IE                 | CN54IE                | CN53IE                 | CN52IE                 | CN51IE                 | CN50IE                 | CN49IE                 | CN48IE <sup>(2)</sup>  | 0000          |

| CNEN5        | 0068 | CN79IE <sup>(2)</sup>  | CN78IE <sup>(1)</sup>  | CN77IE <sup>(1)</sup>  | CN76IE <sup>(2)</sup>  | CN75IE <sup>(2)</sup>  | CN74IE <sup>(1)</sup>  | CN73IE <sup>(1)</sup>  | CN72IE                | CN71IE                 | CN70IE                | CN69IE                 | CN68IE                 | CN67IE <sup>(1)</sup>  | CN66IE <sup>(1)</sup>  | CN65IE                 | CN64IE                 | 0000          |

| CNEN6        | 006A | _                      | _                      | _                      | _                      | _                      | —                      | _                      | _                     | —                      | _                     | _                      | CN84IE                 | CN83IE                 | CN82IE <sup>(2)</sup>  | CN81IE <sup>(2)</sup>  | CN80IE <sup>(2)</sup>  | 0000          |

| CNPU1        | 006C | CN15PUE                | CN14PUE                | CN13PUE                | CN12PUE                | CN11PUE                | CN10PUE                | CN9PUE                 | CN8PUE                | CN7PUE                 | CN6PUE                | CN5PUE                 | CN4PUE                 | <b>CN3PUE</b>          | CN2PUE                 | CN1PUE                 | CN0PUE                 | 0000          |

| CNPU2        | 006E | CN31PUE                | CN30PUE                | CN29PUE                | CN28PUE                | CN27PUE                | CN26PUE                | CN25PUE                | CN24PUE               | CN23PUE                | CN22PUE               | CN21PUE <sup>(1)</sup> | CN20PUE <sup>(1)</sup> | CN19PUE <sup>(1)</sup> | CN18PUE                | CN17PUE                | CN16PUE                | 0000          |

| CNPU3        | 0070 | CN47PUE <sup>(1)</sup> | CN46PUE <sup>(2)</sup> | CN45PUE <sup>(1)</sup> | CN44PUE <sup>(1)</sup> | CN43PUE <sup>(1)</sup> | CN42PUE <sup>(1)</sup> | CN41PUE <sup>(1)</sup> | CN40PUE(2)            | CN39PUE <sup>(2)</sup> | CN38PUE(2)            | CN37PUE <sup>(2)</sup> | CN36PUE <sup>(2)</sup> | CN35PUE <sup>(2)</sup> | CN34PUE <sup>(2)</sup> | CN33PUE <sup>(2)</sup> | CN32PUE                | 0000          |

| CNPU4        | 0072 | CN63PUE                | CN62PUE                | CN61PUE                | CN60PUE                | CN59PUE                | CN58PUE                | CN57PUE <sup>(1)</sup> | CN56PUE               | CN55PUE                | CN54PUE               | CN53PUE                | CN52PUE                | CN51PUE                | CN50PUE                | CN49PUE                | CN48PUE <sup>(2)</sup> | 0000          |

| CNPU5        | 0074 | CN79PUE <sup>(2)</sup> | CN78PUE <sup>(1)</sup> | CN77PUE <sup>(1)</sup> | CN76PUE <sup>(2)</sup> | CN75PUE <sup>(2)</sup> | CN74PUE <sup>(1)</sup> | CN73PUE <sup>(1)</sup> | CN72PUE               | CN71PUE                | CN70PUE               | CN69PUE                | CN68PUE                | CN67PUE <sup>(1)</sup> | CN66PUE <sup>(1)</sup> | CN65PUE                | CN64PUE                | 0000          |

| CNPU6        | 0076 | _                      | _                      | _                      | _                      |                        | —                      |                        | _                     | —                      | _                     | _                      | CN84PUE                | CN83PUE                | CN82PUE <sup>(2)</sup> | CN81PUE <sup>(2)</sup> | CN80PUE <sup>(2)</sup> | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Unimplemented in 64-pin devices; read as '0'.

**2:** Unimplemented in 64-pin and 80-pin devices; read as '0'.

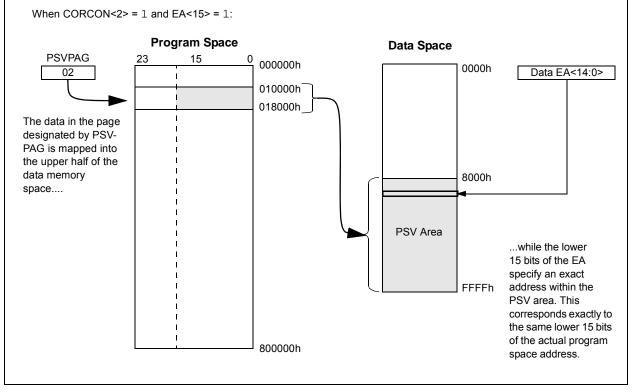

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit (MSb) of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

| U-0          | U-0                                                       | R/W-0                                                                                                                     | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|--------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-----------------|-----------------|--------|--|--|--|--|

| —            | —                                                         | PMPIF                                                                                                                     | OC8IF            | OC7IF              | OC6IF           | OC5IF           | IC6IF  |  |  |  |  |

| bit 15       |                                                           |                                                                                                                           |                  |                    |                 |                 | bit 8  |  |  |  |  |

|              |                                                           |                                                                                                                           |                  |                    |                 |                 |        |  |  |  |  |

| R/W-0        | R/W-0                                                     | R/W-0                                                                                                                     | U-0              | U-0                | U-0             | R/W-0           | R/W-0  |  |  |  |  |

| IC5IF        | IC4IF                                                     | IC3IF                                                                                                                     |                  | _                  |                 | SPI2IF          | SPF2IF |  |  |  |  |

| bit 7        |                                                           |                                                                                                                           |                  |                    |                 |                 | bit    |  |  |  |  |

| Legend:      |                                                           |                                                                                                                           |                  |                    |                 |                 |        |  |  |  |  |

| R = Readab   | le bit                                                    | W = Writable                                                                                                              | bit              | U = Unimplen       | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value a | t POR                                                     | '1' = Bit is set                                                                                                          |                  | '0' = Bit is clea  |                 | x = Bit is unkr | nown   |  |  |  |  |

|              |                                                           |                                                                                                                           |                  |                    |                 |                 |        |  |  |  |  |

| bit 15-14    | Unimplemen                                                | ted: Read as '                                                                                                            | 0'               |                    |                 |                 |        |  |  |  |  |

| bit 13       | PMPIF: Para                                               | llel Master Port                                                                                                          | Interrupt Flag   | Status bit         |                 |                 |        |  |  |  |  |

|              |                                                           | request has oc<br>request has no                                                                                          |                  |                    |                 |                 |        |  |  |  |  |

| bit 12       |                                                           | •                                                                                                                         |                  | ipt Flag Status I  | oit             |                 |        |  |  |  |  |

|              | •                                                         | request has oc                                                                                                            |                  | ipt ing change     |                 |                 |        |  |  |  |  |

|              | 0 = Interrupt                                             | request has no                                                                                                            | toccurred        |                    |                 |                 |        |  |  |  |  |

| bit 11       | OC7IF: Output Compare Channel 7 Interrupt Flag Status bit |                                                                                                                           |                  |                    |                 |                 |        |  |  |  |  |

|              | •                                                         | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| oit 10       | •                                                         | <ul> <li>Interrupt request has not occurred</li> <li>OC6IF: Output Compare Channel 6 Interrupt Flag Status bit</li> </ul> |                  |                    |                 |                 |        |  |  |  |  |

|              | -                                                         | request has oc                                                                                                            |                  | ipt i lag Status i | Jit             |                 |        |  |  |  |  |

|              |                                                           | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| bit 9        | OC5IF: Outp                                               | ut Compare Ch                                                                                                             | annel 5 Interru  | ipt Flag Status I  | oit             |                 |        |  |  |  |  |

|              |                                                           | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| L:1 0        |                                                           | request has no                                                                                                            |                  | les Ctatus bit     |                 |                 |        |  |  |  |  |

| bit 8        | -                                                         | IC6IF: Input Capture Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred                            |                  |                    |                 |                 |        |  |  |  |  |

|              | 0 = Interrupt request has not occurred                    |                                                                                                                           |                  |                    |                 |                 |        |  |  |  |  |

| bit 7        | IC5IF: Input (                                            | Capture Chann                                                                                                             | el 5 Interrupt F | lag Status bit     |                 |                 |        |  |  |  |  |

|              |                                                           | request has oc                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

|              | •                                                         | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| bit 6        | -                                                         | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                                                  |                  |                    |                 |                 |        |  |  |  |  |

|              |                                                           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                    |                  |                    |                 |                 |        |  |  |  |  |

| bit 5        |                                                           | Capture Chann                                                                                                             |                  | lag Status bit     |                 |                 |        |  |  |  |  |

|              | -                                                         | request has oc                                                                                                            | -                | •                  |                 |                 |        |  |  |  |  |

|              | -                                                         | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| oit 4-2      | -                                                         | ted: Read as '                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

| bit 1        |                                                           | Event Interrup                                                                                                            | -                | It                 |                 |                 |        |  |  |  |  |

|              |                                                           | request has oc<br>request has no                                                                                          |                  |                    |                 |                 |        |  |  |  |  |

| bit 0        | -                                                         | 2 Fault Interrup                                                                                                          |                  | it                 |                 |                 |        |  |  |  |  |

|              |                                                           | request has oc                                                                                                            | -                |                    |                 |                 |        |  |  |  |  |

|              |                                                           | request has no                                                                                                            |                  |                    |                 |                 |        |  |  |  |  |

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0          | U-0                                                                                                    | R/W-0                                | U-0             | U-0               | U-0              | U-0             | R/W-0 |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|

| _            |                                                                                                        | CTMUIF                               | _               | _                 | —                | —               | LVDIF |  |  |  |

| bit 15       |                                                                                                        |                                      |                 |                   |                  |                 | bit 8 |  |  |  |

|              |                                                                                                        |                                      |                 |                   |                  |                 |       |  |  |  |

| U-0          | U-0                                                                                                    | U-0                                  | U-0             | R/W-0             | R/W-0            | R/W-0           | U-0   |  |  |  |

|              | —                                                                                                      | —                                    |                 | CRCIF             | U2ERIF           | U1ERIF          | —     |  |  |  |

| bit 7        |                                                                                                        |                                      |                 |                   |                  |                 | bit 0 |  |  |  |

| Legend:      |                                                                                                        |                                      |                 |                   |                  |                 |       |  |  |  |

| R = Readab   | ole bit                                                                                                | W = Writable b                       | oit             | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value a | at POR                                                                                                 | '1' = Bit is set                     |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |  |

|              |                                                                                                        |                                      |                 |                   |                  |                 |       |  |  |  |

| bit 15-14    | Unimplemer                                                                                             | nted: Read as '0                     | ,               |                   |                  |                 |       |  |  |  |

| bit 13       | CTMUIF: CT                                                                                             | MU Interrupt Fla                     | g Status bit    |                   |                  |                 |       |  |  |  |

|              |                                                                                                        | request has occur<br>request has not |                 |                   |                  |                 |       |  |  |  |

| bit 12-9     |                                                                                                        | nted: Read as '0                     |                 |                   |                  |                 |       |  |  |  |

| bit 8        | LVDIF: Low-                                                                                            | Voltage Detect Ir                    | nterrupt Flag S | Status bit        |                  |                 |       |  |  |  |

|              |                                                                                                        | request has occurrequest has not     |                 |                   |                  |                 |       |  |  |  |

| bit 7-4      | Unimplemer                                                                                             | nted: Read as '0                     | ,               |                   |                  |                 |       |  |  |  |

| bit 3        | CRCIF: CRC                                                                                             | Generator Inter                      | rupt Flag Stat  | us bit            |                  |                 |       |  |  |  |

|              |                                                                                                        | request has occu                     |                 |                   |                  |                 |       |  |  |  |

|              |                                                                                                        | request has not                      |                 |                   |                  |                 |       |  |  |  |

| bit 2        |                                                                                                        | RT2 Error Interru                    |                 | s bit             |                  |                 |       |  |  |  |

|              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                      |                 |                   |                  |                 |       |  |  |  |

| bit 1        |                                                                                                        | RT1 Error Interru                    |                 | e hit             |                  |                 |       |  |  |  |

|              |                                                                                                        | request has occi                     |                 | 5 51              |                  |                 |       |  |  |  |

|              |                                                                                                        |                                      |                 |                   |                  |                 |       |  |  |  |

|              | 0 = Interrupt                                                                                          | request has not                      | occurred        |                   |                  |                 |       |  |  |  |

## REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| R/W-0        | U-0                                                                                                                                                                         | R/W-0                                                                                | R/W-0                  | R/W-0             | R/W-0            | R/W-0            | R/W-0  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|-------------------|------------------|------------------|--------|--|--|--|--|--|

| ROEN         |                                                                                                                                                                             | ROSSLP                                                                               | ROSEL                  | RODIV3            | RODIV2           | RODIV1           | RODIV0 |  |  |  |  |  |

| bit 15       |                                                                                                                                                                             |                                                                                      |                        |                   |                  |                  | bit 8  |  |  |  |  |  |

| U-0          | U-0                                                                                                                                                                         | U-0                                                                                  | U-0                    | U-0               | U-0              | U-0              | U-0    |  |  |  |  |  |

| _            | _                                                                                                                                                                           | _                                                                                    | _                      | _                 | _                | _                | _      |  |  |  |  |  |

| bit 7        |                                                                                                                                                                             |                                                                                      |                        |                   |                  |                  | bit C  |  |  |  |  |  |

| Legend:      |                                                                                                                                                                             |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                     | W = Writable                                                                         | bit                    | U = Unimplem      | nented bit, read | d as '0'         |        |  |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                                      | '1' = Bit is set                                                                     |                        | '0' = Bit is clea | ared             | x = Bit is unkn  | own    |  |  |  |  |  |

|              |                                                                                                                                                                             |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

| bit 15       |                                                                                                                                                                             | ence Oscillator                                                                      | -                      |                   |                  |                  |        |  |  |  |  |  |

|              |                                                                                                                                                                             | e oscillator ena<br>e oscillator disa                                                |                        | pin               |                  |                  |        |  |  |  |  |  |

| bit 14       | Unimplemen                                                                                                                                                                  | ted: Read as '                                                                       | 0'                     |                   |                  |                  |        |  |  |  |  |  |

| bit 13       | ROSSLP: Re                                                                                                                                                                  | ROSSLP: Reference Oscillator Output Stop in Sleep bit                                |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1 = Reference oscillator continues to run in Sleep                                                                                                                          |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 0 = Reference                                                                                                                                                               | e oscillator is d                                                                    | isabled in Slee        | р                 |                  |                  |        |  |  |  |  |  |

| bit 12       | ROSEL: Reference Oscillator Source Select bit                                                                                                                               |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1 = Primary Oscillator used as the base clock. Note that the crystal oscillator must be enabled using<br>the FOSC<2:0> bits; crystal maintains the operation in Sleep mode. |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              |                                                                                                                                                                             | •                                                                                    |                        |                   | •                | switching of the | device |  |  |  |  |  |

| bit 11-8     | <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits                                                                                                           |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1111 = Base clock value divided by 32,768                                                                                                                                   |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1110 = Base clock value divided by 16,384                                                                                                                                   |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              |                                                                                                                                                                             | 1101 = Base clock value divided by 8,192<br>1100 = Base clock value divided by 4,096 |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1011 = Base clock value divided by 2,048                                                                                                                                    |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              |                                                                                                                                                                             | 1010 = Base clock value divided by 1,024                                             |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256                                                                                            |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 0111 = Base clock value divided by 128                                                                                                                                      |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 0110 = Base clock value divided by 64                                                                                                                                       |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 0101 = Base clock value divided by 32<br>0100 = Base clock value divided by 16                                                                                              |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              |                                                                                                                                                                             |                                                                                      |                        |                   |                  |                  |        |  |  |  |  |  |

|              | 0011 = Base                                                                                                                                                                 | clock value div                                                                      | ided by 8              |                   |                  |                  |        |  |  |  |  |  |

|              | 0011 = Base<br>0010 = Base                                                                                                                                                  | clock value div<br>clock value div                                                   | ided by 8<br>ided by 4 |                   |                  |                  |        |  |  |  |  |  |

|              | 0011 = Base<br>0010 = Base                                                                                                                                                  | clock value div<br>clock value div<br>clock value div                                | ided by 8<br>ided by 4 |                   |                  |                  |        |  |  |  |  |  |

## © 2010 Microchip Technology Inc.

## REGISTER 10-7: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| U-0     | U-0 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-----|-------|--------|-------|-------|-------|-------|

| _       | —   | IC4R5 | IC4R4  | IC4R3 | IC4R2 | IC4R1 | IC4R0 |

| bit 15  | -   |       | -<br>- | •     |       |       | bit 8 |

|         |     |       |        |       |       |       |       |

| U-0     | U-0 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|         | —   | IC3R5 | IC3R4  | IC3R3 | IC3R2 | IC3R1 | IC3R0 |

| bit 7   |     |       |        |       |       |       | bit 0 |

|         |     |       |        |       |       |       |       |

| Legend: |     |       |        |       |       |       |       |

| Legena.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC4R<5:0>: Assign Input Capture 4 (IC4) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC3R<5:0>: Assign Input Capture 3 (IC3) to Corresponding RPn or RPIn Pin bits |

### REGISTER 10-8: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | IC6R5 | IC6R4 | IC6R3 | IC6R2 | IC6R1 | IC6R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC5R5 | IC5R4 | IC5R3 | IC5R2 | IC5R1 | IC5R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC6R<5:0>: Assign Input Capture 6 (IC6) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC5R<5:0>: Assign Input Capture 5 (IC5) to Corresponding RPn or RPIn Pin bits

|        | • • • • • • • |         |         |         |         |         |         |

|--------|---------------|---------|---------|---------|---------|---------|---------|

| U-0    | U-0           | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

| —      | —             | U4CTSR5 | U4CTSR4 | U4CTSR3 | U4CTSR2 | U4CTSR1 | U4CTSR0 |

| bit 15 |               |         |         |         |         |         | bit 8   |

## REGISTER 10-19: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U4CTSR<5:0>: Assign UART4 Clear to Send (U4CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U4RXR<5:0>: Assign UART4 Receive (U4RX) to Corresponding RPn or RPIn Pin bits         |

## **REGISTER 10-20: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28**

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 SCK3R<5:0>: Assign SPI3 Data Input (SCK3IN) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8

RP21R<5:0>: RP21 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP21 (see Table 10-3 for peripheral function numbers).

bit 7-6

Unimplemented: Read as '0'

- bit 5-0 **RP20R<5:0:>** RP20 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP20 (see Table 10-3 for peripheral function numbers).

#### REGISTER 10-33: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP23R5 | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP23R<5:0>:** RP23 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP23 (see Table 10-3 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP22R<5:0>:** RP22 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP22 (see Table 10-3 for peripheral function numbers).

## 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 14. "Timers" (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two independent 16-bit timers with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- Single 32-bit synchronous counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- ADC Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC event trigger; this is implemented only with Timer3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON      |

|-------|--------------------------------------------|

|       | control bits are ignored. Only T2CON and   |

|       | T4CON control bits are used for setup and  |

|       | control. Timer2 and Timer4 clock and gate  |

|       | inputs are utilized for the 32-bit timer   |

|       | modules, but an interrupt is generated     |

|       | with the Timer3 or Timer5 interrupt flags. |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair: TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

bits

## EQUATION 14-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

Maximum PWM Resolution (bits) =  $\frac{\log_{10} \left( \frac{FCY}{FPWM \bullet (Timer Prescale Value)} \right)}{1 + \frac{FCY}{FPWM \bullet (Timer Prescale Value)}}$

$\log_{10}(2)$

**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

# EXAMPLE 14-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

| 1. | Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where FOSC = 8 MHz with PLL                |  |  |  |  |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|    | (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.                                                         |  |  |  |  |  |  |  |  |

|    | TCY = 2 * TOSC = 62.5  ns                                                                                                 |  |  |  |  |  |  |  |  |

|    | PWM Period = $1/PWM$ Frequency = $1/52.08$ kHz = $19.2 \mu s$                                                             |  |  |  |  |  |  |  |  |

|    | PWM Period = $(PR2 + 1) \bullet TCY \bullet (Timer2 Prescale Value)$                                                      |  |  |  |  |  |  |  |  |

|    | 19.2 $\mu$ s = (PR2 + 1) • 62.5 ns • 1                                                                                    |  |  |  |  |  |  |  |  |

|    | PR2 = 306                                                                                                                 |  |  |  |  |  |  |  |  |

| 2. | Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate: |  |  |  |  |  |  |  |  |

|    | PWM Resolution = $\log_{10}(FCY/FPWM)/\log_{10}2)$ bits                                                                   |  |  |  |  |  |  |  |  |

|    | $= (\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2) \text{ bits}$                                                 |  |  |  |  |  |  |  |  |

|    | = 8.3 bits                                                                                                                |  |  |  |  |  |  |  |  |

|    |                                                                                                                           |  |  |  |  |  |  |  |  |

| N  | ote 1: Based on Tcy = 2 * Tosc, Doze mode and PLL are disabled.                                                           |  |  |  |  |  |  |  |  |

## TABLE 14-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

## TABLE 14-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL 2 REGISTER (CONTINUED)

bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

11111 = This OC module<sup>(1)</sup> 11110 = Input Capture 9<sup>(2)</sup> 11101 = Input Capture 6<sup>(2)</sup> 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 10011 = Input Capture 8<sup>(2)</sup> 10010 = Input Capture 7<sup>(2)</sup> 1000x = reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1 01010 = Input Capture 5<sup>(2)</sup> 01001 = Output Compare 9<sup>(1)</sup> 01000 = Output Compare 8<sup>(1)</sup> 00111 = Output Compare 7<sup>(1)</sup> 00110 = Output Compare 6<sup>(1)</sup> 00101 = Output Compare 5<sup>(1)</sup> 00100 = Output Compare 4<sup>(1)</sup> 00011 = Output Compare 3<sup>(1)</sup> 00010 = Output Compare 2<sup>(1)</sup> 00001 = Output Compare 1<sup>(1)</sup> 00000 = Not synchronized to any other module

- **Note 1:** Never use an OC module as its own trigger source, either by selecting this mode or another equivalent SYNCSEL setting.

- **2:** Use these inputs as trigger sources only and never as sync sources.

## REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                             |

|       | 0 = Stop bit was not detected last                                                                                                                                                                                               |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                               |

| bit 3 | S: Start bit                                                                                                                                                                                                                     |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                       |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                               |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                         |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                              |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>      |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                             |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>            |

## 19.0 REAL-TIME CLOCK AND CALENDAR (RTCC)