Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga110t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Pin Number          |                |                 |     |                   |                                                                                            |

|----------|---------------------|----------------|-----------------|-----|-------------------|--------------------------------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer   | Description                                                                                |

| CTED1    | 28                  | 34             | 42              | I   | ANA               | CTMU External Edge Input 1.                                                                |

| CTED2    | 27                  | 33             | 41              | I   | ANA               | CTMU External Edge Input 2.                                                                |

| CTPLS    | 29                  | 35             | 43              | 0   |                   | CTMU Pulse Output.                                                                         |

| CVREF    | 23                  | 29             | 34              | 0   | _                 | Comparator Voltage Reference Output.                                                       |

| ENVREG   | 57                  | 71             | 86              | I   | ST                | Voltage Regulator Enable.                                                                  |

| INT0     | 35                  | 45             | 55              | I   | ST                | External Interrupt Input.                                                                  |

| MCLR     | 7                   | 9              | 13              | I   | ST                | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 39                  | 49             | 63              | I   | ANA               | Main Oscillator Input Connection.                                                          |

| OSCO     | 40                  | 50             | 64              | 0   | ANA               | Main Oscillator Output Connection.                                                         |

| PGEC1    | 15                  | 19             | 24              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 16                  | 20             | 25              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 17                  | 21             | 26              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 18                  | 22             | 27              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 11                  | 15             | 20              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 12                  | 16             | 21              | I/O | ST                | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

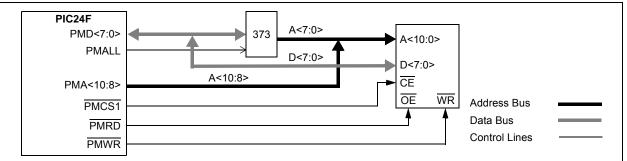

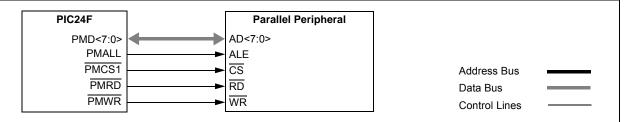

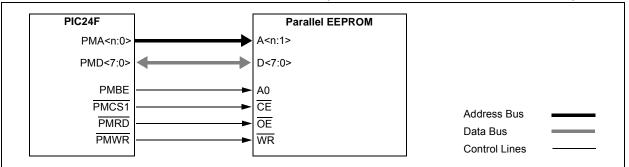

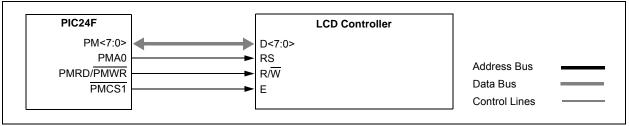

| PMA0     | 30                  | 36             | 44              | I/O | ST                | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29                  | 35             | 43              | I/O | ST                | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8                   | 10             | 14              | 0   |                   | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | 6                   | 8              | 12              | 0   |                   | modes).                                                                                    |

| PMA4     | 5                   | 7              | 11              | 0   | _                 |                                                                                            |

| PMA5     | 4                   | 6              | 10              | 0   |                   |                                                                                            |

| PMA6     | 16                  | 24             | 29              | 0   |                   |                                                                                            |

| PMA7     | 22                  | 23             | 28              | 0   |                   |                                                                                            |

| PMA8     | 32                  | 40             | 50              | 0   |                   |                                                                                            |

| PMA9     | 31                  | 39             | 49              | 0   | _                 |                                                                                            |

| PMA10    | 28                  | 34             | 42              | 0   | —                 |                                                                                            |

| PMA11    | 27                  | 33             | 41              | 0   | _                 |                                                                                            |

| PMA12    | 24                  | 30             | 35              | 0   | _                 |                                                                                            |

| PMA13    | 23                  | 29             | 34              | 0   | _                 |                                                                                            |

| PMCS1    | 45                  | 57             | 71              | I/O | ST/TTL            | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMCS2    | 44                  | 56             | 70              | 0   | ST                | Parallel Master Port Chip Select 2 Strobe/Address Bit 14.                                  |

| PMBE     | 51                  | 63             | 78              | 0   | _                 | Parallel Master Port Byte Enable Strobe.                                                   |

| PMD0     | 60                  | 76             | 93              | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) or                                   |

| PMD1     | 61                  | 77             | 94              | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 62                  | 78             | 98              | I/O | ST/TTL            | 1                                                                                          |

| PMD3     | 63                  | 79             | 99              | I/O | ST/TTL            | 1                                                                                          |

| PMD4     | 64                  | 80             | 100             | I/O | ST/TTL            | 1                                                                                          |

| PMD5     | 1                   | 1              | 3               | I/O | ST/TTL            |                                                                                            |

| PMD6     | 2                   | 2              | 4               | I/O | ST/TTL            |                                                                                            |

| PMD7     | 3                   | 3              | 5               | I/O | ST/TTL            |                                                                                            |

| PMRD     | 53                  | 67             | 82              | 0   | _                 | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 52                  | 66             | 81              | 0   | _                 | Parallel Master Port Write Strobe.                                                         |

| Legend:  | TTL = TTL in        |                |                 | -   | ST = 5            | Schmitt Trigger input buffer                                                               |

|          | ANA = Analog        |                | utput           |     | I <sup>2</sup> C™ | = I <sup>2</sup> C/SMBus input buffer                                                      |

#### TABLE 1-4: PIC24FJ256GA110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

#### 2.4 **Voltage Regulator Pins** (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This section applies only to PIC24F J      |

|-------|--------------------------------------------|

|       | devices with an on-chip voltage regulator. |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- · For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to Section 25.2 "On-Chip Voltage Regulator" for details on connecting and using the on-chip regulator.

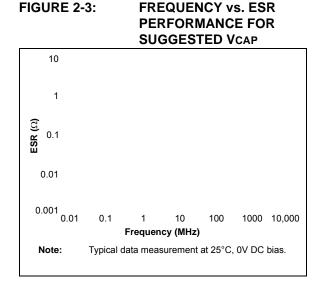

When the regulator is enabled, a low-ESR (<  $5\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10 µF connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to Section 28.0 "Electrical Characteristics" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to Section 28.0 "Electrical Characteristics" for information on VDD and VDDCORE.

| TABLE 2-1: | SUITABLE CAPACITOR EQUIVALENTS |                        |                |               |              |  |  |  |  |

|------------|--------------------------------|------------------------|----------------|---------------|--------------|--|--|--|--|

| Make       | Part #                         | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |  |  |  |  |

| TDK        | C3216X7R1C106K                 | 10 µF                  | ±10%           | 16V           | -55 to 125°C |  |  |  |  |

| TDK        | C3216X5R1C106K                 | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |  |  |  |  |

| Panasonic  | ECJ-3YX1C106K                  | 10 µF                  | ±10%           | 16V           | -55 to 125°C |  |  |  |  |

| Panasonic  | ECJ-4YB1C106K                  | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |  |  |  |  |

| Murata     | GRM32DR71C106KA01L             | 10 µF                  | ±10%           | 16V           | -55 to 125°C |  |  |  |  |

| Murata     | GRM31CR61C106KC31L             | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |  |  |  |  |

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

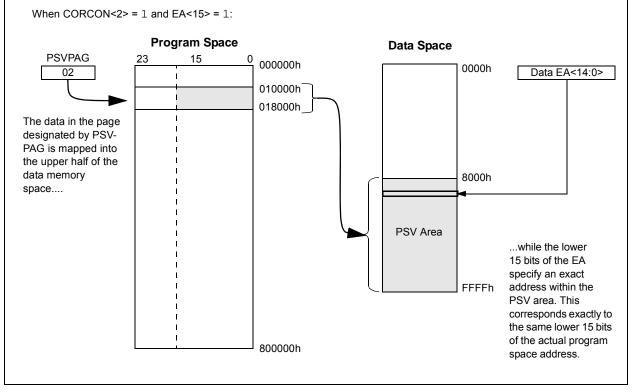

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit (MSb) of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

# FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                        | R/W-0 <sup>(1)</sup>                                                     | U-0                          | U-0                             | U-0                               | U-0                    | U-0                  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|---------------------------------|-----------------------------------|------------------------|----------------------|--|

| WR                    | WREN                                                                                                                                                                                                                                                                                                                                        | WRERR                                                                    | —                            | _                               |                                   |                        |                      |  |

| bit 15                |                                                                                                                                                                                                                                                                                                                                             |                                                                          |                              |                                 |                                   |                        | bit                  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                        | U-0                                                                      | U-0                          | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> |  |

| —                     | ERASE                                                                                                                                                                                                                                                                                                                                       | —                                                                        | _                            | NVMOP3 <sup>(2)</sup>           | NVMOP2 <sup>(2)</sup>             | NVMOP1 <sup>(2)</sup>  | NVMOP0(2             |  |

| bit 7                 |                                                                                                                                                                                                                                                                                                                                             |                                                                          |                              |                                 |                                   |                        | bit                  |  |

| Legend:               |                                                                                                                                                                                                                                                                                                                                             | SO = Set Only                                                            | y bit                        |                                 |                                   |                        |                      |  |

| R = Readable          | e bit                                                                                                                                                                                                                                                                                                                                       | W = Writable                                                             | bit                          | U = Unimplem                    | nented bit, read                  | l as '0'               |                      |  |

| -n = Value at         | POR                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                                         |                              | '0' = Bit is clea               | ared                              | x = Bit is unkr        | iown                 |  |

| bit 15                | cleared b                                                                                                                                                                                                                                                                                                                                   | a Flash memor<br>by hardware one<br>or erase opera                       | ce the operation             | n is complete.                  | n. The operatio                   | n is self-timed        | and the bit          |  |

| bit 14                |                                                                                                                                                                                                                                                                                                                                             | lash program/e                                                           |                              |                                 |                                   |                        |                      |  |

| bit 13                | <ul> <li>0 = Inhibit Flash program/erase operations</li> <li>WRERR: Write Sequence Error Flag bit<sup>(1)</sup></li> <li>1 = An improper program or erase sequence attempt or termination has occurred (bit is se automatically on any set attempt of the WR bit)</li> <li>0 = The program or erase operation completed normally</li> </ul> |                                                                          |                              |                                 |                                   |                        |                      |  |

| bit 12-7              | Unimplemen                                                                                                                                                                                                                                                                                                                                  | ted: Read as '                                                           | )'                           |                                 |                                   |                        |                      |  |

| bit 6                 | ERASE: Eras                                                                                                                                                                                                                                                                                                                                 | se/Program Ena                                                           | able bit <sup>(1)</sup>      |                                 |                                   |                        |                      |  |

|                       |                                                                                                                                                                                                                                                                                                                                             | the erase opera<br>the program op                                        |                              |                                 |                                   |                        | nd                   |  |

| bit 5-4               | Unimplemen                                                                                                                                                                                                                                                                                                                                  | ted: Read as '                                                           | )'                           |                                 |                                   |                        |                      |  |

| bit 3-0               |                                                                                                                                                                                                                                                                                                                                             | NVM Operati                                                              |                              |                                 |                                   |                        |                      |  |

|                       | 0011 = Memo<br>0010 = Memo                                                                                                                                                                                                                                                                                                                  | ory bulk erase o<br>ory word progra<br>ory page erase<br>ory row progran | m operation (E operation (ER | ERASE = 0) or<br>ASE = 1) or no | no operation (E<br>operation (ER/ | ERASE = 1)<br>ASE = 0) |                      |  |

| <b>2:</b> Al          | l other combina                                                                                                                                                                                                                                                                                                                             | nly be reset on I<br>itions of NVMO                                      | P<3:0> are un                | •                               | ing specificatio                  | -                      |                      |  |

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

3: Available in ICSP<sup>™</sup> mode only. Refer to the device programming specification.

| U-0          | U-0                                                                                                    | R/W-0                                  | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-------------------|-----------------|-----------------|--------|--|--|--|--|--|

| —            | —                                                                                                      | PMPIF                                  | OC8IF            | OC7IF             | OC6IF           | OC5IF           | IC6IF  |  |  |  |  |  |

| bit 15       |                                                                                                        |                                        |                  |                   |                 |                 | bit 8  |  |  |  |  |  |

|              |                                                                                                        |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                                  | R/W-0                                  | U-0              | U-0               | U-0             | R/W-0           | R/W-0  |  |  |  |  |  |

| IC5IF        | IC4IF                                                                                                  | IC3IF                                  |                  | _                 |                 | SPI2IF          | SPF2IF |  |  |  |  |  |

| bit 7        |                                                                                                        |                                        |                  |                   |                 |                 | bit (  |  |  |  |  |  |

| Legend:      |                                                                                                        |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                                                                                 | W = Writable                           | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value a | t POR                                                                                                  | '1' = Bit is set                       |                  | '0' = Bit is clea |                 | x = Bit is unkr | nown   |  |  |  |  |  |

|              |                                                                                                        |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 15-14    | Unimplemen                                                                                             | ted: Read as '                         | 0'               |                   |                 |                 |        |  |  |  |  |  |

| bit 13       | PMPIF: Para                                                                                            | llel Master Port                       | Interrupt Flag   | Status bit        |                 |                 |        |  |  |  |  |  |

|              |                                                                                                        | request has oc<br>request has no       |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 12       |                                                                                                        | •                                      |                  | ipt Flag Status I | oit             |                 |        |  |  |  |  |  |

|              | •                                                                                                      | request has oc                         |                  | ipt ing change    |                 |                 |        |  |  |  |  |  |

|              | 0 = Interrupt                                                                                          | request has no                         | toccurred        |                   |                 |                 |        |  |  |  |  |  |

| bit 11       | OC7IF: Output Compare Channel 7 Interrupt Flag Status bit                                              |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt request has occurred                                                                     |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| oit 10       | 0 = Interrupt request has not occurred                                                                 |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | <b>OC6IF:</b> Output Compare Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              |                                                                                                        | request has no                         |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 9        | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit                                              |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt request has occurred                                                                     |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| L:1 0        |                                                                                                        | 0 = Interrupt request has not occurred |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 8        | IC6IF: Input Capture Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred         |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | 0 = Interrupt request has not occurred                                                                 |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 7        | IC5IF: Input (                                                                                         | Capture Chann                          | el 5 Interrupt F | lag Status bit    |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt request has occurred                                                                     |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | •                                                                                                      | request has no                         |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 6        | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                               |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | <ol> <li>Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>         |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 5        |                                                                                                        | Capture Chann                          |                  | lag Status bit    |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt request has occurred                                                                     |                                        |                  |                   |                 |                 |        |  |  |  |  |  |

|              | -                                                                                                      | request has no                         |                  |                   |                 |                 |        |  |  |  |  |  |

| oit 4-2      | -                                                                                                      | ted: Read as '                         |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 1        |                                                                                                        | Event Interrup                         | -                | It                |                 |                 |        |  |  |  |  |  |

|              |                                                                                                        | request has oc<br>request has no       |                  |                   |                 |                 |        |  |  |  |  |  |

| bit 0        | -                                                                                                      | 2 Fault Interrup                       |                  | it                |                 |                 |        |  |  |  |  |  |

|              |                                                                                                        | request has oc                         | -                |                   |                 |                 |        |  |  |  |  |  |

|              |                                                                                                        | request has no                         |                  |                   |                 |                 |        |  |  |  |  |  |

# REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

### REGISTER 7-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0           | U-0                                                                                          | R/W-0                                                      | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| _             | —                                                                                            | PMPIE                                                      | OC8IE           | OC7IE             | OC6IE            | OC5IE           | IC6IE  |  |  |  |  |

| bit 15        |                                                                                              |                                                            |                 | •                 |                  |                 | bit 8  |  |  |  |  |

| R/W-0         | R/W-0                                                                                        | R/W-0                                                      | U-0             | U-0               | U-0              | R/W-0           | R/W-0  |  |  |  |  |

| IC5IE         | IC4IE                                                                                        | IC3IE                                                      | 0-0             | 0-0               | 0-0              | SPI2IE          | SPF2IE |  |  |  |  |

| bit 7         | IC4IE                                                                                        | ICJIE                                                      |                 |                   | _                | JF121L          | bit (  |  |  |  |  |

|               |                                                                                              |                                                            |                 |                   |                  |                 |        |  |  |  |  |

| Legend:       |                                                                                              |                                                            |                 |                   |                  |                 |        |  |  |  |  |

| R = Readable  |                                                                                              | W = Writable                                               | bit             | •                 | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set                                           |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |  |

| bit 15-14     | Unimpleme                                                                                    | ented: Read as '                                           | )'              |                   |                  |                 |        |  |  |  |  |

| bit 13        | PMPIE: Par                                                                                   | allel Master Port                                          | Interrupt Enal  | ole bit           |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enabled<br>t request not ena                     |                 |                   |                  |                 |        |  |  |  |  |

| bit 12        | OC8IE: Out                                                                                   | put Compare Ch                                             | annel 8 Interru | upt Enable bit    |                  |                 |        |  |  |  |  |

|               | <b>OC8IE:</b> Output Compare Channel 8 Interrupt Enable bit<br>1 = Interrupt request enabled |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt request not enabled                                                            |                                                            |                 |                   |                  |                 |        |  |  |  |  |

| bit 11        | OC7IE: Output Compare Channel 7 Interrupt Enable bit                                         |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enabled<br>t request not ena                     |                 |                   |                  |                 |        |  |  |  |  |

| bit 10        | OC6IE: Output Compare Channel 6 Interrupt Enable bit                                         |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enabled<br>t request not ena                     |                 |                   |                  |                 |        |  |  |  |  |

| bit 9         | OC5IE: Out                                                                                   | put Compare Ch                                             | annel 5 Interru | upt Enable bit    |                  |                 |        |  |  |  |  |

|               | •                                                                                            | t request enabled<br>t request not ena                     |                 |                   |                  |                 |        |  |  |  |  |

| bit 8         | IC6IE: Input Capture Channel 6 Interrupt Enable bit                                          |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enable<br>t request not ena                      |                 |                   |                  |                 |        |  |  |  |  |

| bit 7         | IC5IE: Input Capture Channel 5 Interrupt Enable bit                                          |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enabled<br>t request not ena                     |                 |                   |                  |                 |        |  |  |  |  |

| bit 6         | IC4IE: Input Capture Channel 4 Interrupt Enable bit                                          |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enable<br>t request not ena                      |                 |                   |                  |                 |        |  |  |  |  |

| bit 5         | IC3IE: Input Capture Channel 3 Interrupt Enable bit                                          |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt request enabled                                                                |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt                                                                                | t request not ena                                          | bled            |                   |                  |                 |        |  |  |  |  |

| bit 4-2       | Unimpleme                                                                                    | nted: Read as '                                            | )'              |                   |                  |                 |        |  |  |  |  |

| bit 1         |                                                                                              | 2 Event Interrup                                           |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              | t request enable                                           |                 |                   |                  |                 |        |  |  |  |  |

|               |                                                                                              |                                                            |                 |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                            | t request not ena                                          |                 |                   |                  |                 |        |  |  |  |  |

| bit 0         | SPF2IE: SP                                                                                   | t request not ena<br>l2 Fault Interrup<br>t request enable | Enable bit      |                   |                  |                 |        |  |  |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                                      | R/W-0           | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|--|--|--|

| _            | CNIP2                                                                                                                                   | CNIP1                                                      | CNIP0           |                   | CMIP2            | CMIP1           | CMIP0    |  |  |  |  |  |  |

| bit 15       |                                                                                                                                         |                                                            |                 |                   |                  |                 | bit 8    |  |  |  |  |  |  |

|              | <b>- - - - - - - - - -</b>                                                                                                              |                                                            |                 |                   | <b>5</b> 444 4   | 5444.6          | 5444.0   |  |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                                      | R/W-0           | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |  |

|              | MI2C1IP2                                                                                                                                | MI2C1IP1                                                   | MI2C1IP0        |                   | SI2C1IP2         | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |  |

| bit 7        |                                                                                                                                         |                                                            |                 |                   |                  |                 | bit (    |  |  |  |  |  |  |

| Legend:      |                                                                                                                                         |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                  | W = Writable                                               | bit             | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                   | '1' = Bit is set                                           |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |  |  |

| bit 15       | Unimplemen                                                                                                                              | ted: Read as '                                             | 0'              |                   |                  |                 |          |  |  |  |  |  |  |

| bit 14-12    | -                                                                                                                                       |                                                            |                 | rupt Priority bit | S                |                 |          |  |  |  |  |  |  |

|              | <b>CNIP&lt;2:0&gt;:</b> Input Change Notification Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       | •                                                          |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              |                                                                                                                                         |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                      |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              |                                                                                                                                         | pt source is dis                                           | abled           |                   |                  |                 |          |  |  |  |  |  |  |

| bit 11       | Unimplemen                                                                                                                              | ted: Read as '                                             | 0'              |                   |                  |                 |          |  |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits                                                                                           |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                              |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                     |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

| bit 7        |                                                                                                                                         | ted: Read as '                                             |                 |                   |                  |                 |          |  |  |  |  |  |  |

| bit 6-4      | MI2C1IP<2:0>: Master I2C1 Event Interrupt Priority bits                                                                                 |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                              |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                      |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              |                                                                                                                                         | pt source is dis                                           | abled           |                   |                  |                 |          |  |  |  |  |  |  |

| bit 3        | Unimplemen                                                                                                                              | ted: Read as '                                             | 0'              |                   |                  |                 |          |  |  |  |  |  |  |

| bit 2-0      | SI2C1IP<2:0                                                                                                                             | >: Slave I2C1 E                                            | Event Interrupt | Priority bits     |                  |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                                                                                                           | 111 = Interrupt is priority 7 (highest priority interrupt) |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                                                                                       |                                                            |                 |                   |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interru                                                                                                                           | pt is priority 1                                           |                 |                   |                  |                 |          |  |  |  |  |  |  |

# 9.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 10. "Power-Saving Features" (DS39698).

The PIC24FJ256GA110 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0** "Oscillator Configuration".

### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 9-1. Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

Additional power reductions can be achieved by disabling the on-chip voltage regulator whenever Sleep mode is invoked. This is done by clearing the PMSLP bit (RCON<8>). Disabling the regulator adds an additional delay of about 190  $\mu$ s to the device wake-up time. It is recommended that applications not using the voltage regulator leave the PMSLP bit set. For additional details on the regulator and Sleep mode, see **Section 25.2.5 "Voltage Regulator Standby Mode"**.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #0 | ; ] | Put | the | device | into | SLEEP  | mode |

|--------|----|-----|-----|-----|--------|------|--------|------|

| PWRSAV | #1 | ; ] | Put | the | device | into | IDLE r | mode |

NOTES:

# 14.0 OUTPUT COMPARE WITH DEDICATED TIMER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 35. "Output Compare with Dedicated Timer" (DS39723)

Devices in the PIC24FJ256GA110 family all feature 9 independent enhanced output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the enhanced output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 30 user-selectable trigger/sync sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

# 14.1 General Operating Modes

### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the enhanced output compare module operates in a free-running mode. The internal, 16-bit counter, OCxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs. In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-running mode is selected by default, or any time that the SYNCSEL bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSEL bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSEL bits determine the sync/trigger source.

# 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-Bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, modules 1 and 2 are paired, as are modules 3 and 4, and so on.) The odd-numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even module (OCy) provides the Most Significant 16 bits. Wraparounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bits (OCxCON2<8>) for both modules.

bits

# EQUATION 14-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

Maximum PWM Resolution (bits) =  $\frac{\log_{10} \left( \frac{FCY}{FPWM \bullet (Timer Prescale Value)} \right)}{1 + \frac{FCY}{FPWM \bullet (Timer Prescale Value)}}$

$\log_{10}(2)$

**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

# EXAMPLE 14-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

| 1. | Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where FOSC = 8 MHz with PLL                |

|----|---------------------------------------------------------------------------------------------------------------------------|

|    | (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.                                                         |

|    | TCY = 2 * TOSC = 62.5  ns                                                                                                 |

|    | PWM Period = $1/PWM$ Frequency = $1/52.08$ kHz = $19.2 \mu s$                                                             |

|    | PWM Period = $(PR2 + 1) \bullet TCY \bullet (Timer2 Prescale Value)$                                                      |

|    | 19.2 $\mu$ s = (PR2 + 1) • 62.5 ns • 1                                                                                    |

|    | PR2 = 306                                                                                                                 |

| 2. | Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate: |

|    | PWM Resolution = $\log_{10}(FCY/FPWM)/\log_{10}2)$ bits                                                                   |

|    | $= (\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2) \text{ bits}$                                                 |

|    | = 8.3 bits                                                                                                                |

|    |                                                                                                                           |

| N  | ote 1: Based on Tcy = 2 * Tosc, Doze mode and PLL are disabled.                                                           |

# TABLE 14-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

# TABLE 14-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

# 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C<sup>TM</sup>)" (DS39702).

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- · Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications.

- Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

A block diagram of the module is shown in Figure 16-1.

# 16.1 Peripheral Remapping Options

The  $I^2C$  modules are tied to fixed pin assignments and cannot be reassigned to alternate pins using Peripheral Pin Select. To allow some flexibility with peripheral multiplexing, the I2C2 module in 100-pin devices can be reassigned to the alternate pins designated as ASCL2 and ASDA2 during device configuration.

Pin assignment is controlled by the I2C2SEL Configuration bit; programming this bit (= 0) multiplexes the module to the ASCL2 and ASDA2 pins.

# 16.2 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

| R/W-0        | U-0                                                       | R/W-0                               | R/W-1, HC                              | R/W-0                         | R/W-0                     | R/W-0             | R/W-0         |  |  |  |  |

|--------------|-----------------------------------------------------------|-------------------------------------|----------------------------------------|-------------------------------|---------------------------|-------------------|---------------|--|--|--|--|

| I2CEN        | _                                                         | I2CSIDL                             | SCLREL                                 | IPMIEN                        | A10M                      | DISSLW            | SMEN          |  |  |  |  |

| bit 15       |                                                           |                                     |                                        |                               |                           |                   | bit           |  |  |  |  |

| R/W-0        | R/W-0                                                     | R/W-0                               | R/W-0, HC                              | R/W-0, HC                     | R/W-0, HC                 | R/W-0, HC         | R/W-0, HC     |  |  |  |  |