Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 64-VQFN (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga106-e-mr |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- Communications: The PIC24FJ256GA110 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C<sup>™</sup> modules that support both Master and Slave modes of operation. Devices also have, through the Peripheral Pin Select (PPS) feature, four independent UARTs with built-in IrDA<sup>®</sup> encoder/decoders and three SPI modules.

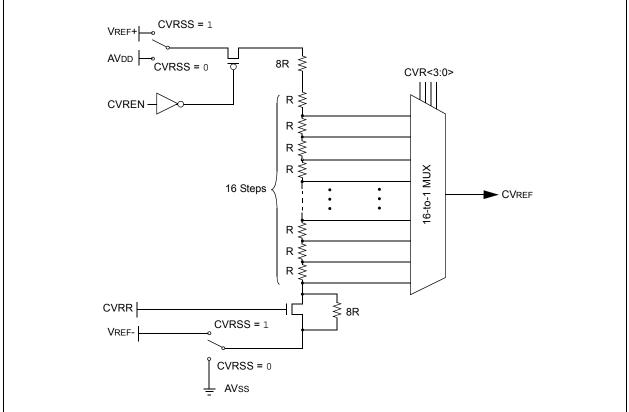

- Analog Features: All members of the PIC24FJ256GA110 family include a 10-bit A/D Converter module and a triple comparator module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256GA110 family include the brand new CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- **Parallel Master Port:** One of the general purpose I/O ports can be reconfigured for enhanced parallel data communications. In this mode, the port can be configured for both master and slave operations, and supports 8-bit transfers with up to 16 external address lines in Master modes.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up the timer resources and program memory space for the use of the core application.

#### 1.3 Details on Individual Family Members

Devices in the PIC24FJ256GA110 family are available in 64-pin, 80-pin and 100-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four ways:

- Flash program memory (64 Kbytes for PIC24FJ64GA1 devices, 128 Kbytes for PIC24FJ128GA1 devices, 192 Kbytes for PIC24FJ192GA1 devices and 256 Kbytes for PIC24FJ256GA1 devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices, 69 pins on 7 ports for 80-pin devices and 85 pins on 7 ports for 100-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (same as the number of available I/O pins for all devices).

- 4. Available remappable pins (31 pins on 64-pin devices, 42 pins on 80-pin devices and 46 pins on 100-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1.

A list of the pin features available on the PIC24FJ256GA110 family devices, sorted by function, is shown in Table 1-4. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

#### TABLE 4-12: PORTA REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7 <sup>(2)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4 <sup>(2)</sup> | Bit 3 <sup>(2)</sup> | Bit2 <sup>(2)</sup> | Bit 1 <sup>(2)</sup> | Bit 0 <sup>(2)</sup> | All<br>Resets |

|--------------|------|---------|---------|--------|--------|--------|---------|--------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|----------------------|----------------------|---------------|

| TRISA        | 02C0 | TRISA15 | TRISA14 | _      | _      | _      | TRISA10 | TRISA9 | _     | TRISA7               | TRISA6               | TRISA5               | TRISA4               | TRISA3               | TRISA2              | TRISA1               | TRISA0               | 36FF          |

| PORTA        | 02C2 | RA15    | RA14    | _      | —      | —      | RA10    | RA9    | _     | RA7                  | RA6                  | RA5                  | RA4                  | RA3                  | RA2                 | RA1                  | RA0                  | xxxx          |

| LATA         | 02C4 | LATA15  | LATA14  | —      | —      | —      | LATA10  | LATA9  |       | LATA7                | LATA6                | LATA5                | LATA4                | LATA3                | LATA2               | LATA1                | LATA0                | xxxx          |

| ODCA         | 02C6 | ODA15   | ODA14   | _      | _      | _      | ODA10   | ODA9   | _     | ODA7                 | ODA6                 | ODA5                 | ODA4                 | ODA3                 | ODA2                | ODA1                 | ODA0                 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: PORTA and all associated bits are unimplemented on 64-pin devices and read as '0'. Bits are available on 80-pin and 100-pin devices only, unless otherwise noted.

2: Bits are implemented on 100-pin devices only; otherwise, read as '0'.

#### TABLE 4-13: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13   | ODB12   | ODB11   | ODB10   | ODB9   | ODB8   | ODB7   | ODB6   | ODB5   | ODB4   | ODB3   | ODB2   | ODB1   | ODB0   | 0000          |

Legend: Reset values are shown in hexadecimal.

#### TABLE 4-14: PORTC REGISTER MAP

| File<br>Name | Addr | Bit 15                | Bit 14  | Bit 13  | Bit 12              | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 <sup>(1)</sup> | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(2)</sup> | Bit 0 | All<br>Resets |

|--------------|------|-----------------------|---------|---------|---------------------|--------|--------|-------|-------|-------|-------|-------|----------------------|----------------------|----------------------|----------------------|-------|---------------|

| TRISC        | 02D0 | TRISC15               | TRISC14 | TRISC13 | TRISC12             | _      | _      |       | -     | —     | —     | -     | TRISC4               | TRISC3               | TRISC2               | TRISC1               |       | F01E          |

| PORTC        | 02D2 | RC15 <sup>(3,4)</sup> | RC14    | RC13    | RC12 <sup>(3)</sup> |        |        | _     | —     | _     | -     | —     | RC4                  | RC3                  | RC2                  | RC1                  | —     | xxxx          |

| LATC         | 02D4 | LATC15                | LATC14  | LATC13  | LATC12              | —      | —      | —     | —     | —     | —     | —     | LATC4                | LATC3                | LATC2                | LATC1                | _     | xxxx          |

| ODCC         | 02D6 | ODC15                 | ODC14   | ODC13   | ODC12               | _      | _      | _     | _     | _     | _     | _     | ODC4                 | ODC3                 | ODC2                 | ODC1                 | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

**Note** 1: Bits are unimplemented in 64-pin and 80-pin devices; read as '0'.

2: Bits are unimplemented in 64-pin devices; read as '0'.

3: RC12 and RC15 are only available when the Primary Oscillator is disabled or when EC mode is selected (POSCMD<1:0> Configuration bits = 11 or 00); otherwise, read as '0'

4: RC15 is only available when POSCMD<1:0> Configuration bits = 11 or 00 and the OSCIOFN Configuration bit = 1.

#### TABLE 4-15: PORTD REGISTER MAP

| File<br>Name | Addr | Bit 15 <sup>(1)</sup> | Bit 14 <sup>(1)</sup> | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|-----------------------|-----------------------|-----------------------|-----------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD        | 02D8 | TRISD15               | TRISD14               | TRISD13               | TRISD12               | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD        | 02DA | RD15                  | RD14                  | RD13                  | RD12                  | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD         | 02DC | LATD15                | LATD14                | LATD13                | LATD12                | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD         | 02DE | ODD15                 | ODD14                 | ODD13                 | ODD12                 | ODD11   | ODD10   | ODD9   | ODD8   | ODD7   | ODD6   | ODD5   | ODD4   | ODD3   | ODD2   | ODD1   | ODD0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: Bits are unimplemented on 64-pin devices; read as '0'.

#### 5.6.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOP bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit, as shown in Example 5-7. An equivalent procedure in C, using the MPLAB C30 compiler and built-in hardware functions, is shown in Example 5-8.

#### EXAMPLE 5-7: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY (ASSEMBLY LANGUAGE CODE)

| ; Setup a p | pointer to data Program Memory       |                                                        |

|-------------|--------------------------------------|--------------------------------------------------------|

| MOV         | <pre>#tblpage(PROG_ADDR), W0</pre>   | ;                                                      |

| MOV         | W0, TBLPAG                           | ;Initialize PM Page Boundary SFR                       |

| MOV         | <pre>#tbloffset(PROG_ADDR), W0</pre> | ;Initialize a register with program memory address     |

| MOV         | #LOW_WORD, W2                        | ;                                                      |

| MOV         | #HIGH_BYTE, W3                       | i                                                      |

| TBLWTL      | W2, [W0]                             | ; Write PM low word into program latch                 |

| TBLWTH      | W3, [W0++]                           | ; Write PM high byte into program latch                |

| ; Setup NVN | MCON for programming one word t      | o data Program Memory                                  |

| MOV         | #0x4003, W0                          | i                                                      |

| MOV         | W0, NVMCON                           | ; Set NVMOP bits to 0011                               |

| DISI        | #5                                   | ; Disable interrupts while the KEY sequence is written |

| MOV         | #0x55, W0                            | ; Write the key sequence                               |

| MOV         | W0, NVMKEY                           |                                                        |

| MOV         | #0xAA, W0                            |                                                        |

| MOV         | W0, NVMKEY                           |                                                        |

| BSET        | NVMCON, #WR                          | ; Start the write cycle                                |

| NOP         |                                      | ; Insert two NOPs after the erase                      |

| NOP         |                                      | ; Command is asserted                                  |

#### EXAMPLE 5-8: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY (C LANGUAGE CODE)

```

// C example using MPLAB C30

unsigned int offset;

unsigned long progAddr = 0xXXXXXX;

// Address of word to program

unsigned int progDataL = 0xXXXX;

// Data to program lower word

unsigned char progDataH = 0xXX;

// Data to program upper byte

//Set up NVMCON for word programming

NVMCON = 0 \times 4003;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

// Initialize PM Page Boundary SFR

TBLPAG = progAddr>>16;

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write latches

// Write to address low word

__builtin_tblwtl(offset, progDataL);

__builtin_tblwth(offset, progDataH);

// Write to upper byte

asm("DISI #5");

// Block interrupts with priority < 7</pre>

// for next 5 instructions

__builtin_write_NVM();

// C30 function to perform unlock

// sequence and set WR

```

| R/W-0      | R/W-0                                             | U-0                                                                         | U-0                | U-0                  | U-0               | R/W-0            | R/W-0        |

|------------|---------------------------------------------------|-----------------------------------------------------------------------------|--------------------|----------------------|-------------------|------------------|--------------|

| TRAPR      | IOPUWR                                            | _                                                                           |                    | _                    | _                 | СМ               | PMSLP        |

| oit 15     |                                                   |                                                                             |                    |                      |                   |                  | bit          |

| R/W-0      | R/W-0                                             | R/W-0                                                                       | R/W-0              | R/W-0                | R/W-0             | R/W-1            | R/W-1        |

| EXTR       | SWR                                               | SWDTEN <sup>(2)</sup>                                                       | WDTO               | SLEEP                | IDLE              | BOR              | POR          |

| bit 7      | OWIX                                              | OWDIEN                                                                      | WDTO               | OLLLI                | IDLL              | BOIX             | bit          |

|            |                                                   |                                                                             |                    |                      |                   |                  | _            |

| Legend:    |                                                   |                                                                             |                    |                      |                   | (0)              |              |

| R = Read   |                                                   | W = Writable bi                                                             | it                 | •                    | ented bit, read   |                  |              |

| -n = Value | e at POR                                          | '1' = Bit is set                                                            |                    | '0' = Bit is clea    | ared              | x = Bit is unkr  | IOWN         |

| bit 15     | 1 = A Trap C                                      | o Reset Flag bit<br>onflict Reset has<br>onflict Reset has                  |                    |                      |                   |                  |              |

| bit 14     | 1 = An illega<br>Pointer c                        | egal Opcode or U<br>I opcode detectio<br>aused a Reset<br>I opcode or unini | n, an illegal a    | ddress mode or       | r uninitialized W | / register used  | as an Addre  |

| bit 13-10  | -                                                 | ted: Read as '0'                                                            |                    |                      |                   |                  |              |

| bit 9      | 1 = A Configu                                     | ation Word Mism<br>aration Word Mise<br>aration Word Mise                   | match Reset        | has occurred         | d                 |                  |              |

| bit 8      | 1 = Program                                       | gram Memory Po<br>memory bias volt<br>nemory bias volta                     | age remains        | powered during       |                   | regulator enters | s Standby mo |

| bit 7      | 1 = A Master                                      | nal Reset (MCLR<br>Clear (pin) Rese<br>Clear (pin) Rese                     | t has occurre      |                      |                   |                  |              |

| bit 6      | 1 <b>= A</b> reset                                | are Reset (Instruction has b instruction has n                              | een executed       |                      |                   |                  |              |

| bit 5      | <b>SWDTEN:</b> So<br>1 = WDT is e<br>0 = WDT is d |                                                                             | isable of WD       | T bit <sup>(2)</sup> |                   |                  |              |

| bit 4      | <b>WDTO:</b> Wate                                 | hdog Timer Time<br>e-out has occurre<br>e-out has not occ                   | ed                 |                      |                   |                  |              |

| bit 3      | SLEEP: Wak                                        | e From Sleep Fla<br>as been in Sleep<br>as not been in Sle                  | ag bit<br>mode     |                      |                   |                  |              |

| bit 2      | IDLE: Wake-<br>1 = Device ha                      | up From Idle Flag<br>as been in Idle m<br>as not been in Idl                | g bit<br>ode       |                      |                   |                  |              |

| bit 1      | <b>BOR:</b> Brown                                 | out Reset Flag b<br>out Reset has oc<br>out Reset has no                    | it<br>curred. Note | that BOR is also     | o set after a Po  | wer-on Reset.    |              |

| bit 0      | 1 = A Power-                                      | on Reset Flag bi<br>on Reset has occ<br>on Reset has no                     | curred             |                      |                   |                  |              |

| Note 1:    | All of the Reset<br>cause a device                |                                                                             | e set or cleare    | ed in software. S    | Setting one of th | ese bits in soft | ware does n  |

| 2:         | If the FWDTEN                                     | Configuration bit                                                           | is '1' (unprog     | rammed), the W       | VDT is always e   | enabled, regard  | dless of the |

### 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### REGISTER 7-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0          | R/W-0                                  | R/W-0                                                  | R/W-0                          | R/W-0            | R/W-0           | R/W-0             | U-0              |

|----------------|----------------------------------------|--------------------------------------------------------|--------------------------------|------------------|-----------------|-------------------|------------------|

| U2TXIE         | U2RXIE                                 | INT2IE <sup>(1)</sup>                                  | T5IE                           | T4IE             | OC4IE           | OC3IE             | _                |

| bit 15         |                                        |                                                        | L                              |                  |                 |                   | bit 8            |

| D44/0          | DAMO                                   |                                                        | DAMO                           | DAMA             | DAMO            | DAMA              | DAMA             |

| R/W-0          | R/W-0                                  | U-0                                                    | R/W-0                          | R/W-0            | R/W-0           | R/W-0             | R/W-0            |

| IC8IE<br>bit 7 | IC7IE                                  | —                                                      | INT1IE <sup>(1)</sup>          | CNIE             | CMIE            | MI2C1IE           | SI2C1IE<br>bit ( |

|                |                                        |                                                        |                                |                  |                 |                   | Dit t            |

| Legend:        |                                        |                                                        |                                |                  |                 |                   |                  |

| R = Readab     | le bit                                 | W = Writable                                           | bit                            | U = Unimpler     | mented bit, rea | d as '0'          |                  |

| -n = Value a   | t POR                                  | '1' = Bit is set                                       |                                | '0' = Bit is cle | ared            | x = Bit is unkr   | nown             |

| bit 15         | 1 = Interrupt                          | RT2 Transmitter<br>request enabled<br>request not ena  | , t                            | ole bit          |                 |                   |                  |

| bit 14         | <b>U2RXIE:</b> UAP<br>1 = Interrupt    | RT2 Receiver Ir<br>request enabled<br>request not ena  | nterrupt Enable                | e bit            |                 |                   |                  |

| bit 13         | INT2IE: Exten<br>1 = Interrupt         | rnal Interrupt 2<br>request enabled<br>request not ena | Enable bit <sup>(1)</sup><br>1 |                  |                 |                   |                  |

| bit 12         | <b>T5IE:</b> Timer5<br>1 = Interrupt   | Interrupt Enable<br>request enable<br>request not ena  | e bit<br>1                     |                  |                 |                   |                  |

| bit 11         | <b>T4IE:</b> Timer4<br>1 = Interrupt   | Interrupt Enable<br>request enable<br>request not ena  | e bit<br>1                     |                  |                 |                   |                  |

| bit 10         | <b>OC4IE:</b> Outp                     | ut Compare Ch<br>request enabled<br>request not ena    | annel 4 Interru<br>ว           | pt Enable bit    |                 |                   |                  |

| bit 9          | 1 = Interrupt                          | ut Compare Ch<br>request enabled<br>request not ena    | t                              | pt Enable bit    |                 |                   |                  |

| bit 8          |                                        | ted: Read as '                                         |                                |                  |                 |                   |                  |

| bit 7          | 1 = Interrupt                          | Capture Channe<br>request enablee<br>request not ena   | t t                            | nable bit        |                 |                   |                  |

| bit 6          | <b>IC7IE:</b> Input (<br>1 = Interrupt | Capture Channe<br>request enablee<br>request not ena   | el 7 Interrupt E<br>ป          | nable bit        |                 |                   |                  |

| bit 5          |                                        | ted: Read as '                                         |                                |                  |                 |                   |                  |

| bit 4          | 1 = Interrupt                          | rnal Interrupt 1<br>request enableo<br>request not ena | t                              |                  |                 |                   |                  |

| bit 3          | 1 = Interrupt                          | Change Notifica<br>request enableo<br>request not ena  | t                              | Enable bit       |                 |                   |                  |

| bit 2          | <b>CMIE:</b> Comp<br>1 = Interrupt     | arator Interrupt<br>request enabled<br>request not ena | Enable bit<br>d                |                  |                 |                   |                  |

| Note 1: If     | an external inte                       | errupt is enabled                                      | I, the interrupt               | input must also  | o be configured | d to an available | RPn or RPI       |

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. See **Section 10.4 "Peripheral Pin Select**" for more information.

| U-0                          | U-0                              | U-0                                  | U-0              | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|----------------------------------|--------------------------------------|------------------|------------------|------------------|-----------------|---------|

| —                            | —                                | —                                    | —                | —                | INT4IP2          | INT4IP1         | INT4IP0 |

| bit 15                       |                                  |                                      |                  |                  |                  |                 | bit 8   |

|                              |                                  |                                      |                  |                  |                  |                 |         |

| U-0                          | R/W-1                            | R/W-0                                | R/W-0            | U-0              | U-0              | U-0             | U-0     |

| —                            | INT3IP2                          | INT3IP1                              | INT3IP0          |                  | <u> </u>         |                 | _       |

| bit 7                        |                                  |                                      |                  |                  |                  |                 | bit (   |

| Logondi                      |                                  |                                      |                  |                  |                  |                 |         |

| <b>Legend:</b><br>R = Readab | le bit                           | W = Writable                         | hit              | U = Unimplei     | mented bit, read | 1 as '0'        |         |

| -n = Value a                 |                                  | '1' = Bit is set                     |                  | '0' = Bit is cle |                  | x = Bit is unkr | NOWD    |

|                              |                                  |                                      |                  |                  |                  |                 |         |

| bit 15-11                    | Unimplemen                       | ted: Read as '                       | )'               |                  |                  |                 |         |

| bit 10-8                     | INT4IP<2:0>:                     | External Interr                      | upt 4 Priority b | oits             |                  |                 |         |

|                              | 111 = Interrup                   | ot is priority 7 (I                  | nighest priority | interrupt)       |                  |                 |         |

|                              | •                                |                                      |                  |                  |                  |                 |         |

|                              | •                                |                                      |                  |                  |                  |                 |         |

|                              | 001 = Interrup                   | ot is priority 1                     |                  |                  |                  |                 |         |

|                              |                                  | ot source is dis                     | abled            |                  |                  |                 |         |

| oit 7                        | Unimplemen                       | ted: Read as '                       | )'               |                  |                  |                 |         |

| bit 6-4                      | INT3IP<2:0>:                     | External Interr                      | upt 3 Priority b | oits             |                  |                 |         |

|                              | 111 = Interrup                   | ot is priority 7 (I                  | nighest priority | interrupt)       |                  |                 |         |

|                              | •                                |                                      |                  |                  |                  |                 |         |

|                              | •                                |                                      |                  |                  |                  |                 |         |

|                              |                                  |                                      |                  |                  |                  |                 |         |

|                              | 001 = Interru                    | ot is priority 1                     |                  |                  |                  |                 |         |

|                              | 001 = Interrup<br>000 = Interrup | ot is priority 1<br>ot source is dis | abled            |                  |                  |                 |         |

#### REGISTER 7-30: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

| R/W-0<br>DOZE2<br>U-0<br>                                                                                               | R/W-0<br>DOZE1<br>U-0<br>W = Writable I                                                                                                                                                                                                                                                                                        | R/W-0<br>DOZE0<br>U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0<br>DOZEN <sup>(1)</sup><br>U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0<br>RCDIV2<br>U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0<br>RCDIV1<br>U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-1<br>RCDIV0<br>bit 8<br>U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-0<br>—                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e bit                                                                                                                   | -                                                                                                                                                                                                                                                                                                                              | U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| e bit                                                                                                                   | -                                                                                                                                                                                                                                                                                                                              | U-0<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| POP                                                                                                                     | •••••••••••••••••••••••••••••••••••••••                                                                                                                                                                                                                                                                                        | oit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U = Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ION                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |