Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga106-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.2 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- Communications: The PIC24FJ256GA110 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C™ modules that support both Master and Slave modes of operation. Devices also have, through the Peripheral Pin Select (PPS) feature, four independent UARTs with built-in IrDA<sup>®</sup> encoder/decoders and three SPI modules.

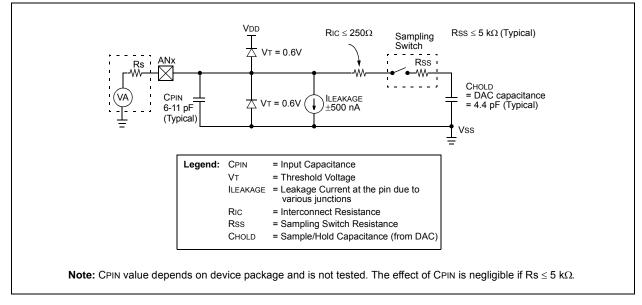

- Analog Features: All members of the PIC24FJ256GA110 family include a 10-bit A/D Converter module and a triple comparator module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

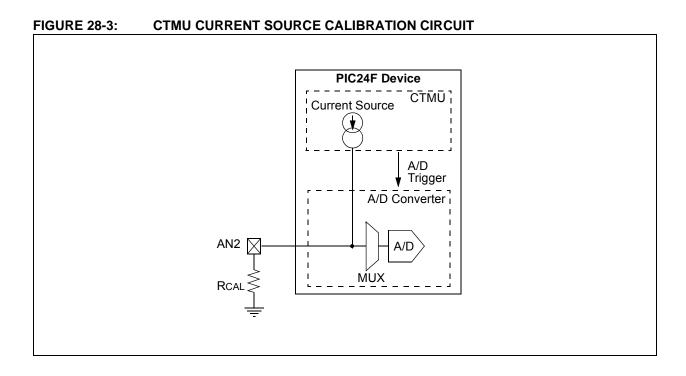

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256GA110 family include the brand new CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- **Parallel Master Port:** One of the general purpose I/O ports can be reconfigured for enhanced parallel data communications. In this mode, the port can be configured for both master and slave operations, and supports 8-bit transfers with up to 16 external address lines in Master modes.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up the timer resources and program memory space for the use of the core application.

### 1.3 Details on Individual Family Members

Devices in the PIC24FJ256GA110 family are available in 64-pin, 80-pin and 100-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four ways:

- Flash program memory (64 Kbytes for PIC24FJ64GA1 devices, 128 Kbytes for PIC24FJ128GA1 devices, 192 Kbytes for PIC24FJ192GA1 devices and 256 Kbytes for PIC24FJ256GA1 devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices, 69 pins on 7 ports for 80-pin devices and 85 pins on 7 ports for 100-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (same as the number of available I/O pins for all devices).

- 4. Available remappable pins (31 pins on 64-pin devices, 42 pins on 80-pin devices and 46 pins on 100-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1.

A list of the pin features available on the PIC24FJ256GA110 family devices, sorted by function, is shown in Table 1-4. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ256GA110 FAMILY: 80-PIN DEVICES

| Features                                                               | PIC24FJ64GA108 | PIC24FJ128GA108                                              | PIC24FJ192GA108      | PIC24FJ256GA108 |

|------------------------------------------------------------------------|----------------|--------------------------------------------------------------|----------------------|-----------------|

| Operating Frequency                                                    |                | DC – 3                                                       | 32 MHz               |                 |

| Program Memory (bytes)                                                 | 64K            | 128K                                                         | 192K                 | 256K            |

| Program Memory (instructions)                                          | 22,016         | 44,032                                                       | 67,072               | 87,552          |

| Data Memory (bytes)                                                    |                | 16,                                                          | 384                  |                 |

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                | 66 (                                                         | 62/4)                |                 |

| I/O Ports                                                              |                | Ports A, B,                                                  | C, D, E, F, G        |                 |

| Total I/O Pins                                                         |                | 6                                                            | 9                    |                 |

| Remappable Pins                                                        |                | 42 (31 I/O, 1                                                | 11 input only)       |                 |

| Timers:<br>Total Number (16-bit)<br>32-Bit (from paired 16-bit timers) |                |                                                              | (1)                  |                 |

| Input Capture Channels                                                 |                | 9                                                            | (1)                  |                 |

| Output Compare/PWM<br>Channels                                         |                | 9                                                            | (1)                  |                 |

| Input Change Notification<br>Interrupt                                 |                | 6                                                            | 9                    |                 |

| Serial Communications:                                                 |                |                                                              |                      |                 |

| UART                                                                   |                | -                                                            | (1)                  |                 |

| SPI (3-wire/4-wire)                                                    |                | 3                                                            | (1)                  |                 |

| l <sup>2</sup> C™                                                      |                |                                                              | 3                    |                 |

| Parallel Communications<br>(PMP/PSP)                                   |                | Y                                                            | es                   |                 |

| JTAG Boundary Scan                                                     |                | Y                                                            | es                   |                 |

| 10-Bit Analog-to-Digital Module<br>(input channels)                    |                | 1                                                            | 6                    |                 |

| Analog Comparators                                                     |                |                                                              | 3                    |                 |

| CTMU Interface                                                         |                | Y                                                            | es                   |                 |

| Resets (and delays)                                                    |                | OR, RESET Instructior<br>truction, Hardware Tra<br>(PWRT, OS |                      |                 |

| Instruction Set                                                        | 76 Bas         | e Instructions, Multiple                                     | e Addressing Mode Va | ariations       |

| Packages                                                               |                | 80-Pir                                                       | TQFP                 |                 |

**Note 1:** Peripherals are accessible through remappable pins.

| TABLE 1-3: D | DEVICE FEATURES FOR THE PIC24FJ256GA110 FAMILY: 100-PIN DEVICES |

|--------------|-----------------------------------------------------------------|

|--------------|-----------------------------------------------------------------|

| Features                                            | PIC24FJ64GA110 | PIC24FJ128GA110                                               | PIC24FJ192GA110      | PIC24FJ256GA110 |

|-----------------------------------------------------|----------------|---------------------------------------------------------------|----------------------|-----------------|

| Operating Frequency                                 |                | DC – 3                                                        | 32 MHz               | •               |

| Program Memory (bytes)                              | 64K            | 128K                                                          | 192K                 | 256K            |

| Program Memory (instructions)                       | 22,016         | 44,032                                                        | 67,072               | 87,552          |

| Data Memory (bytes)                                 |                | 16,                                                           | 384                  |                 |

| Interrupt Sources<br>(soft vectors/NMI traps)       |                | 66 (                                                          | 62/4)                |                 |

| I/O Ports                                           |                | Ports A, B,                                                   | C, D, E, F, G        |                 |

| Total I/O Pins                                      |                | 8                                                             | 35                   |                 |

| Remappable Pins                                     |                | 46 (32 I/O, 1                                                 | 14 input only)       |                 |

| Timers:                                             |                |                                                               |                      |                 |

| Total Number (16-bit)                               |                | 5                                                             | (1)                  |                 |

| 32-Bit (from paired 16-bit timers)                  |                |                                                               | 2                    |                 |

| Input Capture Channels                              |                | 9                                                             | (1)                  |                 |

| Output Compare/PWM<br>Channels                      |                | 9                                                             | (1)                  |                 |

| Input Change Notification<br>Interrupt              |                | 8                                                             | 35                   |                 |

| Serial Communications:                              |                |                                                               |                      |                 |

| UART                                                |                | 4                                                             | (1)                  |                 |

| SPI (3-wire/4-wire)                                 |                | 3                                                             | (1)                  |                 |

| I <sup>2</sup> C™                                   |                |                                                               | 3                    |                 |

| Parallel Communications<br>(PMP/PSP)                |                | Y                                                             | es                   |                 |

| JTAG Boundary Scan                                  |                | Y                                                             | es                   |                 |

| 10-Bit Analog-to-Digital Module<br>(input channels) |                | 1                                                             | 6                    |                 |

| Analog Comparators                                  |                | :                                                             | 3                    |                 |

| CTMU Interface                                      |                | Y                                                             | es                   |                 |

| Resets (and delays)                                 |                | OR, RESET Instructior<br>struction, Hardware Tra<br>(PWRT, OS |                      |                 |

| Instruction Set                                     | 76 Bas         | e Instructions, Multiple                                      | e Addressing Mode Va | ariations       |

| Packages                                            |                | 100-Pi                                                        | n TQFP               |                 |

**Note 1:** Peripherals are accessible through remappable pins.

### TABLE 4-6: TIMER REGISTER MAP

| DS39905E-pag |  |

|--------------|--|

| e 42         |  |

|              |  |

| File Name | Addr | Bit 15 | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8        | Bit 7        | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|------------------------------------------------------------|--------|--------|--------|--------|-------------|--------------|--------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1      | 0100 |        |                                                            |        |        |        |        |             | Timer1       | Register     |              |        |        |       |       |       |       | 0000          |

| PR1       | 0102 |        |                                                            |        |        |        |        |             | Timer1 Peri  | iod Register | r            |        |        |       |       |       |       | FFFF          |

| T1CON     | 0104 | TON    | —                                                          | TSIDL  | _      | _      | _      | —           | _            | _            | TGATE        | TCKPS1 | TCKPS0 |       | TSYNC | TCS   |       | 0000          |

| TMR2      | 0106 |        | Timer2 Register                                            |        |        |        |        |             |              |              |              |        |        |       | 0000  |       |       |               |

| TMR3HLD   | 0108 |        | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |             |              |              |              |        |        |       | 0000  |       |       |               |

| TMR3      | 010A |        |                                                            |        |        |        |        |             | Timer3       | Register     |              |        |        |       |       |       |       | 0000          |

| PR2       | 010C |        |                                                            |        |        |        |        |             | Timer2 Peri  | iod Register | r            |        |        |       |       |       |       | FFFF          |

| PR3       | 010E |        |                                                            |        |        |        |        |             | Timer3 Peri  | iod Register | r            |        |        |       |       |       |       | FFFF          |

| T2CON     | 0110 | TON    | _                                                          | TSIDL  | _      | _      | _      | _           | _            | _            | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON     | 0112 | TON    | _                                                          | TSIDL  | _      | _      | _      | _           | _            | _            | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4      | 0114 |        |                                                            |        |        |        |        |             | Timer4       | Register     |              |        |        |       |       |       |       | 0000          |

| TMR5HLD   | 0116 |        |                                                            |        |        |        | Tim    | ner5 Holdin | g Register ( | for 32-bit o | perations or | nly)   |        |       |       |       |       | 0000          |

| TMR5      | 0118 |        |                                                            |        |        |        |        |             | Timer5       | Register     |              |        |        |       |       |       |       | 0000          |

| PR4       | 011A |        |                                                            |        |        |        |        |             | Timer4 Peri  | iod Register | r            |        |        |       |       |       |       | FFFF          |

| PR5       | 011C |        |                                                            |        |        |        |        |             | Timer5 Peri  | iod Register | r            |        |        |       |       |       |       | FFFF          |

| T4CON     | 011E | TON    | _                                                          | TSIDL  | —      | —      | —      | _           | _            | _            | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T5CON     | 0120 | TON    |                                                            | TSIDL  | _      | _      | _      | _           | _            |              | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | U-0            | R/W-0                            | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0  |

|--------------|----------------|----------------------------------|------------------|--------------------|-----------------|-----------------|--------|

| —            | —              | PMPIF                            | OC8IF            | OC7IF              | OC6IF           | OC5IF           | IC6IF  |

| bit 15       |                |                                  |                  |                    |                 |                 | bit 8  |

|              |                |                                  |                  |                    |                 |                 |        |

| R/W-0        | R/W-0          | R/W-0                            | U-0              | U-0                | U-0             | R/W-0           | R/W-0  |

| IC5IF        | IC4IF          | IC3IF                            |                  | _                  |                 | SPI2IF          | SPF2IF |

| bit 7        |                |                                  |                  |                    |                 |                 | bit (  |

| Legend:      |                |                                  |                  |                    |                 |                 |        |

| R = Readab   | le bit         | W = Writable                     | bit              | U = Unimplen       | nented bit, rea | d as '0'        |        |

| -n = Value a | t POR          | '1' = Bit is set                 |                  | '0' = Bit is clea  |                 | x = Bit is unkr | nown   |

|              |                |                                  |                  |                    |                 |                 |        |

| bit 15-14    | Unimplemen     | ted: Read as '                   | 0'               |                    |                 |                 |        |

| bit 13       | PMPIF: Para    | llel Master Port                 | Interrupt Flag   | Status bit         |                 |                 |        |

|              |                | request has oc<br>request has no |                  |                    |                 |                 |        |

| bit 12       |                | •                                |                  | ipt Flag Status I  | oit             |                 |        |

|              | •              | request has oc                   |                  | ipt ing change     |                 |                 |        |

|              | 0 = Interrupt  | request has no                   | toccurred        |                    |                 |                 |        |

| bit 11       | -              | -                                |                  | ipt Flag Status I  | oit             |                 |        |

|              | •              | request has oc                   |                  |                    |                 |                 |        |

| oit 10       | •              | request has no<br>ut Compare Ch  |                  | ıpt Flag Status I  | nit             |                 |        |

|              | -              | request has oc                   |                  | ipt i lag Status i | Jit             |                 |        |

|              |                | request has no                   |                  |                    |                 |                 |        |

| bit 9        | OC5IF: Outp    | ut Compare Ch                    | annel 5 Interru  | ipt Flag Status I  | oit             |                 |        |

|              |                | request has oc                   |                  |                    |                 |                 |        |

| L:1 0        |                | request has no                   |                  | les Ctatus bit     |                 |                 |        |

| bit 8        | -              | Capture Chann<br>request has oc  |                  | lag Status bit     |                 |                 |        |

|              |                | request has no                   |                  |                    |                 |                 |        |

| bit 7        | IC5IF: Input ( | Capture Chann                    | el 5 Interrupt F | lag Status bit     |                 |                 |        |

|              |                | request has oc                   |                  |                    |                 |                 |        |

|              | •              | request has no                   |                  |                    |                 |                 |        |

| bit 6        | -              | Capture Chann                    | -                | lag Status bit     |                 |                 |        |

|              |                | request has oc<br>request has no |                  |                    |                 |                 |        |

| bit 5        |                | Capture Chann                    |                  | lag Status bit     |                 |                 |        |

|              | -              | request has oc                   | -                | •                  |                 |                 |        |

|              | -              | request has no                   |                  |                    |                 |                 |        |

| oit 4-2      | -              | ted: Read as '                   |                  |                    |                 |                 |        |

| bit 1        |                | Event Interrup                   | -                | It                 |                 |                 |        |

|              |                | request has oc<br>request has no |                  |                    |                 |                 |        |

| bit 0        | -              | 2 Fault Interrup                 |                  | it                 |                 |                 |        |

|              |                | request has oc                   | -                |                    |                 |                 |        |

|              |                | request has no                   |                  |                    |                 |                 |        |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |             |                               |               |                   |                  |                 |       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| bit 15       bit         U-0       U-0       U-0       R/W-0       R/W-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0          | U-0         | R/W-0                         | U-0           | U-0               | U-0              | U-0             | R/W-0 |  |  |  |  |

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       U-0         -       -       -       CRCIE       U2ERIE       U1ERIE       -         bit 7       bit       bit       bit       Bit       U=0       U=0       U=0       D=0         constraints       R= Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         Dit 15-14       Unimplemented: Read as '0'       D= Bit is cleared       x = Bit is unknown         Dit 15-14       Unimplemented: Read as '0'       D= Interrupt request enabled       0 = Interrupt request as '0'         Dit 12-9       Unimplemented: Read as '0'       Dit 12:       D= Interrupt request enabled       D= Interrupt request not enabled         Dit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request enabled       D = Interrupt request not enabled         Dit 7-4       Unimplemented: Read as '0'       Dit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled         Dit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request enabled       D = Interrupt request enabled         Dit 1       UIERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request enabled       D = Interrupt request enabled         Di Interrupt request enabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —            | —           | CTMUIE                        | —             | —                 |                  | —               | LVDIE |  |  |  |  |

| Image: Section of the section of t | bit 15       |             |                               |               |                   |                  |                 | bit 8 |  |  |  |  |

| Image: Section of the section of t |              |             |                               |               |                   |                  |                 |       |  |  |  |  |

| bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit       x = Bit is unknown         bit 12-9       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 12-9       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 7-4       Unimplemented: Read as '0'       bit       1 = Interrupt request not enabled         bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request enabled       0 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0          | U-0         | U-0                           | U-0           |                   |                  |                 | U-0   |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'          bit 15-14       Unimplemented: Read as '0'          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled         bit 12-9       Unimplemented: Read as '0'         bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled <t< td=""><td></td><td></td><td>_</td><td>—</td><td>CRCIE</td><td>U2ERIE</td><td>U1ERIE</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |             | _                             | —             | CRCIE             | U2ERIE           | U1ERIE          |       |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'           bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request not enabled          bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request not enabled          bit 7-4       Unimplemented: Read as '0'            bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled          bit 4       Interrupt request ont enabled             bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled            bit 1       UITERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7        |             |                               |               |                   |                  |                 | bit C |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'           bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request enabled          bit 13       CTMUIE: CTMU Interrupt Enable bit       1 = Interrupt request not enabled          bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 12-9       Unimplemented: Read as '0'           bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit       1 = Interrupt request not enabled          bit 7-4       Unimplemented: Read as '0'            bit 3       CRCIE: CRC Generator Interrupt Enable bit       1 = Interrupt request not enabled          bit 4       Interrupt request ont enabled             bit 2       U2ERIE: UART2 Error Interrupt Enable bit       1 = Interrupt request not enabled            bit 1       UITERIE: UART1 Error Interrupt Enable bit       1 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:      |             |                               |               |                   |                  |                 |       |  |  |  |  |

| bit 15-14       Unimplemented: Read as '0'         0 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -            | ole bit     | W = Writable b                | oit           | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |

| bit 13       CTMUIE: CTMU Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -n = Value a | It POR      | '1' = Bit is set              |               | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |  |  |

| bit 13       CTMUIE: CTMU Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |             |                               |               |                   |                  |                 |       |  |  |  |  |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 12-9         Unimplemented: Read as '0'         bit 8         LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request ont enabled         0 = Interrupt request not enabled         bit 7-4         Unimplemented: Read as '0'         cRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 3         CRCIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 2         U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled         bit 1         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15-14    | Unimplemer  | nted: Read as '0              | ,             |                   |                  |                 |       |  |  |  |  |

| <ul> <li>o = Interrupt request not enabled</li> <li>bit 12-9</li> <li>Unimplemented: Read as '0'</li> <li>LVDIE: Low-Voltage Detect Interrupt Enable bit         <ol> <li>= Interrupt request enabled</li> <li>= Interrupt request enabled</li> <li>o = Interrupt request not enabled</li> </ol> </li> <li>bit 3</li> <li>CRCIE: CRC Generator Interrupt Enable bit         <ol> <li>= Interrupt request enabled</li> <li>= Interrupt request not enabled</li> </ol> </li> <li>bit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit         <ol> <li>I = Interrupt request enabled</li> <li>= Interrupt request not enabled</li> <li>I = Interrupt request not enabled</li> <li>= Interrupt request not</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 13       | CTMUIE: CT  | MU Interrupt En               | able bit      |                   |                  |                 |       |  |  |  |  |

| bit 8       LVDIE: Low-Voltage Detect Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 7-4       Unimplemented: Read as '0'         bit 3       CRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 1       Interrupt request enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 1       U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |             |                               |               |                   |                  |                 |       |  |  |  |  |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = CRCIE: CRC Generator Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 12-9     | Unimplemer  | nted: Read as '0              | ,             |                   |                  |                 |       |  |  |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>bit 7-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3</li> <li>CRCIE: CRC Generator Interrupt Enable bit         <ol> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit                 <ol> <li>a = Interrupt request enabled</li> <li>bit 1 = Interrupt request enabled</li> <li>bit 2</li> <li>U1ERIE: UART2 Error Interrupt Enable bit                     <ol> <li>a = Interrupt request enabled</li> <li>bit 1 = Interrupt request not enabled</li> <li>bit 1 = Interrupt request not enabled</li> <li>bit 1 = Interrupt request not enabled</li></ol></li></ol></li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 8        | LVDIE: Low- | Voltage Detect I              | nterrupt Enat | ole bit           |                  |                 |       |  |  |  |  |

| bit 3       CRCIE: CRC Generator Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 2       U2ERIE: UART2 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1         U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |             | •                             |               |                   |                  |                 |       |  |  |  |  |

| <pre>1 = Interrupt request enabled 0 = Interrupt request not enabled bit 2 U2ERIE: UART2 Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 1 U1ERIE: UART1 Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request enabled 0 = Interrupt request enabled</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7-4      | Unimplemer  | nted: Read as '0              | '             |                   |                  |                 |       |  |  |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>Dit 2</li> <li>U2ERIE: UART2 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>Dit 1</li> <li>U1ERIE: UART1 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3        | CRCIE: CRC  | Generator Inter               | rupt Enable I | oit               |                  |                 |       |  |  |  |  |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1         U1ERIE: UART1 Error Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |             |                               |               |                   |                  |                 |       |  |  |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>Dit 1</li> <li>DIERIE: UART1 Error Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 2        | U2ERIE: UA  | RT2 Error Interro             | upt Enable bi | t                 |                  |                 |       |  |  |  |  |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |             | 1 = Interrupt request enabled |               |                   |                  |                 |       |  |  |  |  |

| 0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1        |             |                               |               | t                 |                  |                 |       |  |  |  |  |