#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | ZNEO                                                      |

| Core Size                  | 16-Bit                                                    |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 60                                                        |

| Program Memory Size        | 128KB (128K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 80-BQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z16f2810fi20ag |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| On-Chip Debugger                 | 298 |

|----------------------------------|-----|

| Architecture                     | 298 |

| Operation                        | 299 |

| On-Chip Debug Enable 2           | 299 |

| Serial Interface                 | 300 |

| Serial Data Format               | 300 |

| Baud Rate Generator              | 301 |

| Auto-Baud Detector               | 302 |

| Line Control                     | 303 |

| 9-Bit Mode                       | 303 |

| Start Bit Flow Control 3         | 304 |

| Initialization                   | 304 |

| Initialization during Reset      | 305 |

| Debug Lock                       | 305 |

| Error Reset                      | 305 |

| DEBUG Halt Mode                  | 306 |

| Reading and Writing Memory 3     | 306 |

| Reading Memory CRC 3             | 307 |

| Breakpoints                      | 307 |

| Instruction Trace                | 308 |

| On-Chip Debugger Commands 3      | 309 |

| Cyclic Redundancy Check 3        | 313 |

| Memory Cyclic Redundancy Check 3 | 313 |

| UART Mode                        | 313 |

| Serial Errors                    | 314 |

| Interrupts                       | 314 |

| DBG Pin as a GPIO Pin 3          | 314 |

| Control Register Definitions 3   | 315 |

| Receive Data Register 3          | 315 |

| Transmit Data Register           | 315 |

| Baud Rate Reload Register 3      | 316 |

| Line Control Register            | 316 |

| Status Register                  | 318 |

| Control Register                 | 319 |

|                                  | 321 |

| OCD Status Register              | 323 |

| Hardware Breakpoint Registers 3  |     |

| Trace Control Register           |     |

| Trace Address Register           | 326 |

|                                  |     |

IPO Trim Registers (Information Area Address 0021h and 0022h) ...... 296 ADC Reference Voltage Trim (Information Area Address 0023h) ...... 297

#### xiii

| Register Description                      | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset (Hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port J Stop Mode Recovery<br>Enable       | PJSMRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Port J Reserved                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| dress = FF_E190                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Port K Input Data                         | PKIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>71</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Output Data                        | PKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>72</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Data Direction                     | PKDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>73</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K High Drive Enable                  | PKHDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>74</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reserved                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Port K Alternate Function Low             | PKAFL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>76</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Output Control                     | PKOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>76</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Pull-Up Enable                     | PKPUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>76</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Stop Mode Recovery<br>Enable       | PKSMRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>77</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port K Reserved                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Address = FF_E200                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| lress = FF_E200                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LIN-UART0 Transmit Data                   | U0TXD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>154</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Receive Data                    | U0RXD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>154</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Status 0                        | U0STAT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000011Xb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>155</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Control 0                       | U0CTL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>160</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Control 1                       | U0CTL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>164</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Mode Select and<br>Status       | U0MDSTAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>162</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Address Compare<br>Register     | U0ADDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>166</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Baud Rate High U0BRH FF<br>Byte |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>166</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIN-UART0 Baud Rate Low U0BRL FF<br>Byte  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>167</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Reserved                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Iress = FF E210                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                           | Port J Stop Mode Recovery<br>EnablePort J Reserveddress = FF_E190Port K Input DataPort K Output DataPort K Output DataPort K Data DirectionPort K High Drive EnableReservedPort K Alternate Function LowPort K Output ControlPort K Stop Mode Recovery<br>EnablePort K Stop Mode Recovery<br>EnablePort K ReservedAddress = FF_E200Iress = FF_E200Iress = FF_E200Iress = FF_E200LIN-UART0 Transmit Data<br>LIN-UART0 Control 0LIN-UART0 Control 1LIN-UART0 Control 1LIN-UART0 Address Compare<br>RegisterLIN-UART0 Baud Rate High<br>ByteByteReserved | Port J Stop Mode Recovery<br>EnablePJSMRE<br>EnablePort J Reserved—dress = FF_E190Port K Input DataPKINPort K Output DataPKOUTPort K Output DataPKOUTPort K Data DirectionPKDDPort K High Drive EnablePKHDEReserved—Port K Alternate Function LowPKAFLPort K Output ControlPKOCPort K Pull-Up EnablePKPUEPort K Stop Mode Recovery<br>EnablePKSMREPort K Reserved—Address = FF_E200—Iress = FF_E200UOTXDLIN-UART0 Transmit DataUOTXDLIN-UART0 Status 0UOSTAT0LIN-UART0 Control 1UOCTL0LIN-UART0 Control 1UOCTL1LIN-UART0 Address Compare<br>RegisterU0ADDRLIN-UART0 Baud Rate High<br>ByteU0BRH<br>ByteReserved— | Port J Stop Mode Recovery<br>EnablePJSMRE00Port J Reserved——Port J Reserved——Port K Input DataPKINXXPort K Output DataPKOUT00Port K Data DirectionPKDD00Port K High Drive EnablePKHDE00Reserved——Port K Alternate Function LowPKAFL00Port K Output ControlPKOC00Port K Stop Mode Recovery<br>EnablePKSMRE00Port K Reserved——Port K Reserved——Port K Reserved——Port K Reserved——Port K Reserved——Port K Reserved——Port K Reserved——In-UART0 Transmit DataU0TXDXXLIN-UART0 Control 0U0STAT000000111XbLIN-UART0 Control 1U0CTL000LIN-UART0 Mode Select andU0MDSTAT00StatusLIN-UART0 Address CompareU0ADDR00LIN-UART0 Address CompareU0ADDR00RegisterLIN-UART0 Baud Rate HighU0BRHFFByteEnserved——Reserved——XX |

### Table 6. Register File Address Map (Continued)

XX = Undefined.

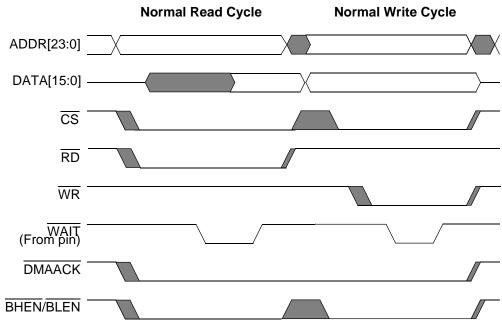

determination, be aware that the input data is captured on chip during the rising edge of the system clock prior to the RD signal deassertion. The Read signal  $(\overline{RD})$  timing is shown for both NORMAL and ISA modes.

|                                                             | Dela                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | y (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abbreviation                                                | Minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

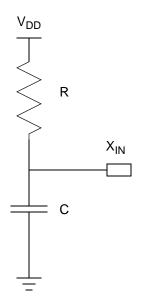

| X <sub>IN</sub> Rise to Address Valid Delay                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| X <sub>IN</sub> Rise to Address Output Hold Time            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Data Input Valid to X <sub>IN</sub> Rise Setup Time         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RD Rise to Data Input Hold Time                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| X <sub>IN</sub> Rise to CS Assertion Delay                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| X <sub>IN</sub> Rise to CS Deassertion Hold Time            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| X <sub>IN</sub> Rise to RD Assertion Delay                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| X <sub>IN</sub> Rise to RD Deassertion Hold Time            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WAIT Input Pin Assertion to X <sub>IN</sub> Rise Setup Time | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WAIT Input Pin Deassertion to XIN Rise Setup Time           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |