#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "Embedded -Microcontrollers

| Core Processor             | ZNEO                                            |

|----------------------------|-------------------------------------------------|

| Core Size                  | 16-Bit                                          |

| Speed                      | 20MHz                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WI       |

| Number of I/O              | 46                                              |

| Program Memory Size        | 128KB (128K x 8)                                |

| Program Memory Type        | FLASH                                           |

| EEPROM Size                | -                                               |

| RAM Size                   | 4K x 8                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                     |

| Data Converters            | A/D 12x10b                                      |

|                            |                                                 |

Obsolete

DT Oscillator Type Internal **Operating Temperature** -40°C ~ 105°C (TA)

Mounting Type Surface Mount Package / Case 68-LCC (J-Lead) Supplier Device Package -Purchase URL https://www.e-xfl.com/product-detail/zilog/z16f2810vh20eg

Email: info@E-XFL.COM

Details

Product Status

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Section                       | Description                                                                                                                                                                                                                                                                                                                                        | Page<br>No.                                                |  |  |  |

|-------------|-------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| Nov<br>2013 | 12                | Signal Descriptions           | Corrected active status of RD, WR and $\overline{CS}$ signals.                                                                                                                                                                                                                                                                                     | <u>12</u>                                                  |  |  |  |

| Jul<br>2013 | 11                | Analog Functions              | Updated the Analog Functions Block Dia-<br>gram.                                                                                                                                                                                                                                                                                                   | <u>242</u>                                                 |  |  |  |

| Aug<br>2011 | 10                | Multi-Channel PWM Timer       | Per CR#13095, corrected PWMEN descrip-<br>tion in PWM Control 0 Register (PWMCTL0)<br>table; corrected description in PWM Dead-<br>band Register (PWMDB) table and added<br>footnote; added same footnote to PWM Mini-<br>mum Pulse Width Filter (PWMMPF), PWM<br>Fault Mask Register (PWMFM), and PWM<br>Fault Control Register (PWMFCTL) tables. | <u>125</u> ,<br><u>127</u> –<br><u>129</u> ,<br><u>131</u> |  |  |  |

| Jun<br>2011 | 09                | Electrical Characteristics    | Corrected V <sub>COFF</sub> input offset value in Com-<br>parator Electrical Characteristics table                                                                                                                                                                                                                                                 | <u>347</u>                                                 |  |  |  |

| Aug         | 08                | N/A                           | Removed ISO information.                                                                                                                                                                                                                                                                                                                           | <u>ii</u>                                                  |  |  |  |

| 2010        |                   | All                           | Updated logos.                                                                                                                                                                                                                                                                                                                                     | All                                                        |  |  |  |

|             |                   | Table 191                     | Changed the Minimum, Typical and Maxi-<br>mum values for V <sub>REF</sub> (Externally supplied<br>Voltage Reference only).                                                                                                                                                                                                                         | <u>346</u>                                                 |  |  |  |

| Jan<br>2009 | 07                | Timer 0–2 Control 0 Register  | Table 62: added "Only Counter Mode should<br>be used with this feature" to Bit 4 description                                                                                                                                                                                                                                                       |                                                            |  |  |  |

|             |                   | Analog Functions              | ADC Overview, updated fast conversion time to $2.5 \mu s$ .                                                                                                                                                                                                                                                                                        | <u>243</u>                                                 |  |  |  |

|             |                   | Electrical Characteristics    | Updated Table 185.                                                                                                                                                                                                                                                                                                                                 | <u>337</u>                                                 |  |  |  |

|             |                   | Internal Precision Oscillator | Removed reference to 32kHz.                                                                                                                                                                                                                                                                                                                        | <u>336</u>                                                 |  |  |  |

## ZNEO<sup>®</sup> Z16F Series MCUs Product Specification

| Low-Power Modes                                     |

|-----------------------------------------------------|

| Stop Mode                                           |

| Halt Mode                                           |

| Peripheral-Level Power Control                      |

| Power Control Option Bits                           |

| General-Purpose Input/Output                        |

| GPIO Port Availability by Device                    |

| Architecture                                        |

| GPIO Alternate Functions                            |

| GPIO Interrupts                                     |

| GPIO Control Register Definitions                   |

| Port A-K Input Data Registers                       |

| Port A-K Output Data Registers                      |

| Port A-K Data Direction Registers                   |

| Port A-K High Drive Enable Registers                |

| Port A-K Alternate Function High and Low Registers  |

| Port A-K Output Control Registers                   |

| Port A-K Pull-Up Enable Registers                   |

| Port A-K Stop Mode Recovery Source Enable Registers |

| Port A IRQ MUX1 Register                            |

| Port A IRQ MUX Register                             |

| Port A IRQ Edge Register                            |

| Port C IRQ MUX Register                             |

| Interrupt Controller                                |

| Interrupt Vector Listing                            |

| Architecture                                        |

| Operation                                           |

| Master Interrupt Enable                             |

| Interrupt Vectors and Priority                      |

| System Exceptions                                   |

| Interrupt Assertion                                 |

| System Exception Status Registers                   |

| Last IRQ Register                                   |

| Interrupt Request 0 Register                        |

| Interrupt Request 1 Register                        |

| Interrupt Request 2 Register                        |

| IRQ0 Enable High and Low Bit Registers              |

| IRQ1 Enable High and Low Bit Registers              |

| IRQ2 Enable High and Low Bit Registers              |

|                                                     |

|                                                     |

#### vii

the address space between internal and external nonvolatile memory and between non-volatile and volatile memory.

- Any external volatile (random access) memory must be located at or above80\_0000h in the 24-bit address space (in the CS1 range). This location is a requirement of the ZDSII GUI. Volatile memory on CS0 is located in a lower address range if it is configured by adding an edited linkerRANGE command to the Additional Linker Commands field of the ZDSII project settings.

- External volatile memory falling below FF\_8000h must be addressed as a contiguous block. The ZDSII C-Compiler large model does not support holes in 32-bit addressed volatile memory. There is a hole between this memory and volatilememory at or above FF\_8000h, however.

- External volatile memory at or above FF\_8000h must be addressed as a block contiguous with the microcontroller's internal RAM. The ZDSII C-Compiler small model does not support holes in 16-bit addressable volatile memory.

- External volatile memory must not be located above internal RAM, which ends at FF\_BFFFh. This location is a requirement of the ZDSII GUI. Volatile memory is located at FF\_C000h and extend up to FF\_DFFFh if the space is not used for I/O, but the range must be configured by adding an edited linker RANGE command to the Additional Linker Commands field of the project settings. The debugger memory window always displays this range as part of the I/O Data space, however.

- The ZDSII GUI assumes external I/O is located in the range FF\_C000h to FF\_DFFFh. Any external I/O that is located elsewhere is accessed using absolute addressing. The debugger memory window displays all addresses below FF\_C000h as part of theMemory space.

For details about how ZDSII development tools use memory, refer to the <u>Zilog Developer</u> <u>Studio II – ZNEO User Manual (UM0171)</u>.

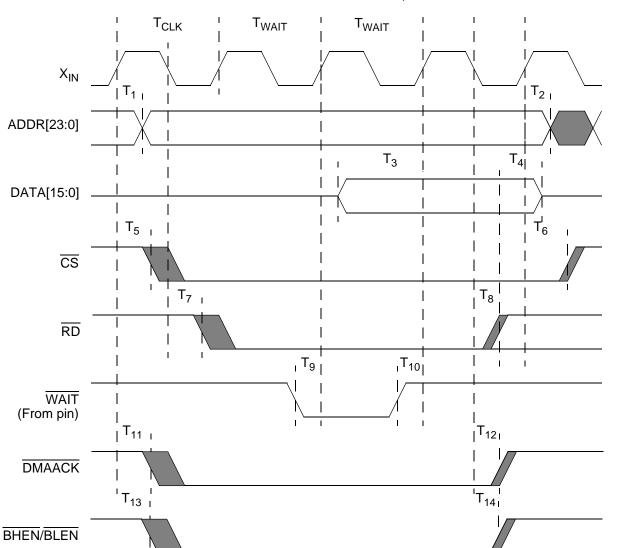

## **External WAIT Pin Operation**

Setup of the external  $\overline{\text{WAIT}}$  pin is selected by the GPIO alternate function. When using the external  $\overline{\text{WAIT}}$  pin, at least one internal wait state must be added to allow sufficient address valid to wait input setup time.

Table 13 lists the External Chip Select Control Registers Low for  $\overline{CS2}$  to  $\overline{CS5}$  (EXTC-SxL). This register sets the number of wait states for chip selects 2 through 5. Waits are only added if the chip select is enabled.

Table 13. External Chip Select Control Registers Low for  $\overline{CS2}$  to  $\overline{CS5}$  (EXTCSxL)

| Bits      |   | 7                                              | 6             | 5           | 4            | 3           | 2    | 1       | 0   |  |  |

|-----------|---|------------------------------------------------|---------------|-------------|--------------|-------------|------|---------|-----|--|--|

| Field     |   | RESE                                           | ERVED PRxWA   |             | NAIT         | /AIT        |      | CSxWAIT |     |  |  |

| RESET     | 0 |                                                | 0             | 0           | 0            | 0           | 0    | 0       | 0   |  |  |

| R/W       | R | /W                                             | R/W           | R/W         | R/W          | R/W         | R/W  | R/W     | R/W |  |  |

| Addr      |   |                                                |               | FF_         | (E077, E079  | , E07B, E07 | 7D)H |         | •   |  |  |

| Bit       |   | Descr                                          | iption        |             |              |             |      |         |     |  |  |

| [7:6]     |   | Reser                                          | •             |             |              |             |      |         |     |  |  |

| [7.0]     |   |                                                |               | erved and n | nust be prog | rammed to   | 00.  |         |     |  |  |

| [5:4]     |   |                                                |               |             |              |             |      |         |     |  |  |

| PRxWAIT[2 |   | Post Read Wait Selection<br>00 = 0 wait state. |               |             |              |             |      |         |     |  |  |

|           |   | 01 = 1 wait state.                             |               |             |              |             |      |         |     |  |  |

|           |   | 10 = 2 wait states.                            |               |             |              |             |      |         |     |  |  |

|           |   | 11 = 3                                         | wait states.  |             |              |             |      |         |     |  |  |

| [3:0]     |   | Chip Select x Wait Selection                   |               |             |              |             |      |         |     |  |  |

| CSxWAIT   |   | 0000 = 0 wait state.                           |               |             |              |             |      |         |     |  |  |

|           |   | 0001 = 2 wait state.                           |               |             |              |             |      |         |     |  |  |

|           |   | 0010 = 4 wait states.                          |               |             |              |             |      |         |     |  |  |

|           |   | 0011 = 6 wait states.                          |               |             |              |             |      |         |     |  |  |

|           |   | 0100 = 8 wait states.                          |               |             |              |             |      |         |     |  |  |

|           |   | 0101 = 10 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   | 0110 = 12 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   | -                                              | = 14 wait sta |             |              |             |      |         |     |  |  |

|           |   | 1000 = 16 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   | 1001 = 18 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   | 1010 = 20 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   | 1011 = 22 wait states.                         |               |             |              |             |      |         |     |  |  |

|           |   |                                                | = 24 wait sta |             |              |             |      |         |     |  |  |

|           |   | -                                              | = 26 wait sta |             |              |             |      |         |     |  |  |

|           |   |                                                | = 28 wait sta |             |              |             |      |         |     |  |  |

|           |   | 1111 =                                         | = 30 wait sta | tes.        |              |             |      |         |     |  |  |

#### 1 Wait State from Wait State Generator and 1 Wait State from External WAIT pin

- 5. Enable the timer interrupt, if required and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin(s) for the timer output alternate function.

- 7. Write to the Timer Control 1 Register to enable the timer and initiate counting.

The PWM period is determined by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001h is loaded into the Timer High and Low Byte registers, use the One-Shot Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is determined by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is determined by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **Capture Modes**

There are three Capture modes which provide slightly different methods for recording the time or time interval between timer input events. These modes are Capture Mode, Capture Restart Mode and Capture Compare Mode. In all of the three modes, when the appropriate timer input transition (capture event) occurs, the timer counter value is captured and stored in the PWM High and Low Byte registers. The TPOL bit in the Timer Control 1 Register determines if the Capture occurs on a rising edge or a falling edge of the timer input signal. The TICONFIG bit determines whether interrupts are generated on capture events, reload events or both. The INCAP bit in Timer Control 0 Register clears to indicate an interrupt caused by a reload event and sets to indicate the timer interrupt is caused by an input capture event.

If the timer output alternate function is enabled, the timer output pin changes state (from Low to High or High to Low) at timer Reload. The initial value is determined by the TPOL bit.

## **PWM Reload High and Low Byte Registers**

The PWM Reload High and Low Byte (PWMRH and PWMRL) registers, shown in Tables 66 and 67, store a 12-bit reload value, {PWMRH[3:0], PWMRL[7:0]}. The PWM reload value is held in buffer registers. The PWM reload value written to the buffer registers are not used by the PWM generator until the next PWM reload event occurs. Reads from these registers always return the values from the buffer registers.

Edge-Aligned PWM Mode Period =  $\frac{\text{Prescaler} \times \text{Reload Value}}{\text{f}_{PWMclk}}$

Center-Aligned PWM Mode Period =  $\frac{2 \times \text{Prescaler} \times \text{Reload Value}}{\text{f}_{PWMclk}}$

#### Table 66. PWM Reload High Byte Register (PWMRH)

| Bits  | 7        | 6    | 5     | 4 | 3     | 2 | 1 | 0 |  |  |

|-------|----------|------|-------|---|-------|---|---|---|--|--|

| Field |          | Rese | erved |   | PWMRH |   |   |   |  |  |

| RESET |          | 0    | h     |   | Fh    |   |   |   |  |  |

| R/W   |          | R/   | W     |   | R/W   |   |   |   |  |  |

| Addr  | FF_E38EH |      |       |   |       |   |   |   |  |  |

| Bit            | Description                                                                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                                                                            |

| [3:0]<br>PWMRH | <b>PWM Reload Register High and Low</b><br>These two bytes form the 12-bit reload value, {PWMRH[3:0], PWMRL[7:0]}. This value sets the<br>PWM period. |

#### Table 67. PWM Reload Low Byte Register (PWMRL)

| Bits  | 7     | 6 | 5 | 4    | 3    | 2 | 1 | 0 |  |

|-------|-------|---|---|------|------|---|---|---|--|

| Field | PWMRL |   |   |      |      |   |   |   |  |

| RESET | FF    |   |   |      |      |   |   |   |  |

| R/W   | R/W   |   |   |      |      |   |   |   |  |

| Addr  |       |   |   | FF_E | 38Fh |   |   |   |  |

| Bit            | Description                                                                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PWMRL | <b>PWM Reload Register High and Low</b><br>These two bytes form the 12-bit reload value, {PWMRH[3:0], PWMRL[7:0]}. This value sets the<br>PWM period. |

- 2. Load the appropriate 16-bit count value into the LIN-UART Baud Rate High and Low Byte registers.

- 3. Enable the BRG timer function and associated interrupt by setting the BRGCTL bit in the LIN-UART Control 1 Register to 1. Enable the UART receive interrupt in the interrupt controller.

When configured as a general purpose timer, the BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

## **Noise Filter**

A noise filter circuit is included to filter noise on a digital input signal, such as UART receive data before the data is sampled by the block. This filter is a requirement for protocols in a noisy environment.

The noise filter includes following features:

- Synchronizes the receive input data to the system clock.

- Noise filter enable (NFEN)input selects whether the noise filter is bypassed (NFEN = 0) or included (NFEN = 1) in the receive data path.

- Noise filter control (NFCTL[2:0])input selects the width of the up/down saturating counter digital filter. The available widths range is from 4 to11 bits.

- The digital filter output has hysteresis.

- Provides an active low saturated state output (FiltSatB), used to indicate presence of noise.

### Architecture

Figure 30 displays how the noise filter is integrated with the LIN-UART for use on a LIN network.

- STR bit on the SPI module replaced with ESPIEN1. SPIEN replaced with ESPIEN0. This enhancement allows unidirectional transfers which minimizes software or DMA overhead.

- BIRQ replaced with BRGCTL.

- Mode register:

- Added SSMD field which adds support for loop back and I2S modes.

- Moved SSV bit to the transmit data command register as described above.

- Added slave select polarity (SSPO) to support active High and Low slave select on  $\overline{SS}$  pin.

- Status register:

- IRQ split into TDRE and RDRF (separate transmit and receive interrupts).

- Replace overrun error with separate transmit under-run and receive overrun.

- State register.

- Replaced SCKEN bit with SCKI.

- Replaced TCKEN with SDI.

## Operation

During transfer, data is sent and received simultaneously by both master and slave devices. Separate signals are required to transmit data, receive data and the serial clock. When a transfer occurs, a multibit (typically 8-bt) character is shifted out one data pin and a multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the master and an 8-bit shift register in the slave is connected as a circular buffer. The ESPI shift register is buffered to support back-to-back character transfers in high performance applications.

A transaction is initiated when the Transmit Data Register is written in the master device. The value from the data register is transferred into the shift register and the transaction begins. After the transmit data is loaded into the shift register, the Transmit Data register Empty (TDRE) status bit asserts, indicating that Transmit Data Register is written with the next value. At the end of each character transfer, the shift register value (receive data) is loaded into the Receive Data Register. At that point the Receive Data register Full (RDRF) status bit asserts. When software or DMA reads the receive data from the Receive Data Register, the RDRF signal deasserts.

The master sources the SCK and  $\overline{SS}$  signal during the transfer.

Internal data movement (either by software or DMA) to/from the ESPI block is controlled by the Transmit Data Register empty (TDRE) and Receive Data Register full (RDRF) signals. These signals are read only bits in the ESPI Status Register. When either the TDRE or RDRF bits assert, an interrupt is sent to the interrupt controller if the data interrupt

| Bit  | Description (Continued)                                                                 |

|------|-----------------------------------------------------------------------------------------|

| [2]  | Wire-OR (Open-Drain) Mode Enabled                                                       |

| WOR  | 0 = ESPI signal pins not configured for open-drain.                                     |

|      | 1 = All four ESPI signal pins (SCK, SS, MISO, MOSI) configured for open-drain function. |

|      | This setting is used for Multi-Master and/or Multi-Slave configurations.                |

| [1]  | ESPI Master Mode Enable                                                                 |

| MMEN | This bit controls the data I/O pin selection and SCK direction.                         |

|      | 0 = Data-out on MISO, data-in on MOSI (used in SPI Slave Mode), SCK is an input.        |

|      | 1 = Data-out on MOSI, data-in on MISO (used in SPI Master Mode), SCK is an output.      |

# **Caution:** If reading the counter one byte at a time while the BRG is counting keep in mind that the values will not be in sync. It is recommended to read the counter using word (2-byte) reads.

## **ESPI Mode Register**

The ESPI Mode Register, shown in Table 105, configures the character bit width and mode of the ESPI I/O pins.

#### Table 105. ESPI Mode Register (ESPIMODE)

| Bits  | 7 | 6        | 5 | 4   | 3           | 2    | 1    | 0   |  |  |

|-------|---|----------|---|-----|-------------|------|------|-----|--|--|

| Field |   | SSMD     |   | N   | IUMBITS[2:0 | SSIO | SSPO |     |  |  |

| RESET |   | 000      |   |     | 000         | 0    | 0    |     |  |  |

| R/W   |   | R/W      |   | R/W |             |      | R/W  | R/W |  |  |

| Addr  |   | FF_E263h |   |     |             |      |      |     |  |  |

#### Bit Description

#### [7:5] Slave Select Mode

SSMD

#### This field select would

This field selects the behavior of  $\overline{SS}$  as a framing signal. For a detailed description of these modes, see the <u>Slave Select</u> section on page 179.

#### 000 = SPI Mode

When SSIO = 1, the  $\overline{SS}$  pin is driven directly from the SSV bit in the Transmit Data Command register. The Master software or DMA must set SSV (or a GPIO output if the  $\overline{SS}$  pin is not connected to the appropriate Slave) to the asserted state prior to or on the same clock cycle with which the Transmit Data Register is written with the initial byte. At the end of a frame (after the last RDRF event), SSV is deasserted by software. Alternatively, SSV is automatically deasserted by hardware if the TEOF bit in the Transmit Data Command register is set when the last transmit byte is loaded. In SPI Mode, SCK is active only for data transfer (one clock cycle per bit transferred).

#### 001 = LOOPBACK Mode

When ESPI is configured as Master (MMEN = 1) the outputs are deasserted and data is looped from shift register out to shift register in. When ESPI is configured as a Slave (MMEN = 0) and  $\overline{SS}$  in asserts, MISO (Slave output) is tied to MOSI (Slave input) to provide an a remote loop back (echo) function.

#### $010 = I^2 S Mode$

In this mode, the value from SSV will be output by the Master on the  $\overline{SS}$  pin one SCK period before the data and will remain in that state until the start of the next frame. Typically this mode is used to send back-to-back frames with  $\overline{SS}$  alternating on each frame. A frame boundary is indicated in the Master when  $\underline{SSV}$  changes. A frame boundary is detected in the Slave by  $\overline{SS}$  changing state. The  $\overline{SS}$  framing signal will lead the frame by one SCK period. In this mode SCK will run continuously, starting with the initial  $\overline{SS}$  assertion. Frames will run back-to-back as long as software/DMA continue to provide data. The  $I^2S$  protocol (Inter IC Sound) is used to carry left and right channel audio data with the  $\underline{SS}$  signal indicating which channel is being sent. In Slave Mode, the change in state of  $\overline{SS}$  (Low to High or High to Low) will trigger the start of a transaction on the next SCK cycle.

Each interrupt source other than the baud rate generator interrupt has an associated bit in the I2CISTAT Register, which clears automatically when software reads the register or performs some other task such as reading or writing the data register.

#### **Transmit Interrupts**

Transmit interrupts (TDRE bit = 1 in I2CISTAT) occur under the following conditions:

- The Transmit Data Register is empty and the TXI bit = 1 in the  $I^2C$  Control Register

- The I<sup>2</sup>C Controller is enabled, with any one of the following operations:

- The first bit of a 10-bit address is shifted out

- The first bit of the final byte of an address is shifted out and the RD bit is deasserted

- The first bit of a data byte is shifted out

Writing to the I<sup>2</sup>C Data Register always clears the TRDE bit to 0.

#### **Receive Interrupts**

Receive interrupts (RDRF bit = 1 in I2CISTAT) occur when a byte of data has been received by the I<sup>2</sup>C Controller. The RDRF bit is cleared by reading from the I<sup>2</sup>C Data Register. If the RDRF interrupt is not serviced prior to the completion of the next receive byte, the I<sup>2</sup>C Controller holds SCL Low during the last data bit of the next byte until RDRF is cleared to prevent receive overruns. A receive interrupt does not occur when a Slave receives an address byte or for data bytes following a Slave address that did not match. An exception is if the interactive receive mode (IRM) bit is set in the I2CMODE Register in which case receive interrupts occur for all receive address and data bytes in Slave Mode.

#### **Slave Address Match Interrupts**

Slave address match interrupts (SAM bit = 1 in I2CISTAT) occur when the I<sup>2</sup>C Controller is in Slave Mode and an address is received which matches the unique Slave address. The General Call Address (0000\_0000) and STARTBYTE (0000\_0001) are recognized if the GCE bit = 1 in the I2CMODE Register. Software verifies the RD bit in the I2CISTAT Register to determine if the transaction is a read or write transaction. The General Call Address and STARTBYTE addresses are also distinguished by the RD bit. The general call address (GCA) bit of the I2CISTAT Register indicates whether the address match occurred on the unique Slave address or the General Call/STARTBYTE address. The SAM bit clears automatically when the I2CISTAT Register is read.

If configured using the MODE[1:0] field of the I<sup>2</sup>C Mode Register for 7-bit slave addressing, the most significant 7 bits of the first byte of the transaction are compared against the SLA[6:0] bits of the Slave Address Register. If configured for 10-bit slave addressing, the

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>SPRS | <b>Stop/Restart Condition Interrupt</b><br>This bit is set when the I <sup>2</sup> C Controller is enabled in Slave Mode and detects a Stop or Restart condition during a transaction directed to this slave. This bit clears when the I2CISTAT Register is read. Read the RSTR bit of the I2CSTATE Register to determine whether the interrupt was caused by a Stop or Restart condition. |

| [0]<br>NCKI | <b>NAK Interrupt</b><br>In Master Mode, this bit is set when a Not Acknowledge condition is received or sent and nei-<br>ther the Start nor the Stop bit is active. In Master Mode, this bit is cleared only by setting the<br>Start or Stop bits.                                                                                                                                         |

|             | In Slave Mode, this bit is set when a Not Acknowledge condition is received (Master reading data from Slave), indicating the Master is finished reading. A Stop or Restart condition follows. In Slave Mode this bit clears when the I2CISTAT Register is read.                                                                                                                            |

## I<sup>2</sup>C Control Register

The I<sup>2</sup>C Control Register, shown in Table 114, enables and configures the I<sup>2</sup>C operation.

| Bits                                                   | 7        | 6     | 5    | 4    | 3   | 2    | 1     | 0      |  |

|--------------------------------------------------------|----------|-------|------|------|-----|------|-------|--------|--|

| Field                                                  | IEN      | START | STOP | BIRQ | TXI | NAK  | FLUSH | FILTEN |  |

| RESET                                                  | 0        | 0     | 0    | 0    | 0   | 0    | 0     | 0      |  |

| R/W                                                    | R/W      | R/W1  | R/W1 | R/W  | R/W | R/W1 | R/W   | R/W    |  |

| Addr                                                   | FF–E242h |       |      |      |     |      |       |        |  |

| Note: R/W1 = The bit is set (write 1) but not cleared. |          |       |      |      |     |      |       |        |  |

#### Table 114. I<sup>2</sup>C Control Register (I2CCTL)

#### Bit Description

| [7] | I <sup>2</sup> C Enable                           |

|-----|---------------------------------------------------|

| IEN | This bit enables the I <sup>2</sup> C Controller. |

#### [6] Send Start Condition

START When set, this bit causes the I<sup>2</sup>C Controller (when configured as the Master) to send the Start condition. After it is asserted, this bit is cleared by the I<sup>2</sup>C Controller after it sends the Start condition or by deasserting the IEN bit. If this bit is 1, it cannot be cleared by writing to the bit. After this bit is set, the Start condition is sent if there is data in the I2CDATA or I2CSHIFT Register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until data is loaded. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a Restart condition after the byte shifts and the acknowledge phase completes. If the Stop bit is also set, it also waits until the Stop condition is sent before the Start condition.

If Start is set while a Slave Mode transaction is underway to this device, the Start bit is cleared and ARBLST bit in the Interrupt Status Register will be set.

## Sample Time Register

The Sample Time Register is used to program the length of active time for the sample after a conversion has begun by setting the Start bit in the ADC Control Register or initiated by the PWM. The number of system clock cycles required for sample time varies from system to system depending on the clock period used. This register must be programmed to contain the number of system clocks required to meet a 1 µs minimum sample time.

| Bits         | 7                                                                        | 6                                                                                                                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| Field        | Reserved ST                                                              |                                                                                                                   |   |   |   |   |   |   |  |  |

| RESET        | (                                                                        | 0                                                                                                                 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| R/W          | R R/W                                                                    |                                                                                                                   |   |   |   |   |   |   |  |  |

| Addr         | FF–E505h                                                                 |                                                                                                                   |   |   |   |   |   |   |  |  |

| Bit          | Description                                                              |                                                                                                                   |   |   |   |   |   |   |  |  |

| [7:6]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |                                                                                                                   |   |   |   |   |   |   |  |  |

| [5:0]<br>SHT | -                                                                        | <b>Sample Hold Time</b><br>$00h-3Fh = Sample Hold time in number of system clock periods to meet 1 \mus minimum.$ |   |   |   |   |   |   |  |  |

| Table | 130. | Sample | Time | (ADCST) |

|-------|------|--------|------|---------|

| Table | 100. | Campic |      |         |

## **ADC Clock Prescale Register**

The ADC Clock Prescale Register is used to provide a divided system clock to the ADC. When this register is programmed with 0h, the system clock is used for the ADC Clock.

| Bits  | 7        | 6    | 5     | 4 | 3     | 2    | 1    | 0    |

|-------|----------|------|-------|---|-------|------|------|------|

| Field |          | Rese | erved |   | DIV16 | DIV8 | DIV4 | DIV2 |

| RESET |          | (    | )     |   | 0     | 0    | 0    | 0    |

| R/W   |          | F    | र     |   |       | R/   | W    |      |

| Addr  | FF–E506h |      |       |   |       |      |      |      |

Table 131. ADC Clock Prescale Register (ADCCP)

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:4] | Reserved                                                |

|       | These bits are reserved and must be programmed to 0000. |

| [3]   | DIV16                                                   |

| DIV16 | 0 = Clock is not divided.                               |

|       | 1 = System Clock is divided by 16 for ADC Clock.        |

| Bit    | Description (Continued)                           |

|--------|---------------------------------------------------|

| [4]    | Comparator Input Select                           |

| CPISEL | 0 = PortB6 provides the comparator - input.       |

|        | 1 = PortC0 provides the comparator - input.       |

| [3]    | Comparator Interrupt Edge Select                  |

| CMPIRQ | 0 = Interrupt Request on Comparator Rising Edge.  |

|        | 1 = Interrupt Request on Comparator Falling Edge. |

| [2]    | PWM Fault Comparator Polarity                     |

| CMPIV  | 0 = PWM Fault is active when cp+ > cp-            |

|        | 1 = PWM Fault is active when cp- > cp+            |

| [1]    | Comparator Output Value                           |

| CMPOUT | 0 = Comparator output is logical 0.               |

|        | 1 = Comparator output is logical 1.               |

| [0]    | Comparator Enable                                 |

| CMPEN  | 0 = Comparator is disabled.                       |

|        | 1 = Comparator is enabled.                        |

## **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 142, protects Flash memory sectors from being programmed or erased from user code. User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code).

| Bits                                                                                                    | 7 6 5 4 3 2 1 0 |       |       |       |       |       |       | 0     |

|---------------------------------------------------------------------------------------------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|

| Field                                                                                                   | SECT7           | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |

| RESET                                                                                                   | 0               | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W                                                                                                     | R/W1            | R/W1  | R/W1  | R/W1  | R/W1  | R/W1  | R/W1  | R/W1  |

| Addr                                                                                                    | FF_E062h        |       |       |       |       |       |       |       |

| Note: R/W1 = Register is accessible for read operations. Register is written to 1 only (via user code). |                 |       |       |       |       |       |       |       |

#### Table 142. Flash Sector Protect Register (FSECT)

| Bit   | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| [7:0] | Sector Protect                                                                      |

| SECTn | 0 = Sector <i>n</i> is programmed or erased from user code.                         |

|       | 1 = Sector <i>n</i> is protected and cannot be programmed or erased from user code. |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TXCOL  | Transmit CollisionThis bit is set when a Transmit Collision occurs. This bit is cleared by writing a one to this bit.0 = No collision has been detected.1 = Transmit Collision has been detected.                                                                             |

| [1]<br>RXBUSY | <ul> <li>Receiver Busy</li> <li>This bit is set when the receiver is receiving the data. Multi-master systems uses this bit to ensure the line is idle before sending the data.</li> <li>0 = Receiver is idle.</li> <li>1 = Receiver is receiving data.</li> </ul>            |

| [0]<br>TXBUSY | <ul> <li>Transmitter Busy</li> <li>This bit is set when the transmitter is sending the data. This bit is used to determine when to turn off a transceiver for RS-485 applications.</li> <li>0 = Transmitter is idle.</li> <li>1 = Transmitter is sending the data.</li> </ul> |

## **Control Register**

The Control Register (DBGCTL), shown in Table 175, sets the mode of the serial interface.

| Bits  | 7       | 6     | 5        | 4   | 3     | 2      | 1      | 0      |

|-------|---------|-------|----------|-----|-------|--------|--------|--------|

| Field | OCDLOCK | OCDEN | Reserved |     | CRCEN | UARTEN | ABCHAR | ABSRCH |

| RESET | 1       | 1     | 00       |     | 1     | 0      | 0      | 1      |

| R/W   | R/W     | R/W   | R        |     | R/W   | R/W    | R/W    | R/W    |

| Addr  |         |       |          | FF_ | E086  |        |        |        |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>OCDLOCK | <ul> <li>On-Chip Debug Lock</li> <li>This bit locks the Debug Control register so it cannot be written by the CPU. This bit is automatically set if the DBGUART option bit is in its default erased state (one).</li> <li>0 = Debug Control register unlocked.</li> <li>1 = Debug Control register locked.</li> </ul>                                                    |

| [6]<br>OCDEN   | <ul> <li>On-Chip Debug Enable</li> <li>This bit is set when the OCD is enabled. When this bit is set, received data is interpreted as debug command. To use the DBG pin as a UART or GPIO pin, this bit must be cleared to 0 by software. This bit cannot be written by the CPU if OCDLOCK is set.</li> <li>0 = OCD is disabled.</li> <li>1 = OCD is enabled.</li> </ul> |

| Bit                    | Description (Continued)                                                  |

|------------------------|--------------------------------------------------------------------------|

| [23:16]<br>ADDR[23:16] | Breakpoint Address<br>The address to match when generating a breakpoint. |

| [15:0]<br>ADDR[15:0]   | _                                                                        |

## **Trace Control Register**

The Trace Control Register (TRACECTL), shown in Table 179, is used to enable the Trace operation. It also selects the size of the trace buffer.

| Table 179. Trace Control Register | (TRACECTL) |

|-----------------------------------|------------|

|-----------------------------------|------------|

| Bits  | 7       | 6 | 5    | 4     | 3        | 2   | 1 | 0 |  |

|-------|---------|---|------|-------|----------|-----|---|---|--|

| Field | TRACEEN |   | Rese | erved | TRACESEL |     |   |   |  |

| RESET | 0       | 0 | 0    | 0     | 0        | 000 |   |   |  |

| R/W   | R/W     | R | R    | R     | R        | R/W |   |   |  |

| Addr  | FF_E013 |   |      |       |          |     |   |   |  |

| Bit               | Description                                                                                                                                                                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TRACEEN    | <b>Trace Enable</b><br>0 = Trace is disabled.                                                                                                                                                                                                                                                                                  |

|                   | 1 = Traces is enabled                                                                                                                                                                                                                                                                                                          |

| [6:3]             | Reserved<br>This bit is reserved and must be programmed to 0000.                                                                                                                                                                                                                                                               |

| [2:0]<br>TRACESEL | Trace Size Select         000 – 128 Bytes (16 Events)         001 – 256 Bytes (32 Events)         010 – 512 Bytes (64 Events)         011 – 1024 Bytes (128 Events)         100 – 2048 Bytes (256 Events)         101 – 4096 Bytes (512 Events)         110 – 8192 Bytes (1024 Events)         111 – 16384 Bytes (2048 Events) |

## **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 187 lists the POR and VBO electrical characteristics and timing. Table 188 lists the Reset and Stop Mode Recovery pin timing.

|                   |                                                                                  | T <sub>A</sub> = | –40°C to 1       | 25°C |       |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------|------------------|------------------|------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                        | Min              | Typ <sup>1</sup> | Max  | Units | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset voltage threshold                                                 | 2.20             | 2.45             | 2.70 | V     | $V_{DD} = V_{POR}$                                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brown-Out reset voltage threshold                                        | 2.15             | 2.40             | 2.65 | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | V <sub>POR</sub> -V <sub>VBO</sub>                                               |                  | 50               | 100  | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to ensure valid POR                             | —                | $V_{SS}$         | —    | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset analog delay                                                      | —                | 50               |      | ms    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset digital delay                                                     | —                | 12               | _    | μs    | 66 IPO cycles                                                                                         |  |

| T <sub>VBO</sub>  | Voltage Brown-Out pulse rejection period                                         | —                | 10               | —    | ms    | V <sub>DD</sub> < V <sub>VBO</sub> to generate a<br>Reset                                             |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10             | _                | 100  | ms    |                                                                                                       |  |

| I <sub>CC</sub>   | Supply current                                                                   |                  | 500              |      | μA    | V <sub>DD</sub> = 3.3 V.                                                                              |  |

#### Table 187. POR and VBO Electrical Characteristics and Timing

1. Data in the typical column is from characterization at 3.3 V and 0°C. These values are provided for design guidance only and are not tested in production.

|                    |                                                     | T <sub>A</sub> = | –40°C to | 125°C |                  |                                                              |  |  |

|--------------------|-----------------------------------------------------|------------------|----------|-------|------------------|--------------------------------------------------------------|--|--|

| Symbol             | Parameter                                           | Min              | Тур      | Max   | Units            | Conditions                                                   |  |  |

| T <sub>RESET</sub> | RESET pin assertion to initiate a System Reset      | 4                | —        | —     | T <sub>CLK</sub> | Not in Stop Mode.<br>T <sub>CLK</sub> = System Clock period. |  |  |

| T <sub>SMR</sub>   | Stop Mode Recovery<br>pin Pulse Rejection<br>Period | 10               | 20       | 40    | ns               | RESET, DBG and GPIO pins configured as SMR sources.          |  |  |

#### Table 188. Reset and Stop Mode Recovery Pin Timing

| Part Number                        | Flash (Kbytes) | RAM (Kbytes) | External Interface | NO   | Multi-Channel timers<br>with PWM | Standard Timers<br>with PWM | ADC Inputs                                    | I <sup>2</sup> C Master/Slave | UART with LIN and IrDA | ESPI | Package      |

|------------------------------------|----------------|--------------|--------------------|------|----------------------------------|-----------------------------|-----------------------------------------------|-------------------------------|------------------------|------|--------------|

| Automotive Tempe                   | rature         | e: -40°0     | C to +1            | 25°C |                                  |                             |                                               |                               |                        |      |              |

| Z16F2811AL20AG                     | 128            | 4            | Yes                | 76   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 100-pin LQFP |

| Z16F2811FI20AG                     | 128            | 4            | Yes                | 60   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 80-pin QFP   |

| Z16F2810FI20AG                     | 128            | 4            | No                 | 60   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 80-pin QFP   |

| Z16F2810AG20AG                     | 128            | 4            | No                 | 46   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 64-pin LQFP  |

| Z16F2810VH20AG                     | 128            | 4            | No                 | 46   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 68-pin PLCC  |

| Z16F6411AL20AG                     | 64             | 4            | Yes                | 76   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 100-pin LQFP |

| Z16F6411FI20AG                     | 64             | 4            | Yes                | 60   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 80-pin QFP   |

| Z16F3211AL20AG                     | 32             | 2            | Yes                | 76   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 100-pin LQFP |

| Z16F3211FI20AG                     | 32             | 2            | Yes                | 60   | 1                                | 3                           | 12                                            | 1                             | 2                      | 1    | 80-pin QFP   |

| ZNEO Z16F Series Development Tools |                |              |                    |      |                                  |                             |                                               |                               |                        |      |              |

| Z16F2800100ZCOG                    |                |              |                    |      |                                  |                             | ZNEO <sup>®</sup> Z16F Series Development Kit |                               |                        |      |              |

| ZUSBSC00100ZACG                    |                |              |                    |      |                                  |                             | USB Smart Cable Accessory Kit                 |                               |                        |      |              |

| ZUSBOPTSC01ZACG                    |                |              |                    |      |                                  |                             | Opto-Isolated USB Smart Cable Accessory Kit   |                               |                        |      |              |

| ZENETSC0100ZACG                    |                |              |                    |      |                                  |                             | Ethernet Smart Cable Accessory Kit            |                               |                        |      |              |

#### Table 203. ZNEO Z16F Series Part Numbering

| ZNEO Z16F Series Development Tools |                                               |

|------------------------------------|-----------------------------------------------|

| Z16F2800100ZCOG                    | ZNEO <sup>®</sup> Z16F Series Development Kit |

| ZUSBSC00100ZACG                    | USB Smart Cable Accessory Kit                 |

| ZUSBOPTSC01ZACG                    | Opto-Isolated USB Smart Cable Accessory Kit   |

| ZENETSC0100ZACG                    | Ethernet Smart Cable Accessory Kit            |

|                                    |                                               |