Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | ZNEO                                                      |

| Core Size                  | 16-Bit                                                    |

| Speed                      | 20MHz                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 76                                                        |

| Program Memory Size        | 128KB (128K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 100-LQFP                                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z16f2811al20eg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Section                       | Description                                                                                                                                                                                                                                                                                                                                        | Page<br>No. |  |  |

|-------------|-------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Nov<br>2013 | 12                | Signal Descriptions           | Corrected active status of RD, WR and $\overline{CS}$ signals.                                                                                                                                                                                                                                                                                     | <u>12</u>   |  |  |

| Jul<br>2013 | 11                | Analog Functions              | Updated the Analog Functions Block Dia-<br>gram.                                                                                                                                                                                                                                                                                                   | <u>242</u>  |  |  |

| Aug<br>2011 | 10                | Multi-Channel PWM Timer       | Per CR#13095, corrected PWMEN descrip-<br>tion in PWM Control 0 Register (PWMCTL0)<br>table; corrected description in PWM Dead-<br>band Register (PWMDB) table and added<br>footnote; added same footnote to PWM Mini-<br>mum Pulse Width Filter (PWMMPF), PWM<br>Fault Mask Register (PWMFM), and PWM<br>Fault Control Register (PWMFCTL) tables. |             |  |  |

| Jun<br>2011 | 09                | Electrical Characteristics    | Corrected V <sub>COFF</sub> input offset value in Com-<br>parator Electrical Characteristics table                                                                                                                                                                                                                                                 | <u>347</u>  |  |  |

| Aug         | 08                | N/A                           | Removed ISO information.                                                                                                                                                                                                                                                                                                                           | <u>ii</u>   |  |  |

| 2010        |                   | All                           | Updated logos.                                                                                                                                                                                                                                                                                                                                     | All         |  |  |

|             |                   | Table 191                     | Changed the Minimum, Typical and Maxi-<br>mum values for V <sub>REF</sub> (Externally supplied<br>Voltage Reference only).                                                                                                                                                                                                                         | <u>346</u>  |  |  |

| Jan<br>2009 | 07                | Timer 0–2 Control 0 Register  | Table 62: added "Only Counter Mode should be used with this feature" to Bit 4 description.                                                                                                                                                                                                                                                         | <u>109</u>  |  |  |

|             |                   | Analog Functions              | ADC Overview, updated fast conversion time to $2.5 \mu s$ .                                                                                                                                                                                                                                                                                        | <u>243</u>  |  |  |

|             |                   | Electrical Characteristics    | Updated Table 185.                                                                                                                                                                                                                                                                                                                                 | <u>337</u>  |  |  |

|             |                   | Internal Precision Oscillator | Removed reference to 32kHz.                                                                                                                                                                                                                                                                                                                        | <u>336</u>  |  |  |

# ZNEO<sup>®</sup> Z16F Series MCUs Product Specification

| Table 136. | Flash Memory Configurations    255                      |

|------------|---------------------------------------------------------|

| Table 137. | Flash Memory Sector Addresses    255                    |

| Table 138. | ZNEO Z16F Series Information Area Map 257               |

| Table 139. | Flash Command Register (FCMD) 261                       |

| Table 140. | Flash Status Register (FSTAT)    262                    |

| Table 141. | Flash Control Register (FCTL)    263                    |

| Table 142. | Flash Sector Protect Register (FSECT)    264            |

| Table 143. | Flash Page Select Register (FPAGE)    265               |

| Table 144. | Flash Frequency Register (FFREQ)    266                 |

| Table 145. | Linked List Descriptor                                  |

| Table 146. | DMA Priority                                            |

| Table 147. | DMA Bandwidth Selection                                 |

| Table 148. | DMA Select Register (DAMxREQSEL)                        |

| Table 149. | DMA Control Register A (DMAxCTL)                        |

| Table 150. | DMA X Transfer Length High Register (DMAxTXLNH)         |

| Table 151. | DMA X Transfer Length Low Register (DMAxTXLNL)          |

| Table 152. | DMA X Destination Address Register Upper (DMAxDARU) 287 |

| Table 153. | DMA X Destination Address Register High (DMAxDARH) 287  |

| Table 154. | DMA X Destination Address Register Low (DMAxDARL)       |

| Table 155. | DMA X Source Address Register Upper DMAxSARU            |

| Table 156. | DMA X Source Address Register High (DMAxSARH) 288       |

| Table 157. | DMA X Source Address Register Low (DMAxSARL)            |

| Table 158. | DMA X List Address Register Upper DMAxLARU              |

| Table 159. | DMA X List Address Register High (DMAxLARH) 289         |

| Table 160. | DMA X List Address Register Low (DMAxLARL)              |

| Table 161. | Option Bits At Program Memory Address 0000h 293         |

| Table 162. | Options Bits at Program Memory Address 0001h 294        |

| Table 163. | Options Bits at Program Memory Address 0002h 295        |

| Table 164. | Options Bits at Program Memory Address 0003h 295        |

| Table 165. | IPO Trim 1 (IPOTRIM1)                                   |

| Table 166. | IPO Trim 2 (IPOTRIM2)                                   |

| Table 167. | ADC Reference Voltage Trim (ADCTRIM)                    |

| Table 168. | OCD Baud Rate Limits                                    |

| Table 169. | On-Chip Debugger Commands                               |

| Table 170. | Receive Data Register (DBGRXD)                          |

| Table 171. | Transmit Data Register (DBGTXD)                         |

### **Brackets**

The square brackets, [], indicate a register or bus.

**Example.** For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

### Braces

The curly braces { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

**Example.** The 12-bit register address {0h, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0h) and two 4-bit register values taken from the register pointer (RP) and working register R1. 0h is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

# Parentheses

The parentheses (), indicate an indirect register address lookup.

**Example.** (R1) is the memory location referenced by the address contained in the working register R1.

# Parentheses/Bracket Combinations

The parentheses (), indicate an indirect register address lookup and the square brackets [], indicate a register or bus.

**Example.** Assume PC[15:0] contains the value 1234h. (PC[15:0]) refers to the contents of the memory location at the address 1234h.

# Use of the Words Set, Reset, and Clear

The word set implies that a register bit or a condition contains a logical 1. The words reset or clear imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word logical may not be included; however, it is implied.

# Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[n:n].

**Example.** ADDR[15:0] refers to bit 15 through bit 0 of the address.

| Internal I/O Memory            | FF_FFFFh - Top of I/O Memory<br>FF_E000h - Bottom of I/O Memory<br>FF DFFFh     |

|--------------------------------|---------------------------------------------------------------------------------|

| External Memory                |                                                                                 |

| Internal RAM                   | FF_C000h<br>FF_BFFFh - Top of Internal RAM<br>XX XXXXH - Bottom of Internal RAM |

|                                | (device specific)                                                               |

|                                |                                                                                 |

| External Memory                |                                                                                 |

|                                |                                                                                 |

|                                |                                                                                 |

|                                |                                                                                 |

| Internal nonvolatile<br>Memory | XX_XXXH - Top of Internal nonvolatile Memory<br>(device specific)               |

|                                | 00_0000h - Bottom of Internal nonvolatile Memory                                |

Figure 6. Physical Memory Map

To determine the amount of internal RAM and internal nonvolatile memory available for the specific device, see the <u>Ordering Information</u> section on page 356.

# **Internal Nonvolatile Memory**

Internal nonvolatile memory contains executable program code, constants and data. For each product within the ZNEO CPU family, a memory block beginning at address 00\_0000h is reserved for user option bits and system vectors (for example, RESET, Trap, Interrupts and System Exceptions, etc.). Table 4 provides an example of reserved memory map for a ZNEO CPU product with 24 interrupt vectors.

| Address (Hex)        | Register Description                   | Mnemonic                          | Reset (Hex) | Page No   |

|----------------------|----------------------------------------|-----------------------------------|-------------|-----------|

| FF_E132              | Port D Data Direction                  | PDDD                              | 00          | <u>73</u> |

| FF_E133              | Port D High Drive Enable               | PDHDE                             | 00          | <u>74</u> |

| FF_E134              | Port D Alternate Function High         | PDAFH                             | 00          | <u>75</u> |

| FF_E135              | Port D Alternate Function Low          | PDAFL                             | 00          | <u>76</u> |

| FF_E136              | Port D Output Control                  | PDOC                              | 00          | <u>76</u> |

| FF_E137              | Port D Pull-Up Enable                  | PDPUE                             | 00          | <u>76</u> |

| FF_E138              | Port D Stop Mode Recovery<br>Enable    | PDSMRE                            | 00          | 77        |

| FF_E139-FF_E13F      | Port D Reserved                        | —                                 | _           | _         |

| GPIO Port E Base Ade | dress = FF_E140                        |                                   |             |           |

| FF_E140              | Port E Input Data                      | PEIN                              | XX          | <u>71</u> |

| FF_E141              | Port E Output Data                     | PEOUT                             | 00          | <u>72</u> |

| FF_E142              | Port E Data Direction                  | PEDD                              | 00          | <u>73</u> |

| FF_E143              | Port E High Drive Enable               | PEHDE                             | 00          | <u>74</u> |

| FF_E144              | Reserved                               | _                                 | _           | _         |

| FF_E145              | Reserved                               | —                                 | —           | _         |

| FF_E146              | Port E Output Control                  | PEOC                              | 00          | <u>76</u> |

| FF_E147              | Port E Pull-Up Enable                  | rt E Pull-Up Enable PEPUE 00      |             | <u>76</u> |

| FF_E148              | Port E Stop Mode Recovery<br>Enable    | PESMRE                            | 00          | <u>77</u> |

| FF_E149-FF_E14F      | Port E Reserved                        | —                                 | _           | _         |

| GPIO Port F Base Add | dress = FF_E150                        |                                   |             |           |

| FF_E150              | Port F Input Data                      | PFIN                              | XX          | <u>71</u> |

| FF_E151              | Port F Output Data                     | PFOUT                             | 00          | <u>72</u> |

| FF_E152              | Port F Data Direction                  | PFDD                              | 00          | <u>73</u> |

| FF_E153              | Port F High Drive Enable               | Port F High Drive Enable PFHDE 00 |             | <u>74</u> |

| FF_E154              | Reserved                               | Reserved — —                      |             | _         |

| FF_E155              | Port F Alternate Function Low PFAFL 00 |                                   | 00          | <u>76</u> |

| FF_E156              | Port F Output Control PFOC 00          |                                   | 00          | <u>76</u> |

| FF_E157              | Port F Pull-Up Enable                  | Port F Pull-Up Enable PFPUE 00    |             | <u>76</u> |

| FF_E158              | Port F Stop Mode Recovery<br>Enable    |                                   |             | 77        |

| FF_E159-FF_E15F      | Port F Reserved                        |                                   |             | _         |

| XX - Undefined       |                                        |                                   |             |           |

XX = Undefined.

| 9 | 4 |

|---|---|

|---|---|

| Bit                        | Description                                       |

|----------------------------|---------------------------------------------------|

| [4]<br>PWMFENL             | PWM Fault Interrupt Request Enable Low Bit.       |

| [3:0]<br>CxENL/<br>DMAxENL | Port Cx or DMAx Interrupt Request Enable Low Bit. |

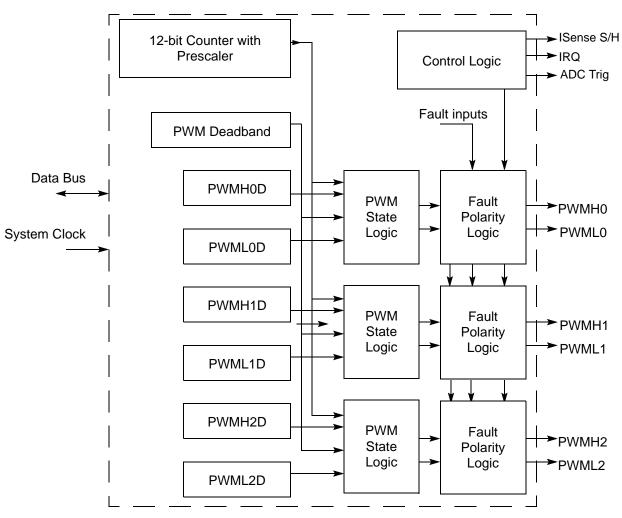

Figure 21. PWM Block Diagram

# Operation

### **PWM Option Bits**

To protect the configuration of critical PWM parameters, settings to enable output channels and the default off-state are maintained as user option bits. These values are set when the user program code is written to the part; the software cannot change these values. For more, see the <u>Option Bits</u> chapter on page 292.

# PWM 0–2 Duty Cycle High and Low Byte Registers

The PWM 0–2 H/L (High Side/Low Side) Duty Cycle High and Low Byte (PWMxDH and PWMxDL) registers, shown in Tables 68 and 69, set the duty cycle of the PWM signal. This 14-bit signed value is compared to the PWM count value to determine the PWM output. Reads from these registers always return the values from the temporary holding registers. The PWM generator does not use the PWM duty cycle value until the next PWM reload event occurs.

$PWM Duty Cycle = 100 \times \frac{PWM Duty Cycle Value}{PWM Reload Value}$

Writing a negative value (DUTYH[7] = 1) forces the PWM to be OFF for the full PWM period. Writing a positive value greater than the 12-bit PWM reload value forces the PWM to be ON for the full PWM period.

#### Table 68. PWM 0–2 H/L Duty Cycle High Byte Register (PWMHxDH, PWMLxDH)

| Bits  | 7                  | 6        | 5 | 4         | 3         | 2         | 1        | 0 |  |  |

|-------|--------------------|----------|---|-----------|-----------|-----------|----------|---|--|--|

| Field | SIGN               | Reserved |   |           | DUTYH     |           |          |   |  |  |

| RESET | Х                  | XX       |   | X_XXXX    |           |           |          |   |  |  |

| R/W   | R/W                | R/W      |   |           |           | R/W       |          |   |  |  |

| Addr  | FF_E390h, FF_E392h |          |   | FF_E394h, | FF_E396h, | FF_E398h, | FF_E39Ah |   |  |  |

| Bit            | Description                                                                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>SIGN    | <ul> <li>Duty Cycle Sign</li> <li>0 = Duty cycle is a positive two's complement number.</li> <li>1 = Duty cycle is a negative two's complement number. Output is forced to the off-state.</li> </ul>                                       |

| [6:5]          | Reserved<br>These bits are reserved and must be programmed to 00.                                                                                                                                                                          |

| [4:0]<br>DUTYH | <b>PWM Duty Cycle High and Low Bytes</b><br>The upper byte of two bytes {DUTYH[7:0], DUTYL[7:0]} that form a 14-bit signed value; bits<br>5 and 6 of the High byte are always 0. The value is compared to the current 12-bit PWM<br>count. |

| Description (Continued)                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Fault 0 Interrupt                                                                                                                        |

| 0 = Interrupt on fault 0 pin assertion disabled.                                                                                         |

| 1 = Interrupt on Fault0 pin assertion enabled.                                                                                           |

| Fault 0 Restart                                                                                                                          |

| 0 = Automatic recovery. PWM resumes control of outputs when all fault sources have deas-<br>stered.                                      |

| Software Controlled Recovery                                                                                                             |

| 1 = PWM resumes control of outputs only after all fault sources have deasserted and all fault flags are cleared and a PWM reload occurs. |

|                                                                                                                                          |

# **PWM Input Sample Register**

The PWM pin value is sampled by reading the PWM Input Sample Register, shown in Table 77.

Table 77. PWM Input Sample Register (PWMIN)

| Bits  | 7        | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|----------|-------|------|------|------|------|------|------|

| Field | Reserved | FAULT | IN2L | IN2H | IN1L | IN1H | INOL | IN0H |

| RESET | 0        | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R        | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Addr  | FF_E386h |       |      |      |      |      |      |      |

| Bit                                            | Description                                                                                                                  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| [7]                                            | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                         |

| [6]<br>FAULT                                   | Sample Fault0 pin<br>0 = A Low-level signal was read on the fault pin.<br>1 = A High-level signal was read on the fault pin. |

| [5:0]<br>IN2L/IN2H/<br>IN1L/IN1H/<br>IN0L/IN0H | Sample PWM Pins<br>0 = A Low-level signal was read on the pins.<br>1 = A High-level signal was read on the pins.             |

passed to the UART. Communication is half-duplex, which means that simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bps) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

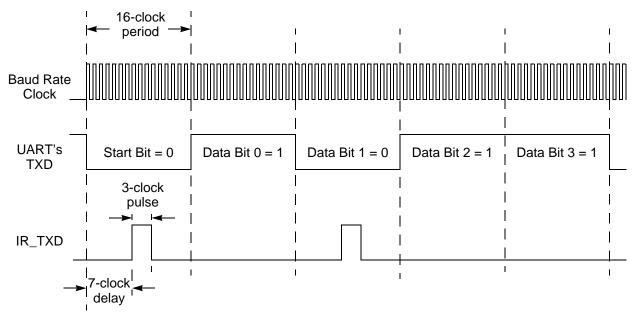

# **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains Low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 33 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the ZNEO Z16F Series products while the IR\_TXD signal is output through the TXD pin.

Figure 33. Infrared Data Transmission

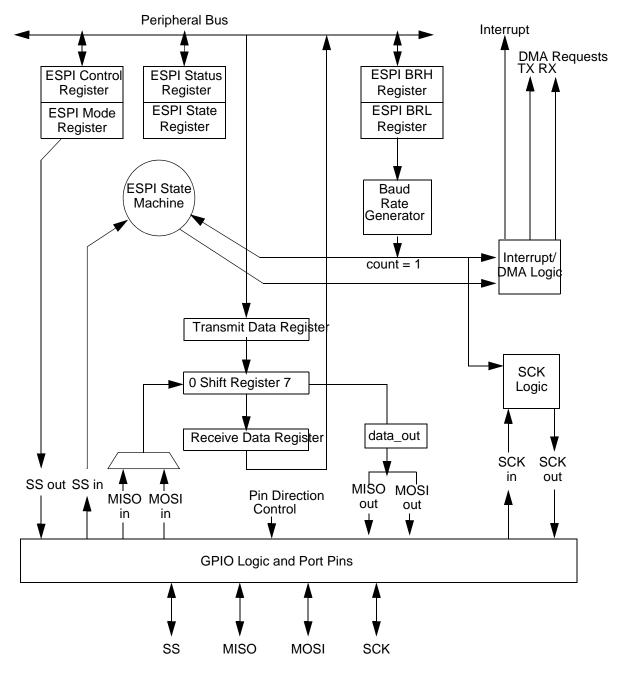

Figure 35. ESPI Block Diagram

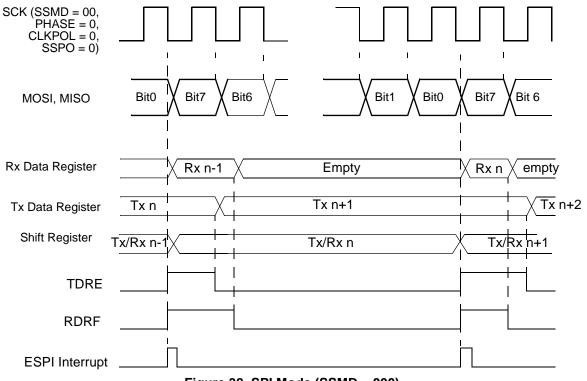

Figure 38. SPI Mode (SSMD = 000)

### I2S (Inter-IC Sound) Mode

This mode is selected by setting the SSMD field of the mode register to 010. The PHASE and CLKPOL bits of the control register must be set to 0. This mode is illustrated in Figure 39 with  $\overline{SS}$  alternating between consecutive frames. A frame consists of a fixed number of data bytes as defined in the DMA buffer descriptor or by software. I<sup>2</sup>S (Inter-IC Sound) mode is typically used to transfer left or right channel audio data.

The SSV indicates whether the corresponding bytes are left or right channel data. The SSV value must be updated when servicing the TDRE interrupt/request for the first byte in a left or write channel frame. This update is accomplished by performing a word write when writing the first byte of the audio word, which updates both the ESPI data and transmit data command words or by doing a byte write to update SSV followed by a byte write to the data register. The SS signal leads the data by one SCK period.

If a DMA Channel is controlling data transfer each sequence of left (or right) channel byte is considered a frame with a buffer descriptor. The SSV bit is defined in the buffer descriptor command field and is automatically written to the transmit data command register just prior to or in synchronous with the first data byte of the frame being written. Note that the

• Support for multi-master environments. If arbitration is lost when operating as a Master, the ARBLST bit in the I2CISTAT Register is set and the mode automatically switches to Slave Mode.

# Operation

The I<sup>2</sup>C Master/Slave Controller operates in either Slave Only Mode or Master/Slave Mode with Master arbitration. In Master/Slave Mode, it is used as the only Master on the bus or as one of several Masters on the bus with arbitration. In a multi-Master environment, the controller switches from Master to Slave Mode on losing arbitration.

Though slave operation is fully supported in Master/Slave Mode, if a device is intended to operate only as a slave, the Slave Only Mode is selected. In Slave Only Mode, the device does not initiate a transaction even if software inadvertently sets the Start bit.

# **SDA and SCL Signals**

I<sup>2</sup>C sends all addresses, data and acknowledge signals over the SDA line, the most-significant bit first. SCL is the clock for the I<sup>2</sup>C bus. When the SDA and SCL pin alternate functions are selected for their respective GPIO ports, the pins are automatically configured for open-drain operation.

The Master is responsible for driving the SCL clock signal. During the Low period of the clock, a Slave holds the SCL signal Low to suspend the transaction if it is not ready to proceed. The Master releases the clock at the end of the Low period and notices that the clock remains Low instead of returning to a High level. When the Slave releases the clock, the I<sup>2</sup>C Master continues the transaction. All data is transferred in bytes and there is no limit to the amount of data transferred in one operation. When transmitting address, data or acknowledge, the SDA signal changes in the middle of the Low period of SCL. When receiving address, data, or acknowledge, the SDA signal is sampled in the middle of the High period of SCL.

A low-pass digital filter is applied to the SDA and SCL receive signals by setting the filter enable (FILTEN) bit in the I<sup>2</sup>C Control Register. When the filter is enabled, any glitch, which is less than a system clock period in width is rejected. This filter must be enabled when running in I<sup>2</sup>C Fast Mode (400 kbps) and is also used at lower data rates.

# I<sup>2</sup>C Interrupts

The I<sup>2</sup>C Controller contains multiple interrupt sources that are combined into one interrupt request signal to the interrupt controller. If the I<sup>2</sup>C Controller is enabled, the source of the interrupt is determined by bits, which are set in the I2CISTAT Register. If the I<sup>2</sup>C Controller is disabled, the BRG Controller is used to generate general-purpose timer interrupts.

- 7. When the Master receives the data byte, the Master transmits an Acknowledge instruction (or Not Acknowledge instruction for the last data byte).

- 8. The bus cycles through steps 5–7 until the last byte has been transferred. If software has not yet loaded the next data byte when the Master brings SCL Low to transfer the most significant data bit, the Slave I<sup>2</sup>C Controller holds SCL Low until the data register is written. When the Slave receives a Not Acknowledge instruction, the I<sup>2</sup>C Controller sets the NCKI bit in the I2CISTAT Register and generates the Not Acknowledge interrupt.

- 9. Software responds to the Not Acknowledge interrupt by clearing the TXI bit in the I2CCTL Register and by asserting the FLUSH bit of the I2CCTL Register to empty the data register.

- 10. When the Master completes the last acknowledge cycle, it asserts the Stop or Restart condition on the bus.

- 11. The Slave I<sup>2</sup>C Controller asserts the Stop/Restart interrupt (set the SPRS bit in I2CISTAT Register).

- 12. Software responds to the Stop/Restart interrupt by reading the I2CISTAT Register which clears the SPRS bit.

### Slave Transmit (Master Read) Transaction with 10-Bit Address

Figure 51 displays the data transfer format for a Master reading data from a Slave with 10-Bit Addressing.

| S | Slave Address<br>1st Byte | W=0 | A | Slave Address<br>2nd Byte | A | s | Slave Address<br>1st Byte | R=1 | А | Data | А | Data | А | Ρ |

|---|---------------------------|-----|---|---------------------------|---|---|---------------------------|-----|---|------|---|------|---|---|

|---|---------------------------|-----|---|---------------------------|---|---|---------------------------|-----|---|------|---|------|---|---|

Figure 51. Data Transfer Format, Slave Transmit Transaction with 10-Bit Addressing

The following procedure describes the I<sup>2</sup>C Master/Slave Controller operating as a Slave in 10-Bit Addressing Mode, transmitting data to the bus Master:

- 1. Software configures the controller for operation as a Slave in 10-Bit Addressing Mode.

- Initialize the MODE field in the I<sup>2</sup>C Mode Register for either Slave Only Mode or Master/Slave Mode with 10-Bit Addressing.

- Optionally set the GCE bit.

- Initialize the SLA[7:0] bits in the I2CSLVAD Register and SLA[9:8] in the I2CMODE Register.

- Set IEN = 1, NAK = 0 in the  $I^2C$  Control Register.

- Program the Baud Rate High and Low Byte registers for the  $I^2C$  baud rate.

# ADC0 Data Low Bits Register

The ADC0 Data Low Bits Register contains the lower bits of the ADC0 output. Access to the ADC0 Data Low Bits Register is Read-Only.

#### Table 128. ADC0 Data Low Bits Register (ADC0D\_L)

| Bits  | 7   | 6    | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|------|----------|---|---|---|---|---|--|--|

| Field | ADC | 0D_L | Reserved |   |   |   |   |   |  |  |

| RESET | )   | X    |          |   | ) | K |   |   |  |  |

| R/W   | F   | २    |          |   | F | २ |   |   |  |  |

| Addr  |     |      | FF–E503h |   |   |   |   |   |  |  |

|       | _   | _    |          |   |   |   |   |   |  |  |

| Bit              | Description                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>ADC0D_L | ADC0 Low Bits<br>00–11b = These bits are the 2 least significant bits of the 10-bit ADC0 output. These bits are<br>undefined after a Reset. |

| [5:0]            | <b>Reserved</b> These bits are reserved and must be programmed to 0.                                                                        |

# Sample Settling Time Register

The Sample Settling Time Register is used to program the length of time from the SAM-PLE/HOLD signal to the Start signal, when the conversion begins. The number of clock cycles required for settling varies from system to system depending on the system clock period used. This register must be programmed to contain the number of clocks required to meet a  $0.5 \,\mu$ s minimum settling time.

| Table 129. | Sample and | Settling | J Time (ADCSST) |

|------------|------------|----------|-----------------|

|------------|------------|----------|-----------------|

| Bits         | 7                      | 6                                                                                                                     | 5 | 4 | 3   | 2 | 1 | 0 |  |  |  |  |

|--------------|------------------------|-----------------------------------------------------------------------------------------------------------------------|---|---|-----|---|---|---|--|--|--|--|

| Field        | Reserved               |                                                                                                                       |   |   | SST |   |   |   |  |  |  |  |

| RESET        | 0 0 0 1 1 1 1          |                                                                                                                       |   |   |     |   |   |   |  |  |  |  |

| R/W          |                        | R R/W                                                                                                                 |   |   |     |   |   |   |  |  |  |  |

| Addr         |                        | FF–E504h                                                                                                              |   |   |     |   |   |   |  |  |  |  |

| Bit          | Descriptio             | n                                                                                                                     |   |   |     |   |   |   |  |  |  |  |

| [7:5]        | Reserved<br>These bits | Reserved<br>These bits are reserved and must be programmed to 0.                                                      |   |   |     |   |   |   |  |  |  |  |

| [4:0]<br>SST | -                      | Sample Settling Time<br>$00h-1Fh = Sample settling time in number of system clock periods to meet 0.5 \mu s minimum.$ |   |   |     |   |   |   |  |  |  |  |

# **Buffer Closure**

A DMA buffer closure is requested in two ways. The first is when the transfer length reaches zero. The second is when the DMA receives a request end of frame from the peripheral. When either of these cases occur, the DMA begins closure of the buffer.

### Loop Mode Closure

If the LOOP bit is set then the current buffer descriptor is not modified. The DMAxLAR increments or a new LAR value is fetched from the descriptor.

### **EOF Closure**

The DMAxEN bit is reset to 0. If the EOF bit is set, the CMDSTAT field is set with the status data from the peripheral. If the channel is in LINKED LIST Mode then the DMAx-CTL word is written back to the CONTROL word of the descriptor. The DMAxLAR increments or is loaded with new LAR data from the descriptor if the TXFR bit is set.

### **Normal Closure**

The DMAxEN bit is reset to 0. If the channel is in LINKED LIST Mode then the DMAx-CTL word is written back to the CONTROL word of the descriptor. The DMAxLAR increments or is loaded with new LAR data from the descriptor if the TXFR bit is set.

# **DMA Modes**

Each DMA channel operates in two modes, direct and linked list. Both modes use the DMA Channel registers. The only difference is in how they are loaded. In DIRECT Mode, the DMA Channel registers are directly loaded by software and when the transfer is complete, the DMA stops. In LINKED LIST Mode, the DMA will load its own registers from a descriptor list which is pointed to by the DMAxLAR Register. It then loads the next descriptor in the list and continues executing.

The descriptor Control/Status field and address bytes maintain the same format as the control and address registers in the DMA.

### **Direct Mode**

DIRECT Mode only uses the registers in the DMA for operation. The software writes these registers directly to set up and enable the DMA. DIRECT Mode is entered by directly setting the DMAxEN bit in the DMAxCTL0 Register.

Figure 58 displays the DMA registers and how they point to the buffers allocated in memory.

# Program Memory Address 0002h

Option Bits in this space are altered to change the chip configuration at reset.

#### Table 163. Options Bits at Program Memory Address 0002h

| Bits      | 7                    | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|----------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|--|

| Field     |                      | Reserved     |                |     |     |     |     |     |  |  |  |  |

| RESET     | U                    | U            | U              | U   | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                  | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Addr      | Program Memory 0002h |              |                |     |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b          | y Reset. R/W | / = Read/Write | е.  |     |     |     |     |  |  |  |  |

#### Bit Description

#### [7:0] Reserved

These option bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

# Program Memory Address 0003h

Option bits in this space are altered to change the chip configuration at reset.

### Table 164. Options Bits at Program Memory Address 0003h

| Bits      | 7                                               | 6     | 5        | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-------|----------|-----|-----|-----|-----|-----|--|--|--|

| Field     | ROMLESS 16                                      | LPOPT | Reserved |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U     |          |     |     |     |     |     |  |  |  |

| R/W       | R/W                                             | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Addr      | Addr Program Memory 0003h                       |       |          |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |       |          |     |     |     |     |     |  |  |  |

| Bit        | Description                                                                             |

|------------|-----------------------------------------------------------------------------------------|

| [7]        | ROMLESS 16 Select                                                                       |

| ROMLESS 16 | 0 = If the device is ROMLESS, the data bus is 8 bits wide and is on Port E[7:0].        |

|            | 1 = If the device is ROMLESS, the data bus is 16 bits wide and is on {Port J[7:0], Port |

|            | E[7:0]}                                                                                 |

The UARTEN control bit must be set to 1 to use the serial interface as a UART. Clearing the UARTEN control bit to 0 will prevent data received on the DBG pin from being written to the Receive Data register. Clearing the UARTEN control bit to 0 also prevents data written to the Transmit Data register from being transmitted on the single pin interface.

If the UART is disabled, data is still written to the Receive Data register and read from the Transmit Data register. These actions still generates UART interrupts. The UARTEN control bit only prevents data from being transmitted to or received from the DBG pin.

### **Serial Errors**

The serial interface detects the following error conditions:

- Receive framing error (received Stop bit is Low)

- Transmit collision (OCD releases the bus high to send a logic 1 and detects it is Low)

- Receive overrun (received data before previously received data read)

- Receive break detect (10 or more bits Low)

Transmission of data is prevented if the transmit collision, receive framing error, receive break detect, receive overrun, or Receive Data Register full status bits are set.

### Interrupts

The Debug UART generates interrupts during the following conditions:

- Receive Data register is Full (includes Rx Framing Error and Rx Overrun Error)

- Transmit Data register is empty

- Auto-Baud Detector loads the BRG (auto-baud character received)

- Receive Break detected

### DBG Pin as a GPIO Pin

The DBG pin is used as a GPIO pin. The serial interface cannot be used for debugging when the DBG pin is configured as a GPIO pin. To set up the DBG pin as a GPIO pin, software must clear the DBGUART option bit and OCDEN control bit.

Software uses the pin as an input by clearing the output enable control bit. The PIN status bit in Line Control Register (DBGLCR) reflects the state of the DBG pin.

The DBG pin is configured as an output pin by setting the output enable control bit. The logic state of the IDLE bit in Line Control Register is driven onto the DBG pin.

| ົ | ົ | 2 |

|---|---|---|

| ు | J | 2 |

| Table 182. Oscillator Configuration and Selection |

|---------------------------------------------------|

|---------------------------------------------------|

| Clock Source                                               | Characteristics                                                                                                                                               | Required Setup                                                                                                                 |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>Oscillator                           | <ul> <li>5.5 MHz</li> <li>High precision possible when trimmed</li> <li>No external components required</li> </ul>                                            | The reset default.                                                                                                             |

| External Crystal/<br>Resonator/<br>External Clock<br>Drive | <ul> <li>0 to 20 MHz</li> <li>Very high accuracy (dependent<br/>on crystal/resonator or external<br/>source)</li> <li>Requires external components</li> </ul> |                                                                                                                                |

| Internal Watch-<br>dog Timer Oscil-<br>lator               | <ul> <li>10 kHz nominal</li> <li>Low accuracy</li> <li>No external components required</li> <li>Low power consumption</li> </ul>                              | <ul> <li>Unlock and write Oscillator Control Register<br/>(OSCCTL) to enable and select Internal WDT<br/>oscillator</li> </ul> |

Unintentional access to the Oscillator Control Register (OSCCTL) stops the chip by switching to a nonfunctioning oscillator. Accidental alteration of the OSCCTL Register is prevented by a locking/unlocking scheme. To write the register, unlock it by making two writes to the OSCCTL Register with the values E7h followed by 18h. A third write to the OSCCTL Register then changes the value of the register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but is not required to be consecutive. It is possible to access other registers within the locking/unlocking operation.

### **Clock Selection Following System Reset**

The internal precision oscillator is selected following a System Reset. Startup code after the System Reset changes the system clock source by unlocking and configuring the OSC-CTL Register. If the LPOPT bit in Program Memory Address 0003h is zero, Flash Low Power Mode is enabled during reset. When Flash Low Power Mode is enabled during reset, the FLPEN bit in the Oscillator Control Register (OSCCTL) will be set and the DIV field of the OSCDIV Register will be set to 08h.

# **Oscillator Divide Register**

The Oscillator Divide Register (OSCDIV), shown in Table 184, provides the value to divide the system clock by. The Oscillator Divide Register must be unlocked before writing. Writing the two-step sequence E7h followed by 18h to the Oscillator Control Register address unlocks it. The register locks after completion of a register write to the OSCDIV.

| Bits       | 7             | 6                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|------------|---------------|--------------------------------------------------|---|---|---|---|---|---|--|--|--|--|

| Field      |               | DIV                                              |   |   |   |   |   |   |  |  |  |  |

| RESET      |               | 00h*                                             |   |   |   |   |   |   |  |  |  |  |

| R/W        |               |                                                  |   | R | W |   |   |   |  |  |  |  |

| Addr       |               | FF_E0A1h                                         |   |   |   |   |   |   |  |  |  |  |

| Note: *The | e reset value | reset value is 08h if the option bit LPOPT is 0. |   |   |   |   |   |   |  |  |  |  |

|            |               |                                                  |   |   |   |   |   |   |  |  |  |  |

#### Table 184. Oscillator Divide Register (OSCDIV)

| Bit          | Value (H) | Description                                                                                                                    |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>DIV | 00h-FFh   | <b>Oscillator Divide</b><br>00h–divider is disabled; all other entries are the divide value for scaling the sys-<br>tem clock. |