Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Obsolete                                                        |

| Core Processor             | XCore                                                           |

| Core Size                  | 32-Bit 24-Core                                                  |

| Speed                      | 4000MIPS                                                        |

| Connectivity               | USB                                                             |

| Peripherals                | -                                                               |

| Number of I/O              | 176                                                             |

| Program Memory Size        | 2MB (2M x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | •                                                               |

| RAM Size                   | 1M x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                    |

| Data Converters            | •                                                               |

| Oscillator Type            | External                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

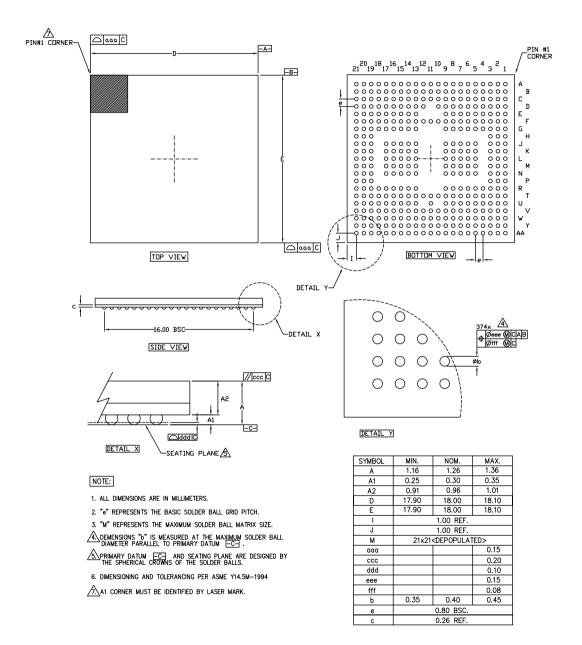

| Package / Case             | 374-LFBGA                                                       |

| Supplier Device Package    | 374-FBGA (18x18)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xuf224-1024-fb374-i40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Signal Function Type Properties X3D42 8D<sup>6</sup> 16B<sup>14</sup> I/O IOT, PD

X3D43

|              | System pins (4)     |            |             |  |  |  |  |  |  |

|--------------|---------------------|------------|-------------|--|--|--|--|--|--|

| Signal       | Function            | Properties |             |  |  |  |  |  |  |

| CLK          | PLL reference clock | Input      | IOL, PD, ST |  |  |  |  |  |  |

| GLOBAL_DEBUG | Multi-chip debug    | I/O        | IOL, PU     |  |  |  |  |  |  |

| MODE0        | Boot mode select    | Input      | PU          |  |  |  |  |  |  |

| MODE1        | Boot mode select    | Input      | PU          |  |  |  |  |  |  |

8D<sup>7</sup>

16B<sup>15</sup>

I/0

IOT, PD

|             | usb pins (10) |      |            |

|-------------|---------------|------|------------|

| Signal      | Function      | Туре | Properties |

| USB_DM_0    |               | I/O  |            |

| USB_DM_1    |               | I/O  |            |

| USB_DP_0    |               | I/O  |            |

| USB_DP_1    |               | I/O  |            |

| USB_ID_0    |               | I/O  |            |

| USB_ID_1    |               | I/O  |            |

| USB_RTUNE_0 |               | I/O  |            |

| USB_RTUNE_1 |               | I/0  |            |

| USB_VBUS_0  |               | I/0  |            |

| VUSB_BUS_1  |               | I/0  |            |

-XMOS<sup>®</sup>

-XMOS°

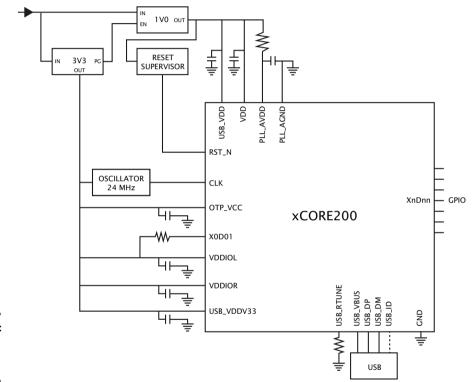

Figure 2: Simplified Reference Schematic

- A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- ▶ A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

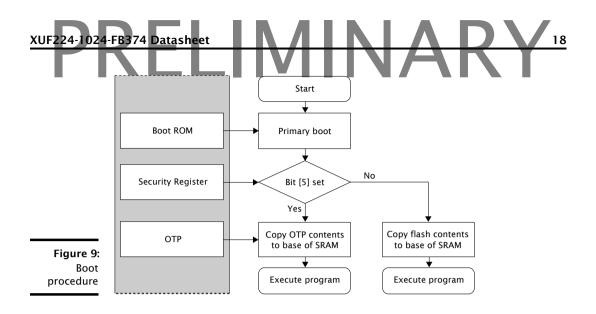

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 8.1 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

#### 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

#### 12.2.1 General routing and placement guidelines

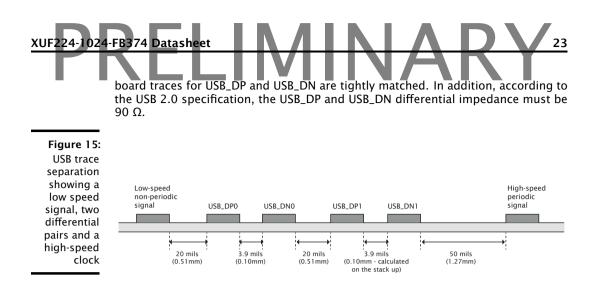

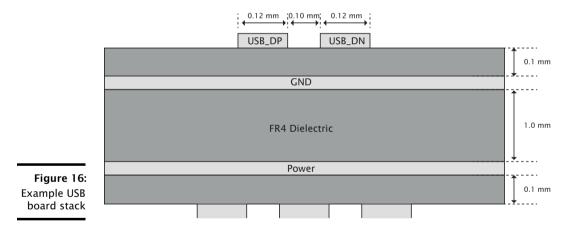

The following guidelines will help to avoid signal quality and EMI problems on high speed USB designs. They relate to a four-layer (Signal, GND, Power, Signal) PCB.

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-UF24A-1024-FB374 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

#### 13.1 Operating Conditions

| Symbol     | Parameter                                     | MIN   | TYP  | MAX   | UNITS | Notes |

|------------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD        | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIO      | I/O supply voltage                            | 2.30  | 3.30 | 3.60  | V     |       |

| VDDIOT 3v3 | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| VDDIOT 2v5 | I/O supply voltage                            | 2.375 | 2.50 | 2.625 | V     |       |

| VDD33      | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD   | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| CI         | xCORE Tile I/O load<br>capacitance            |       |      | 25    | pF    |       |

| Та         | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|            | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Тј         | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg       | Storage temperature                           | -65   |      | 150   | °C    |       |

Figure 17: Operating conditions

Figure 18: DC characteristics

#### 13.2 DC Characteristics

| Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | А     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | А     |

| V(OH)  | Output high voltage  | 2.20  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.40 | V     | B, C  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

A All pins except power supply pins.

B All general-purpose I/Os are nominal 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

#### 13.3 ESD Stress Voltage

| Figure 19: | Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|------------|--------|----------------------|-------|-----|------|-------|-------|

| ESD stress | HBM    | Human body model     | -2.00 |     | 2.00 | KV    |       |

| voltage    | CDM    | Charged Device Model | -500  |     | 500  | V     |       |

-XMOS

XS2-UF24A-1024-FB374

## XUF224-1024-FB374 Datasheet 30

-XMOS

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | control-token |

|---------------|------------------------|-----------------|-------|---------------|

| 37            | channel-end identifier | register number | size  | 1             |

The response to the read message comprises either control token 3, data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

| XUF224-1024-1 | FB374 D | atashee | et   |             | ΝΙ           | Λ | D | V | 37 |

|---------------|---------|---------|------|-------------|--------------|---|---|---|----|

|               |         |         |      |             | $\mathbf{I}$ | A | Γ |   |    |

|               | Bits    | Perm    | Init | Description |              |   |   |   |    |

| Bits  | Perm | Init | Description                                                                                                                                                                                                                               |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                                |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1     |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                       |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock<br>divider is enabled. In dynamic mode the clock divider is only<br>activated when all active threads are paused. In static mode the<br>clock divider is always enabled. |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                    |

| 3     | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 2     | RW   |      | Select between UTMI (1) and ULPI (0) mode.                                                                                                                                                                                                |

| 1     | RW   |      | Enable the ULPI Hardware support module                                                                                                                                                                                                   |

| 0     | RO   | -    | Reserved                                                                                                                                                                                                                                  |

0x02: xCORE Tile control

#### B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS<sup>®</sup>

| Bits  | Perm | Init | Description                                               |

|-------|------|------|-----------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                  |

| 23:16 | RO   |      | Processor number.                                         |

| 15:9  | RO   | -    | Reserved                                                  |

| 8     | RO   |      | Overwrite BOOT_MODE.                                      |

| 7:6   | RO   | -    | Reserved                                                  |

| 5     | RO   |      | Indicates if core1 has been powered off                   |

| 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| 3     | RO   |      | Boot ROM boots from RAM                                   |

| 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03 xCORE Tile boot status

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31    | RW   |      | Disables write permission on this register                  |

| 30:15 | RO   | -    | Reserved                                                    |

| 14    | RW   |      | Disable access to XCore's global debug                      |

| 13    | RO   | -    | Reserved                                                    |

| 12    | RW   |      | lock all OTP sectors                                        |

| 11:8  | RW   |      | lock bit for each OTP sector                                |

| 7     | RW   |      | Enable OTP reduanacy                                        |

| 6     | RO   | -    | Reserved                                                    |

| 5     | RW   |      | Override boot mode and read boot image from OTP             |

| 4     | RW   |      | Disable JTAG access to the PLL/BOOT configuration registers |

| 3:1   | RO   | -    | Reserved                                                    |

| 0     | RW   |      | Disable access to XCore's JTAG debug TAP                    |

Copy of the security register as read from OTP.

0x05: Security configuration

#### B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator has been stopped for at least 10 core clock cycles (this can be achieved by inserting two nop instructions between the SETPS and GETPS). The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| • | Bits | Perm | Init | Description                        |  |

|---|------|------|------|------------------------------------|--|

| : | 31:2 | RO   | -    | Reserved                           |  |

|   | 1    | RW   | 0    | Core ring oscillator enable.       |  |

|   | 0    | RW   | 0    | Peripheral ring oscillator enable. |  |

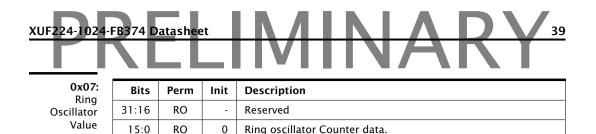

#### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

-XM()S

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08** Ring Oscillator Value

| 08:<br>ing | Bits  | Perm | Init | Description                   |

|------------|-------|------|------|-------------------------------|

| tor        | 31:16 | RO   | -    | Reserved                      |

| lue        | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

**0x09** Ring Oscillator Value

| 9:       | Bits  | Perm | Init | Description                   |

|----------|-------|------|------|-------------------------------|

| ig<br>or | 31:16 | RO   | -    | Reserved                      |

| ie       | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A:** Ring Oscillator Value

| )A:<br>ng | Bits  | Perm | Init | Description                   |

|-----------|-------|------|------|-------------------------------|

| tor       | 31:16 | RO   | -    | Reserved                      |

| ue        | 15:0  | RO   | 0    | Ring oscillator Counter data. |

XMOS

#### B.11 RAM size: 0x0C

The size of the RAM in bytes

| XUF224-1024- | FB374 | Datashe | et   | <b>IMINARY</b> <sup>40</sup>               |

|--------------|-------|---------|------|--------------------------------------------|

|              | Bits  | Perm    | Init | Description                                |

| 0x0C:        | 31:2  | RO      |      | Most significant 16 bits of all addresses. |

| RAM size     | 1:0   | RO      | -    | Reserved                                   |

#### B.12 Debug SSR: 0x10

This register contains the value of the SSR register when the debugger was called.

| Bits  | Perm | Init | Description                                                                        |  |

|-------|------|------|------------------------------------------------------------------------------------|--|

| 31:11 | RO   | -    | Reserved                                                                           |  |

| 10    | DRW  |      | Address space indentifier                                                          |  |

| 9     | DRW  |      | Determines the issue mode (DI bit) upon Kernel Entry after Exception or Interrupt. |  |

| 8     | RO   |      | Determines the issue mode (DI bit).                                                |  |

| 7     | DRW  |      | When 1 the thread is in fast mode and will continually issue.                      |  |

| 6     | DRW  |      | When 1 the thread is paused waiting for events, a lock or another resource.        |  |

| 5     | RO   | -    | Reserved                                                                           |  |

| 4     | DRW  |      | 1 when in kernel mode.                                                             |  |

| 3     | DRW  |      | 1 when in an interrupt handler.                                                    |  |

| 2     | DRW  |      | 1 when in an event enabling sequence.                                              |  |

| 1     | DRW  |      | When 1 interrupts are enabled for the thread.                                      |  |

| 0     | DRW  |      | When 1 events are enabled for the thread.                                          |  |

**0x10:** Debug SSR

#### B.13 Debug SPC: 0x11

This register contains the value of the SPC register when the debugger was called.

| 0x11:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SPC | 31:0 | DRW  |      | Value.      |

-XMOS"-

#### B.14 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

| XUF224-1024-FB374 Datasheet |       |      |      | MINARY <sup>45</sup>                                                                                     |

|-----------------------------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|                             | Bits  | Perm | Init | Description                                                                                              |

|                             | 31:24 | RO   | -    | Reserved                                                                                                 |

|                             | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 0x9C 0x9F:<br>Resources     | 15:2  | RO   | -    | Reserved                                                                                                 |

| breakpoint<br>control       | 1     | DRW  | 0    | When 0 break when condition A is met. When 1 = break when condition B is met.                            |

| register                    | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

| XUF224-1024-1 | FB374 D | atashee | et   | MINARY <sup>49</sup>                                        |

|---------------|---------|---------|------|-------------------------------------------------------------|

|               | Bits    | Perm    | Init | Description                                                 |

|               | 31      | CRO     |      | Disables write permission on this register                  |

|               | 30:15   | RO      | -    | Reserved                                                    |

|               | 14      | CRO     |      | Disable access to XCore's global debug                      |

|               | 13      | RO      | -    | Reserved                                                    |

|               | 12      | CRO     |      | lock all OTP sectors                                        |

|               | 11:8    | CRO     |      | lock bit for each OTP sector                                |

|               | 7       | CRO     |      | Enable OTP reduanacy                                        |

|               | 6       | RO      | -    | Reserved                                                    |

|               | 5       | CRO     |      | Override boot mode and read boot image from OTP             |

| 0x07:         | 4       | CRO     |      | Disable JTAG access to the PLL/BOOT configuration registers |

| Security      | 3:1     | RO      | -    | Reserved                                                    |

| configuration | 0       | CRO     |      | Disable access to XCore's JTAG debug TAP                    |

#### C.8 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27 Debug scratch

| <b>0x27:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| cratch                | 31:0 | CRW  |      | Value.      |

#### C.9 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40 PC of logical core 0

| 0x40:<br>ogical | Bits | Perm | Init | Description |

|-----------------|------|------|------|-------------|

| ore 0           | 31:0 | CRO  |      | Value.      |

XMOS

#### C.10 PC of logical core 1: 0x41

Value of the PC of logical core 1.

Value of the SR of logical core 7

| <b>0x67:</b><br>SR of logical | Bits | Perm | Init | Description |

|-------------------------------|------|------|------|-------------|

| core 7                        | 31:0 | CRO  |      | Value.      |

### 54 XUF224-1024-FB374 Datasheet **Node Configuration** D

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x09      | R    | System JTAG device ID register        |

| 0x0A      | R    | System USERCODE register              |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | Reserved                              |

| 0x11      | RW   | Reserved.                             |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x28 | RW   | Link status, direction, and network   |

| 0x40 0x47 | RO   | PLink status and network              |

| 0x80 0x88 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 31: Summary

#### D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|            | Bits                                                       | Perm | Init                                              | Description       |

|------------|------------------------------------------------------------|------|---------------------------------------------------|-------------------|

|            | 31:24                                                      | RO   | -                                                 | Reserved          |

| 0x00:      | 23:16 RO Sampled values of BootCtl pins on Power On Reset. |      | Sampled values of BootCtl pins on Power On Reset. |                   |

| Device     | 15:8                                                       | RO   |                                                   | SSwitch revision. |

| tification | 7:0                                                        | RO   |                                                   | SSwitch version.  |

-XMOS

identi

XS2-UF24A-1024-FB374

# XUF224-1024-FB374 Datasheet 58

|            | Bits Perm Init Description |    | Description |                                                 |

|------------|----------------------------|----|-------------|-------------------------------------------------|

|            | 31:28                      | RW | 0           | The direction for packets whose dimension is F. |

|            | 27:24 RW 0                 |    | 0           | The direction for packets whose dimension is E. |

|            | 23:20                      | RW | 0           | The direction for packets whose dimension is D. |

|            | 19:16                      | RW | 0           | The direction for packets whose dimension is C. |

|            | 15:12                      | RW | 0           | The direction for packets whose dimension is B. |

| 0x0D:      | 11:8                       | RW | 0           | The direction for packets whose dimension is A. |

| Directions | 7:4                        | RW | 0           | The direction for packets whose dimension is 9. |

| 8-15       | 3:0                        | RW | 0           | The direction for packets whose dimension is 8. |

D.12 Reserved: 0x10

Reserved.

| 0x10:    |

|----------|

| Reserved |

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:2 | RO   | -    | Reserved    |

| 1    | RW   | 0    | Reserved.   |

| 0    | RW   | 0    | Reserved.   |

### D.13 Reserved.: 0x11

Reserved.

**0x11:** Reserved.

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:2 | RO   | -    | Reserved    |

| 1    | RW   | 0    | Reserved.   |

| 0    | RW   | 0    | Reserved.   |

#### D.14 Debug source: 0x1F

Contains the source of the most recent debug event.

-XM

The USB node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number | Perm | Description                    |

|--------|------|--------------------------------|

| 0x00   | RO   | Device identification register |

| 0x04   | RW   | Node configuration register    |

| 0x05   | RW   | Node identifier                |

| 0x51   | RW   | System clock frequency         |

| 0x80   | RW   | Link Control and Status        |

Figure 32: Summary

#### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

**0x00:** Device identification register

| Bits  | Perm | Init | Description                      |

|-------|------|------|----------------------------------|

| 31:24 | RO   | 0x0F | Chip identifier                  |

| 23:16 | RO   | -    | Reserved                         |

| 15:8  | RO   | 0x02 | Revision number of the USB block |

| 7:0   | RO   | 0x00 | Version number of the USB block  |

#### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

|                | Bits | Perm | Init | Description                                                                                          |

|----------------|------|------|------|------------------------------------------------------------------------------------------------------|

| 0x04:          | 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |

| Node<br>ration | 30:1 | RO   | -    | Reserved                                                                                             |

| gister         | 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |

·XM(

#### 65 XUF224-1024-FB374 Datasheet Bits Perm Init Description 31:8 RO \_ Reserved 7 RW 0 Set to 1 to enable XEVACKMODE mode. 6 RW 0 Set to 1 to enable SOFISTOKEN mode. 5 RW 0 Set to 1 to enable UIFM power signalling mode. 4 RW 0 Set to 1 to enable IF timing mode.

0x04: **UIFM IFM**

control

3

2

1

0

RO

RW

RW

RW

#### F.3 UIFM Device Address: 0x08

\_

0

0

0

Reserved

The device address whose packets should be received. 0 until enumeration, it should be set to the assigned value after enumeration.

Set to 1 to enable UIFM linestate decoder.

Set to 1 to enable UIFM DOTOKENS mode.

Set to 1 to enable UIFM CHECKTOKENS mode.

0x08: **UIFM Device** Address

| Bits | Perm | Init | Description                                                                                        |

|------|------|------|----------------------------------------------------------------------------------------------------|

| 31:7 | RO   | -    | Reserved                                                                                           |

| 6:0  | RW   | 0    | The enumerated USB device address must be stored here. Only packets to this address are passed on. |

#### F.4 UIFM functional control: 0x0C

0x0C: UIFM functional control

|   | Bits | Perm | Init | Description                                       |

|---|------|------|------|---------------------------------------------------|

|   | 31:5 | RO   | -    | Reserved                                          |

| : | 4:2  | RW   | 1    | Set to 0 to disable UIFM to UTMI+ OPMODE mode.    |

|   | 1    | RW   | 1    | Set to 1 to switch UIFM to UTMI+ TERMSELECT mode. |

| - | 0    | RW   | 1    | Set to 1 to switch UIFM to UTMI+ XCVRSELECT mode. |

#### F.5 UIFM on-the-go control: 0x10

This register is used to negotiate an on-the-go connection.

-XMOS

| Document Title                                  | Information                               | Document Number |

|-------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-UF Devices | Power consumption                         |                 |

| Programming XC on XMOS Devices                  | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                        | Compilers, assembler and linker/mapper    | X3766           |

|                                                 | Timing analyzer, xScope, debugger         |                 |

|                                                 | Flash and OTP programming utilities       |                 |

### L Related Documentation

| Document Title                                   | Information                         | Document Number |

|--------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                        | ISA manual                          | X7879           |

| XS1 Port I/O Timing                              | Port timings                        | X5821           |

| xCONNECT Architecture                            | Link, switch and system information | X4249           |

| XS1-UF Link Performance and Design<br>Guidelines | Link timings                        |                 |

| XS1-UF Clock Frequency Control                   | Advanced clock control              |                 |

-XMOS°

### XUF224-1024-FB374 Datasheet 77 M Revision History

| Date       | Description                                                                   |  |

|------------|-------------------------------------------------------------------------------|--|

| 2015-03-20 | Preliminary release                                                           |  |

| 2015-04-14 | Added RST to pins to be pulled hard, and removed reference to TCK from Errata |  |

|            | Removed TRST_N references in packages that have no TRST_N                     |  |

|            | New diagram for boot from embedded flash showing ports                        |  |

|            | Pull up requirements for shared clock and external resistor for QSPI          |  |

| 2015-05-06 | Removed references tro DEBUG_N                                                |  |

| 2015-07-09 | Updated electrical characteristics - Section 13                               |  |

| 2015-08-19 | Added I(USB_VDD) - Section 13                                                 |  |

|            | Added USB layout guidelines - Section 12                                      |  |

| 2015-08-27 | Updated part marking and product code - Section 15                            |  |

Copyright © 2015, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.