Welcome to E-XFL.COM

### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

### Details

| Product Status                  | Active                                                   |

|---------------------------------|----------------------------------------------------------|

| Programmable Type               | In System Programmable                                   |

| Delay Time tpd(1) Max           | 5.4 ns                                                   |

| Voltage Supply - Internal       | 2.5V, 3.3V                                               |

| Number of Logic Elements/Blocks | 570                                                      |

| Number of Macrocells            | 440                                                      |

| Number of Gates                 | -                                                        |

| Number of I/O                   | 160                                                      |

| Operating Temperature           | -40°C ~ 100°C (TJ)                                       |

| Mounting Type                   | Surface Mount                                            |

| Package / Case                  | 256-BGA                                                  |

| Supplier Device Package         | 256-FBGA (17x17)                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm570f256i5n |

|                                 |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

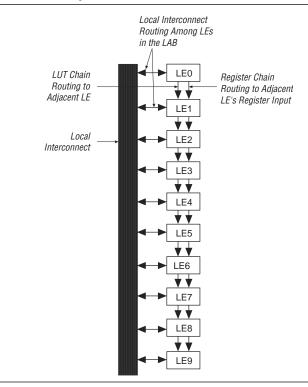

# **Logic Array Blocks**

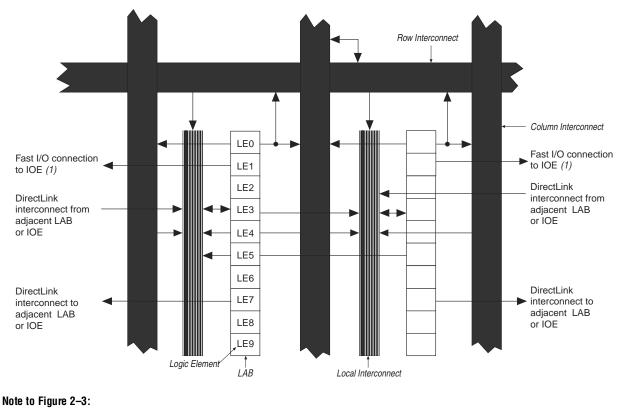

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, a look-up table (LUT) chain, and register chain connection lines. There are 26 possible unique inputs into an LAB, with an additional 10 local feedback input lines fed by LE outputs in the same LAB. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register chain connections transfer the output of one LE's register chain an LAB. The Quartus® II software places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–3 shows the MAX II LAB.

Figure 2–3. MAX II LAB Structure

(1) Only from LABs adjacent to IOEs.

# LAB Interconnects

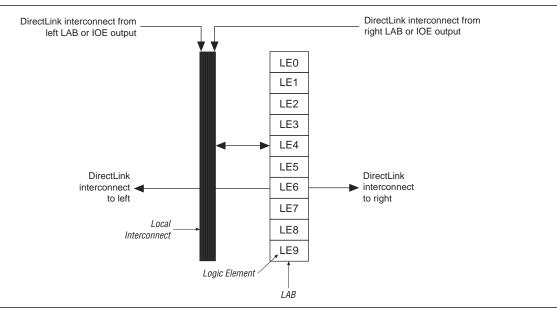

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, from the left and right, can also drive an LAB's local interconnect through the DirectLink connection. The DirectLink connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and DirectLink interconnects. Figure 2–4 shows the DirectLink connection.

### Figure 2-4. DirectLink Connection

### **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, a synchronous clear, an asynchronous preset/load, a synchronous load, and add/subtract control signals, providing a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal turns off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-back option or assign a given register to power-up high using the Quartus II software, the preset is then achieved using the asynchronous load signal with asynchronous load data input tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB column clocks [3..0], driven by the global clock network, and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnect structure drives the LAB local interconnect for non-global control signal generation. The MultiTrack interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–5 shows the LAB control signal generation circuit.

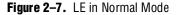

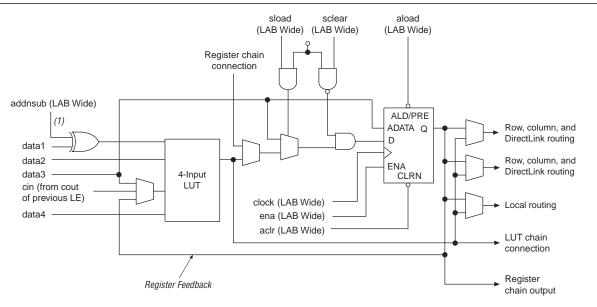

### **Normal Mode**

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–7). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinational output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

#### Note to Figure 2-7:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

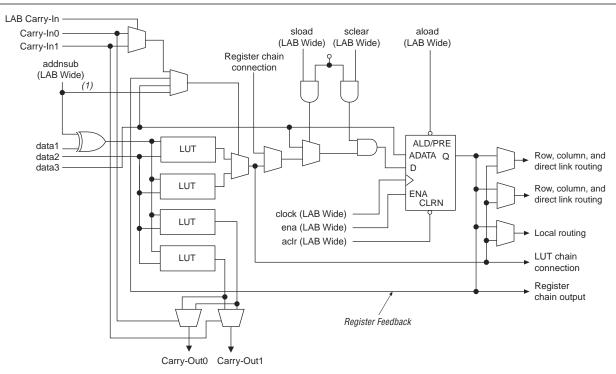

### **Dynamic Arithmetic Mode**

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry-select circuitry. As shown in Figure 2–8, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinational or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums:

```

data1 + data2 + carry in0

or

data1 + data2 + carry-in1

```

The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals: one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry-select for the carry-out0 output and carry-in1 acts as the carry-select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

Figure 2–8. LE in Dynamic Arithmetic Mode

### Note to Figure 2-8:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

### **Carry-Select Chain**

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–11 shows the LUT chain and register chain interconnects.

The C4 interconnects span four LABs up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–12 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by column and row IOEs. For LAB interconnection, a primary LAB or its vertical LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column to-column connections.

The UFM block communicates with the logic array similar to LAB-to-LAB interfaces. The UFM block connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. This block also has DirectLink interconnects for fast connections to and from a neighboring LAB. For more information about the UFM interface to the logic array, see "User Flash Memory Block" on page 2–18.

Table 2–2 shows the MAX II device routing scheme.

Table 2–2.

MAX II Device Routing Scheme

|                            |              | Destination       |                     |                          |               |                       |              |              |               |              |                        |

|----------------------------|--------------|-------------------|---------------------|--------------------------|---------------|-----------------------|--------------|--------------|---------------|--------------|------------------------|

| Source                     | LUT<br>Chain | Register<br>Chain | Local<br><i>(1)</i> | DirectLink<br><i>(1)</i> | R4 <i>(1)</i> | C4 <i>(1)</i>         | LE           | UFM<br>Block | Column<br>IOE | Row<br>IOE   | Fast I/0<br><i>(1)</i> |

| LUT Chain                  | —            | —                 | —                   | —                        | —             | —                     | $\checkmark$ | —            | —             | —            | —                      |

| Register Chain             |              | _                 | _                   | —                        | _             | —                     | $\checkmark$ | _            | _             | —            | —                      |

| Local<br>Interconnect      | _            | _                 | _                   |                          |               | _                     | $\checkmark$ | ~            | ~             | ~            | _                      |

| DirectLink<br>Interconnect | _            | _                 | ~                   |                          |               |                       | _            | _            | _             | _            | _                      |

| R4 Interconnect            | _            | _                 | $\checkmark$        | _                        | $\checkmark$  | $\checkmark$          |              | _            | _             | —            | _                      |

| C4 Interconnect            | _            | _                 | $\checkmark$        | —                        | $\checkmark$  | $\checkmark$          | _            | —            | _             | —            | _                      |

| LE                         | $\checkmark$ | $\checkmark$      | $\checkmark$        | $\checkmark$             | $\checkmark$  | <ul> <li>✓</li> </ul> |              | —            | $\checkmark$  | $\checkmark$ | $\checkmark$           |

| UFM Block                  | _            |                   | $\checkmark$        | $\checkmark$             | $\checkmark$  | $\checkmark$          |              | _            | _             | —            | _                      |

| Column IOE                 | -            | —                 | _                   | —                        | —             | ~                     | —            | _            | —             | —            | —                      |

| Row IOE                    |              |                   |                     | $\checkmark$             | $\checkmark$  | $\checkmark$          |              | —            |               | —            |                        |

Note to Table 2-2:

(1) These categories are interconnects.

# **Global Signals**

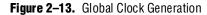

Each MAX II device has four dual-purpose dedicated clock pins (GCLK[3..0], two pins on the left side and two pins on the right side) that drive the global clock network for clocking, as shown in Figure 2–13. These four pins can also be used as general-purpose I/O if they are not used to drive the global clock network.

The four global clock lines in the global clock network drive throughout the entire device. The global clock network can provide clocks for all resources within the device including LEs, LAB local interconnect, IOEs, and the UFM block. The global clock lines can also be used for global control signals, such as clock enables, synchronous or asynchronous clears, presets, output enables, or protocol control signals such as TRDY and IRDY for PCI. Internal logic can drive the global clock network for internally-generated global clocks and control signals. Figure 2–13 shows the various sources that drive the global clock network.

### Note to Figure 2-13:

(1) Any I/O pin can use a MultiTrack interconnect to route as a logic array-generated global clock signal.

The global clock network drives to individual LAB column signals, LAB column clocks [3..0], that span an entire LAB column from the top to the bottom of the device. Unused global clocks or control signals in a LAB column are turned off at the LAB column clock buffers shown in Figure 2–14. The LAB column clocks [3..0] are multiplexed down to two LAB clock signals and one LAB clear signal. Other control signal types route from the global clock network into the LAB local interconnect. See "LAB Control Signals" on page 2–5 for more information.

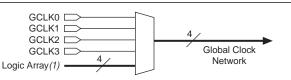

#### Figure 2–19. MAX II IOE Structure

### (1) Available in EPM1270 and EPM2210 devices only.

## I/O Blocks

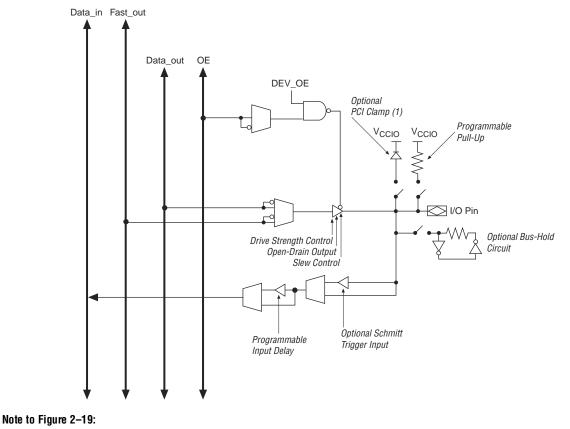

The IOEs are located in I/O blocks around the periphery of the MAX II device. There are up to seven IOEs per row I/O block (5 maximum in the EPM240 device) and up to four IOEs per column I/O block. Each column or row I/O block interfaces with its adjacent LAB and MultiTrack interconnect to distribute signals throughout the device. The row I/O blocks drive row, column, or DirectLink interconnects. The column I/O blocks drive column interconnects.

Figure 2–21 shows how a column I/O block connects to the logic array.

### Note to Figure 2-21:

```

(1) Each of the four IOEs in the column I/O block can have one data_out or fast_out output, one OE output, and one data_in input.

```

## I/O Standards and Banks

MAX II device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

Table 2–4 describes the I/O standards supported by MAX II devices.

| Table 2-4. | MAX II I/O | Standards |

|------------|------------|-----------|

|------------|------------|-----------|

| I/O Standard       | Туре         | Output Supply Voltage<br>(VCCIO) (V) |

|--------------------|--------------|--------------------------------------|

| 3.3-V LVTTL/LVCMOS | Single-ended | 3.3                                  |

| 2.5-V LVTTL/LVCMOS | Single-ended | 2.5                                  |

| 1.8-V LVTTL/LVCMOS | Single-ended | 1.8                                  |

| 1.5-V LVCMOS       | Single-ended | 1.5                                  |

| 3.3-V PCI (1)      | Single-ended | 3.3                                  |

### Note to Table 2-4:

(1) The 3.3-V PCI compliant I/O is supported in Bank 3 of the EPM1270 and EPM2210 devices.

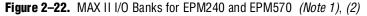

The EPM240 and EPM570 devices support two I/O banks, as shown in Figure 2–22. Each of these banks support all the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is not supported in these devices and banks.

#### Notes to Figure 2–22:

(1) Figure 2-22 is a top view of the silicon die.

(2) Figure 2-22 is a graphical representation only. Refer to the pin list and the Quartus II software for exact pin locations.

The EPM1270 and EPM2210 devices support four I/O banks, as shown in Figure 2–23. Each of these banks support all of the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is supported in Bank 3. Bank 3 supports the PCI clamping diode on inputs and PCI drive compliance on outputs. You must use Bank 3 for designs requiring PCI compliant I/O pins. The Quartus II software automatically places I/O pins in this bank if assigned with the PCI I/O standard.

| Device  | 33-MHz PCI       | 66-MHz PCI     |  |  |  |

|---------|------------------|----------------|--|--|--|

| EPM1270 | All Speed Grades | –3 Speed Grade |  |  |  |

| EPM2210 | All Speed Grades | –3 Speed Grade |  |  |  |

| Table 2–5.         MAX II Devices and Speed Grades that Support 3.3-V PCI Electrical Specifications and |  |

|---------------------------------------------------------------------------------------------------------|--|

| Meet PCI Timing                                                                                         |  |

### Schmitt Trigger

The input buffer for each MAX II device I/O pin has an optional Schmitt trigger setting for the 3.3-V and 2.5-V standards. The Schmitt trigger allows input buffers to respond to slow input edge rates with a fast output edge rate. Most importantly, Schmitt triggers provide hysteresis on the input buffer, preventing slow-rising noisy input signals from ringing or oscillating on the input signal driven into the logic array. This provides system noise tolerance on MAX II inputs, but adds a small, nominal input delay.

The JTAG input pins (TMS, TCK, and TDI) have Schmitt trigger buffers that are always enabled.

P

The TCK input is susceptible to high pulse glitches when the input signal fall time is greater than 200 ns for all I/O standards.

### **Output Enable Signals**

Each MAX II IOE output buffer supports output enable signals for tri-state control. The output enable signal can originate from the GCLK[3..0] global signals or from the MultiTrack interconnect. The MultiTrack interconnect routes output enable signals and allows for a unique output enable for each output or bidirectional pin.

MAX II devices also provide a chip-wide output enable pin (DEV\_OE) to control the output enable for every output pin in the design. An option set before compilation in the Quartus II software controls this pin. This chip-wide output enable uses its own routing resources and does not use any of the four global resources. If this option is turned on, all outputs on the chip operate normally when DEV\_OE is asserted. When the pin is deasserted, all outputs are tri-stated. If this option is turned off, the DEV\_OE pin is disabled when the device operates in user mode and is available as a user I/O pin.

### **Programmable Drive Strength**

The output buffer for each MAX II device I/O pin has two levels of programmable drive strength control for each of the LVTTL and LVCMOS I/O standards. Programmable drive strength provides system noise reduction control for high performance I/O designs. Although a separate slew-rate control feature exists, using the lower drive strength setting provides signal slew-rate control to reduce system noise and signal overshoot without the large delay adder associated with the slew-rate control feature. Table 2–6 shows the possible settings for the I/O standards with drive strength control. The Quartus II software uses the maximum current strength as the default setting. The PCI I/O standard is always set at 20 mA with no alternate setting.

### **Bus Hold**

Each MAX II device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option.

The bus-hold circuitry uses a resistor to pull the signal level to the last driven state. The *DC and Switching Characteristics* chapter in the *MAX II Device Handbook* gives the specific sustaining current for each  $V_{CCIO}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after the device has fully initialized. The bus-hold circuit captures the value on the pin present at the moment user mode is entered.

### Programmable Pull-Up Resistor

Each MAX II device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor holds the output to the  $V_{CCIO}$  level of the output pin's bank.

P

The programmable pull-up resistor feature should not be used at the same time as the bus-hold feature on a given I/O pin.

### **Programmable Input Delay**

The MAX II IOE includes a programmable input delay that is activated to ensure zero hold times. A path where a pin directly drives a register, with minimal routing between the two, may require the delay to ensure zero hold time. However, a path where a pin drives a register through long routing or through combinational logic may not require the delay to achieve a zero hold time. The Quartus II software uses this delay to ensure zero hold times when needed.

### MultiVolt I/O Interface

The MAX II architecture supports the MultiVolt I/O interface feature, which allows MAX II devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation ( $V_{CCINT}$ ), and up to four sets for input buffers and I/O output driver buffers ( $V_{CCIO}$ ), depending on the number of I/O banks available in the devices where each set of VCC pins powers one I/O bank. The EPM240 and EPM570 devices have two I/O banks respectively while the EPM1270 and EPM2210 devices have four I/O banks respectively.

Make sure that the  $V_{CCNT}$  is within the recommended operating range even though SRAM download has completed.

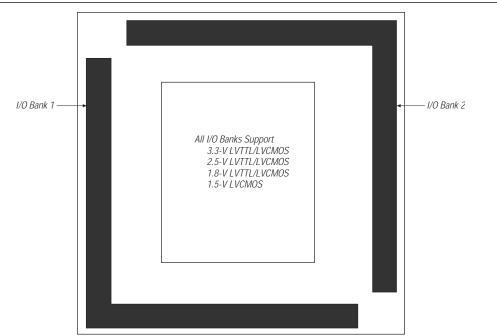

Each I/O and clock pin has the circuitry shown in Figure 4–1.

Figure 4–1. Hot Socketing Circuit Block Diagram for MAX II Devices

The POR circuit monitors  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels and keeps I/O pins tri-stated until the device has completed its flash memory configuration of the SRAM logic. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is enabled during download to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  are powered, and it prevents the I/O pins from driving out when the device is not fully powered or operational. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$  and  $V_{CCINT}$  when driven by external signals before the device is powered.

٠.,

For information about 5.0-V tolerance, refer to the *Using MAX II Devices in Multi-Voltage Systems* chapter in the *MAX II Device Handbook*.

Figure 4–2 shows a transistor-level cross section of the MAX II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{CCIO}$  is powered before  $V_{CCINT}$  or if the I/O pad voltage is higher than  $V_{CCIO}$ . This also applies for sudden voltage spikes during hot insertion. The  $V_{PAD}$  leakage current charges the 3.3-V tolerant circuit capacitance.

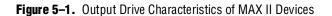

## **Output Drive Characteristics**

Figure 5–1 shows the typical drive strength characteristics of MAX II devices.

### Note to Figure 5–1:

(1) The DC output current per pin is subject to the absolute maximum rating of Table 5-1.

# I/O Standard Specifications

Table 5–5 through Table 5–10 show the MAX II device family I/O standard specifications.

| Symbol            | Parameter                 | Conditions      | Minimum | Maximum | Unit |

|-------------------|---------------------------|-----------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | —               | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage  | —               | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | —               | -0.5    | 0.8     | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -4 mA (1) | 2.4     |         | V    |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 4 mA (1)  |         | 0.45    | V    |

Table 5–6. 3.3-V LVCMOS Specifications (Part 1 of 2)

| Symbol            | Parameter                | Conditions | Minimum | Maximum | Unit |

|-------------------|--------------------------|------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage       | —          | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage |            | 1.7     | 4.0     | V    |

| VIL               | Low-level input voltage  |            | -0.5    | 0.8     | V    |

| Symbol            | Parameter                    | Conditions    | Minimum               | Typical | Maximum                      | Unit |

|-------------------|------------------------------|---------------|-----------------------|---------|------------------------------|------|

| V <sub>ccio</sub> | I/O supply<br>voltage        |               | 3.0                   | 3.3     | 3.6                          | V    |

| V <sub>IH</sub>   | High-level input<br>voltage  |               | $0.5 \times V_{ccio}$ | _       | V <sub>CC10</sub> + 0.5      | V    |

| V <sub>IL</sub>   | Low-level input<br>voltage   |               | -0.5                  |         | $0.3 \times V_{\text{cc10}}$ | V    |

| V <sub>OH</sub>   | High-level<br>output voltage | IOH = -500 μA | $0.9 \times V_{ccio}$ | _       | _                            | V    |

| V <sub>ol</sub>   | Low-level<br>output voltage  | IOL = 1.5 mA  | _                     | _       | 0.1 × V <sub>cc10</sub>      | V    |

### Table 5–10. 3.3-V PCI Specifications (Note 1)

### Note to Table 5-10:

(1) 3.3-V PCI I/O standard is only supported in Bank 3 of the EPM1270 and EPM2210 devices.

## **Bus Hold Specifications**

Table 5–11 shows the MAX II device family bus hold specifications.

|                           |                                            | V <sub>ccio</sub> Level |       |     |       |     |      |       |      |      |

|---------------------------|--------------------------------------------|-------------------------|-------|-----|-------|-----|------|-------|------|------|

|                           |                                            | 1.                      | 1.5 V |     | 1.8 V |     | 5 V  | 3.3 V |      |      |

| Parameter                 | Conditions                                 | Min                     | Max   | Min | Max   | Min | Max  | Min   | Max  | Unit |

| Low sustaining current    | $V_{IN} > V_{IL}$ (maximum)                | 20                      |       | 30  |       | 50  |      | 70    |      | μA   |

| High sustaining current   | V <sub>IN</sub> < V <sub>⊮</sub> (minimum) | -20                     |       | -30 | _     | -50 |      | -70   |      | μA   |

| Low overdrive current     | $0 V < V_{IN} < V_{CCIO}$                  |                         | 160   |     | 200   |     | 300  |       | 500  | μA   |

| High overdrive<br>current | $0 V < V_{IN} < V_{CCIO}$                  | —                       | -160  | —   | -200  | _   | -300 | _     | -500 | μA   |

## **Power-Up Timing**

Table 5–12 shows the power-up timing characteristics for MAX II devices.

Table 5-12. MAX II Power-Up Timing

| Symbol                  | Parameter                                                               | Device  | Min | Тур | Max | Unit |

|-------------------------|-------------------------------------------------------------------------|---------|-----|-----|-----|------|

| t <sub>config</sub> (1) | The amount of time from when                                            | EPM240  | —   | _   | 200 | μs   |

|                         | minimum $V_{CCINT}$ is reached until<br>the device enters user mode (2) | EPM570  | _   | _   | 300 | μs   |

|                         |                                                                         | EPM1270 | _   | _   | 300 | μs   |

|                         |                                                                         | EPM2210 |     |     | 450 | μs   |

### Notes to Table 5-12:

(1) Table 5–12 values apply to commercial and industrial range devices. For extended temperature range devices, the t<sub>CONFIG</sub> maximum values are as follows:

Device Maximum

| Device  | Maximui |

|---------|---------|

| EPM240  | 300 µs  |

| EPM570  | 400 µs  |

| EPM1270 | 400 µs  |

| EPM2210 | 500 µs  |

(2) For more information about POR trigger voltage, refer to the *Hot Socketing and Power-On Reset in MAX II Devices* chapter in the *MAX II Device Handbook*.

# **Power Consumption**

Designers can use the Altera<sup>®</sup> PowerPlay Early Power Estimator and PowerPlay Power Analyzer to estimate the device power.

• For more information about these power analysis tools, refer to the *Understanding and Evaluating Power in MAX II Devices* chapter in the *MAX II Device Handbook* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

# **Timing Model and Specifications**

MAX II devices timing can be analyzed with the Altera Quartus<sup>®</sup> II software, a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 5–2.

MAX II devices have predictable internal delays that enable the designer to determine the worst-case timing of any design. The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

|                            |                                                                |                   | Ν     | IAX II            | / MAX II | G                 |       |                   |       |                   |       |                   |       |      |

|----------------------------|----------------------------------------------------------------|-------------------|-------|-------------------|----------|-------------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|------|

|                            |                                                                | –3 Speed<br>Grade |       | –4 Speed<br>Grade |          | –5 Speed<br>Grade |       | –6 Speed<br>Grade |       | –7 Speed<br>Grade |       | –8 Speed<br>Grade |       |      |

| Symbol                     | Parameter                                                      | Min               | Max   | Min               | Max      | Min               | Max   | Min               | Max   | Min               | Max   | Min               | Max   | Unit |

| t <sub>fastio</sub>        | Data output delay<br>from adjacent LE<br>to I/O block          |                   | 159   |                   | 207      |                   | 254   |                   | 170   |                   | 348   |                   | 428   | ps   |

| t <sub>iN</sub>            | I/O input pad and<br>buffer delay                              | _                 | 708   | _                 | 920      |                   | 1,132 | _                 | 907   | _                 | 970   | _                 | 986   | ps   |

| t <sub>glob</sub> (1)      | I/O input pad and<br>buffer delay used<br>as global signal pin | _                 | 1,519 |                   | 1,974    | _                 | 2,430 |                   | 2,261 |                   | 2,670 | _                 | 3,322 | ps   |

| t <sub>ioe</sub>           | Internally<br>generated output<br>enable delay                 |                   | 354   | _                 | 374      |                   | 460   |                   | 530   | _                 | 966   | _                 | 1,410 | ps   |

| t <sub>DL</sub>            | Input routing delay                                            | _                 | 224   | —                 | 291      | _                 | 358   | _                 | 318   | —                 | 410   | _                 | 509   | ps   |

| t <sub>od</sub> (2)        | Output delay buffer<br>and pad delay                           | _                 | 1,064 |                   | 1,383    |                   | 1,702 | —                 | 1,319 |                   | 1,526 | _                 | 1,543 | ps   |

| t <sub>xz</sub> <i>(3)</i> | Output buffer<br>disable delay                                 | _                 | 756   | _                 | 982      | —                 | 1,209 | —                 | 1,045 | —                 | 1,264 | _                 | 1,276 | ps   |

| t <sub>zx</sub> (4)        | Output buffer<br>enable delay                                  | —                 | 1,003 |                   | 1,303    |                   | 1,604 | _                 | 1,160 | _                 | 1,325 | —                 | 1,353 | ps   |

Table 5–16. IOE Internal Timing Microparameters

#### Notes to Table 5-16:

(1) Delay numbers for t<sub>GLOB</sub> differ for each device density and speed grade. The delay numbers for t<sub>GLOB</sub>, shown in Table 5–16, are based on an EPM240 device target.

(2) Refer to Table 5–32 and 5–24 for delay adders associated with different I/O standards, drive strengths, and slew rates.

(3) Refer to Table 5–19 and 5–14 for txz delay adders associated with different I/O standards, drive strengths, and slew rates.

(4) Refer to Table 5–17 and 5–13 for  $t_{zx}$  delay adders associated with different I/O standards, drive strengths, and slew rates.

Table 5–17 through Table 5–20 show the adder delays for  $t_{zx}$  and  $t_{xz}$  microparameters when using an I/O standard other than 3.3-V LVTTL with 16 mA drive strength.

Table 5–17.

t<sub>ZX</sub> IOE Microparameter Adders for Fast Slew Rate

(Part 1 of 2)

|               |       |     | I                       | MAX II , | / MAX III | G                                |       |     |     | MA          | X IIZ             |         |     |      |

|---------------|-------|-----|-------------------------|----------|-----------|----------------------------------|-------|-----|-----|-------------|-------------------|---------|-----|------|

|               |       |     | -3 Speed<br>Grade Grade |          |           | –5 Speed –6 Speed<br>Grade Grade |       |     |     | peed<br>ade | –8 Speed<br>Grade |         |     |      |

| Standard      | d     | Min | Max                     | Min      | Max       | Min                              | Max   | Min | Max | Min         | Max               | Min Max |     | Unit |

| 3.3-V LVTTL   | 16 mA | —   | 0                       | —        | 0         | —                                | 0     | —   | 0   | —           | 0                 | —       | 0   | ps   |

|               | 8 mA  | —   | 28                      |          | 37        |                                  | 45    | —   | 72  | _           | 71                |         | 74  | ps   |

| 3.3-V LVCMOS  | 8 mA  | —   | 0                       | _        | 0         | _                                | 0     | —   | 0   | —           | 0                 | _       | 0   | ps   |

|               | 4 mA  | _   | 28                      |          | 37        |                                  | 45    | _   | 72  | _           | 71                |         | 74  | ps   |

| 2.5-V LVTTL / | 14 mA | —   | 14                      |          | 19        |                                  | 23    | —   | 75  | —           | 87                | _       | 90  | ps   |

| LVCMOS        | 7 mA  | —   | 314                     | _        | 409       | _                                | 503   | —   | 162 | —           | 174               | _       | 177 | ps   |

| 1.8-V LVTTL / | 6 mA  | —   | 450                     | —        | 585       | _                                | 720   | —   | 279 | _           | 289               | _       | 291 | ps   |

| LVCMOS        | 3 mA  | _   | 1,443                   |          | 1,876     |                                  | 2,309 |     | 499 |             | 508               |         | 512 | ps   |

|               |       |     | N                 | IAX II / | MAX II            | G   |                   | MAX IIZ |                   |     |             |                   |       |      |  |

|---------------|-------|-----|-------------------|----------|-------------------|-----|-------------------|---------|-------------------|-----|-------------|-------------------|-------|------|--|

|               |       |     | –3 Speed<br>Grade |          | –4 Speed<br>Grade |     | –5 Speed<br>Grade |         | –6 Speed<br>Grade |     | peed<br>ade | –8 Speed<br>Grade |       |      |  |

| Standard      | ł     | Min | Max               | Min      | Max               | Min | Max               | Min     | Max               | Min | Max         | Min Max           |       | Unit |  |

| 3.3-V LVTTL   | 16 mA | —   | 206               | —        | -20               |     | -247              | —       | 1,433             |     | 1,446       | —                 | 1,454 | ps   |  |

|               | 8 mA  | _   | 891               | _        | 665               |     | 438               | _       | 1,332             |     | 1,345       | _                 | 1,348 | ps   |  |

| 3.3-V LVCMOS  | 8 mA  | _   | 206               | _        | -20               |     | -247              | —       | 1,433             |     | 1,446       | —                 | 1,454 | ps   |  |

|               | 4 mA  | _   | 891               | _        | 665               | —   | 438               | —       | 1,332             | _   | 1,345       | —                 | 1,348 | ps   |  |

| 2.5-V LVTTL / | 14 mA |     | 222               |          | -4                | _   | -231              | —       | 213               |     | 208         | —                 | 213   | ps   |  |

| LVCMOS        | 7 mA  | _   | 943               |          | 717               | —   | 490               | —       | 166               |     | 161         | —                 | 166   | ps   |  |

| 3.3-V PCI     | 20 mA | _   | 161               |          | 210               |     | 258               | —       | 1,332             |     | 1,345       | —                 | 1,348 | ps   |  |

Table 5–20.  $t_{\text{XZ}}$  IOE Microparameter Adders for Slow Slew Rate

The default slew rate setting for MAX II devices in the Quartus II design software is "fast".

|            |                          | MAX II / MAX IIG                   |  |

|------------|--------------------------|------------------------------------|--|

| Table 5-21 | I. UFM Block Internal Ti | ming Microparameters (Part 1 of 3) |  |

|                   |                                                                     | MAX II / MAX IIG MAX IIZ |     |             |     |             |     |     |             |     |                                  |     |     |      |

|-------------------|---------------------------------------------------------------------|--------------------------|-----|-------------|-----|-------------|-----|-----|-------------|-----|----------------------------------|-----|-----|------|

|                   |                                                                     | –3 Sp<br>Gra             |     | –4 S<br>Gra |     | –5 S<br>Gra |     |     | peed<br>ade |     | -7 Speed -8 Speed<br>Grade Grade |     |     |      |

| Symbol            | Parameter                                                           | Min                      | Max | Min         | Max | Min         | Max | Min | Max         | Min | Max                              | Min | Max | Unit |

| t <sub>aclk</sub> | Address register clock period                                       | 100                      | -   | 100         | -   | 100         | -   | 100 | —           | 100 | -                                | 100 | —   | ns   |

| t <sub>asu</sub>  | Address register shift<br>signal setup to<br>address register clock | 20                       | _   | 20          | —   | 20          | —   | 20  | _           | 20  | -                                | 20  | _   | ns   |

| t <sub>an</sub>   | Address register shift<br>signal hold to address<br>register clock  | 20                       | _   | 20          | _   | 20          | _   | 20  | _           | 20  | _                                | 20  | _   | ns   |

| t <sub>ADS</sub>  | Address register data<br>in setup to address<br>register clock      | 20                       | -   | 20          | -   | 20          | -   | 20  | _           | 20  | -                                | 20  | _   | ns   |

| t <sub>adh</sub>  | Address register data<br>in hold from address<br>register clock     | 20                       | _   | 20          | _   | 20          | _   | 20  | _           | 20  | _                                | 20  | _   | ns   |

| t <sub>dclk</sub> | Data register clock<br>period                                       | 100                      | -   | 100         | -   | 100         | -   | 100 | -           | 100 | -                                | 100 | -   | ns   |

| $t_{\text{DSS}}$  | Data register shift<br>signal setup to data<br>register clock       | 60                       | -   | 60          | -   | 60          | -   | 60  | -           | 60  | -                                | 60  | _   | ns   |

| t <sub>dsh</sub>  | Data register shift<br>signal hold from data<br>register clock      | 20                       | _   | 20          | _   | 20          | _   | 20  | _           | 20  | _                                | 20  | _   | ns   |

## **External Timing Parameters**

External timing parameters are specified by device density and speed grade. All external I/O timing parameters shown are for the 3.3-V LVTTL I/O standard with the maximum drive strength and fast slew rate. For external I/O timing using standards other than LVTTL or for different drive strengths, use the I/O standard input and output delay adders in Table 5–27 through Table 5–31.

Table 5–23 shows the external I/O timing parameters for EPM240 devices.

Table 5–23.

EPM240 Global Clock External I/O Timing Parameters

(Part 1 of 2)

|                  |                                                                          |           |                   | ľ   | MAX II / | MAX II            | G   |                   | MAX IIZ |              |                   |      |     |              |      |

|------------------|--------------------------------------------------------------------------|-----------|-------------------|-----|----------|-------------------|-----|-------------------|---------|--------------|-------------------|------|-----|--------------|------|

|                  |                                                                          |           | –3 Speed<br>Grade |     |          | –4 Speed<br>Grade |     | –5 Speed<br>Grade |         | Speed<br>ade | –7 Speed<br>Grade |      |     | Speed<br>ade |      |

| Symbol           | Parameter                                                                | Condition | Min               | Max | Min      | Max               | Min | Max               | Min     | Max          | Min               | Max  | Min | Max          | Unit |

| t <sub>PD1</sub> | Worst case<br>pin-to-pin<br>delay<br>through 1<br>look-up table<br>(LUT) | 10 pF     |                   | 4.7 |          | 6.1               | _   | 7.5               |         | 7.9          |                   | 12.0 | _   | 14.0         | ns   |

| t <sub>PD2</sub> | Best case<br>pin-to-pin<br>delay<br>through<br>1 LUT                     | 10 pF     |                   | 3.7 | _        | 4.8               | _   | 5.9               |         | 5.8          |                   | 7.8  | _   | 8.5          | ns   |

| t <sub>su</sub>  | Global clock<br>setup time                                               | _         | 1.7               |     | 2.2      | _                 | 2.7 |                   | 2.4     |              | 4.1               |      | 4.6 |              | ns   |

| t <sub>H</sub>   | Global clock<br>hold time                                                | _         | 0                 |     | 0        |                   | 0   |                   | 0       |              | 0                 |      | 0   |              | ns   |

| t <sub>co</sub>  | Global clock<br>to output<br>delay                                       | 10 pF     | 2.0               | 4.3 | 2.0      | 5.6               | 2.0 | 6.9               | 2.0     | 6.6          | 2.0               | 8.1  | 2.0 | 8.6          | ns   |

| t <sub>CH</sub>  | Global clock<br>high time                                                | _         | 166               |     | 216      |                   | 266 |                   | 253     |              | 335               | _    | 339 |              | ps   |

| t <sub>CL</sub>  | Global clock<br>low time                                                 | —         | 166               |     | 216      |                   | 266 |                   | 253     |              | 335               |      | 339 |              | ps   |

| t <sub>cnt</sub> | Minimum<br>global clock<br>period for<br>16-bit<br>counter               |           | 3.3               |     | 4.0      |                   | 5.0 |                   | 5.4     |              | 8.1               |      | 8.4 |              | ns   |

For more information about each external timing parameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

### Table 5–31. MAX II IOE Programmable Delays

|                                               |                   | MAX II / MAX IIG |                   |       |                   |       |                   | MAX IIZ |                   |       |                   |       |      |  |

|-----------------------------------------------|-------------------|------------------|-------------------|-------|-------------------|-------|-------------------|---------|-------------------|-------|-------------------|-------|------|--|

|                                               | –3 Speed<br>Grade |                  | –4 Speed<br>Grade |       | –5 Speed<br>Grade |       | -6 Speed<br>Grade |         | –7 Speed<br>Grade |       | –8 Speed<br>Grade |       |      |  |

| Parameter                                     | Min               | Max              | Min               | Max   | Min               | Max   | Min               | Max     | Min               | Max   | Min               | Max   | Unit |  |

| Input Delay from Pin to<br>Internal Cells = 1 | _                 | 1,225            | -                 | 1,592 | -                 | 1,960 | _                 | 1,858   | _                 | 2,171 | _                 | 2,214 | ps   |  |

| Input Delay from Pin to<br>Internal Cells = 0 | —                 | 89               | -                 | 115   | —                 | 142   | _                 | 569     | —                 | 609   | —                 | 616   | ps   |  |

# **Maximum Input and Output Clock Rates**

Table 5–32 and Table 5–33 show the maximum input and output clock rates for standard I/O pins in MAX II devices.

Table 5-32. MAX II Maximum Input Clock Rate for I/O

|              |                            | м                 | AX II / MAX       | liG               |                   |                   |                   |      |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------|

| I/O S        | tandard                    | –3 Speed<br>Grade | –4 Speed<br>Grade | –5 Speed<br>Grade | –6 Speed<br>Grade | –7 Speed<br>Grade | –8 Speed<br>Grade | Unit |

| 3.3-V LVTTL  | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |

|              | With Schmitt<br>Trigger    | 250               | 250               | 250               | 250               | 250               | 250               | MHz  |

| 3.3-V LVCMOS | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |

|              | With Schmitt<br>Trigger    | 250               | 250               | 250               | 250               | 250               | 250               | MHz  |

| 2.5-V LVTTL  | Without Schmitt<br>Trigger | 220               | 220               | 220               | 220               | 220               | 220               | MHz  |

|              | With Schmitt<br>Trigger    | 188               | 188               | 188               | 188               | 188               | 188               | MHz  |

| 2.5-V LVCMOS | Without Schmitt<br>Trigger | 220               | 220               | 220               | 220               | 220               | 220               | MHz  |

|              | With Schmitt<br>Trigger    | 188               | 188               | 188               | 188               | 188               | 188               | MHz  |

| 1.8-V LVTTL  | Without Schmitt<br>Trigger | 200               | 200               | 200               | 200               | 200               | 200               | MHz  |

| 1.8-V LVCMOS | Without Schmitt<br>Trigger | 200               | 200               | 200               | 200               | 200               | 200               | MHz  |

| 1.5-V LVCMOS | Without Schmitt<br>Trigger | 150               | 150               | 150               | 150               | 150               | 150               | MHz  |

| 3.3-V PCI    | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |