Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 5.4 ns                                                    |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                             |

| Number of Logic Elements/Blocks | 570                                                       |

| Number of Macrocells            | 440                                                       |

| Number of Gates                 | -                                                         |

| Number of I/O                   | 160                                                       |

| Operating Temperature           | -40°C ~ 100°C (TJ)                                        |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 256-BGA                                                   |

| Supplier Device Package         | 256-FBGA (17x17)                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm570gf256i5n |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1-6. Document Revision History

| Date and Revision             | Changes Made                           | Summary of Changes |

|-------------------------------|----------------------------------------|--------------------|

| June 2005,<br>version 1.3     | ■ Updated timing numbers in Table 1-1. | _                  |

| December 2004,<br>version 1.2 | ■ Updated timing numbers in Table 1-1. | _                  |

| June 2004,<br>version 1.1     | ■ Updated timing numbers in Table 1-1. | _                  |

## 2. MAX II Architecture

MII51002-2.2

## Introduction

This chapter describes the architecture of the MAX II device and contains the following sections:

- "Functional Description" on page 2–1

- "Logic Array Blocks" on page 2–4

- "Logic Elements" on page 2–6

- "MultiTrack Interconnect" on page 2–12

- "Global Signals" on page 2–16

- "User Flash Memory Block" on page 2–18

- "MultiVolt Core" on page 2–22

- "I/O Structure" on page 2–23

# **Functional Description**

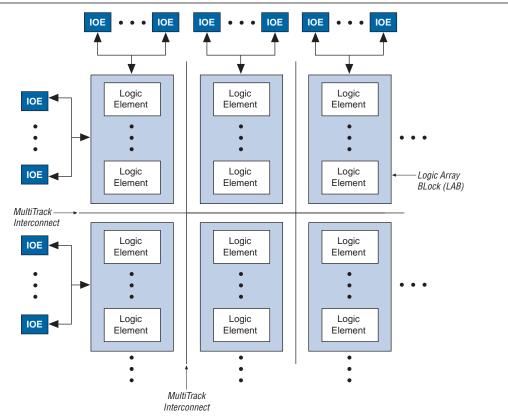

MAX® II devices contain a two-dimensional row- and column-based architecture to implement custom logic. Row and column interconnects provide signal interconnects between the logic array blocks (LABs).

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device. The MultiTrack interconnect provides fast granular timing delays between LABs. The fast routing between LEs provides minimum timing delay for added levels of logic versus globally routed interconnect structures.

The MAX II device I/O pins are fed by I/O elements (IOE) located at the ends of LAB rows and columns around the periphery of the device. Each IOE contains a bidirectional I/O buffer with several advanced features. I/O pins support Schmitt trigger inputs and various single-ended standards, such as 66-MHz, 32-bit PCI, and LVTTL.

MAX II devices provide a global clock network. The global clock network consists of four global clock lines that drive throughout the entire device, providing clocks for all resources within the device. The global clock lines can also be used for control signals such as clear, preset, or output enable.

Figure 2–1 shows a functional block diagram of the MAX II device.

Figure 2–1. MAX II Device Block Diagram

Each MAX II device contains a flash memory block within its floorplan. On the EPM240 device, this block is located on the left side of the device. On the EPM570, EPM1270, and EPM2210 devices, the flash memory block is located on the bottom-left area of the device. The majority of this flash memory storage is partitioned as the dedicated configuration flash memory (CFM) block. The CFM block provides the non-volatile storage for all of the SRAM configuration information. The CFM automatically downloads and configures the logic and I/O at power-up, providing instant-on operation.

For more information about configuration upon power-up, refer to the *Hot Socketing* and *Power-On Reset in MAX II Devices* chapter in the *MAX II Device Handbook*.

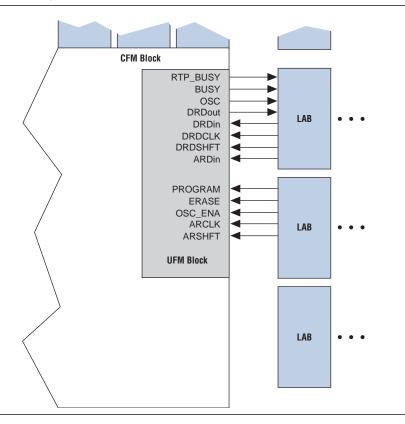

A portion of the flash memory within the MAX II device is partitioned into a small block for user data. This user flash memory (UFM) block provides 8,192 bits of general-purpose user storage. The UFM provides programmable port connections to the logic array for reading and writing. There are three LAB rows adjacent to this block, with column numbers varying by device.

Table 2–1 shows the number of LAB rows and columns in each device, as well as the number of LAB rows and columns adjacent to the flash memory area in the EPM570, EPM1270, and EPM2210 devices. The long LAB rows are full LAB rows that extend from one side of row I/O blocks to the other. The short LAB rows are adjacent to the UFM block; their length is shown as width in LAB columns.

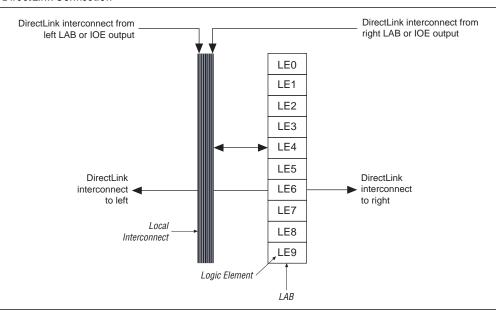

Figure 2-4. DirectLink Connection

#### **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, a synchronous clear, an asynchronous preset/load, a synchronous load, and add/subtract control signals, providing a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal turns off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-back option or assign a given register to power-up high using the Quartus II software, the preset is then achieved using the asynchronous load signal with asynchronous load data input tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB column clocks [3..0], driven by the global clock network, and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnect structure drives the LAB local interconnect for non-global control signal generation. The MultiTrack interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–5 shows the LAB control signal generation circuit.

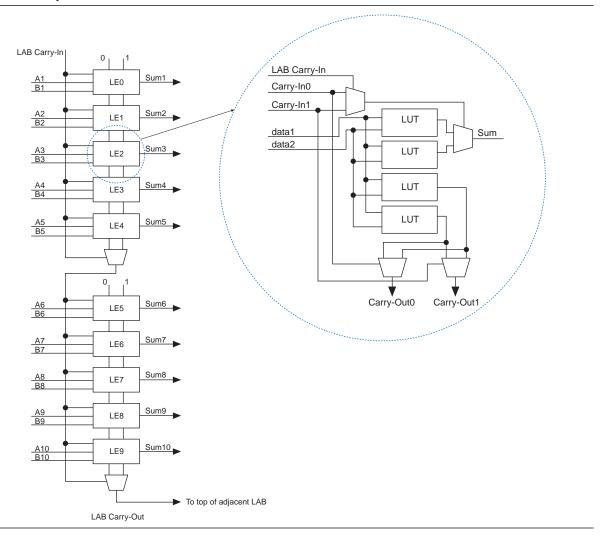

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the MAX II architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 2–9 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Figure 2-9. Carry-Select Chain

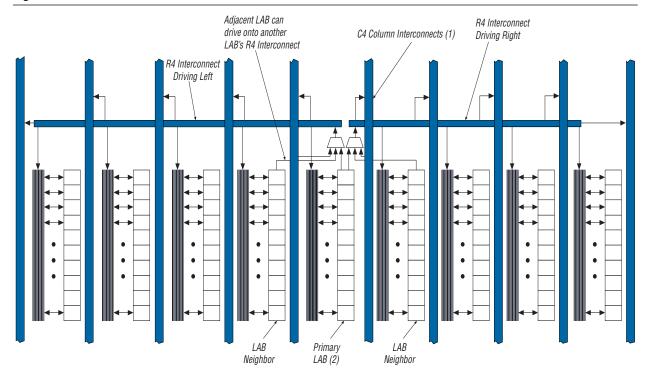

The R4 interconnects span four LABs and are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–10 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by row IOEs. For LAB interfacing, a primary LAB or horizontal LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

Figure 2–10. R4 Interconnect Connections

#### Notes to Figure 2-10:

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The column interconnect operates similarly to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs and row and column IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four LABs in an up and down direction

MAX II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinational output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in

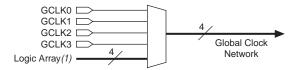

Figure 2–13. Global Clock Generation

#### Note to Figure 2-13:

(1) Any I/O pin can use a MultiTrack interconnect to route as a logic array-generated global clock signal.

The global clock network drives to individual LAB column signals, LAB column clocks [3..0], that span an entire LAB column from the top to the bottom of the device. Unused global clocks or control signals in a LAB column are turned off at the LAB column clock buffers shown in Figure 2–14. The LAB column clocks [3..0] are multiplexed down to two LAB clock signals and one LAB clear signal. Other control signal types route from the global clock network into the LAB local interconnect. See "LAB Control Signals" on page 2–5 for more information.

Figure 2-17. EPM570, EPM1270, and EPM2210 UFM Block LAB Row Interface

# **MultiVolt Core**

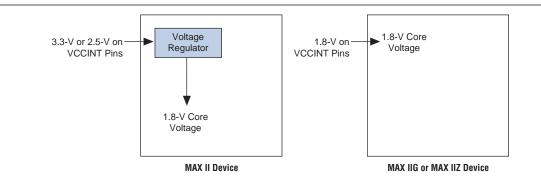

The MAX II architecture supports the MultiVolt core feature, which allows MAX II devices to support multiple  $V_{CC}$  levels on the  $V_{CCNT}$  supply. An internal linear voltage regulator provides the necessary 1.8-V internal voltage supply to the device. The voltage regulator supports 3.3-V or 2.5-V supplies on its inputs to supply the 1.8-V internal voltage to the device, as shown in Figure 2–18. The voltage regulator is not guaranteed for voltages that are between the maximum recommended 2.5-V operating voltage and the minimum recommended 3.3-V operating voltage.

The MAX IIG and MAX IIZ devices use external 1.8-V supply. The 1.8-V  $V_{CC}$  external supply powers the device core directly.

Figure 2–18. MultiVolt Core Feature in MAX II Devices

Table 2–4 describes the I/O standards supported by MAX II devices.

Table 2-4. MAX II I/O Standards

| I/O Standard       | Туре         | Output Supply Voltage<br>(VCCIO) (V) |

|--------------------|--------------|--------------------------------------|

| 3.3-V LVTTL/LVCMOS | Single-ended | 3.3                                  |

| 2.5-V LVTTL/LVCMOS | Single-ended | 2.5                                  |

| 1.8-V LVTTL/LVCMOS | Single-ended | 1.8                                  |

| 1.5-V LVCMOS       | Single-ended | 1.5                                  |

| 3.3-V PCI (1)      | Single-ended | 3.3                                  |

#### Note to Table 2-4:

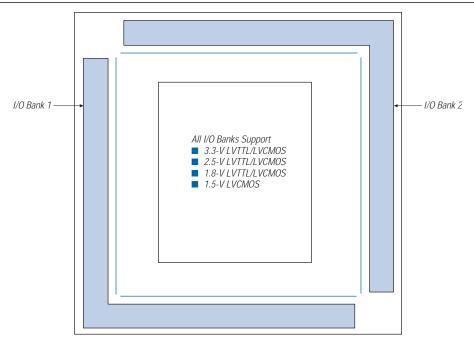

The EPM240 and EPM570 devices support two I/O banks, as shown in Figure 2–22. Each of these banks support all the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is not supported in these devices and banks.

Figure 2–22. MAX II I/O Banks for EPM240 and EPM570 (Note 1), (2)

#### Notes to Figure 2-22:

- (1) Figure 2-22 is a top view of the silicon die.

- (2) Figure 2–22 is a graphical representation only. Refer to the pin list and the Quartus II software for exact pin locations.

The EPM1270 and EPM2210 devices support four I/O banks, as shown in Figure 2–23. Each of these banks support all of the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is supported in Bank 3. Bank 3 supports the PCI clamping diode on inputs and PCI drive compliance on outputs. You must use Bank 3 for designs requiring PCI compliant I/O pins. The Quartus II software automatically places I/O pins in this bank if assigned with the PCI I/O standard.

The 3.3-V PCI compliant I/O is supported in Bank 3 of the EPM1270 and EPM2210 devices.

I/O Standard IOH/IOL Current Strength Setting (mA) 3.3-V LVTTL 16 8 3.3-V LVCMOS 8 4 2.5-V LVTTL/LVCMOS 14 7 1.8-V LVTTL/LVCMOS 6 3 4 1.5-V LVCMOS 2

**Table 2–6.** Programmable Drive Strength (Note 1)

#### Note to Table 2-6:

#### Slew-Rate Control

The output buffer for each MAX II device I/O pin has a programmable output slew-rate control that can be configured for low noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal output delay to rising and falling edges. The lower the voltage standard (for example, 1.8-V LVTTL) the larger the output delay when slow slew is enabled. Each I/O pin has an individual slew-rate control, allowing the designer to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

## **Open-Drain Output**

MAX II devices provide an optional open-drain (equivalent to open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (for example, interrupt and write enable signals) that can be asserted by any of several devices. This output can also provide an additional wired-OR plane.

## **Programmable Ground Pins**

Each unused I/O pin on MAX II devices can be used as an additional ground pin. This programmable ground feature does not require the use of the associated LEs in the device. In the Quartus II software, unused pins can be set as programmable GND on a global default basis or they can be individually assigned. Unused pins also have the option of being set as tri-stated input pins.

<sup>(1)</sup> The  $I_{OH}$  current strength numbers shown are for a condition of a  $V_{OUT} = V_{OH}$  minimum, where the  $V_{OH}$  minimum is specified by the I/O standard. The  $I_{OL}$  current strength numbers shown are for a condition of a  $V_{OUT} = V_{OL}$  maximum, where the  $V_{OL}$  maximum is specified by the I/O standard. For 2.5-V LVTTL/LVCMOS, the  $I_{OH}$  condition is  $V_{OUT} = 1.7$  V and the  $I_{OL}$  condition is  $V_{OUT} = 0.7$  V.

#### **IEEE 1532 Support**

The JTAG circuitry and ISP instruction set in MAX II devices is compliant to the IEEE 1532-2002 programming specification. This provides industry-standard hardware and software for in-system programming among multiple vendor programmable logic devices (PLDs) in a JTAG chain.

The MAX II 1532 BSDL files will be released on the Altera website when available.

## Jam Standard Test and Programming Language (STAPL)

The Jam STAPL JEDEC standard, JESD71, can be used to program MAX II devices with in-circuit testers, PCs, or embedded processors. The Jam byte code is also supported for MAX II devices. These software programming protocols provide a compact embedded solution for programming MAX II devices.

For more information, refer to the *Using Jam STAPL for ISP via an Embedded Processor* chapter in the *MAX II Device Handbook*.

## **Programming Sequence**

During in-system programming, 1532 instructions, addresses, and data are shifted into the MAX II device through the TDI input pin. Data is shifted out through the TDO output pin and compared against the expected data. Programming a pattern into the device requires the following six ISP steps. A stand-alone verification of a programmed pattern involves only stages 1, 2, 5, and 6. These steps are automatically executed by third-party programmers, the Quartus II software, or the Jam STAPL and Jam Byte-Code Players.

- 1. *Enter ISP*—The enter ISP stage ensures that the I/O pins transition smoothly from user mode to ISP mode.

- 2. *Check ID*—Before any program or verify process, the silicon ID is checked. The time required to read this silicon ID is relatively small compared to the overall programming time.

- 3. Sector Erase—Erasing the device in-system involves shifting in the instruction to erase the device and applying an erase pulse(s). The erase pulse is automatically generated internally by waiting in the run/test/idle state for the specified erase pulse time of 500 ms for the CFM block and 500 ms for each sector of the UFM block.

- 4. *Program*—Programming the device in-system involves shifting in the address, data, and program instruction and generating the program pulse to program the flash cells. The program pulse is automatically generated internally by waiting in the run/test/idle state for the specified program pulse time of 75 μs. This process is repeated for each address in the CFM and UFM blocks.

- 5. *Verify*—Verifying a MAX II device in-system involves shifting in addresses, applying the verify instruction to generate the read pulse, and shifting out the data for comparison. This process is repeated for each CFM and UFM address.

- 6. Exit ISP—An exit ISP stage ensures that the I/O pins transition smoothly from ISP mode to user mode.

#### I/O Pins Remain Tri-Stated during Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, the MAX II device's output buffers are turned off during system power-up. MAX II devices do not drive out until the device attains proper operating conditions and is fully configured. Refer to "Power-On Reset Circuitry" on page 4–5 for information about turn-on voltages.

## Signal Pins Do Not Drive the $V_{cco}$ or $V_{ccint}$ Power Supplies

MAX II devices do not have a current path from I/O pins or GCLK[3..0] pins to the  $V_{\text{CCIO}}$  or  $V_{\text{CCINT}}$  pins before or during power-up. A MAX II device may be inserted into (or removed from) a system board that was powered up without damaging or interfering with system-board operation. When hot socketing, MAX II devices may have a minimal effect on the signal integrity of the backplane.

## **AC and DC Specifications**

You can power up or power down the  $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$  pins in any sequence. During hot socketing, the I/O pin capacitance is less than 8 pF. MAX II devices meet the following hot socketing specifications:

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is:  $|I_{IOPIN}|$  < 8 mA for 10 ns or less.

MAX II devices are immune to latch-up when hot socketing. If the TCK JTAG input pin is driven high during hot socketing, the current on that pin might exceed the specifications above.

$I_{\text{IOPIN}}$  is the current at any user I/O pin on the device. The AC specification applies when the device is being powered up or powered down. This specification takes into account the pin capacitance but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading must be taken into consideration separately. The peak current duration due to power-up transients is 10 ns or less.

The DC specification applies when all  $V_{\text{CC}}$  supplies to the device are stable in the powered-up or powered-down conditions.

# **Hot Socketing Feature Implementation in MAX II Devices**

The hot socketing feature turns off (tri-states) the output buffer during the power-up event (either  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  supplies) or power-down event. The hot-socket circuit generates an internal HOTSCKT signal when either  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  is below the threshold voltage during power-up or power-down. The HOTSCKT signal cuts off the output buffer to make sure that no DC current (except for weak pull-up leaking) leaks through the pin. When  $V_{\text{CC}}$  ramps up very slowly during power-up,  $V_{\text{CC}}$  may still be relatively low even after the power-on reset (POR) signal is released and device configuration is complete.

# **Referenced Documents**

This chapter refereces the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

# **Document Revision History**

Table 4–1 shows the revision history for this chapter.

Table 4-1. Document Revision History

| Date and Revision             | Changes Made                                                                              | Summary of Changes                         |

|-------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------|

| October 2008, version2.1      | Updated "MAX II Hot-Socketing Specifications" and "Power-On<br>Reset Circuitry" sections. | _                                          |

|                               | Updated New Document Format.                                                              |                                            |

| December 2007,<br>version 2.0 | Updated "Hot Socketing Feature Implementation in MAX II<br>Devices" section.              | Updated document with MAX IIZ information. |

|                               | Updated "Power-On Reset Circuitry" section.                                               |                                            |

|                               | ■ Updated Figure 4–5.                                                                     |                                            |

|                               | Added "Referenced Documents" section.                                                     |                                            |

| December 2006, version 1.5    | Added document revision history.                                                          | _                                          |

| February 2006,                | <ul><li>Updated "MAX II Hot-Socketing Specifications" section.</li></ul>                  | _                                          |

| version 1.4                   | Updated "AC and DC Specifications" section.                                               |                                            |

|                               | Updated "Power-On Reset Circuitry" section.                                               |                                            |

| June 2005,<br>version 1.3     | Updated AC and DC specifications on page 4-2.                                             | _                                          |

| December 2004,                | Added content to Power-Up Characteristics section.                                        | _                                          |

| version 1.2                   | ■ Updated Figure 4-5.                                                                     |                                            |

| June 2004,<br>version 1.1     | Corrected Figure 4-2.                                                                     | _                                          |

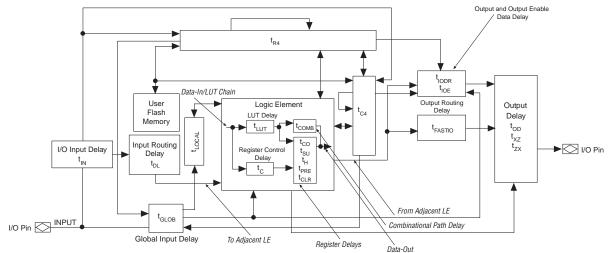

Figure 5–2. MAX II Device Timing Model

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays, can be calculated as the sum of internal parameters.

Refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook* for more information.

This section describes and specifies the performance, internal, external, and UFM timing specifications. All specifications are representative of the worst-case supply voltage and junction temperature conditions.

## **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–13 shows the status of the MAX II device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under the worst-case voltage and junction temperature conditions.

**Table 5–13.** MAX II Device Timing Model Status (Part 1 of 2)

| Device      | Preliminary | Final |

|-------------|-------------|-------|

| EPM240      | _           | ✓     |

| EPM240Z (1) | _           | ✓     |

| EPM570      | _           | ✓     |

| EPM570Z (1) | _           | ✓     |

## **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Table 5–15 through Table 5–22 describe the MAX II device internal timing microparameters for logic elements (LEs), input/output elements (IOEs), UFM blocks, and MultiTrack interconnects. The timing values for -3, -4, and -5 speed grades shown in Table 5–15 through Table 5–22 are based on an EPM1270 device target, while -6, -7, and -8 speed grade values are based on an EPM570Z device target.

For more explanations and descriptions about each internal timing microparameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

**Table 5–15.** LE Internal Timing Microparameters

|                    |                                        |     | MAX II / MAX IIG                                |     |                                  |     |       |     | MAX IIZ           |     |       |     |       |      |

|--------------------|----------------------------------------|-----|-------------------------------------------------|-----|----------------------------------|-----|-------|-----|-------------------|-----|-------|-----|-------|------|

|                    |                                        |     | -3 Speed -4 Speed -5 Speed<br>Grade Grade Grade |     | -6 Speed -7 Speed<br>Grade Grade |     |       |     | –8 Speed<br>Grade |     |       |     |       |      |

| Symbol             | Parameter                              | Min | Max                                             | Min | Max                              | Min | Max   | Min | Max               | Min | Max   | Min | Max   | Unit |

| t <sub>LUT</sub>   | LE combinational<br>LUT delay          | _   | 571                                             | _   | 742                              | _   | 914   | _   | 1,215             | _   | 2,247 | _   | 2,247 | ps   |

| t <sub>comb</sub>  | Combinational path delay               | _   | 147                                             | _   | 192                              | _   | 236   | _   | 243               | _   | 305   | _   | 309   | ps   |

| t <sub>CLR</sub>   | LE register clear<br>delay             | 238 | _                                               | 309 | _                                | 381 | _     | 401 | _                 | 541 | _     | 545 | _     | ps   |

| t <sub>PRE</sub>   | LE register preset delay               | 238 | _                                               | 309 | _                                | 381 | _     | 401 | _                 | 541 | _     | 545 | _     | ps   |

| t <sub>su</sub>    | LE register setup<br>time before clock | 208 | _                                               | 271 | _                                | 333 | _     | 260 | _                 | 319 | _     | 321 | _     | ps   |

| t <sub>H</sub>     | LE register hold time after clock      | 0   | _                                               | 0   | _                                | 0   | _     | 0   | _                 | 0   | _     | 0   | _     | ps   |

| t <sub>co</sub>    | LE register clock-<br>to-output delay  | _   | 235                                             | _   | 305                              | _   | 376   | _   | 380               | _   | 489   | _   | 494   | ps   |

| t <sub>CLKHL</sub> | Minimum clock<br>high or low time      | 166 | _                                               | 216 | _                                | 266 | _     | 253 | _                 | 335 | _     | 339 | _     | ps   |

| t <sub>c</sub>     | Register control delay                 | _   | 857                                             |     | 1,114                            |     | 1,372 | _   | 1,356             | _   | 1,722 | _   | 1,741 | ps   |

**Table 5–27.** External Timing Input Delay Adders (Part 2 of 2)

|                         |                            |     | N           | MAX II , | MAX I       | IG  |               |     |             | MA  | X IIZ       |     |             |      |

|-------------------------|----------------------------|-----|-------------|----------|-------------|-----|---------------|-----|-------------|-----|-------------|-----|-------------|------|

|                         |                            | ı   | peed<br>ade | 1        | peed<br>ade |     | Speed<br>rade |     | peed<br>ade |     | peed<br>ade | 1   | peed<br>ade |      |

| I/0 St                  | andard                     | Min | Max         | Min      | Max         | Min | Max           | Min | Max         | Min | Max         | Min | Max         | Unit |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0           | _        | 0           | _   | 0             | _   | 0           | _   | 0           | _   | 0           | ps   |

|                         | With Schmitt<br>Trigger    | _   | 334         | _        | 434         | _   | 535           | _   | 387         | _   | 434         | _   | 442         | ps   |

| 2.5-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 23          | _        | 30          | _   | 37            | _   | 42          | _   | 43          | _   | 43          | ps   |

|                         | With Schmitt<br>Trigger    | _   | 339         | _        | 441         | _   | 543           | _   | 429         | _   | 476         | _   | 483         | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 291         | _        | 378         | _   | 466           | _   | 378         | _   | 373         | _   | 373         | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 681         | _        | 885         | _   | 1,090         | _   | 681         | _   | 622         | _   | 658         | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 0           | _        | 0           | _   | 0             | _   | 0           | _   | 0           | _   | 0           | ps   |

**Table 5–28.** External Timing Input Delay  $t_{\mbox{\tiny GLOB}}$  Adders for GCLK Pins

|                         |                            |     | ľ           | II XAN | / MAX II     | G   |               |     |             | MA  | X IIZ       |     |             |      |

|-------------------------|----------------------------|-----|-------------|--------|--------------|-----|---------------|-----|-------------|-----|-------------|-----|-------------|------|

|                         |                            |     | peed<br>ade |        | Speed<br>ade |     | Speed<br>rade |     | peed<br>ade |     | peed<br>ade |     | peed<br>ade |      |

| I/0 St                  | andard                     | Min | Max         | Min    | Max          | Min | Max           | Min | Max         | Min | Max         | Min | Max         | Unit |

| 3.3-V LVTTL             | Without Schmitt<br>Trigger | _   | 0           | _      | 0            | _   | 0             | _   | 0           | _   | 0           | _   | 0           | ps   |

|                         | With Schmitt<br>Trigger    | _   | 308         | _      | 400          | _   | 493           | _   | 387         | _   | 434         | _   | 442         | ps   |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0           | _      | 0            | _   | 0             | _   | 0           | _   | 0           | _   | 0           | ps   |

|                         | With Schmitt<br>Trigger    | _   | 308         | _      | 400          | _   | 493           | _   | 387         | _   | 434         | _   | 442         | ps   |

| 2.5-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 21          | _      | 27           | _   | 33            | _   | 42          | _   | 43          | _   | 43          | ps   |

|                         | With Schmitt<br>Trigger    | _   | 423         | _      | 550          | _   | 677           | _   | 429         | _   | 476         | _   | 483         | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 353         | _      | 459          | _   | 565           | _   | 378         | _   | 373         | _   | 373         | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 855         | _      | 1,111        | _   | 1,368         | _   | 681         | _   | 622         | _   | 658         | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 6           | _      | 7            | _   | 9             | _   | 0           | _   | 0           | _   | 0           | ps   |

Table 5-33. MAX II Maximum Output Clock Rate for I/O

|              |              | MAX II / MAX IIG |                   |                   | MAX IIZ           |                   |                   |  |  |  |

|--------------|--------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|--|--|

| I/O Stand    | I/O Standard |                  | -4 Speed<br>Grade | –5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade |  |  |  |

| 3.3-V LVTTL  | 304          | 304              | 304               | 304               | 304               | 304               | MHz               |  |  |  |

| 3.3-V LVCMOS | 304          | 304              | 304               | 304               | 304               | 304               | MHz               |  |  |  |

| 2.5-V LVTTL  | 220          | 220              | 220               | 220               | 220               | 220               | MHz               |  |  |  |

| 2.5-V LVCMOS | 220          | 220              | 220               | 220               | 220               | 220               | MHz               |  |  |  |

| 1.8-V LVTTL  | 200          | 200              | 200               | 200               | 200               | 200               | MHz               |  |  |  |

| 1.8-V LVCMOS | 200          | 200              | 200               | 200               | 200               | 200               | MHz               |  |  |  |

| 1.5-V LVCMOS | 150          | 150              | 150               | 150               | 150               | 150               | MHz               |  |  |  |

| 3.3-V PCI    | 304          | 304              | 304               | 304               | 304               | 304               | MHz               |  |  |  |

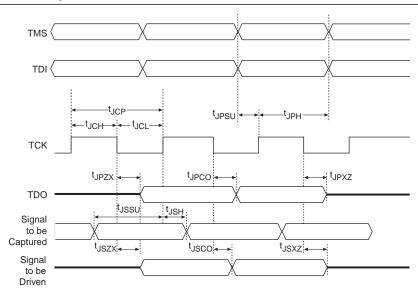

# **JTAG Timing Specifications**

Figure 5–6 shows the timing waveforms for the JTAG signals.

Figure 5-6. MAX II JTAG Timing Waveforms

Table 5–34 shows the JTAG Timing parameters and values for MAX II devices.

**Table 5–34.** MAX II JTAG Timing Parameters (Part 1 of 2)

| Symbol               | Parameter                                               | Min  | Max | Unit |

|----------------------|---------------------------------------------------------|------|-----|------|

| t <sub>JCP</sub> (1) | TCK clock period for $V_{\text{CCIO1}} = 3.3 \text{ V}$ | 55.5 | _   | ns   |

|                      | TCK clock period for $V_{\text{CCIO1}} = 2.5 \text{ V}$ | 62.5 | _   | ns   |

|                      | TCK clock period for $V_{CCIO1} = 1.8 \text{ V}$        | 100  | _   | ns   |

|                      | TCK clock period for $V_{CCIO1} = 1.5 \text{ V}$        | 143  | _   | ns   |

| t <sub>JCH</sub>     | TCK clock high time                                     | 20   | _   | ns   |

| t <sub>JCL</sub>     | TCK clock low time                                      | 20   | _   | ns   |

# **Referenced Documents**

This chapter references the following document:

■ Package Information chapter in the MAX II Device Handbook

# **Document Revision History**

Table 6–1 shows the revision history for this chapter.

Table 6-1. Document Revision History

| Date and Revision             | Changes Made                                                                        | Summary of Changes                         |

|-------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------|

| August 2009,<br>version 1.6   | ■ Updated Figure 6–1.                                                               | Added information for speed grade –8       |

| October 2008,<br>version 1.5  | Updated New Document Format.                                                        | _                                          |

| December 2007,<br>version 1.4 | <ul><li>Added "Referenced Documents" section.</li><li>Updated Figure 6–1.</li></ul> | Updated document with MAX IIZ information. |

| December 2006,<br>version 1.3 | Added document revision history.                                                    | _                                          |

| October 2006,<br>version 1.2  | <ul><li>Updated Figure 6-1.</li></ul>                                               | _                                          |

| June 2005,<br>version 1.1     | Removed Dual Marking section.                                                       | _                                          |