# E·XFL

## Intel - EPM570GT100C5N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### Applications of Embedded - CPLDs

#### Details

| Product Status                  | Active                                                    |

|---------------------------------|-----------------------------------------------------------|

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 5.4 ns                                                    |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                             |

| Number of Logic Elements/Blocks | 570                                                       |

| Number of Macrocells            | 440                                                       |

| Number of Gates                 | -                                                         |

| Number of I/O                   | 76                                                        |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                           |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 100-TQFP                                                  |

| Supplier Device Package         | 100-TQFP (14x14)                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm570gt100c5n |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

# Introduction

The MAX® II family of instant-on, non-volatile CPLDs is based on a 0.18-µm, 6-layer-metal-flash process, with densities from 240 to 2,210 logic elements (LEs) (128 to 2,210 equivalent macrocells) and non-volatile storage of 8 Kbits. MAX II devices offer high I/O counts, fast performance, and reliable fitting versus other CPLD architectures. Featuring MultiVolt core, a user flash memory (UFM) block, and enhanced in-system programmability (ISP), MAX II devices are designed to reduce cost and power while providing programmable solutions for applications such as bus bridging, I/O expansion, power-on reset (POR) and sequencing control, and device configuration control.

# **Features**

The MAX II CPLD has the following features:

- Low-cost, low-power CPLD

- Instant-on, non-volatile architecture

- Standby current as low as 25 μA

- Provides fast propagation delay and clock-to-output times

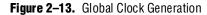

- Provides four global clocks with two clocks available per logic array block (LAB)

- UFM block up to 8 Kbits for non-volatile storage

- MultiVolt core enabling external supply voltages to the device of either 3.3 V/2.5 V or 1.8 V

- MultiVolt I/O interface supporting 3.3-V, 2.5-V, 1.8-V, and 1.5-V logic levels

- Bus-friendly architecture including programmable slew rate, drive strength, bus-hold, and programmable pull-up resistors

- Schmitt triggers enabling noise tolerant inputs (programmable per pin)

- I/Os are fully compliant with the Peripheral Component Interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 66 MHz

- Supports hot-socketing

- Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990

- ISP circuitry compliant with IEEE Std. 1532

MAX II devices have an internal linear voltage regulator which supports external supply voltages of 3.3 V or 2.5 V, regulating the supply down to the internal operating voltage of 1.8 V. MAX IIG and MAX IIZ devices only accept 1.8 V as the external supply voltage. MAX IIZ devices are pin-compatible with MAX IIG devices in the 100-pin Micro FineLine BGA and 256-pin Micro FineLine BGA packages. Except for external supply voltage requirements, MAX II and MAX II G devices have identical pin-outs and timing specifications. Table 1–5 shows the external supply voltages supported by the MAX II family.

Table 1–5. MAX II External Supply Voltages

| Devices                                                     | EPM240<br>EPM570<br>EPM1270<br>EPM2210 | EPM240G<br>EPM570G<br>EPM1270G<br>EPM2210G<br>EPM240Z<br>EPM570Z <i>(1)</i> |

|-------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------|

| MultiVolt core external supply voltage ( $V_{CCINT}$ ) (2)  | 3.3 V, 2.5 V                           | 1.8 V                                                                       |

| MultiVolt I/O interface voltage levels (V <sub>ccio</sub> ) | 1.5 V, 1.8 V, 2.5 V, 3.3 V             | 1.5 V, 1.8 V, 2.5 V, 3.3 V                                                  |

Notes to Table 1-5:

(1) MAX IIG and MAX IIZ devices only accept 1.8 V on their VCCINT pins. The 1.8-V V<sub>CCINT</sub> external supply powers the device core directly.

(2) MAX II devices operate internally at 1.8 V.

# **Referenced Documents**

This chapter references the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- MAX II Logic Element to Macrocell Conversion Methodology white paper

# **Document Revision History**

Table 1–6 shows the revision history for this chapter.

Table 1–6.

Document Revision History

| Date and Revision           | Changes Made                                              | Summary of Changes                         |

|-----------------------------|-----------------------------------------------------------|--------------------------------------------|

| August 2009,<br>version 1.9 | ■ Updated Table 1–2.                                      | Added information for speed grade –8       |

| October 2008,               | <ul> <li>Updated "Introduction" section.</li> </ul>       | —                                          |

| version 1.8                 | <ul> <li>Updated new Document Format.</li> </ul>          |                                            |

| December 2007,              | ■ Updated Table 1–1 through Table 1–5.                    | Updated document with MAX IIZ information. |

| version1.7                  | <ul> <li>Added "Referenced Documents" section.</li> </ul> |                                            |

| December 2006, version 1.6  | <ul> <li>Added document revision history.</li> </ul>      | _                                          |

| August 2006,<br>version 1.5 | <ul> <li>Minor update to features list.</li> </ul>        | _                                          |

| July 2006,<br>version 1.4   | <ul> <li>Minor updates to tables.</li> </ul>              | _                                          |

## Table 1–6. Document Revision History

| Date and Revision          | Changes Made                                             | Summary of Changes |

|----------------------------|----------------------------------------------------------|--------------------|

| June 2005,<br>version 1.3  | Updated timing numbers in Table 1-1.                     | _                  |

| December 2004, version 1.2 | <ul> <li>Updated timing numbers in Table 1-1.</li> </ul> | _                  |

| June 2004,<br>version 1.1  | <ul> <li>Updated timing numbers in Table 1-1.</li> </ul> | _                  |

## **Normal Mode**

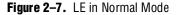

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–7). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinational output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

#### Note to Figure 2-7:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

### **Dynamic Arithmetic Mode**

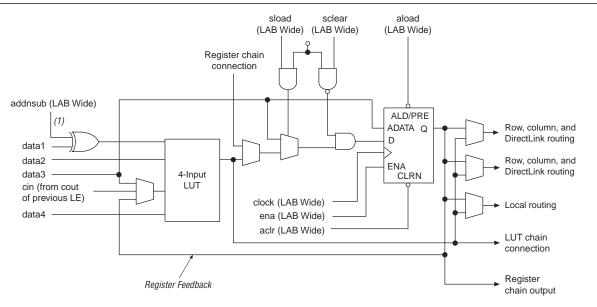

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry-select circuitry. As shown in Figure 2–8, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinational or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums:

```

data1 + data2 + carry in0

or

data1 + data2 + carry-in1

```

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the MAX II architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 2–9 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

#### Note to Figure 2-13:

(1) Any I/O pin can use a MultiTrack interconnect to route as a logic array-generated global clock signal.

The global clock network drives to individual LAB column signals, LAB column clocks [3..0], that span an entire LAB column from the top to the bottom of the device. Unused global clocks or control signals in a LAB column are turned off at the LAB column clock buffers shown in Figure 2–14. The LAB column clocks [3..0] are multiplexed down to two LAB clock signals and one LAB clear signal. Other control signal types route from the global clock network into the LAB local interconnect. See "LAB Control Signals" on page 2–5 for more information.

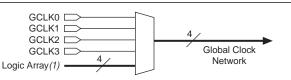

- Auto-increment addressing

- Serial interface to logic array with programmable interface

# **UFM Storage**

Each device stores up to 8,192 bits of data in the UFM block. Table 2–3 shows the data size, sector, and address sizes for the UFM block.

Table 2–3.

UFM Array Size

| Device  | Total Bits | Sectors             | Address Bits | Data Width |

|---------|------------|---------------------|--------------|------------|

| EPM240  | 8,192      | 2                   | 9            | 16         |

| EPM570  |            | (4,096 bits/sector) |              |            |

| EPM1270 |            |                     |              |            |

| EPM2210 |            |                     |              |            |

There are 512 locations with 9-bit addressing ranging from 000h to 1FFh. Sector 0 address space is 000h to 0FFh and Sector 1 address space is from 100h to 1FFh. The data width is up to 16 bits of data. The Quartus II software automatically creates logic to accommodate smaller read or program data widths. Erasure of the UFM involves individual sector erasing (that is, one erase of sector 0 and one erase of sector 1 is required to erase the entire UFM block). Since sector erase is required before a program or write, having two sectors enables a sector size of data to be left untouched while the other sector is erased and programmed with new data.

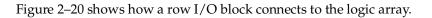

#### Note to Figure 2-20:

(1) Each of the seven IOEs in the row I/O block can have one data\_out or fast\_out output, one OE output, and one data\_in input.

Connect VCCIO pins to either a 1.5-V, 1.8 V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (that is, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems. Table 2–7 summarizes MAX II MultiVolt I/O support.

Table 2–7. MAX II MultiVolt I/O Support (Note 1)

|           | Input Signal |              |              |              | ut Signal Output Signal |              |              |              | al           |       |

|-----------|--------------|--------------|--------------|--------------|-------------------------|--------------|--------------|--------------|--------------|-------|

| VCCIO (V) | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V        | 5.0 V                   | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V        | 5.0 V |

| 1.5       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —                       | $\checkmark$ | _            |              | _            | —     |

| 1.8       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _                       | ✓ (2)        | $\checkmark$ | _            | _            | —     |

| 2.5       | _            | _            | $\checkmark$ | $\checkmark$ | _                       | ✓ (3)        | ✓ (3)        | $\checkmark$ | _            | _     |

| 3.3       | _            | —            | ✓ (4)        | $\checkmark$ | ✓ (5)                   | ✓ (6)        | ✓ (6)        | ✓ (6)        | $\checkmark$ | ✓ (7) |

#### Notes to Table 2-7:

(1) To drive inputs higher than  $V_{CGIO}$  but less than 4.0 V including the overshoot, disable the I/O clamp diode. However, to drive 5.0-V inputs to the device, enable the I/O clamp diode to prevent V<sub>1</sub> from rising above 4.0 V.

- (2) When  $V_{CCIO} = 1.8$  V, a MAX II device can drive a 1.5-V device with 1.8-V tolerant inputs.

- (3) When  $V_{CCIO} = 2.5$  V, a MAX II device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

- (4) When V<sub>CCI0</sub> = 3.3 V and a 2.5-V input signal feeds an input pin, the VCCI0 supply current will be slightly larger than expected.

- (5) MAX II devices can be 5.0-V tolerant with the use of an external resistor and the internal I/O clamp diode on the EPM1270 and EPM2210 devices.

- (6) When  $V_{CCIO} = 3.3$  V, a MAX II device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

- (7) When V<sub>CCI0</sub> = 3.3 V, a MAX II device can drive a device with 5.0-V TTL inputs but not 5.0-V CMOS inputs. In the case of 5.0-V CMOS, opendrain setting with internal I/O clamp diode (available only on EPM1270 and EPM2210 devices) and external resistor is required.

• For information about output pin source and sink current guidelines, refer to the *AN* 428: *MAX II CPLD Design Guidelines*.

# **Referenced Documents**

This chapter referenced the following documents:

- AN 428: MAX II CPLD Design Guidelines

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- *Hot Socketing and Power-On Reset in MAX II Devices* chapter in the *MAX II Device Handbook*

- Using User Flash Memory in MAX II Devices chapter in the MAX II Device Handbook

|  | Table 3-1. | MAX II JTAG | Instructions | (Part 2 of 2) |

|--|------------|-------------|--------------|---------------|

|--|------------|-------------|--------------|---------------|

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the boundary scan test data to pass synchronously through selected devices to adjacent devices during normal device operation, while holding I/O pins to a state defined by the data in the boundary-scan register. |

| USER0                     | 00 0000 1100     | This instruction allows you to define the scan chain between $TDI$ and $TDO$ in the MAX II logic array. This instruction is also used for custom logic and JTAG interfaces.                                                                                                                     |

| USER1                     | 00 0000 1110     | This instruction allows you to define the scan chain between $TDI$ and $TDO$ in the MAX II logic array. This instruction is also used for custom logic and JTAG interfaces.                                                                                                                     |

| IEEE 1532<br>instructions | (2)              | IEEE 1532 ISC instructions used when programming a MAX II device via the JTAG port.                                                                                                                                                                                                             |

### Notes to Table 3-1:

(1) HIGHZ, CLAMP, and EXTEST instructions do not disable weak pull-up resistors or bus hold features.

(2) These instructions are shown in the 1532 BSDL files, which will be posted on the Altera® website at www.altera.com when they are available.

Unsupported JTAG instructions should not be issued to the MAX II device as this may put the device into an unknown state, requiring a power cycle to recover device operation.

The MAX II device instruction register length is 10 bits and the USERCODE register length is 32 bits. Table 3–2 and Table 3–3 show the boundary-scan register length and device IDCODE information for MAX II devices.

Table 3–2. MAX II Boundary-Scan Register Length

| Device  | Boundary-Scan Register Length |

|---------|-------------------------------|

| EPM240  | 240                           |

| EPM570  | 480                           |

| EPM1270 | 636                           |

| EPM2210 | 816                           |

#### Table 3-3. 32-Bit MAX II Device IDCODE (Part 1 of 2)

| Device   | Version<br>(4 Bits) | Part Number         | Manufacturer<br>Identity (11 Bits) | LSB<br>(1 Bit) <i>(2)</i> | HEX IDCODE |

|----------|---------------------|---------------------|------------------------------------|---------------------------|------------|

| EPM240   | 0000                | 0010 0000 1010 0001 | 000 0110 1110                      | 1                         | 0x020A10DD |

| EPM240G  |                     |                     |                                    |                           |            |

| EPM570   | 0000                | 0010 0000 1010 0010 | 000 0110 1110                      | 1                         | 0x020A20DD |

| EPM570G  |                     |                     |                                    |                           |            |

| EPM1270  | 0000                | 0010 0000 1010 0011 | 000 0110 1110                      | 1                         | 0x020A30DD |

| EPM1270G |                     |                     |                                    |                           |            |

| EPM2210  | 0000                | 0010 0000 1010 0100 | 000 0110 1110                      | 1                         | 0x020A40DD |

| EPM2210G |                     |                     |                                    |                           |            |

## **IEEE 1532 Support**

The JTAG circuitry and ISP instruction set in MAX II devices is compliant to the IEEE 1532-2002 programming specification. This provides industry-standard hardware and software for in-system programming among multiple vendor programmable logic devices (PLDs) in a JTAG chain.

The MAX II 1532 BSDL files will be released on the Altera website when available.

## Jam Standard Test and Programming Language (STAPL)

The Jam STAPL JEDEC standard, JESD71, can be used to program MAX II devices with in-circuit testers, PCs, or embedded processors. The Jam byte code is also supported for MAX II devices. These software programming protocols provide a compact embedded solution for programming MAX II devices.

## **Programming Sequence**

During in-system programming, 1532 instructions, addresses, and data are shifted into the MAX II device through the TDI input pin. Data is shifted out through the TDO output pin and compared against the expected data. Programming a pattern into the device requires the following six ISP steps. A stand-alone verification of a programmed pattern involves only stages 1, 2, 5, and 6. These steps are automatically executed by third-party programmers, the Quartus II software, or the Jam STAPL and Jam Byte-Code Players.

- 1. *Enter ISP*—The enter ISP stage ensures that the I/O pins transition smoothly from user mode to ISP mode.

- 2. *Check ID*—Before any program or verify process, the silicon ID is checked. The time required to read this silicon ID is relatively small compared to the overall programming time.

- 3. *Sector Erase*—Erasing the device in-system involves shifting in the instruction to erase the device and applying an erase pulse(s). The erase pulse is automatically generated internally by waiting in the run/test/idle state for the specified erase pulse time of 500 ms for the CFM block and 500 ms for each sector of the UFM block.

- 4. *Program*—Programming the device in-system involves shifting in the address, data, and program instruction and generating the program pulse to program the flash cells. The program pulse is automatically generated internally by waiting in the run/test/idle state for the specified program pulse time of 75 µs. This process is repeated for each address in the CFM and UFM blocks.

- 5. *Verify*—Verifying a MAX II device in-system involves shifting in addresses, applying the verify instruction to generate the read pulse, and shifting out the data for comparison. This process is repeated for each CFM and UFM address.

- 6. *Exit ISP*—An exit ISP stage ensures that the I/O pins transition smoothly from ISP mode to user mode.

**<sup>•</sup>** For more information, refer to the Using Jam STAPL for ISP via an Embedded Processor chapter in the MAX II Device Handbook.

Table 3–4 shows the programming times for MAX II devices using in-circuit testers to execute the algorithm vectors in hardware. Software-based programming tools used with download cables are slightly slower because of data processing and transfer limitations.

| Description                     | EPM240<br>EPM240G<br>EPM240Z | EPM570<br>EPM570G<br>EPM570Z | EPM1270<br>EPM1270G | EPM2210<br>EPM2210G | Unit |

|---------------------------------|------------------------------|------------------------------|---------------------|---------------------|------|

| Erase + Program (1 MHz)         | 1.72                         | 2.16                         | 2.90                | 3.92                | Sec  |

| Erase + Program (10 MHz)        | 1.65                         | 1.99                         | 2.58                | 3.40                | sec  |

| Verify (1 MHz)                  | 0.09                         | 0.17                         | 0.30                | 0.49                | sec  |

| Verify (10 MHz)                 | 0.01                         | 0.02                         | 0.03                | 0.05                | sec  |

| Complete Program Cycle (1 MHz)  | 1.81                         | 2.33                         | 3.20                | 4.41                | sec  |

| Complete Program Cycle (10 MHz) | 1.66                         | 2.01                         | 2.61                | 3.45                | sec  |

Table 3-4. MAX II Device Family Programming Times

## **UFM Programming**

The Quartus II software, with the use of POF, Jam, or JBC files, supports programming of the user flash memory (UFM) block independent of the logic array design pattern stored in the CFM block. This allows updating or reading UFM contents through ISP without altering the current logic array design, or vice versa. By default, these programming files and methods will program the entire flash memory contents, which includes the CFM block and UFM contents. The stand-alone embedded Jam STAPL player and Jam Byte-Code Player provides action commands for programming or reading the entire flash memory (UFM and CFM together) or each independently.

For more information, refer to the *Using Jam STAPL for ISP via an Embedded Processor* chapter in the *MAX II Device Handbook*.

## **In-System Programming Clamp**

By default, the IEEE 1532 instruction used for entering ISP automatically tri-states all I/O pins with weak pull-up resistors for the duration of the ISP sequence. However, some systems may require certain pins on MAX II devices to maintain a specific DC logic level during an in-field update. For these systems, an optional in-system programming clamp instruction exists in MAX II circuitry to control I/O behavior during the ISP sequence. The in-system programming clamp instruction enables the device to sample and sustain the value on an output pin (an input pin would remain tri-stated if sampled) or to explicitly set a logic high, logic low, or tri-state value on any pin. Setting these options is controlled on an individual pin basis using the Quartus II software.

For more information, refer to the *Real-Time ISP and ISP Clamp for MAX II Devices* chapter in the *MAX II Device Handbook*.

# 4. Hot Socketing and Power-On Reset in MAX II Devices

#### MII51004-2.1

# Introduction

MAX<sup>®</sup> II devices offer hot socketing, also known as hot plug-in or hot swap, and power sequencing support. Designers can insert or remove a MAX II board in a system during operation without undesirable effects to the system bus. The hot socketing feature removes some of the difficulties designers face when using components on printed circuit boards (PCBs) that contain a mixture of 3.3-, 2.5-, 1.8-, and 1.5-V devices.

The MAX II device hot socketing feature provides:

- Board or device insertion and removal

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter contains the following sections:

- "MAX II Hot-Socketing Specifications" on page 4–1

- "Power-On Reset Circuitry" on page 4–5

# **MAX II Hot-Socketing Specifications**

MAX II devices offer all three of the features required for the hot-socketing capability listed above without any external components or special design requirements. The following are hot-socketing specifications:

- The device can be driven before and during power-up or power-down without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the  $V_{CCIO}$  or  $V_{CCINT}$  power supplies. External input signals to device I/O pins do not power the device  $V_{CCIO}$  or  $V_{CCINT}$  power supplies via internal paths. This is true if the  $V_{CCINT}$  and the  $V_{CCIO}$  supplies are held at GND.

## **Devices Can Be Driven before Power-Up**

Signals can be driven into the MAX II device I/O pins and GCLK[3..0] pins before or during power-up or power-down without damaging the device. MAX II devices support any power-up or power-down sequence ( $V_{CCIO1}$ ,  $V_{CCIO2}$ ,  $V_{CCIO3}$ ,  $V_{CCIO4}$ ,  $V_{CCINT}$ ), simplifying the system-level design.

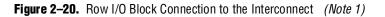

#### Notes to Figure 4–5:

(1) Time scale is relative.

(2) Figure 4–5 assumes all  $V_{CCIO}$  banks power up simultaneously with the  $V_{CCINT}$  profile shown. If not,  $t_{CONFIG}$  stretches out until all  $V_{CCIO}$  banks are powered.

After SRAM configuration, all registers in the device are cleared and released into user function before I/O tri-states are released. To release clears after tri-states are released, use the DEV\_CLRn pin option. To hold the tri-states beyond the power-up configuration time, use the DEV\_OE pin option.

# 5. DC and Switching Characteristics

# Introduction

System designers must consider the recommended DC and switching conditions discussed in this chapter to maintain the highest possible performance and reliability of the MAX<sup>®</sup> II devices. This chapter contains the following sections:

- "Operating Conditions" on page 5–1

- "Power Consumption" on page 5–8

- "Timing Model and Specifications" on page 5–8

# **Operating Conditions**

Table 5–1 through Table 5–12 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for MAX II devices.

## **Absolute Maximum Ratings**

Table 5-1 shows the absolute maximum ratings for the MAX II device family.

Table 5–1. MAX II Device Absolute Maximum Ratings (Note 1), (2)

| Symbol             | Parameter                      | Parameter Conditions             |      | Maximum | Unit |

|--------------------|--------------------------------|----------------------------------|------|---------|------|

| V <sub>CCINT</sub> | Internal supply voltage (3)    | With respect to ground           | -0.5 | 4.6     | V    |

| V <sub>CCIO</sub>  | I/O supply voltage             | —                                | -0.5 | 4.6     | V    |

| Vi                 | DC input voltage               | —                                | -0.5 | 4.6     | V    |

| I <sub>OUT</sub>   | DC output current, per pin (4) | —                                | -25  | 25      | mA   |

| T <sub>stg</sub>   | Storage temperature            | No bias                          | -65  | 150     | 0°   |

| T <sub>AMB</sub>   | Ambient temperature            | Under bias <i>(5)</i>            | -65  | 135     | 0°   |

| TJ                 | Junction temperature           | TQFP and BGA packages under bias | _    | 135     | J°   |

#### Notes to Table 5-1:

(1) Refer to the Operating Requirements for Altera Devices Data Sheet.

(2) Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

(3) Maximum  $V_{\mbox{\tiny CCINT}}$  for MAX II devices is 4.6 V. For MAX IIG and MAX IIZ devices, it is 2.4 V.

(4) Refer to AN 286: Implementing LED Drivers in MAX & MAX II Devices for more information about the maximum source and sink current for MAX II devices.

(5) Refer to Table 5–2 for information about "under bias" conditions.

| Device  | Preliminary | Final        |

|---------|-------------|--------------|

| EPM1270 | _           | $\checkmark$ |

| EPM2210 | _           | $\checkmark$ |

| N       | •           | •            |

Table 5–13.

MAX II Device Timing Model Status

(Part 2 of 2)

Note to Table 5-13:

(1) The MAX IIZ device timing models are only available in the Quartus II software version 8.0 and later.

## Performance

Table 5–14 shows the MAX II device performance for some common designs. All performance values were obtained with the Quartus II software compilation of megafunctions. Performance values for –3, –4, and –5 speed grades are based on an EPM1270 device target, while –6, –7, and –8 speed grades are based on an EPM570Z device target.

Table 5–14. MAX II Device Performance

|                  |                                         |                        | Performance |               |                      |                      |                      |                      |                      |                      |      |

|------------------|-----------------------------------------|------------------------|-------------|---------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|------|

|                  |                                         | Reso                   | ources      | Used          | MA                   | X II / MAX           | ( IIG                |                      |                      |                      |      |

| Resource<br>Used | Design Size and<br>Function             | Mode                   | LEs         | UFM<br>Blocks | –3<br>Speed<br>Grade | –4<br>Speed<br>Grade | –5<br>Speed<br>Grade | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade | Unit |

| LE               | 16-bit counter (1)                      | —                      | 16          | 0             | 304.0                | 247.5                | 201.1                | 184.1                | 123.5                | 118.3                | MHz  |

|                  | 64-bit counter (1)                      | —                      | 64          | 0             | 201.5                | 154.8                | 125.8                | 83.2                 | 83.2                 | 80.5                 | MHz  |

|                  | 16-to-1 multiplexer                     | _                      | 11          | 0             | 6.0                  | 8.0                  | 9.3                  | 17.4                 | 17.3                 | 20.4                 | ns   |

|                  | 32-to-1 multiplexer                     | _                      | 24          | 0             | 7.1                  | 9.0                  | 11.4                 | 12.5                 | 22.8                 | 25.3                 | ns   |

|                  | 16-bit XOR function                     | _                      | 5           | 0             | 5.1                  | 6.6                  | 8.2                  | 9.0                  | 15.0                 | 16.1                 | ns   |

|                  | 16-bit decoder with single address line |                        | 5           | 0             | 5.2                  | 6.6                  | 8.2                  | 9.2                  | 15.0                 | 16.1                 | ns   |

| UFM              | 512 × 16                                | None                   | 3           | 1             | 10.0                 | 10.0                 | 10.0                 | 10.0                 | 10.0                 | 10.0                 | MHz  |

|                  | 512 × 16                                | SPI <i>(2)</i>         | 37          | 1             | 8.0                  | 8.0                  | 8.0                  | 9.7                  | 9.7                  | 9.7                  | MHz  |

|                  | 512 × 8                                 | Parallel<br><i>(3)</i> | 73          | 1             | (4)                  | (4)                  | (4)                  | (4)                  | (4)                  | (4)                  | MHz  |

|                  | 512 × 16                                | I²C <i>(3)</i>         | 142         | 1             | 100<br><i>(5)</i>    | 100<br><i>(5)</i>    | 100<br><i>(5)</i>    | 100<br><i>(5)</i>    | 100<br><i>(5)</i>    | 100<br><i>(5)</i>    | kHz  |

### Notes to Table 5-14:

(1) This design is a binary loadable up counter.

(2) This design is configured for read-only operation in Extended mode. Read and write ability increases the number of LEs used.

(3) This design is configured for read-only operation. Read and write ability increases the number of LEs used.

(4) This design is asynchronous.

(5) The I<sup>2</sup>C megafunction is verified in hardware up to 100-kHz serial clock line (SCL) rate.

# **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Table 5–15 through Table 5–22 describe the MAX II device internal timing microparameters for logic elements (LEs), input/output elements (IOEs), UFM blocks, and MultiTrack interconnects. The timing values for –3, –4, and –5 speed grades shown in Table 5–15 through Table 5–22 are based on an EPM1270 device target, while –6, –7, and –8 speed grade values are based on an EPM570Z device target.

•••

• For more explanations and descriptions about each internal timing microparameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

Table 5–15. LE Internal Timing Microparameters

|                    |                                        |                   | I   | MAX II | / MAX I           | IG  |                   |     |                   |     |                   |     |                   |      |

|--------------------|----------------------------------------|-------------------|-----|--------|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|------|

|                    |                                        | –3 Speed<br>Grade |     |        | –4 Speed<br>Grade |     | –5 Speed<br>Grade |     | –6 Speed<br>Grade |     | –7 Speed<br>Grade |     | –8 Speed<br>Grade |      |

| Symbol             | Parameter                              | Min               | Max | Min    | Max               | Min | Max               | Min | Max               | Min | Max               | Min | Max               | Unit |

| t <sub>lut</sub>   | LE combinational<br>LUT delay          | _                 | 571 |        | 742               | —   | 914               | -   | 1,215             |     | 2,247             | —   | 2,247             | ps   |

| t <sub>сомв</sub>  | Combinational path delay               | —                 | 147 | _      | 192               | _   | 236               | -   | 243               | _   | 305               | -   | 309               | ps   |

| t <sub>clr</sub>   | LE register clear<br>delay             | 238               | _   | 309    | _                 | 381 |                   | 401 | _                 | 541 |                   | 545 |                   | ps   |

| t <sub>PRE</sub>   | LE register preset<br>delay            | 238               | _   | 309    | _                 | 381 |                   | 401 | _                 | 541 |                   | 545 |                   | ps   |

| t <sub>su</sub>    | LE register setup<br>time before clock | 208               | _   | 271    | _                 | 333 |                   | 260 | _                 | 319 |                   | 321 |                   | ps   |

| t <sub>H</sub>     | LE register hold<br>time after clock   | 0                 | —   | 0      | _                 | 0   |                   | 0   | _                 | 0   | _                 | 0   |                   | ps   |

| t <sub>co</sub>    | LE register clock-<br>to-output delay  | _                 | 235 | _      | 305               | _   | 376               | _   | 380               | _   | 489               | -   | 494               | ps   |

| t <sub>clkhl</sub> | Minimum clock<br>high or low time      | 166               | _   | 216    | _                 | 266 |                   | 253 | _                 | 335 |                   | 339 |                   | ps   |

| tc                 | Register control delay                 | —                 | 857 | —      | 1,114             | —   | 1,372             | —   | 1,356             | —   | 1,722             | —   | 1,741             | ps   |

|               |       |                   | Μ     | AX II / | MAX IIG | Ì                 |       | MAX IIZ           |     |                   |     |                   |     |      |  |

|---------------|-------|-------------------|-------|---------|---------|-------------------|-------|-------------------|-----|-------------------|-----|-------------------|-----|------|--|

|               |       | –3 Speed<br>Grade |       |         |         | –5 Speed<br>Grade |       | –6 Speed<br>Grade |     | –7 Speed<br>Grade |     | –8 Speed<br>Grade |     |      |  |

| I/O Standa    | rd    | Min               | Max   | Min     | Max     | Min               | Max   | Min               | Max | Min Max           |     | Min               | Max | Unit |  |

| 3.3-V LVTTL   | 16 mA | —                 | 0     | —       | 0       | _                 | 0     | —                 | 0   | —                 | 0   | —                 | 0   | ps   |  |

|               | 8 mA  |                   | 65    | —       | 84      |                   | 104   | —                 | -6  | —                 | -2  | —                 | -3  | ps   |  |

| 3.3-V LVCMOS  | 8 mA  |                   | 0     | —       | 0       |                   | 0     | —                 | 0   | —                 | 0   | —                 | 0   | ps   |  |

|               | 4 mA  | —                 | 65    | —       | 84      | —                 | 104   | —                 | -6  | —                 | -2  | —                 | -3  | ps   |  |

| 2.5-V LVTTL / | 14 mA | _                 | 122   |         | 158     |                   | 195   | _                 | -63 | —                 | -71 | —                 | -88 | ps   |  |

| LVCMOS        | 7 mA  | _                 | 193   |         | 251     |                   | 309   | —                 | 10  | —                 | -1  | —                 | 1   | ps   |  |

| 1.8-V LVTTL / | 6 mA  | _                 | 568   |         | 738     |                   | 909   | _                 | 128 | —                 | 118 | —                 | 118 | ps   |  |

| LVCMOS        | 3 mA  | _                 | 654   | _       | 850     |                   | 1,046 | _                 | 352 | —                 | 327 | —                 | 332 | ps   |  |

| 1.5-V LVCMOS  | 4 mA  | _                 | 1,059 | —       | 1,376   |                   | 1,694 |                   | 421 | —                 | 400 | —                 | 400 | ps   |  |

|               | 2 mA  | _                 | 1,167 |         | 1,517   |                   | 1,867 | _                 | 757 | —                 | 743 | —                 | 743 | ps   |  |

| 3.3-V PCI     | 20 mA | _                 | 3     | —       | 4       | _                 | 5     | _                 | -6  | —                 | -2  | —                 | -3  | ps   |  |

Table 5–29. External Timing Output Delay and  $t_{\scriptscriptstyle OD}$  Adders for Fast Slew Rate

|               |       |     | Speed<br>rade | –4 Speed<br>Grade |        | –5 Speed<br>Grade |        | –6 Speed<br>Grade |        | –7 Speed<br>Grade |        | –8 Speed<br>Grade |        |      |

|---------------|-------|-----|---------------|-------------------|--------|-------------------|--------|-------------------|--------|-------------------|--------|-------------------|--------|------|

| I/O Standa    | rd    | Min | Max           | Min               | Max    | Min               | Max    | Min               | Max    | Min               | Max    | Min Max           |        | Unit |

| 3.3-V LVTTL   | 16 mA | _   | 7,064         | —                 | 6,745  | —                 | 6,426  | —                 | 5,966  | —                 | 5,992  | —                 | 6,118  | ps   |

|               | 8 mA  |     | 7,946         |                   | 7,627  |                   | 7,308  |                   | 6,541  |                   | 6,570  | —                 | 6,720  | ps   |

| 3.3-V LVCMOS  | 8 mA  | _   | 7,064         |                   | 6,745  |                   | 6,426  |                   | 5,966  |                   | 5,992  | —                 | 6,118  | ps   |

|               | 4 mA  | _   | 7,946         | _                 | 7,627  |                   | 7,308  |                   | 6,541  |                   | 6,570  | —                 | 6,720  | ps   |

| 2.5-V LVTTL / | 14 mA | _   | 10,434        | _                 | 10,115 |                   | 9,796  |                   | 9,141  |                   | 9,154  | —                 | 9,297  | ps   |

| LVCMOS        | 7 mA  | _   | 11,548        | —                 | 11,229 |                   | 10,910 |                   | 9,861  |                   | 9,874  | —                 | 10,037 | ps   |

| 1.8-V LVTTL / | 6 mA  | _   | 22,927        | —                 | 22,608 |                   | 22,289 |                   | 21,811 |                   | 21,854 | —                 | 21,857 | ps   |

| LVCMOS        | 3 mA  | _   | 24,731        | _                 | 24,412 |                   | 24,093 | _                 | 23,081 |                   | 23,034 | —                 | 23,107 | ps   |

| 1.5-V LVCMOS  | 4 mA  | _   | 38,723        | —                 | 38,404 |                   | 38,085 |                   | 39,121 |                   | 39,124 | —                 | 39,124 | ps   |

|               | 2 mA  | _   | 41,330        | _                 | 41,011 |                   | 40,692 |                   | 40,631 |                   | 40,634 | —                 | 40,634 | ps   |

| 3.3-V PCI     | 20 mA |     | 261           |                   | 339    |                   | 418    |                   | 6,644  |                   | 6,627  |                   | 6,914  | ps   |