Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                          |

|---------------------------------|----------------------------------------------------------|

| Product Status                  | Active                                                   |

| Programmable Type               | In System Programmable                                   |

| Delay Time tpd(1) Max           | 5.4 ns                                                   |

| Voltage Supply - Internal       | 2.5V, 3.3V                                               |

| Number of Logic Elements/Blocks | 570                                                      |

| Number of Macrocells            | 440                                                      |

| Number of Gates                 | -                                                        |

| Number of I/O                   | 76                                                       |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                          |

| Mounting Type                   | Surface Mount                                            |

| Package / Case                  | 100-TFBGA                                                |

| Supplier Device Package         | 100-MBGA (6x6)                                           |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm570m100c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

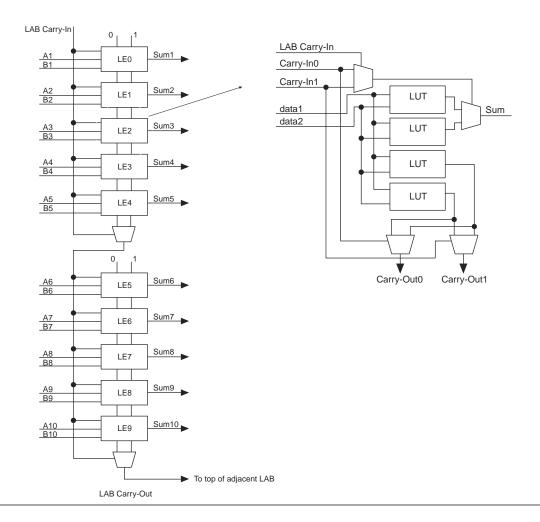

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the MAX II architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 2–9 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Figure 2-9. Carry-Select Chain

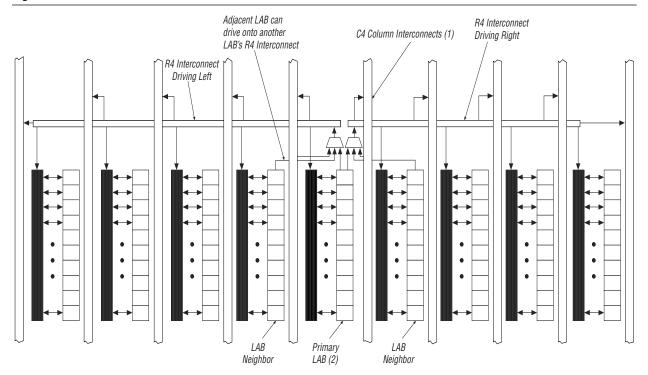

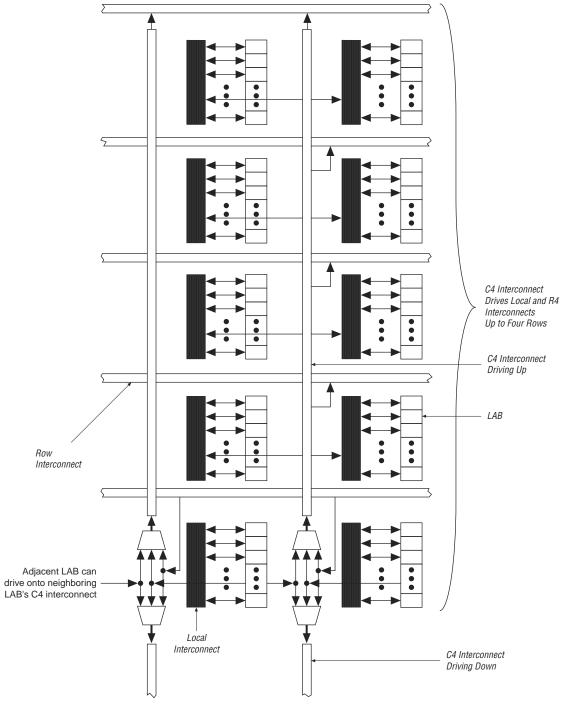

The R4 interconnects span four LABs and are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–10 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by row IOEs. For LAB interfacing, a primary LAB or horizontal LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

Figure 2-10. R4 Interconnect Connections

#### Notes to Figure 2-10:

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The column interconnect operates similarly to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs and row and column IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four LABs in an up and down direction

MAX II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinational output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in

Figure 2–12. C4 Interconnect Connections (Note 1)

### Note to Figure 2–12:

(1) Each C4 interconnect can drive either up or down four rows.

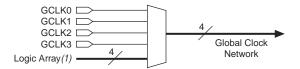

Figure 2–13. Global Clock Generation

#### Note to Figure 2-13:

(1) Any I/O pin can use a MultiTrack interconnect to route as a logic array-generated global clock signal.

The global clock network drives to individual LAB column signals, LAB column clocks [3..0], that span an entire LAB column from the top to the bottom of the device. Unused global clocks or control signals in a LAB column are turned off at the LAB column clock buffers shown in Figure 2–14. The LAB column clocks [3..0] are multiplexed down to two LAB clock signals and one LAB clear signal. Other control signal types route from the global clock network into the LAB local interconnect. See "LAB Control Signals" on page 2–5 for more information.

### **Internal Oscillator**

As shown in Figure 2–15, the dedicated circuitry within the UFM block contains an oscillator. The dedicated circuitry uses this internally for its read and program operations. This oscillator's divide by 4 output can drive out of the UFM block as a logic interface clock source or for general-purpose logic clocking. The typical OSC output signal frequency ranges from 3.3 to 5.5 MHz, and its exact frequency of operation is not programmable.

### **Program, Erase, and Busy Signals**

The UFM block's dedicated circuitry automatically generates the necessary internal program and erase algorithm once the PROGRAM or ERASE input signals have been asserted. The PROGRAM or ERASE signal must be asserted until the busy signal deasserts, indicating the UFM internal program or erase operation has completed. The UFM block also supports JTAG as the interface for programming and/or reading.

For more information about programming and erasing the UFM block, refer to the *Using User Flash Memory in MAX II Devices* chapter in the *MAX II Device Handbook*.

### **Auto-Increment Addressing**

The UFM block supports standard read or stream read operations. The stream read is supported with an auto-increment address feature. Deasserting the ARSHIFT signal while clocking the ARCLK signal increments the address register value to read consecutive locations from the UFM array.

### **Serial Interface**

The UFM block supports a serial interface with serial address and data signals. The internal shift registers within the UFM block for address and data are 9 bits and 16 bits wide, respectively. The Quartus II software automatically generates interface logic in LEs for a parallel address and data interface to the UFM block. Other standard protocol interfaces such as SPI are also automatically generated in LE logic by the Quartus II software.

For more information about the UFM interface signals and the Quartus II LE-based alternate interfaces, refer to the *Using User Flash Memory in MAX II Devices* chapter in the *MAX II Device Handbook*.

# **UFM Block to Logic Array Interface**

The UFM block is a small partition of the flash memory that contains the CFM block, as shown in Figure 2–1 and Figure 2–2. The UFM block for the EPM240 device is located on the left side of the device adjacent to the left most LAB column. The UFM block for the EPM570, EPM1270, and EPM2210 devices is located at the bottom left of the device. The UFM input and output signals interface to all types of interconnects (R4 interconnect, C4 interconnect, and DirectLink interconnect to/from adjacent LAB rows). The UFM signals can also be driven from global clocks, GCLK[3..0]. The interface region for the EPM240 device is shown in Figure 2–16. The interface regions for EPM570, EPM1270, and EPM2210 devices are shown in Figure 2–17.

Table 2–4 describes the I/O standards supported by MAX II devices.

Table 2-4. MAX II I/O Standards

| I/O Standard       | Туре         | Output Supply Voltage<br>(VCCIO) (V) |

|--------------------|--------------|--------------------------------------|

| 3.3-V LVTTL/LVCMOS | Single-ended | 3.3                                  |

| 2.5-V LVTTL/LVCMOS | Single-ended | 2.5                                  |

| 1.8-V LVTTL/LVCMOS | Single-ended | 1.8                                  |

| 1.5-V LVCMOS       | Single-ended | 1.5                                  |

| 3.3-V PCI (1)      | Single-ended | 3.3                                  |

#### Note to Table 2-4:

The EPM240 and EPM570 devices support two I/O banks, as shown in Figure 2–22. Each of these banks support all the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is not supported in these devices and banks.

Figure 2–22. MAX II I/O Banks for EPM240 and EPM570 (Note 1), (2)

#### Notes to Figure 2-22:

- (1) Figure 2-22 is a top view of the silicon die.

- (2) Figure 2–22 is a graphical representation only. Refer to the pin list and the Quartus II software for exact pin locations.

The EPM1270 and EPM2210 devices support four I/O banks, as shown in Figure 2–23. Each of these banks support all of the LVTTL and LVCMOS standards shown in Table 2–4. PCI compliant I/O is supported in Bank 3. Bank 3 supports the PCI clamping diode on inputs and PCI drive compliance on outputs. You must use Bank 3 for designs requiring PCI compliant I/O pins. The Quartus II software automatically places I/O pins in this bank if assigned with the PCI I/O standard.

The 3.3-V PCI compliant I/O is supported in Bank 3 of the EPM1270 and EPM2210 devices.

# **Document Revision History**

Table 2–8 shows the revision history for this chapter.

Table 2-8. Document Revision History

| Date and Revision             | Changes Made                                                                       | Summary of Changes    |

|-------------------------------|------------------------------------------------------------------------------------|-----------------------|

| October 2008,                 | ■ Updated Table 2–4 and Table 2–6.                                                 | _                     |

| version 2.2                   | ■ Updated "I/O Standards and Banks" section.                                       |                       |

|                               | ■ Updated New Document Format.                                                     |                       |

| March 2008,<br>version 2.1    | ■ Updated "Schmitt Trigger" section.                                               | _                     |

| December 2007,                | ■ Updated "Clear and Preset Logic Control" section.                                | Updated document with |

| version 2.0                   | ■ Updated "MultiVolt Core" section.                                                | MAX IIZ information.  |

|                               | ■ Updated "MultiVolt I/O Interface" section.                                       |                       |

|                               | ■ Updated Table 2–7.                                                               |                       |

|                               | ■ Added "Referenced Documents" section.                                            |                       |

| December 2006,<br>version 1.7 | Minor update in "Internal Oscillator" section. Added document<br>revision history. | _                     |

| August 2006,<br>version 1.6   | ■ Updated functional description and I/O structure sections.                       | _                     |

| July 2006,<br>vervion 1.5     | ■ Minor content and table updates.                                                 | _                     |

| February 2006,                | ■ Updated "LAB Control Signals" section.                                           | _                     |

| version 1.4                   | ■ Updated "Clear and Preset Logic Control" section.                                |                       |

|                               | ■ Updated "Internal Oscillator" section.                                           |                       |

|                               | ■ Updated Table 2–5.                                                               |                       |

| August 2005,<br>version 1.3   | Removed Note 2 from Table 2-7.                                                     | _                     |

| December 2004,<br>version 1.2 | Added a paragraph to page 2-15.                                                    | _                     |

| June 2004,<br>version 1.1     | Added CFM acronym. Corrected Figure 2-19.                                          | _                     |

**Table 3–3.** 32-Bit MAX II Device IDCODE (Part 2 of 2)

|         |                     | Binary IDCODE (32 Bits) (1) |                                    |                           |            |  |  |  |  |  |  |

|---------|---------------------|-----------------------------|------------------------------------|---------------------------|------------|--|--|--|--|--|--|

| Device  | Version<br>(4 Bits) | Part Number                 | Manufacturer<br>Identity (11 Bits) | LSB<br>(1 Bit) <i>(2)</i> | HEX IDCODE |  |  |  |  |  |  |

| EPM240Z | 0000                | 0010 0000 1010 0101         | 000 0110 1110                      | 1                         | 0x020A50DD |  |  |  |  |  |  |

| EPM570Z | 0000                | 0010 0000 1010 0110         | 000 0110 1110                      | 1                         | 0x020A60DD |  |  |  |  |  |  |

#### Notes to Table 3-2:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

For more information about JTAG BST, refer to the *IEEE 1149.1 (JTAG) Boundary-Scan Testing for MAX II Devices* chapter in the *MAX II Device Handbook*.

### **JTAG Block**

The MAX II JTAG block feature allows you to access the JTAG TAP and state signals when either the USER0 or USER1 instruction is issued to the JTAG TAP. The USER0 and USER1 instructions bring the JTAG boundary-scan chain (TDI) through the user logic instead of the MAX II device's boundary-scan cells. Each USER instruction allows for one unique user-defined JTAG chain into the logic array.

#### **Parallel Flash Loader**

The JTAG block ability to interface JTAG to non-JTAG devices is ideal for general-purpose flash memory devices (such as Intel- or Fujitsu-based devices) that require programming during in-circuit test. The flash memory devices can be used for FPGA configuration or be part of system memory. In many cases, the MAX II device is already connected to these devices as the configuration control logic between the FPGA and the flash device. Unlike ISP-capable CPLD devices, bulk flash devices do not have JTAG TAP pins or connections. For small flash devices, it is common to use the serial JTAG scan chain of a connected device to program the non-JTAG flash device. This is slow and inefficient in most cases and impractical for large parallel flash devices. Using the MAX II device's JTAG block as a parallel flash loader, with the Quartus II software, to program and verify flash contents provides a fast and cost-effective means of in-circuit programming during test. Figure 3–1 shows MAX II being used as a parallel flash loader.

**MAX II Device** Flash Altera FPGA **Memory Device** CONF DONE nSTATUS nCE DATA0 **nCONFIG** TDO\_U DCLK TDI\_U TDI TMS TMS\_U TCK\_U SHIFT U CLKDR\_U TDO UPDATE\_U

RUNIDLE\_U USER1\_U

Figure 3–1. MAX II Parallel Flash Loader

#### Notes to Figure 3-1:

- This block is implemented in LEs.

- (2) This function is supported in the Quartus II software.

# In System Programmability

MAX II devices can be programmed in-system via the industry standard 4-pin IEEE Std. 1149.1 (JTAG) interface. In-system programmability (ISP) offers quick, efficient iterations during design development and debugging cycles. The logic, circuitry, and interconnects in the MAX II architecture are configured with flash-based SRAM configuration elements. These SRAM elements require configuration data to be loaded each time the device is powered. The process of loading the SRAM data is called configuration. The on-chip configuration flash memory (CFM) block stores the SRAM element's configuration data. The CFM block stores the design's configuration pattern in a reprogrammable flash array. During ISP, the MAX II JTAG and ISP circuitry programs the design pattern into the CFM block's non-volatile flash array.

The MAX II JTAG and ISP controller internally generate the high programming voltages required to program the CFM cells, allowing in-system programming with any of the recommended operating external voltage supplies (that is, 3.3 V/2.5 V or 1.8 V for the MAX IIG and MAX IIZ devices). ISP can be performed anytime after  $V_{\text{CCINT}}$  and all  $V_{\text{CCIO}}$  banks have been fully powered and the device has completed the configuration power-up time. By default, during in-system programming, the I/O pins are tri-stated and weakly pulled-up to  $V_{\text{CCIO}}$  to eliminate board conflicts. The insystem programming clamp and real-time ISP feature allow user control of I/O state or behavior during ISP.

For more information, refer to "In-System Programming Clamp" on page 3–6 and "Real-Time ISP" on page 3–7.

These devices also offer an ISP\_DONE bit that provides safe operation when insystem programming is interrupted. This ISP\_DONE bit, which is the last bit programmed, prevents all I/O pins from driving until the bit is programmed.

### **IEEE 1532 Support**

The JTAG circuitry and ISP instruction set in MAX II devices is compliant to the IEEE 1532-2002 programming specification. This provides industry-standard hardware and software for in-system programming among multiple vendor programmable logic devices (PLDs) in a JTAG chain.

The MAX II 1532 BSDL files will be released on the Altera website when available.

### Jam Standard Test and Programming Language (STAPL)

The Jam STAPL JEDEC standard, JESD71, can be used to program MAX II devices with in-circuit testers, PCs, or embedded processors. The Jam byte code is also supported for MAX II devices. These software programming protocols provide a compact embedded solution for programming MAX II devices.

For more information, refer to the *Using Jam STAPL for ISP via an Embedded Processor* chapter in the *MAX II Device Handbook*.

### **Programming Sequence**

During in-system programming, 1532 instructions, addresses, and data are shifted into the MAX II device through the TDI input pin. Data is shifted out through the TDO output pin and compared against the expected data. Programming a pattern into the device requires the following six ISP steps. A stand-alone verification of a programmed pattern involves only stages 1, 2, 5, and 6. These steps are automatically executed by third-party programmers, the Quartus II software, or the Jam STAPL and Jam Byte-Code Players.

- 1. *Enter ISP*—The enter ISP stage ensures that the I/O pins transition smoothly from user mode to ISP mode.

- 2. *Check ID*—Before any program or verify process, the silicon ID is checked. The time required to read this silicon ID is relatively small compared to the overall programming time.

- 3. Sector Erase—Erasing the device in-system involves shifting in the instruction to erase the device and applying an erase pulse(s). The erase pulse is automatically generated internally by waiting in the run/test/idle state for the specified erase pulse time of 500 ms for the CFM block and 500 ms for each sector of the UFM block.

- 4. *Program*—Programming the device in-system involves shifting in the address, data, and program instruction and generating the program pulse to program the flash cells. The program pulse is automatically generated internally by waiting in the run/test/idle state for the specified program pulse time of 75 μs. This process is repeated for each address in the CFM and UFM blocks.

- 5. *Verify*—Verifying a MAX II device in-system involves shifting in addresses, applying the verify instruction to generate the read pulse, and shifting out the data for comparison. This process is repeated for each CFM and UFM address.

- 6. Exit ISP—An exit ISP stage ensures that the I/O pins transition smoothly from ISP mode to user mode.

# **Referenced Documents**

This chapter refereces the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

# **Document Revision History**

Table 4–1 shows the revision history for this chapter.

Table 4-1. Document Revision History

| Date and Revision             | Changes Made                                                                              | Summary of Changes                         |

|-------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------|

| October 2008, version2.1      | Updated "MAX II Hot-Socketing Specifications" and "Power-On<br>Reset Circuitry" sections. | _                                          |

|                               | ■ Updated New Document Format.                                                            |                                            |

| December 2007,<br>version 2.0 | Updated "Hot Socketing Feature Implementation in MAX II<br>Devices" section.              | Updated document with MAX IIZ information. |

|                               | ■ Updated "Power-On Reset Circuitry" section.                                             |                                            |

|                               | ■ Updated Figure 4–5.                                                                     |                                            |

|                               | <ul><li>Added "Referenced Documents" section.</li></ul>                                   |                                            |

| December 2006, version 1.5    | Added document revision history.                                                          | _                                          |

| February 2006,                | ■ Updated "MAX II Hot-Socketing Specifications" section.                                  | _                                          |

| version 1.4                   | Updated "AC and DC Specifications" section.                                               |                                            |

|                               | ■ Updated "Power-On Reset Circuitry" section.                                             |                                            |

| June 2005,<br>version 1.3     | ■ Updated AC and DC specifications on page 4-2.                                           | _                                          |

| December 2004,                | Added content to Power-Up Characteristics section.                                        | _                                          |

| version 1.2                   | ■ Updated Figure 4-5.                                                                     |                                            |

| June 2004,<br>version 1.1     | ■ Corrected Figure 4-2.                                                                   | _                                          |

# **Programming/Erasure Specifications**

Table 5–3 shows the MAX II device family programming/erasure specifications.

**Table 5–3.** MAX II Device Programming/Erasure Specifications

| Parameter                  | Minimum | Typical | Maximum        | Unit   |

|----------------------------|---------|---------|----------------|--------|

| Erase and reprogram cycles | _       | _       | 100 <i>(1)</i> | Cycles |

### Note to Table 5-3:

(1) This specification applies to the UFM and configuration flash memory (CFM) blocks.

### **DC Electrical Characteristics**

Table 5–4 shows the MAX II device family DC electrical characteristics.

**Table 5–4.** MAX II Device DC Electrical Characteristics (*Note 1*) (Part 1 of 2)

| Symbol                   | Parameter                             | Conditions                           | Minimum | Typical | Maximum | Unit |

|--------------------------|---------------------------------------|--------------------------------------|---------|---------|---------|------|

| I <sub>I</sub>           | Input pin leakage current             | $V_1 = V_{ccio} max to 0 V (2)$      | -10     |         | 10      | μА   |

| I <sub>oz</sub>          | Tri-stated I/O pin<br>leakage current | $V_0 = V_{ccio}$ max to 0 V (2)      | -10     | _       | 10      | μА   |

| I <sub>CCSTANDBY</sub>   | V <sub>CCINT</sub> supply current     | MAX II devices                       |         | 12      | _       | mA   |

|                          | (standby) (3)                         | MAX IIG devices                      | _       | 2       | _       | mA   |

| (standby) (3)            |                                       | EPM240Z (Commercial grade) (4)       | _       | 25      | 90      | μА   |

|                          |                                       | EPM240Z (Industrial grade) (5)       | _       | 25      | 139     | μА   |

|                          |                                       | EPM570Z (Commercial grade) (4)       | _       | 27      | 96      | μΑ   |

|                          |                                       | EPM570Z (Industrial grade) (5)       | _       | 27      | 152     | μА   |

| V <sub>SCHMITT</sub> (6) | Hysteresis for Schmitt                | V <sub>ccio</sub> = 3.3 V            | _       | 400     | _       | mV   |

|                          | trigger input (7)                     | V <sub>CCIO</sub> = 2.5 V            | _       | 190     | _       | mV   |

| I <sub>CCPOWERUP</sub>   | V <sub>CCINT</sub> supply current     | MAX II devices                       | _       | 55      | _       | mA   |

|                          | during power-up (8)                   | MAX IIG and MAX IIZ devices          | _       | 40      | _       | mA   |

| R <sub>PULLUP</sub>      | Value of I/O pin pull-up              | V <sub>ccio</sub> = 3.3 V (9)        | 5       | _       | 25      | kΩ   |

|                          | resistor during user                  | V <sub>ccio</sub> = 2.5 V (9)        | 10      | _       | 40      | kΩ   |

|                          | mode and in-system programming        | V <sub>ccio</sub> = 1.8 V (9)        | 25      | _       | 60      | kΩ   |

|                          | . 5                                   | V <sub>ccio</sub> = 1.5 V <i>(9)</i> | 45      | _       | 95      | kΩ   |

**Operating Conditions**

**Table 5–4.** MAX II Device DC Electrical Characteristics (*Note 1*) (Part 2 of 2)

| Symbol              | Parameter                                                       | Conditions  | Minimum | Typical | Maximum | Unit |

|---------------------|-----------------------------------------------------------------|-------------|---------|---------|---------|------|

| I <sub>PULLUP</sub> | I/O pin pull-up resistor<br>current when I/O is<br>unprogrammed | _           | _       | _       | 300     | μА   |

| C <sub>IO</sub>     | Input capacitance for user I/O pin                              | <del></del> | _       | _       | 8       | pF   |

| C <sub>GCLK</sub>   | Input capacitance for dual-purpose GCLK/user I/O pin            | _           | _       | _       | 8       | pF   |

#### Notes to Table 5-4:

- (1) Typical values are for  $T_A = 25$ °C,  $V_{CCINT} = 3.3$  or 2.5 V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, or 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>ccio</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (3)  $V_1$  = ground, no load, no toggling inputs.

- (4) Commercial temperature ranges from 0°C to 85°C with maximum current at 85°C.

- (5) Industrial temperature ranges from -40°C to 100°C with maximum current at 100°C.

- (6) This value applies to commercial and industrial range devices. For extended temperature range devices, the  $V_{SCHMITT}$  typical value is 300 mV for  $V_{CCIO} = 3.3$  V and 120 mV for  $V_{CCIO} = 2.5$  V.

- (7) The TCK input is susceptible to high pulse glitches when the input signal fall time is greater than 200 ns for all I/O standards.

- (8) This is a peak current value with a maximum duration of  $t_{\text{CONFIG}}$  time.

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than  $V_{\text{CCIO}}$ .

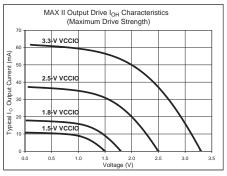

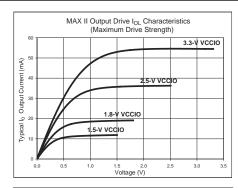

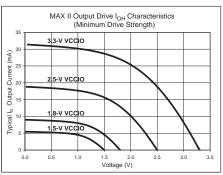

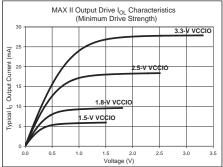

# **Output Drive Characteristics**

Figure 5–1 shows the typical drive strength characteristics of MAX II devices.

Figure 5-1. Output Drive Characteristics of MAX II Devices

### Note to Figure 5-1:

(1) The DC output current per pin is subject to the absolute maximum rating of Table 5-1.

# I/O Standard Specifications

Table 5–5 through Table 5–10 show the MAX II device family I/O standard specifications.

Table 5-5. 3.3-V LVTTL Specifications

| Symbol            | Parameter                 | Conditions      | Minimum | Maximum | Unit |

|-------------------|---------------------------|-----------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage  | _               | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.5    | 0.8     | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -4 mA (1) | 2.4     | _       | V    |

| V <sub>oL</sub>   | Low-level output voltage  | IOL = 4 mA (1)  | _       | 0.45    | V    |

Table 5-6. 3.3-V LVCMOS Specifications (Part 1 of 2)

| Symbol            | Parameter                | Conditions | Minimum | Maximum | Unit |

|-------------------|--------------------------|------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage       | _          | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage | _          | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage  | _          | -0.5    | 0.8     | V    |

Output and Output Enable  $t_{R4}$ Data-In/LUT Chain Output Routing User Logic Element Output Delay LUT De Delay Memory  $t_{OD}$ t<sub>LUT</sub> t<sub>FASTIO</sub> t<sub>xz</sub> Input Routing I/O Input Delay ► I/O Pin Register Control  $t_{SU}$ Delay t<sub>c</sub>  $t_{PRE}$ From Adjacent LE

Figure 5–2. MAX II Device Timing Model

I/O Pin INPUT

t<sub>GLOB</sub>

Global Input Delay

To Adjacent LE

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays, can be calculated as the sum of internal parameters.

Register Delays

Combinational Path Delay

Data-Out

Refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook* for more information.

This section describes and specifies the performance, internal, external, and UFM timing specifications. All specifications are representative of the worst-case supply voltage and junction temperature conditions.

# **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–13 shows the status of the MAX II device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under the worst-case voltage and junction temperature conditions.

Device

Preliminary

Final

EPM240

—

✓

EPM240Z (1)

—

✓

EPM570

—

✓

EPM570Z (1)

—

✓

**Table 5–13.** MAX II Device Timing Model Status (Part 1 of 2)

## **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Table 5–15 through Table 5–22 describe the MAX II device internal timing microparameters for logic elements (LEs), input/output elements (IOEs), UFM blocks, and MultiTrack interconnects. The timing values for –3, –4, and –5 speed grades shown in Table 5–15 through Table 5–22 are based on an EPM1270 device target, while –6, –7, and –8 speed grade values are based on an EPM570Z device target.

For more explanations and descriptions about each internal timing microparameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

**Table 5–15.** LE Internal Timing Microparameters

|                    |                                        | MAX II / MAX IIG |             |     |             |     |              | MAX IIZ |               |     |              |     |              |      |

|--------------------|----------------------------------------|------------------|-------------|-----|-------------|-----|--------------|---------|---------------|-----|--------------|-----|--------------|------|

| Symbol             |                                        | −3 S<br>Gra      | peed<br>ade |     | peed<br>ade | ı   | Speed<br>ade |         | Speed<br>rade |     | Speed<br>ade |     | Speed<br>ade |      |

|                    | Parameter                              | Min              | Max         | Min | Max         | Min | Max          | Min     | Max           | Min | Max          | Min | Max          | Unit |

| t <sub>lut</sub>   | LE combinational<br>LUT delay          | _                | 571         | _   | 742         | _   | 914          | _       | 1,215         | _   | 2,247        | _   | 2,247        | ps   |

| t <sub>сомв</sub>  | Combinational path delay               | _                | 147         | _   | 192         | _   | 236          | _       | 243           | _   | 305          | _   | 309          | ps   |

| t <sub>CLR</sub>   | LE register clear<br>delay             | 238              | _           | 309 | _           | 381 | _            | 401     | _             | 541 | _            | 545 | _            | ps   |

| t <sub>PRE</sub>   | LE register preset delay               | 238              | _           | 309 | _           | 381 | _            | 401     | _             | 541 | _            | 545 | _            | ps   |

| t <sub>su</sub>    | LE register setup<br>time before clock | 208              | _           | 271 | _           | 333 | _            | 260     | _             | 319 | _            | 321 | _            | ps   |

| t <sub>H</sub>     | LE register hold time after clock      | 0                | _           | 0   | _           | 0   | _            | 0       | _             | 0   | _            | 0   | _            | ps   |

| t <sub>co</sub>    | LE register clock-<br>to-output delay  | _                | 235         | _   | 305         | _   | 376          | _       | 380           | _   | 489          | _   | 494          | ps   |

| t <sub>clkhl</sub> | Minimum clock<br>high or low time      | 166              | _           | 216 | _           | 266 | _            | 253     | _             | 335 | _            | 339 | _            | ps   |

| tc                 | Register control delay                 | _                | 857         | _   | 1,114       | _   | 1,372        | _       | 1,356         | _   | 1,722        | _   | 1,741        | ps   |

|                         |       |     | MAX II / MAX IIG MAX IIZ |     |             |     |             |     |              |     |             |                   |         |    |

|-------------------------|-------|-----|--------------------------|-----|-------------|-----|-------------|-----|--------------|-----|-------------|-------------------|---------|----|

|                         |       |     | peed<br>ade              | _   | peed<br>ade | 1   | peed<br>ade |     | Speed<br>ade |     | peed<br>ade | –8 Speed<br>Grade |         |    |

| Standar                 | d     | Min | Max                      | Min | Max         | Min | Max         | Min | Max          | Min | Max         | Min               | Min Max |    |

| 3.3-V LVTTL             | 16 mA | _   | 206                      | _   | -20         | _   | -247        | _   | 1,433        | _   | 1,446       | _                 | 1,454   | ps |

|                         | 8 mA  | _   | 891                      | _   | 665         | _   | 438         | _   | 1,332        | _   | 1,345       | _                 | 1,348   | ps |

| 3.3-V LVCMOS            | 8 mA  | _   | 206                      | _   | -20         | _   | -247        | _   | 1,433        | _   | 1,446       | _                 | 1,454   | ps |

|                         | 4 mA  | _   | 891                      | _   | 665         | _   | 438         | _   | 1,332        |     | 1,345       | _                 | 1,348   | ps |

| 2.5-V LVTTL /<br>LVCMOS | 14 mA | _   | 222                      | _   | -4          | _   | -231        | _   | 213          | _   | 208         | _                 | 213     | ps |

|                         | 7 mA  | _   | 943                      | _   | 717         | _   | 490         | _   | 166          |     | 161         | _                 | 166     | ps |

| 3.3-V PCI               | 20 mA | _   | 161                      | _   | 210         | _   | 258         | _   | 1,332        | _   | 1,345       | _                 | 1,348   | ps |

**Table 5–20.**  $t_{XZ}$  IOE Microparameter Adders for Slow Slew Rate

The default slew rate setting for MAX II devices in the Quartus II design software is "fast".

**Table 5–21.** UFM Block Internal Timing Microparameters (Part 1 of 3)

|                   | Parameter                                                      | MAX II / MAX IIG  |     |                   |     |                   |     |                   | MAX IIZ |                   |     |                   |     |      |  |

|-------------------|----------------------------------------------------------------|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|---------|-------------------|-----|-------------------|-----|------|--|

| Symbol            |                                                                | -3 Speed<br>Grade |     | –4 Speed<br>Grade |     | –5 Speed<br>Grade |     | -6 Speed<br>Grade |         | -7 Speed<br>Grade |     | –8 Speed<br>Grade |     |      |  |

|                   |                                                                | Min               | Max | Min               | Max | Min               | Max | Min               | Max     | Min               | Max | Min               | Max | Unit |  |

| t <sub>ACLK</sub> | Address register clock period                                  | 100               | _   | 100               | _   | 100               | _   | 100               | _       | 100               | _   | 100               | _   | ns   |  |

| t <sub>ASU</sub>  | Address register shift signal setup to address register clock  | 20                |     | 20                | _   | 20                | _   | 20                | _       | 20                | _   | 20                | _   | ns   |  |

| t <sub>AH</sub>   | Address register shift signal hold to address register clock   | 20                | _   | 20                | _   | 20                | _   | 20                | _       | 20                | _   | 20                | _   | ns   |  |

| t <sub>ADS</sub>  | Address register data<br>in setup to address<br>register clock | 20                | _   | 20                | _   | 20                | _   | 20                | _       | 20                | _   | 20                | _   | ns   |  |

| t <sub>ADH</sub>  | Address register data in hold from address register clock      | 20                | _   | 20                | _   | 20                | _   | 20                | _       | 20                | _   | 20                | _   | ns   |  |

| t <sub>dclk</sub> | Data register clock period                                     | 100               |     | 100               | _   | 100               | _   | 100               | _       | 100               | _   | 100               | _   | ns   |  |

| t <sub>DSS</sub>  | Data register shift<br>signal setup to data<br>register clock  | 60                | _   | 60                | _   | 60                | _   | 60                | _       | 60                | _   | 60                | _   | ns   |  |

| t <sub>DSH</sub>  | Data register shift<br>signal hold from data<br>register clock | 20                | _   | 20                | _   | 20                | _   | 20                | _       | 20                | _   | 20                | _   | ns   |  |

**Table 5–27.** External Timing Input Delay Adders (Part 2 of 2)

|                         | MAX II / MAX IIG           |     |                   |     |                   |     |                   | MAX IIZ |                   |     |                   |     |     |      |

|-------------------------|----------------------------|-----|-------------------|-----|-------------------|-----|-------------------|---------|-------------------|-----|-------------------|-----|-----|------|

|                         | -3 Speed<br>Grade          |     | –4 Speed<br>Grade |     | –5 Speed<br>Grade |     | -6 Speed<br>Grade |         | -7 Speed<br>Grade |     | –8 Speed<br>Grade |     |     |      |

| I/O Standard            |                            | Min | Max               | Min | Max               | Min | Max               | Min     | Max               | Min | Max               | Min | Max | Unit |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0                 | _   | 0                 | _   | 0                 | _       | 0                 | _   | 0                 | _   | 0   | ps   |

|                         | With Schmitt<br>Trigger    | _   | 334               | _   | 434               | _   | 535               | _       | 387               | _   | 434               | _   | 442 | ps   |

| 2.5-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 23                | _   | 30                | _   | 37                | _       | 42                | _   | 43                | _   | 43  | ps   |

|                         | With Schmitt<br>Trigger    | _   | 339               | _   | 441               | _   | 543               | _       | 429               | _   | 476               | _   | 483 | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 291               | _   | 378               | _   | 466               | _       | 378               | _   | 373               | _   | 373 | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 681               | _   | 885               | _   | 1,090             | _       | 681               | _   | 622               | _   | 658 | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 0                 | _   | 0                 | _   | 0                 | _       | 0                 | _   | 0                 | _   | 0   | ps   |

**Table 5–28.** External Timing Input Delay  $t_{\mbox{\tiny GLOB}}$  Adders for GCLK Pins

|                         |                            |     |                   | II XAN | / MAX II          | G   |                   |     |                   | MA  | X IIZ             |     |     |      |

|-------------------------|----------------------------|-----|-------------------|--------|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|-----|-----|------|

|                         | -3 Speed<br>Grade          |     | -4 Speed<br>Grade |        | –5 Speed<br>Grade |     | –6 Speed<br>Grade |     | -7 Speed<br>Grade |     | –8 Speed<br>Grade |     |     |      |

| I/O Standard            |                            | Min | Max               | Min    | Max               | Min | Max               | Min | Max               | Min | Max               | Min | Max | Unit |

| 3.3-V LVTTL             | Without Schmitt<br>Trigger | _   | 0                 | _      | 0                 | _   | 0                 | _   | 0                 | _   | 0                 | _   | 0   | ps   |

|                         | With Schmitt<br>Trigger    | _   | 308               | _      | 400               | _   | 493               | _   | 387               | _   | 434               | _   | 442 | ps   |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0                 | _      | 0                 | _   | 0                 | _   | 0                 | _   | 0                 | _   | 0   | ps   |

|                         | With Schmitt<br>Trigger    | _   | 308               | _      | 400               | _   | 493               | _   | 387               | _   | 434               | _   | 442 | ps   |

| 2.5-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 21                | _      | 27                | _   | 33                | _   | 42                | _   | 43                | _   | 43  | ps   |

|                         | With Schmitt<br>Trigger    | _   | 423               | _      | 550               | _   | 677               | _   | 429               | _   | 476               | _   | 483 | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 353               | _      | 459               | _   | 565               | _   | 378               | _   | 373               | _   | 373 | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 855               | _      | 1,111             | _   | 1,368             | _   | 681               | _   | 622               | _   | 658 | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 6                 | _      | 7                 | _   | 9                 | _   | 0                 | _   | 0                 | _   | 0   | ps   |

**Table 5–34.** MAX II JTAG Timing Parameters (Part 2 of 2)

| Symbol            | Parameter                                      | Min | Max | Unit |

|-------------------|------------------------------------------------|-----|-----|------|

| t <sub>JPSU</sub> | JTAG port setup time (2)                       | 8   | _   | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 10  | _   | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output (2)                  |     | 15  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output (2)   | _   | 15  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance (2)   | _   | 15  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 8   | _   | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 10  | _   | ns   |

| t <sub>JSCO</sub> | Update register clock to output                | _   | 25  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 25  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 25  | ns   |

#### Notes to Table 5-34:

- (1) Minimum clock period specified for 10 pF load on the TDO pin. Larger loads on TDO will degrade the maximum TCK frequency.

- (2) This specification is shown for 3.3-V LVTTL/LVCMOS and 2.5-V LVTTL/LVCMOS operation of the JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the t<sub>JPSU</sub> minimum is 6 ns and t<sub>JPCO</sub>, t<sub>JPZX</sub>, and t<sub>JPXZ</sub> are maximum values at 35 ns.

# **Referenced Documents**

This chapter references the following documents:

- I/O Structure section in the MAX II Architecture chapter in the MAX II Device Handbook

- Hot Socketing and Power-On Reset in MAX II Devices chapter in the MAX II Device Handbook

- Operating Requirements for Altera Devices Data Sheet

- PowerPlay Power Analysis chapter in volume 3 of the Quartus II Handbook

- Understanding and Evaluating Power in MAX II Devices chapter in the MAX II Device Handbook

- *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

MII51006-1.6

### Software

MAX® II devices are supported by the Altera® Quartus® II design software with new, optional MAX+PLUS® II look and feel, which provides HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, and device programming. Refer to the Design Software Selector Guide for more details about the Quartus II software features.

The Quartus II software supports the Windows XP/2000/NT, Sun Solaris, Linux Red Hat v8.0, and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink interface.

# **Device Pin-Outs**

Printed device pin-outs for MAX II devices are available on the Altera website (www.altera.com).

# **Ordering Information**

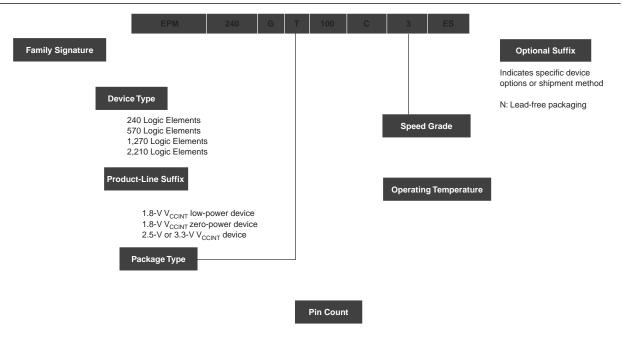

Figure 6–1 describes the ordering codes for MAX II devices. For more information about a specific package, refer to the *Package Information* chapter in the *MAX II Device Handbook*.

Figure 6-1. MAX II Device Packaging Ordering Information