Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Programmable Type               | In System Programmable                                      |

| Delay Time tpd(1) Max           | 9 ns                                                        |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                               |

| Number of Logic Elements/Blocks | 570                                                         |

| Number of Macrocells            | 440                                                         |

| Number of Gates                 | -                                                           |

| Number of I/O                   | 116                                                         |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                             |

| Mounting Type                   | Surface Mount                                               |

| Package / Case                  | 144-TFBGA                                                   |

| Supplier Device Package         | 144-MBGA (7x7)                                              |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epm570zm144c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

MAX II devices are available in space-saving FineLine BGA, Micro FineLine BGA, and thin quad flat pack (TQFP) packages (refer to Table 1–3 and Table 1–4). MAX II devices support vertical migration within the same package (for example, you can migrate between the EPM570, EPM1270, and EPM2210 devices in the 256-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins and JTAG pins are the same and power pins are subsets or supersets for a given package across device densities. The largest density in any package has the highest number of power pins; you must lay out for the largest planned density in a package to provide the necessary power pins for migration. For I/O pin migration across densities, cross reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins can be migrated. The Quartus® II software can automatically cross-reference and place all pins for you when given a device migration list.

Table 1-3. MAX II Packages and User I/O Pins

| Device   | 68-Pin<br>Micro<br>FineLine<br>BGA (1) | 100-Pin<br>Micro<br>FineLine<br>BGA (1) | 100-Pin<br>FineLine<br>BGA | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 144-Pin<br>Micro<br>FineLine<br>BGA (1) | 256-Pin<br>Micro<br>FineLine<br>BGA (1) | 256-Pin<br>FineLine<br>BGA | 324-Pin<br>FineLine<br>BGA |

|----------|----------------------------------------|-----------------------------------------|----------------------------|-----------------|-----------------|-----------------------------------------|-----------------------------------------|----------------------------|----------------------------|

| EPM240   | _                                      | 80                                      | 80                         | 80              | _               | _                                       | _                                       | _                          | _                          |

| EPM240G  |                                        |                                         |                            |                 |                 |                                         |                                         |                            |                            |

| EPM570   | _                                      | 76                                      | 76                         | 76              | 116             | _                                       | 160                                     | 160                        | _                          |

| EPM570G  |                                        |                                         |                            |                 |                 |                                         |                                         |                            |                            |

| EPM1270  | _                                      | _                                       | _                          | _               | 116             | _                                       | 212                                     | 212                        | _                          |

| EPM1270G |                                        |                                         |                            |                 |                 |                                         |                                         |                            |                            |

| EPM2210  | _                                      | _                                       | _                          | _               | _               | _                                       | _                                       | 204                        | 272                        |

| EPM2210G |                                        |                                         |                            |                 |                 |                                         |                                         |                            |                            |

| EPM240Z  | 54                                     | 80                                      | _                          | _               | _               | _                                       | _                                       | _                          | _                          |

| EPM570Z  | _                                      | 76                                      |                            | _               | _               | 116                                     | 160                                     | _                          | _                          |

#### Note to Table 1-3:

Table 1-4. MAX II TQFP, FineLine BGA, and Micro FineLine BGA Package Sizes

| Package                  | 68-Pin<br>Micro<br>FineLine<br>BGA | 100-Pin<br>Micro<br>FineLine<br>BGA | 100-Pin<br>FineLine<br>BGA | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 144-Pin<br>Micro<br>FineLine<br>BGA | 256-Pin<br>Micro<br>FineLine<br>BGA | 256-Pin<br>FineLine<br>BGA | 324-Pin<br>FineLine<br>BGA |

|--------------------------|------------------------------------|-------------------------------------|----------------------------|-----------------|-----------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Pitch (mm)               | 0.5                                | 0.5                                 | 1                          | 0.5             | 0.5             | 0.5                                 | 0.5                                 | 1                          | 1                          |

| Area (mm2)               | 25                                 | 36                                  | 121                        | 256             | 484             | 49                                  | 121                                 | 289                        | 361                        |

| Length × width (mm × mm) | 5 × 5                              | 6 × 6                               | 11 × 11                    | 16 × 16         | 22 × 22         | 7×7                                 | 11 × 11                             | 17 × 17                    | 19 × 19                    |

<sup>(1)</sup> Packages available in lead-free versions only.

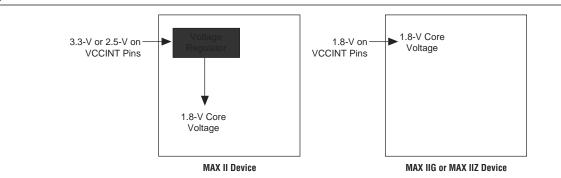

MAX II devices have an internal linear voltage regulator which supports external supply voltages of 3.3 V or 2.5 V, regulating the supply down to the internal operating voltage of 1.8 V. MAX IIG and MAX IIZ devices only accept 1.8 V as the external supply voltage. MAX IIZ devices are pin-compatible with MAX IIG devices in the 100-pin Micro FineLine BGA and 256-pin Micro FineLine BGA packages. Except for external supply voltage requirements, MAX II and MAX II G devices have identical pin-outs and timing specifications. Table 1–5 shows the external supply voltages supported by the MAX II family.

Table 1-5. MAX II External Supply Voltages

| Devices                                                          | EPM240<br>EPM570<br>EPM1270<br>EPM2210 | EPM240G<br>EPM570G<br>EPM1270G<br>EPM2210G<br>EPM240Z<br>EPM570Z <i>(1)</i> |

|------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------|

| MultiVolt core external supply voltage (V <sub>CCINT</sub> ) (2) | 3.3 V, 2.5 V                           | 1.8 V                                                                       |

| MultiVolt I/O interface voltage levels (Vccio)                   | 1.5 V, 1.8 V, 2.5 V, 3.3 V             | 1.5 V, 1.8 V, 2.5 V, 3.3 V                                                  |

#### Notes to Table 1-5:

- (1) MAX IIG and MAX IIZ devices only accept 1.8 V on their VCCINT pins. The 1.8-V VCCINT external supply powers the device core directly.

- (2) MAX II devices operate internally at 1.8 V.

### **Referenced Documents**

This chapter references the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- MAX II Logic Element to Macrocell Conversion Methodology white paper

# **Document Revision History**

Table 1–6 shows the revision history for this chapter.

Table 1-6. Document Revision History

| Date and Revision             | Changes Made                                            | Summary of Changes                         |

|-------------------------------|---------------------------------------------------------|--------------------------------------------|

| August 2009,<br>version 1.9   | ■ Updated Table 1–2.                                    | Added information for speed grade –8       |

| October 2008,                 | ■ Updated "Introduction" section.                       | _                                          |

| version 1.8                   | Updated new Document Format.                            |                                            |

| December 2007,                | ■ Updated Table 1–1 through Table 1–5.                  | Updated document with MAX IIZ information. |

| version1.7                    | <ul><li>Added "Referenced Documents" section.</li></ul> |                                            |

| December 2006,<br>version 1.6 | Added document revision history.                        | _                                          |

| August 2006,<br>version 1.5   | ■ Minor update to features list.                        | _                                          |

| July 2006,<br>version 1.4     | ■ Minor updates to tables.                              | _                                          |

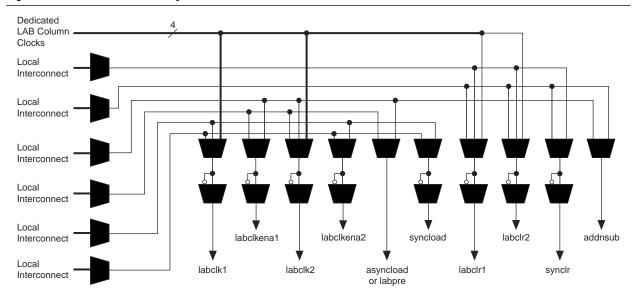

**Figure 2–5.** LAB-Wide Control Signals

# **Logic Elements**

The smallest unit of logic in the MAX II architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry-select capability. A single LE also supports dynamic single-bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and DirectLink interconnects. See Figure 2–6.

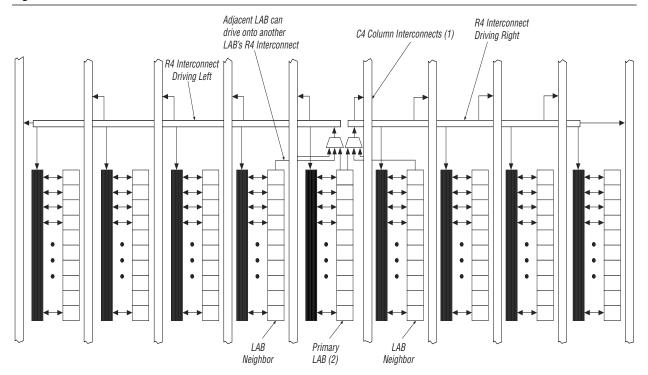

The R4 interconnects span four LABs and are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–10 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by row IOEs. For LAB interfacing, a primary LAB or horizontal LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

Figure 2-10. R4 Interconnect Connections

#### Notes to Figure 2-10:

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The column interconnect operates similarly to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs and row and column IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four LABs in an up and down direction

MAX II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinational output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in

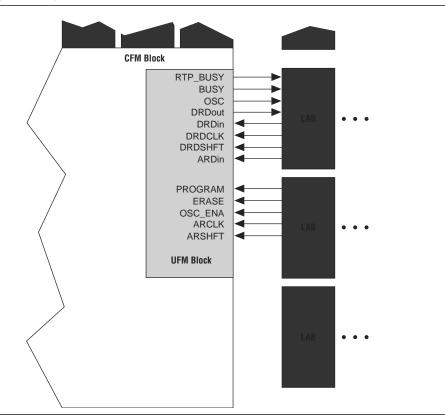

Figure 2–16. EPM240 UFM Block LAB Row Interface (Note 1)

#### Note to Figure 2–16:

(1) The UFM block inputs and outputs can drive to/from all types of interconnects, not only DirectLink interconnects from adjacent row LABs.

Figure 2–17. EPM570, EPM1270, and EPM2210 UFM Block LAB Row Interface

# **MultiVolt Core**

The MAX II architecture supports the MultiVolt core feature, which allows MAX II devices to support multiple  $V_{CC}$  levels on the  $V_{CCNT}$  supply. An internal linear voltage regulator provides the necessary 1.8-V internal voltage supply to the device. The voltage regulator supports 3.3-V or 2.5-V supplies on its inputs to supply the 1.8-V internal voltage to the device, as shown in Figure 2–18. The voltage regulator is not guaranteed for voltages that are between the maximum recommended 2.5-V operating voltage and the minimum recommended 3.3-V operating voltage.

The MAX IIG and MAX IIZ devices use external 1.8-V supply. The 1.8-V  $V_{CC}$  external supply powers the device core directly.

Figure 2–18. MultiVolt Core Feature in MAX II Devices

#### **Bus Hold**

Each MAX II device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option.

The bus-hold circuitry uses a resistor to pull the signal level to the last driven state. The *DC and Switching Characteristics* chapter in the *MAX II Device Handbook* gives the specific sustaining current for each  $V_{\text{CCIO}}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after the device has fully initialized. The bus-hold circuit captures the value on the pin present at the moment user mode is entered.

### **Programmable Pull-Up Resistor**

Each MAX II device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor holds the output to the  $V_{\text{CCIO}}$  level of the output pin's bank.

The programmable pull-up resistor feature should not be used at the same time as the bus-hold feature on a given I/O pin.

## **Programmable Input Delay**

The MAX II IOE includes a programmable input delay that is activated to ensure zero hold times. A path where a pin directly drives a register, with minimal routing between the two, may require the delay to ensure zero hold time. However, a path where a pin drives a register through long routing or through combinational logic may not require the delay to achieve a zero hold time. The Quartus II software uses this delay to ensure zero hold times when needed.

### MultiVolt I/O Interface

The MAX II architecture supports the MultiVolt I/O interface feature, which allows MAX II devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation ( $V_{\text{CCINT}}$ ), and up to four sets for input buffers and I/O output driver buffers ( $V_{\text{CCIO}}$ ), depending on the number of I/O banks available in the devices where each set of VCC pins powers one I/O bank. The EPM240 and EPM570 devices have two I/O banks respectively while the EPM1270 and EPM2210 devices have four I/O banks respectively.

Connect VCCIO pins to either a 1.5-V, 1.8 V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (that is, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems. Table 2–7 summarizes MAX II MultiVolt I/O support.

**Table 2–7.** MAX II MultiVolt I/O Support (Note 1)

|           |       | . !   | nput Signa   | I     |              | Output Signal |              |              |       |              |  |  |

|-----------|-------|-------|--------------|-------|--------------|---------------|--------------|--------------|-------|--------------|--|--|

| VCCIO (V) | 1.5 V | 1.8 V | 2.5 V        | 3.3 V | 5.0 V        | 1.5 V         | 1.8 V        | 2.5 V        | 3.3 V | 5.0 V        |  |  |

| 1.5       | ✓     | ✓     | ✓            | ✓     | _            | ✓             | _            | _            | _     | _            |  |  |

| 1.8       | ✓     | ✓     | ✓            | ✓     | _            | <b>√</b> (2)  | ✓            | _            | _     | _            |  |  |

| 2.5       | _     | _     | ✓            | ✓     | _            | <b>√</b> (3)  | <b>√</b> (3) | ✓            | _     | _            |  |  |

| 3.3       | _     | _     | <b>√</b> (4) | ✓     | <b>√</b> (5) | <b>√</b> (6)  | <b>√</b> (6) | <b>√</b> (6) | ✓     | <b>√</b> (7) |  |  |

#### Notes to Table 2-7:

- (1) To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V including the overshoot, disable the I/O clamp diode. However, to drive 5.0-V inputs to the device, enable the I/O clamp diode to prevent V<sub>I</sub> from rising above 4.0 V.

- (2) When  $V_{CCIO} = 1.8 \text{ V}$ , a MAX II device can drive a 1.5-V device with 1.8-V tolerant inputs.

- (3) When  $V_{CCIO} = 2.5$  V, a MAX II device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

- (4) When V<sub>CCIO</sub> = 3.3 V and a 2.5-V input signal feeds an input pin, the VCCIO supply current will be slightly larger than expected.

- (5) MAX II devices can be 5.0-V tolerant with the use of an external resistor and the internal I/O clamp diode on the EPM1270 and EPM2210 devices.

- (6) When  $V_{CCIO} = 3.3 \text{ V}$ , a MAX II device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

- (7) When V<sub>CCIO</sub> = 3.3 V, a MAX II device can drive a device with 5.0-V TTL inputs but not 5.0-V CMOS inputs. In the case of 5.0-V CMOS, open-drain setting with internal I/O clamp diode (available only on EPM1270 and EPM2210 devices) and external resistor is required.

## **Referenced Documents**

This chapter referenced the following documents:

- AN 428: MAX II CPLD Design Guidelines

- *DC and Switching Characteristics* chapter in the *MAX II Device Handbook*

- Hot Socketing and Power-On Reset in MAX II Devices chapter in the MAX II Device Handbook

- Using User Flash Memory in MAX II Devices chapter in the MAX II Device Handbook

MII51003-1.6

### Introduction

This chapter discusses how to use the IEEE Standard 1149.1 Boundary-Scan Test (BST) circuitry in MAX II devices and includes the following sections:

- "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" on page 3–1

- "In System Programmability" on page 3–4

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All MAX® II devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1-2001 specification. JTAG boundary-scan testing can only be performed at any time after  $V_{\text{CCINT}}$  and all  $V_{\text{CCIO}}$  banks have been fully powered and a  $t_{\text{CONFIG}}$  amount of time has passed. MAX II devices can also use the JTAG port for in-system programming together with either the Quartus® II software or hardware using Programming Object Files (.pof), JamTM Standard Test and Programming Language (STAPL) Files (.jam), or Jam Byte-Code Files (.jbc).

The JTAG pins support 1.5-V, 1.8-V, 2.5-V, or 3.3-V I/O standards. The supported voltage level and standard are determined by the  $V_{\rm CCIO}$  of the bank where it resides. The dedicated JTAG pins reside in Bank 1 of all MAX II devices.

MAX II devices support the JTAG instructions shown in Table 3–1.

**Table 3–1.** MAX II JTAG Instructions (Part 1 of 2)

| JTAG Instruction | Instruction Code | Description                                                                                                                                                                                                                                       |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD   | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.                                                                  |

| EXTEST (1)       | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                               |

| BYPASS           | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                       |

| USERCODE         | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO. This register defaults to all 1's if not specified in the Quartus II software.                          |

| IDCODE           | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                             |

| HIGHZ (1)        | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the boundary scan test data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins. |

**MAX II Device** Flash Altera FPGA **Memory Device** CONF DONE nSTATUS nCE DATA0 **nCONFIG** TDO\_U DCLK TDI\_U TDI TMS TMS\_U TCK\_U SHIFT U CLKDR\_U TDO UPDATE\_U

RUNIDLE\_U USER1\_U

Figure 3–1. MAX II Parallel Flash Loader

#### Notes to Figure 3-1:

- This block is implemented in LEs.

- (2) This function is supported in the Quartus II software.

# In System Programmability

MAX II devices can be programmed in-system via the industry standard 4-pin IEEE Std. 1149.1 (JTAG) interface. In-system programmability (ISP) offers quick, efficient iterations during design development and debugging cycles. The logic, circuitry, and interconnects in the MAX II architecture are configured with flash-based SRAM configuration elements. These SRAM elements require configuration data to be loaded each time the device is powered. The process of loading the SRAM data is called configuration. The on-chip configuration flash memory (CFM) block stores the SRAM element's configuration data. The CFM block stores the design's configuration pattern in a reprogrammable flash array. During ISP, the MAX II JTAG and ISP circuitry programs the design pattern into the CFM block's non-volatile flash array.

The MAX II JTAG and ISP controller internally generate the high programming voltages required to program the CFM cells, allowing in-system programming with any of the recommended operating external voltage supplies (that is, 3.3 V/2.5 V or 1.8 V for the MAX IIG and MAX IIZ devices). ISP can be performed anytime after  $V_{\text{CCINT}}$  and all  $V_{\text{CCIO}}$  banks have been fully powered and the device has completed the configuration power-up time. By default, during in-system programming, the I/O pins are tri-stated and weakly pulled-up to  $V_{\text{CCIO}}$  to eliminate board conflicts. The insystem programming clamp and real-time ISP feature allow user control of I/O state or behavior during ISP.

For more information, refer to "In-System Programming Clamp" on page 3–6 and "Real-Time ISP" on page 3–7.

These devices also offer an ISP\_DONE bit that provides safe operation when insystem programming is interrupted. This ISP\_DONE bit, which is the last bit programmed, prevents all I/O pins from driving until the bit is programmed.

Table 3–4 shows the programming times for MAX II devices using in-circuit testers to execute the algorithm vectors in hardware. Software-based programming tools used with download cables are slightly slower because of data processing and transfer limitations.

Table 3-4. MAX II Device Family Programming Times

| Description                     | EPM240<br>EPM240G<br>EPM240Z | EPM570<br>EPM570G<br>EPM570Z | EPM1270<br>EPM1270G | EPM2210<br>EPM2210G | Unit |

|---------------------------------|------------------------------|------------------------------|---------------------|---------------------|------|

| Erase + Program (1 MHz)         | 1.72                         | 2.16                         | 2.90                | 3.92                | sec  |

| Erase + Program (10 MHz)        | 1.65                         | 1.99                         | 2.58                | 3.40                | sec  |

| Verify (1 MHz)                  | 0.09                         | 0.17                         | 0.30                | 0.49                | sec  |

| Verify (10 MHz)                 | 0.01                         | 0.02                         | 0.03                | 0.05                | sec  |

| Complete Program Cycle (1 MHz)  | 1.81                         | 2.33                         | 3.20                | 4.41                | sec  |

| Complete Program Cycle (10 MHz) | 1.66                         | 2.01                         | 2.61                | 3.45                | sec  |

### **UFM Programming**

The Quartus II software, with the use of POF, Jam, or JBC files, supports programming of the user flash memory (UFM) block independent of the logic array design pattern stored in the CFM block. This allows updating or reading UFM contents through ISP without altering the current logic array design, or vice versa. By default, these programming files and methods will program the entire flash memory contents, which includes the CFM block and UFM contents. The stand-alone embedded Jam STAPL player and Jam Byte-Code Player provides action commands for programming or reading the entire flash memory (UFM and CFM together) or each independently.

For more information, refer to the *Using Jam STAPL for ISP via an Embedded Processor* chapter in the *MAX II Device Handbook*.

## **In-System Programming Clamp**

By default, the IEEE 1532 instruction used for entering ISP automatically tri-states all I/O pins with weak pull-up resistors for the duration of the ISP sequence. However, some systems may require certain pins on MAX II devices to maintain a specific DC logic level during an in-field update. For these systems, an optional in-system programming clamp instruction exists in MAX II circuitry to control I/O behavior during the ISP sequence. The in-system programming clamp instruction enables the device to sample and sustain the value on an output pin (an input pin would remain tri-stated if sampled) or to explicitly set a logic high, logic low, or tri-state value on any pin. Setting these options is controlled on an individual pin basis using the Quartus II software.

For more information, refer to the *Real-Time ISP and ISP Clamp for MAX II Devices* chapter in the *MAX II Device Handbook*.

## **Referenced Documents**

This chapter refereces the following documents:

- DC and Switching Characteristics chapter in the MAX II Device Handbook

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

# **Document Revision History**

Table 4–1 shows the revision history for this chapter.

Table 4-1. Document Revision History

| Date and Revision             | Changes Made                                                                              | Summary of Changes                         |

|-------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------|

| October 2008, version2.1      | Updated "MAX II Hot-Socketing Specifications" and "Power-On<br>Reset Circuitry" sections. | _                                          |

|                               | ■ Updated New Document Format.                                                            |                                            |

| December 2007,<br>version 2.0 | Updated "Hot Socketing Feature Implementation in MAX II<br>Devices" section.              | Updated document with MAX IIZ information. |

|                               | ■ Updated "Power-On Reset Circuitry" section.                                             |                                            |

|                               | ■ Updated Figure 4–5.                                                                     |                                            |

|                               | <ul><li>Added "Referenced Documents" section.</li></ul>                                   |                                            |

| December 2006, version 1.5    | Added document revision history.                                                          | _                                          |

| February 2006,                | ■ Updated "MAX II Hot-Socketing Specifications" section.                                  | _                                          |

| version 1.4                   | Updated "AC and DC Specifications" section.                                               |                                            |

|                               | ■ Updated "Power-On Reset Circuitry" section.                                             |                                            |

| June 2005,<br>version 1.3     | ■ Updated AC and DC specifications on page 4-2.                                           | _                                          |

| December 2004,                | <ul> <li>Added content to Power-Up Characteristics section.</li> </ul>                    | _                                          |

| version 1.2                   | ■ Updated Figure 4-5.                                                                     |                                            |

| June 2004,<br>version 1.1     | ■ Corrected Figure 4-2.                                                                   | _                                          |

### **Output Drive Characteristics**

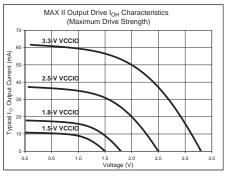

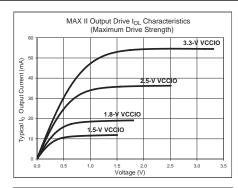

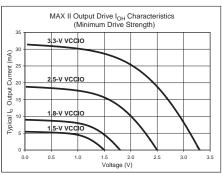

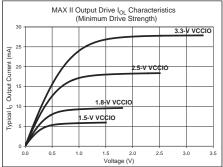

Figure 5–1 shows the typical drive strength characteristics of MAX II devices.

Figure 5-1. Output Drive Characteristics of MAX II Devices

#### Note to Figure 5-1:

(1) The DC output current per pin is subject to the absolute maximum rating of Table 5-1.

# I/O Standard Specifications

Table 5–5 through Table 5–10 show the MAX II device family I/O standard specifications.

Table 5-5. 3.3-V LVTTL Specifications

| Symbol            | Parameter                 | Conditions      | Minimum | Maximum | Unit |

|-------------------|---------------------------|-----------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage  | _               | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.5    | 0.8     | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -4 mA (1) | 2.4     | _       | V    |

| V <sub>oL</sub>   | Low-level output voltage  | IOL = 4 mA (1)  | _       | 0.45    | V    |

Table 5-6. 3.3-V LVCMOS Specifications (Part 1 of 2)

| Symbol            | Parameter                | Conditions | Minimum | Maximum | Unit |

|-------------------|--------------------------|------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage       | _          | 3.0     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage | _          | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage  | _          | -0.5    | 0.8     | V    |

### **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Table 5–15 through Table 5–22 describe the MAX II device internal timing microparameters for logic elements (LEs), input/output elements (IOEs), UFM blocks, and MultiTrack interconnects. The timing values for –3, –4, and –5 speed grades shown in Table 5–15 through Table 5–22 are based on an EPM1270 device target, while –6, –7, and –8 speed grade values are based on an EPM570Z device target.

For more explanations and descriptions about each internal timing microparameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

**Table 5–15.** LE Internal Timing Microparameters

|                    |                                        | MAX II / MAX IIG  |     |                   |       |                   | MAX IIZ |                   |       |                   |       |                   |       |      |

|--------------------|----------------------------------------|-------------------|-----|-------------------|-------|-------------------|---------|-------------------|-------|-------------------|-------|-------------------|-------|------|

|                    |                                        | -3 Speed<br>Grade |     | –4 Speed<br>Grade |       | -5 Speed<br>Grade |         | -6 Speed<br>Grade |       | -7 Speed<br>Grade |       | –8 Speed<br>Grade |       |      |

| Symbol             | Parameter                              | Min               | Max | Min               | Max   | Min               | Max     | Min               | Max   | Min               | Max   | Min               | Max   | Unit |

| t <sub>lut</sub>   | LE combinational<br>LUT delay          | _                 | 571 | _                 | 742   | _                 | 914     | _                 | 1,215 | _                 | 2,247 | _                 | 2,247 | ps   |

| t <sub>сомв</sub>  | Combinational path delay               | _                 | 147 | _                 | 192   | _                 | 236     | _                 | 243   | _                 | 305   | _                 | 309   | ps   |

| t <sub>CLR</sub>   | LE register clear<br>delay             | 238               | _   | 309               | _     | 381               | _       | 401               | _     | 541               | _     | 545               | _     | ps   |

| t <sub>PRE</sub>   | LE register preset delay               | 238               | _   | 309               | _     | 381               | _       | 401               | _     | 541               | _     | 545               | _     | ps   |

| t <sub>su</sub>    | LE register setup<br>time before clock | 208               | _   | 271               | _     | 333               | _       | 260               | _     | 319               | _     | 321               | _     | ps   |

| t <sub>H</sub>     | LE register hold time after clock      | 0                 | _   | 0                 | _     | 0                 | _       | 0                 | _     | 0                 | _     | 0                 | _     | ps   |

| t <sub>co</sub>    | LE register clock-<br>to-output delay  | _                 | 235 | _                 | 305   | _                 | 376     | _                 | 380   | _                 | 489   | _                 | 494   | ps   |

| t <sub>clkhl</sub> | Minimum clock<br>high or low time      | 166               | _   | 216               | _     | 266               | _       | 253               | _     | 335               | _     | 339               | _     | ps   |

| tc                 | Register control delay                 | _                 | 857 | _                 | 1,114 | _                 | 1,372   | _                 | 1,356 | _                 | 1,722 | _                 | 1,741 | ps   |

| Timing | Model | and | Specifications |

|--------|-------|-----|----------------|

|                   |                                                                                                          | MAX II / MAX IIG  |     |     |                   |     |                   | MAX | X IIZ             |     |                   |     |                   |      |

|-------------------|----------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|-----|-------------------|------|

|                   |                                                                                                          | -3 Speed<br>Grade |     | 1   | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | -6 Speed<br>Grade |     | -7 Speed<br>Grade |     | –8 Speed<br>Grade |      |

| Symbol            | Parameter                                                                                                | Min               | Max | Min | Max               | Min | Max               | Min | Max               | Min | Max               | Min | Max               | Unit |

| t <sub>oe</sub>   | Delay from data<br>register clock to data<br>register output                                             | 180               | -   | 180 | _                 | 180 | _                 | 180 | _                 | 180 | _                 | 180 | _                 | ns   |

| t <sub>RA</sub>   | Maximum read access time                                                                                 |                   | 65  | _   | 65                |     | 65                | _   | 65                | _   | 65                | _   | 65                | ns   |

| t <sub>oscs</sub> | Maximum delay between the OSC_ENA rising edge to the erase/program signal rising edge                    | 250               | _   | 250 | _                 | 250 | _                 | 250 | _                 | 250 | _                 | 250 | _                 | ns   |

| t <sub>osch</sub> | Minimum delay<br>allowed from the<br>erase/program signal<br>going low to<br>OSC_ENA signal<br>going low | 250               | _   | 250 | _                 | 250 | _                 | 250 | _                 | 250 | _                 | 250 | _                 | ns   |

**Table 5–21.** UFM Block Internal Timing Microparameters (Part 3 of 3)

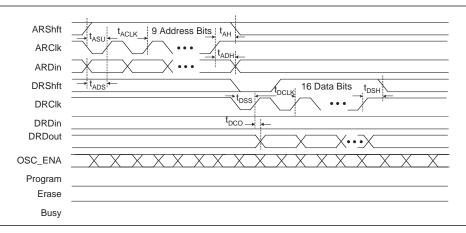

Figure 5–3 through Figure 5–5 show the read, program, and erase waveforms for UFM block timing parameters shown in Table 5–21.

Figure 5-3. UFM Read Waveforms

**Table 5–24.** EPM570 Global Clock External I/O Timing Parameters (Part 2 of 2)

|                  |                                                            |           | MAX II / MAX IIG |               |     |              | MAX IIZ |              |     |              |     |               |     |              |      |

|------------------|------------------------------------------------------------|-----------|------------------|---------------|-----|--------------|---------|--------------|-----|--------------|-----|---------------|-----|--------------|------|

|                  |                                                            |           |                  | Speed<br>rade | 1   | Speed<br>ade |         | Speed<br>ade |     | Speed<br>ade |     | Speed<br>rade |     | Speed<br>ade |      |

| Symbol           | Parameter                                                  | Condition | Min              | Max           | Min | Max          | Min     | Max          | Min | Max          | Min | Max           | Min | Max          | Unit |

| f <sub>CNT</sub> | Maximum<br>global clock<br>frequency for<br>16-bit counter | _         | _                | 304.0<br>(1)  | _   | 247.5        | _       | 201.1        | _   | 184.1        | _   | 123.5         | _   | 118.3        | MHz  |

#### Note to Table 5-24:

(1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global clock input pin maximum frequency.

Table 5–25 shows the external I/O timing parameters for EPM1270 devices.

Table 5-25. EPM1270 Global Clock External I/O Timing Parameters

|                  |                                                                 |           | MAX II / MAX IIG |           |         |          |                |       |      |

|------------------|-----------------------------------------------------------------|-----------|------------------|-----------|---------|----------|----------------|-------|------|

|                  |                                                                 |           | –3 Sp            | eed Grade | -4 Spec | ed Grade | –5 Speed Grade |       |      |

| Symbol           | Parameter                                                       | Condition | Min              | Max       | Min     | Max      | Min            | Max   | Unit |

| t <sub>PD1</sub> | Worst case pin-to-pin<br>delay through 1 look-up<br>table (LUT) | 10 pF     | _                | 6.2       | _       | 8.1      | _              | 10.0  | ns   |

| t <sub>PD2</sub> | Best case pin-to-pin<br>delay through 1 LUT                     | 10 pF     | _                | 3.7       | _       | 4.8      | _              | 5.9   | ns   |

| t <sub>su</sub>  | Global clock setup time                                         | _         | 1.2              | _         | 1.5     | _        | 1.9            | _     | ns   |

| t <sub>H</sub>   | Global clock hold time                                          | _         | 0                | _         | 0       | _        | 0              | _     | ns   |

| t <sub>co</sub>  | Global clock to output delay                                    | 10 pF     | 2.0              | 4.6       | 2.0     | 5.9      | 2.0            | 7.3   | ns   |

| t <sub>ch</sub>  | Global clock high time                                          | _         | 166              | _         | 216     | _        | 266            | _     | ps   |

| t <sub>CL</sub>  | Global clock low time                                           | _         | 166              | _         | 216     | _        | 266            | _     | ps   |

| t <sub>cnt</sub> | Minimum global clock<br>period for<br>16-bit counter            | _         | 3.3              | _         | 4.0     | _        | 5.0            | _     | ns   |

| f <sub>CNT</sub> | Maximum global clock frequency for 16-bit counter               | _         | _                | 304.0 (1) | _       | 247.5    | _              | 201.1 | MHz  |

#### Note to Table 5-25:

(1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global clock input pin maximum frequency.

**Table 5–31.** MAX II IOE Programmable Delays

|                                               |     | N            | / MAX II |              | MAX IIZ |              |     |              |     |              |     |              |      |

|-----------------------------------------------|-----|--------------|----------|--------------|---------|--------------|-----|--------------|-----|--------------|-----|--------------|------|

|                                               |     | Speed<br>ade |          | Speed<br>ade | ı       | Speed<br>ade |     | Speed<br>ade |     | Speed<br>ade |     | Speed<br>ade |      |

| Parameter                                     | Min | Max          | Min      | Max          | Min     | Max          | Min | Max          | Min | Max          | Min | Max          | Unit |

| Input Delay from Pin to<br>Internal Cells = 1 | _   | 1,225        | _        | 1,592        | _       | 1,960        | _   | 1,858        | _   | 2,171        | _   | 2,214        | ps   |

| Input Delay from Pin to<br>Internal Cells = 0 | _   | 89           |          | 115          | _       | 142          | _   | 569          | _   | 609          |     | 616          | ps   |

# **Maximum Input and Output Clock Rates**

Table 5–32 and Table 5–33 show the maximum input and output clock rates for standard I/O pins in MAX II devices.

Table 5-32. MAX II Maximum Input Clock Rate for I/O

|              |                            | MAX II / MAX IIG  |                   |                   |                   | MAX IIZ           |                   |      |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------|

| I/O Standard |                            | -3 Speed<br>Grade | –4 Speed<br>Grade | –5 Speed<br>Grade | -6 Speed<br>Grade | –7 Speed<br>Grade | –8 Speed<br>Grade | Unit |

| 3.3-V LVTTL  | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |

|              | With Schmitt<br>Trigger    | 250               | 250               | 250               | 250               | 250               | 250               | MHz  |

| 3.3-V LVCMOS | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |

|              | With Schmitt<br>Trigger    | 250               | 250               | 250               | 250               | 250               | 250               | MHz  |

| 2.5-V LVTTL  | Without Schmitt<br>Trigger | 220               | 220               | 220               | 220               | 220               | 220               | MHz  |

|              | With Schmitt<br>Trigger    | 188               | 188               | 188               | 188               | 188               | 188               | MHz  |

| 2.5-V LVCMOS | Without Schmitt<br>Trigger | 220               | 220               | 220               | 220               | 220               | 220               | MHz  |

|              | With Schmitt<br>Trigger    | 188               | 188               | 188               | 188               | 188               | 188               | MHz  |

| 1.8-V LVTTL  | Without Schmitt<br>Trigger | 200               | 200               | 200               | 200               | 200               | 200               | MHz  |

| 1.8-V LVCMOS | Without Schmitt<br>Trigger | 200               | 200               | 200               | 200               | 200               | 200               | MHz  |

| 1.5-V LVCMOS | Without Schmitt<br>Trigger | 150               | 150               | 150               | 150               | 150               | 150               | MHz  |

| 3.3-V PCI    | Without Schmitt<br>Trigger | 304               | 304               | 304               | 304               | 304               | 304               | MHz  |

**Table 5–34.** MAX II JTAG Timing Parameters (Part 2 of 2)

| Symbol            | Parameter                                      | Min | Max | Unit |

|-------------------|------------------------------------------------|-----|-----|------|

| t <sub>JPSU</sub> | JTAG port setup time (2)                       | 8   | _   | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 10  | _   | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output (2)                  |     | 15  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output (2)   | _   | 15  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance (2)   | _   | 15  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 8   | _   | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 10  | _   | ns   |

| t <sub>JSCO</sub> | Update register clock to output                | _   | 25  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 25  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 25  | ns   |

#### Notes to Table 5-34:

- (1) Minimum clock period specified for 10 pF load on the TDO pin. Larger loads on TDO will degrade the maximum TCK frequency.

- (2) This specification is shown for 3.3-V LVTTL/LVCMOS and 2.5-V LVTTL/LVCMOS operation of the JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the t<sub>JPSU</sub> minimum is 6 ns and t<sub>JPCO</sub>, t<sub>JPZX</sub>, and t<sub>JPXZ</sub> are maximum values at 35 ns.

### **Referenced Documents**

This chapter references the following documents:

- I/O Structure section in the MAX II Architecture chapter in the MAX II Device Handbook

- Hot Socketing and Power-On Reset in MAX II Devices chapter in the MAX II Device Handbook

- Operating Requirements for Altera Devices Data Sheet

- PowerPlay Power Analysis chapter in volume 3 of the Quartus II Handbook

- Understanding and Evaluating Power in MAX II Devices chapter in the MAX II Device Handbook

- *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

Table 5-35. Document Revision History (Part 2 of 2)

| Date and Revision         | Changes Made                                                           | Summary of Changes |

|---------------------------|------------------------------------------------------------------------|--------------------|

| June 2005,                | ■ Updated the R <sub>PULLUP</sub> parameter in Table 5-4.              | _                  |

| version 1.3               | ■ Added Note 2 to Tables 5-8 and 5-9.                                  |                    |

|                           | ■ Updated Table 5-13.                                                  |                    |

|                           | ■ Added "Output Drive Characteristics" section.                        |                    |

|                           | ■ Added I <sup>2</sup> C mode and Notes 5 and 6 to Table 5-14.         |                    |

|                           | ■ Updated timing values to Tables 5-14 through 5-33.                   |                    |

| December 2004,            | ■ Updated timing Tables 5-2, 5-4, 5-12, and Tables 15-14 through 5-34. | _                  |

| version 1.2               | ■ Table 5-31 is new.                                                   |                    |

| June 2004,<br>version 1.1 | ■ Updated timing Tables 5-15 through 5-32.                             | _                  |